Логічний процесор

Номер патенту: 112424

Опубліковано: 12.12.2016

Автори: Косенко Віктор Васильович, Дергачов Володимир Андрійович, Павлик Ганна Володимирівна

Формула / Реферат

Логічний процесор, що містить дві шини даних, вхід запуску, вихід результату, два мультиплексора, блок пам'яті, двійковий лічильник, вихід наявності рішення, блок керування, елемент рівнозначність, тригер, причому перша шина даних з'єднана з інформаційними входами першого мультиплексора, друга шина даних з'єднана з інформаційними входами другого мультиплексора, вхід запуску з'єднаний з входом запуску блока керування, вихід блока керування з'єднаний з виходом наявності рішення, адресні виходи блока керування з'єднані з адресними входами мультиплексорів, та входами даних блока пам'яті, вихід першого мультиплексора з'єднаний з першим входом елемента рівнозначність, вихід другого мультиплексора з'єднаний з другим входом елемента рівнозначність, вихід якого з'єднаний з входом двійкового лічильника та одиничним входом тригера, вихід тригера з'єднаний з виходом результату, виходи двійкового лічильника з'єднані з адресними входами блока пам'яті, який відрізняється тим, що має формувач імпульсу запису, елемент затримки, причому вихід елемента рівнозначність з'єднаний через елемент затримки з входом формувача імпульсу запису, вихід формувача імпульсу запису з'єднаний з входом запису блока пам'яті.

Текст

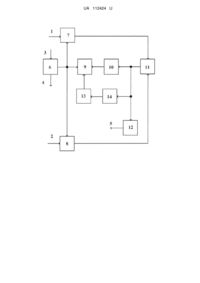

Реферат: Логічний процесор містить дві шини даних, вхід запуску, вихід результату, два мультиплексора, блок пам'яті, двійковий лічильник, вихід наявності рішення, блок керування, елемент рівнозначність, тригер, причому перша шина даних з'єднана з інформаційними входами першого мультиплексора, друга шина даних з'єднана з інформаційними входами другого мультиплексора, вхід запуску з'єднаний з входом запуску блока керування, вихід блока керування з'єднаний з виходом наявності рішення, адресні виходи блока керування з'єднані з адресними входами мультиплексорів, та входами даних блока пам'яті, вихід першого мультиплексора з'єднаний з першим входом елемента рівнозначність, вихід другого мультиплексора з'єднаний з другим входом елемента рівнозначність, вихід якого з'єднаний з входом двійкового лічильника та одиничним входом тригера, вихід тригера з'єднаний з виходом результату, виходи двійкового лічильника з'єднані з адресними входами блока пам'яті. Має формувач імпульсу запису, елемент затримки, причому вихід елемента рівнозначність з'єднаний через елемент затримки з входом формувача імпульсу запису, вихід формувача імпульсу запису з'єднаний з входом запису блока пам'яті. UA 112424 U (12) UA 112424 U UA 112424 U 5 10 15 20 25 30 35 40 45 50 55 60 Корисна модель належить до обчислювальної техніки і призначена для аналізу ортогональності двійкових векторів та визначення множини наборів для яких ортогональність порушується, та апаратної реалізації відповідної мікрокоманди. Відомий пристрій для логічної обробки інформації, що містить вхідні шини коефіцієнтів рівняння, вхідну шину правої частини рівняння, шина результату, двійковий лічильник, групи з першою по n-ную елементів І, операційний пристрій, блок порівняння, тригер, два елементи НІ, два індикатори, генератор імпульсів, два елементи І, суматори по модулю 2, виходи операційного пристрою, елементи Рівнозначність (а.с. СРСР N 1262519, кл.G 06 F 15/20, 1985р.). Недоліком відомого пристрою є низка надійність. Відомий логічний процесор (а.с. СРСР № 1568052, G06F15/20, 1990 р., Бюл. 20), що містить першу шину даних, вхід запуску, вихід результату, два мультиплексора, блок пам'яті, двійковий лічильник, причому перша шина даних з'єднана з інформаційними входами першого мультиплексора. Недоліком відомого пристрою є низка надійність. Найбільш близьким по технічній суті і результату, що досягається є логічний процесор (патент України № 60889, G06F15/20, № 2003032629, заяв. 26.03.2003, опубл. 15.10.2003 р., Бюл. № 10), що містить дві шини даних, вхід запуску, вихід результату, два мультиплексора, блок пам'яті, двійковий лічильник, вихід наявності рішення, блок керування, елемент рівнозначність, тригер, причому перша шина даних з'єднана з інформаційними входами першого мультиплексора, друга шина даних з'єднана з інформаційними входами другого мультиплексора, вхід запуску з'єднаний з входом запуску блока керування, вихід блока керування з'єднаний з виходом наявності рішення, адресні виходи блока керування з'єднані з адресними входами мультиплексорів, та входами даних блока пам'яті, вихід першого мультиплексора з'єднаний з першим входом елемента рівнозначність, вихід другого мультиплексора з'єднаний з другим входом елемента рівнозначність, вихід якого з'єднаний з входом двійкового лічильника та одиничним входом тригера, вихід тригера з'єднаний з виходом результату, виходи двійкового лічильника з'єднані з адресними входами блока пам'яті. Недоліком відомого пристрою є низка надійність. В основу корисної моделі поставлено задачу створити логічний процесор з більшою надійністю шляхом введення нового складу елементів, та нової організації взаємозв'язків між ними. Поставлена задача вирішується тим, що логічний процесор, що містить дві шини даних, вхід запуску, вихід результату, два мультиплексора, блок пам'яті, двійковий лічильник, вихід наявності рішення, блок керування, елемент рівнозначність, тригер, причому перша шина даних з'єднана з інформаційними входами першого мультиплексора, друга шина даних з'єднана з інформаційними входами другого мультиплексора, вхід запуску з'єднаний з входом запуску блока керування, вихід блока керування з'єднаний з виходом наявності рішення, адресні виходи блока керування з'єднані з адресними входами мультиплексорів, та входами даних блока пам'яті, вихід першого мультиплексора з'єднаний з першим входом елемента рівнозначність, вихід другого мультиплексора з'єднаний з другим входом елемента рівнозначність, вихід якого з'єднаний з входом двійкового лічильника та одиничним входомтригера, вихід тригера з'єднаний з виходом результату, виходи двійкового лічильника з'єднані з адресними входами блока пам'яті, згідно з корисною моделлю має формувач імпульсу запису, елемент затримки, причому вихід елемента рівнозначність з'єднаний через елемент затримки з входом формувача імпульсу, вихід формувача імпульсу запису з'єднаний з входом запису блока пам'яті. Заявлений логічний процесор має новий склад елементів, та нову організацію взаємозв'язків між ними, тобто містить нову сукупність ознак, які забезпечують нові технічні властивості винаходу. Технічний результат, як наслідок цих властивостей - підвищена надійність роботи. На кресленні представлена функціональна схема логічного процесора. Логічний процесор містить першу шину даних 1, другу шину даних 2, вхід запуску 3, вихід наявності рішення 4, вихід результату 5, блок керування 6, мультиплексори 7, 8, блок пам'яті 9, двійковий лічильник 10, елемент рівнозначність 11, тригер 12, формувач імпульсу запису 13, елемент затримки 14, причому перша шина даних 1 з'єднана з інформаційними входами першого мультиплексора 7, друга шина даних 2 з'єднана з інформаційними входами другого мультиплексора 8, вхід запуска 3 з'єднаний з входом запуску блока керування 6, вихід блока керування 6 з'єднаний з виходом наявності рішення 4, адресні виходи блока керування 6 з'єднані з адресними входами мультиплексорів 7, 8 та входами даних блока пам'яті 9, вихід першого мультиплексора 7 з'єднаний з першим входом елемента рівнозначність 11, вихід другого мультиплексора 8 з'єднаний з другим входом елемента рівнозначність 11, вихід якого 1 UA 112424 U 5 10 15 20 з'єднаний з входом двійкового лічильника 10 та одиничним входом тригера 12, вихід тригера 12 з'єднаний з виходом результату 5, виходи двійкового лічильника 10 з'єднані з адресними входами блока пам'яті 9, вихід елемента рівнозначність 11 з'єднаний через елемент затримки 14 з входом формувача імпульсу запису 13, вихід формувача імпульсу запису 13 з'єднаний з входом запису блока пам'яті 9. Працює пристрій таким чином. У вихідному стані двійковий лічильник 10 і тригер 12 знаходяться в нульовому стані. На шини даних 1 і 2 подаються відповідно значення першого і другого двійкових векторів. Після подачі сигналу на вхід запуску 3 блок керування 6 послідовно формує двійкові набори. Для кожного набору на виходи мультиплексоров 7 і 8 надходять відповідні значення двійкових векторів. Елемент рівнозначність 11 робить порівняння цих значень і якщо вони рівні, то формує сигнал "1", що переводить тригер 12 у стан "1" і збільшує стан двійкового лічильника 10 на одиницю. Сигнал "1" з виходу елемента рівнозначність 11 через елемент затримки 14 поступає на вхід формувача імпульсу запису, який через заданий час затримки формує імпульс на вході двійкового лічильника 10. Стан двійкового лічильника 10 є адресою, по якому відбувається запис у блок пам'яті 9 набору, на якому виявлена неортогональність. Зазначений процес повторюється для всіх наборів. По закінченні процесу на виході наявності результату формується сигнал "1" і процес зупиняється. Якщо вектора ортогональні, то на виході результату 5 значення "0", якщо неортогональні, то на виході результату значення "1", а в блоці пам'яті 9 записані двійкові коди наборів, на яких умова ортогональності порушується. У заявленому пристрої запис даних у блок пам'яті 9 здійснюється тільки після формування значень на виходах двійкового лічильника 10, тому він має більшу надійність. ФОРМУЛА КОРИСНОЇ МОДЕЛІ 25 30 35 Логічний процесор, що містить дві шини даних, вхід запуску, вихід результату, два мультиплексора, блок пам'яті, двійковий лічильник, вихід наявності рішення, блок керування, елемент рівнозначність, тригер, причому перша шина даних з'єднана з інформаційними входами першого мультиплексора, друга шина даних з'єднана з інформаційними входами другого мультиплексора, вхід запуску з'єднаний з входом запуску блока керування, вихід блока керування з'єднаний з виходом наявності рішення, адресні виходи блока керування з'єднані з адресними входами мультиплексорів, та входами даних блока пам'яті, вихід першого мультиплексора з'єднаний з першим входом елемента рівнозначність, вихід другого мультиплексора з'єднаний з другим входом елемента рівнозначність, вихід якого з'єднаний з входом двійкового лічильника та одиничним входом тригера, вихід тригера з'єднаний з виходом результату, виходи двійкового лічильника з'єднані з адресними входами блока пам'яті, який відрізняється тим, що має формувач імпульсу запису, елемент затримки, причому вихід елемента рівнозначність з'єднаний через елемент затримки з входом формувача імпульсу запису, вихід формувача імпульсу запису з'єднаний з входом запису блока пам'яті. 2 UA 112424 U Комп’ютерна верстка Д. Шеверун Державна служба інтелектуальної власності України, вул. Василя Липківського, 45, м. Київ, МСП, 03680, Україна ДП “Український інститут інтелектуальної власності”, вул. Глазунова, 1, м. Київ – 42, 01601 3

ДивитисяДодаткова інформація

МПК / Мітки

МПК: G06F 15/00

Код посилання

<a href="https://ua.patents.su/5-112424-logichnijj-procesor.html" target="_blank" rel="follow" title="База патентів України">Логічний процесор</a>

Попередній патент: Модель туберкульозного спондиліту

Наступний патент: Автоматизована система контролю

Випадковий патент: Дерматом з секторним механізмом для зрізування середнього рельєфного аутодермотрансплантата