Логічний процесор

Номер патенту: 107519

Опубліковано: 10.06.2016

Автори: Дергачов Володимир Андрійович, Павлик Ганна Володимирівна, Савельєв Анатолій Семенович

Формула / Реферат

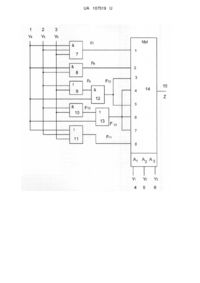

Логічний процесор, що містить шість входів пристрою, вихід пристрою, чотири елементи І, два елемента АБО, який відрізняється тим, що містить мультиплексор із трьома адресними входами й вісьмома інформаційними входами, причому перший вхід пристрою з'єднаний з першими входами першого, другого, третього елементів І, першого та другого елементів АБО, другий вхід пристрою з'єднаний з другими входами першого, другого, елементів І, другого елемента АБО, першими входами першого елемента АБО, четвертого елемента І, третій вхід пристрою з'єднаний з третім входом першого елемента І, другим входом першого елемента АБО, другим входом четвертого елемента І, третім входом другого елемента АБО, вихід першого елемента І з'єднаний з першим інформаційним входом мультиплексора, вихід другого елемента І з'єднаний з другим інформаційним входом мультиплексора, вихід першого елемента АБО з'єднаний з другим входом третього елемента І, вихід четвертого елемента І з'єднаний з другим входом першого елемента АБО, вихід третього елемента І з'єднаний з третім та п'ятим інформаційними входами мультиплексора, вихід першого елемента АБО з'єднаний з четвертим, шостим, сьомим інформаційними входами мультиплексора, вихід другого елемента АБО з'єднаний з восьмим інформаційним входом мультиплексора, четвертий вхід пристрою з'єднаний з першим адресним входом мультиплексора, п'ятий вхід пристрою з'єднаний з другим адресним входом мультиплексора, шостий вхід пристрою з'єднаний з третім адресним входом мультиплексора, вихід мультиплексора з'єднаний з виходом пристрою.

Текст

Реферат: Логічний процесор містить шість входів пристрою, чотири елементи І, два елементи АБО, мультиплексор із трьома адресними входами та вісьмома інформаційними входами, вихід пристрою. UA 107519 U (12) UA 107519 U UA 107519 U 5 10 15 20 25 30 35 40 45 50 55 Корисна модель належить до автоматики і обчислювальної техніки і призначена для реалізації шляхом настройки типових логічних функцій. Відомий логічний процесор, що містить входи модуля, вихід модуля, мажоритарні елементи [патент РФ № 2294008, М. кл. G06F 7/57, опубл. 20.02.2007]. Недоліком відомого пристрою є низькі функціональні можливості. Відомий логічний процесор, що містить входи модуля, вихід модуля, елементи І, АБО [патент РФ № 2491613, М. кл. G06F 7/38, опубл. 27.08.2013]. Недоліком відомого пристрою є низькі функціональні можливості. Найближчим аналогом є логічний процесор [патент РФ № 2260205, М. кл. G06F 7/38, опубл. 10.09.2005], що містить шість входів пристрою, вихід пристрою, чотири елементи І, два елемента АБО. Недоліком відомого пристрою є низькі функціональні можливості. В основу корисної моделі поставлено задачу вдосконалення логічного процесора шляхом введення нового складу елементів та нової організації взаємозв'язків між ними, забезпечення ширших функціональних можливостей. Поставлена задача вирішується тим, що логічний процесор, що містить шість входів пристрою, вихід пристрою, чотири елементи І, два елемента АБО, згідно з корисною моделлю, містить мультиплексор із трьома адресними входами й вісьмома інформаційними входами, причому перший вхід пристрою з'єднаний з першими входами першого, другого, третього елементів І, першого та другого елементів АБО, другий вхід пристрою з'єднаний з другими входами першого, другого, елементів І, другого елемента АБО, першими входами першого елемента АБО, четвертого елемента І, третій вхід пристрою з'єднаний з третім входом першого елемента І, другим входом першого елемента АБО, другим входом четвертого елемента І, третім входом другого елемента АБО, вихід першого елемента І з'єднаний з першим інформаційним входом мультиплексора, вихід другого елемента І з'єднаний з другим інформаційним входом мультиплексора, вихід першого елемента АБО з'єднаний з другим входом третього елемента І, вихід четвертого елемента І з'єднаний з другим входом першого елемента АБО, вихід третього елемента І з'єднаний з третім та п'ятим інформаційними входами мультиплексора, вихід першого елемента АБО з'єднаний з четвертим, шостим, сьомим інформаційними входами мультиплексора, вихід другого елемента АБО з'єднаний з восьмим інформаційним входом мультиплексора, четвертий вхід пристрою з'єднаний з першим адресним входом мультиплексора, п'ятий вхід пристрою з'єднаний з другим адресним входом мультиплексора, шостий вхід пристрою з'єднаний з третім адресним входом мультиплексора, вихід мультиплексора з'єднаний з виходом пристрою. Заявлений пристрій має новий склад елементів та нову організацію взаємозв'язків між ними, тобто містить нову сукупність ознак, які забезпечують нові технічні властивості корисної моделі, розширення функціональних можливостей. На кресленні представлена функціональна схема логічного процесора, що містить шість входів пристрою 1, 2, 3, 4, 5, 6, чотири елементи І 7, 8, 10, 12, два елемента АБО 9, 13, мультиплексор із трьома адресними входами та вісьмома інформаційними входами 14, вихід пристрою 15, причому перший вхід пристрою 1 з'єднаний з першими входами першого 7, другого 8, третього 12 елементів І, першого та другого елементів АБО 9, 13, другий вхід пристрою 2 з'єднаний з другими входами першого 7, другого 8, елементів І, другого елемента АБО 11, першими входами першого елемента АБО 9, четвертого елемента І 10, третій вхід пристрою 3 з'єднаний з третім входом першого елемента І 7, другим входом першого елемента АБО 9, другим входом четвертого елемента І 10, третім входом другого елемента АБО 11, вихід першого елемента І 7 з'єднаний з першим інформаційним входом мультиплексора 14, вихід другого елемента І 8 з'єднаний з другим інформаційним входом мультиплексора 14, вихід першого елемента АБО 9 з'єднаний з другим входом третього елемента 112, вихід четвертого елемента І 10 з'єднаний з другим входом першого елемента АБО 13, вихід третього елемента І 12 з'єднаний з третім та п'ятим інформаційними входами мультиплексора 14, вихід першого елемента АБО 13 з'єднаний з четвертим, шостим, сьомим інформаційними входами мультиплексора 14, вихід другого елемента АБО 11 з'єднаний з восьмим інформаційним входом мультиплексора 14, четвертий вхід пристрою 4 з'єднаний з першим адресним входом мультиплексора 14, п'ятий вхід пристрою 5 з'єднаний з другим адресним входом мультиплексора 14, шостий вхід пристрою 6 з'єднаний з третім адресним входом мультиплексора 14, вихід мультиплексора 14 з'єднаний з виходом пристрою 15. Логічний процесор працює таким чином. Для реалізації логічних функцій необхідно на входи 1, 2, 3, 4, 5, 6 пристрою подати сигнали відповідно до таблиці настроювань. 60 1 UA 107519 U Таблиця № 1 2 3 4 5 6 Значення сигналів на входах Y, Y2 Y3 Y4 Y5 0 X1 Х2 0 Х3 0 Х1 Х2 1 Х3 1 X1 Х2 0 Х3 1 Х1 Х2 1 Х3 0 1 1 Х1 Х2 0 1 0 Х1 Х2 Y6 Х4 Х4 Х4 Х4 Х3 Х3 Вид логічної функції, що реалізується Х 1 × 2Х 3 × 4 Х1 × 2Х3 v X1 × 2X4 v X1 × 3X4 v X2 × 3X4 Х1 × 2 v X1 × 3 v X1 × 4 v X2 × 3 v X2 × 4 v Х3 × 4 X 1 v X2 v Х3 v Х4 X1 v Х2 × 3 X1(Х2 v Х3) Порівняння функціональних можливостей логічного процесора та найближчого аналога показує, що заявлений пристрій реалізує більше логічних функцій, тобто має ширші функціональні можливості. 5 ФОРМУЛА КОРИСНОЇ МОДЕЛІ 10 15 20 25 Логічний процесор, що містить шість входів пристрою, вихід пристрою, чотири елементи І, два елементи АБО, який відрізняється тим, що містить мультиплексор із трьома адресними входами й вісьмома інформаційними входами, причому перший вхід пристрою з'єднаний з першими входами першого, другого, третього елементів І, першого та другого елементів АБО, другий вхід пристрою з'єднаний з другими входами першого, другого, елементів І, другого елемента АБО, першими входами першого елемента АБО, четвертого елемента І, третій вхід пристрою з'єднаний з третім входом першого елемента І, другим входом першого елемента АБО, другим входом четвертого елемента І, третім входом другого елемента АБО, вихід першого елемента І з'єднаний з першим інформаційним входом мультиплексора, вихід другого елемента І з'єднаний з другим інформаційним входом мультиплексора, вихід першого елемента АБО з'єднаний з другим входом третього елемента І, вихід четвертого елемента І з'єднаний з другим входом першого елемента АБО, вихід третього елемента І з'єднаний з третім та п'ятим інформаційними входами мультиплексора, вихід першого елемента АБО з'єднаний з четвертим, шостим, сьомим інформаційними входами мультиплексора, вихід другого елемента АБО з'єднаний з восьмим інформаційним входом мультиплексора, четвертий вхід пристрою з'єднаний з першим адресним входом мультиплексора, п'ятий вхід пристрою з'єднаний з другим адресним входом мультиплексора, шостий вхід пристрою з'єднаний з третім адресним входом мультиплексора, вихід мультиплексора з'єднаний з виходом пристрою. 2 UA 107519 U Комп’ютерна верстка Г. Паяльніков Державна служба інтелектуальної власності України, вул. Урицького, 45, м. Київ, МСП, 03680, Україна ДП “Український інститут промислової власності”, вул. Глазунова, 1, м. Київ – 42, 01601 3

ДивитисяДодаткова інформація

МПК / Мітки

МПК: G06F 7/00

Код посилання

<a href="https://ua.patents.su/5-107519-logichnijj-procesor.html" target="_blank" rel="follow" title="База патентів України">Логічний процесор</a>

Попередній патент: Інформаційна система

Наступний патент: Інформаційно-діагностична система

Випадковий патент: Похідні гетероциклічних оксимів, спосіб їх одержання (варіанти), фармацевтична композиція, яка їх містить, проміжна сполука