Оптимізуючий процесор

Номер патенту: 119493

Опубліковано: 25.09.2017

Автори: Губка Сергій Олексійович, Федорович Олег Євгенович, Дергачов Володимир Андрійович

Формула / Реферат

Оптимізуючий процесор, що містить шину вихідних даних, вхід запуску, шину результату, пристрій для керування, блок генерації варіантів тотожних графів, формувач псевдорозкладів, аналізатор реалізованості розкладу, вихід готовності даних, елемент АБО, блок обчислення тривалості процесу, причому вхід запуску з'єднаний з першим входом пристрою для керування, виходи якого з'єднані з першою групою входів блока генерації варіантів тотожних графів, шина вихідних даних з'єднана з другою групою входів блока генерації варіантів тотожних графів, виходи блока генерації варіантів тотожних графів з'єднані з першою групою входів формувача псевдорозкладів, виходи якого з'єднані з входами аналізатора реалізованості розкладу та входами блока обчислення тривалості процесу, виходи аналізатора реалізованості розкладу з'єднані з вхідною шиною пристрою для керування, входами елемента АБО та з другою групою входів формувача псевдорозкладів, вихід елемента АБО з'єднаний з другим входом пристрою для керування та виходом готовності даних, який відрізняється тим, що має схему порівняння, комутатор, другу шину даних, причому виходи формувача псевдорозкладів з'єднані з входами комутатора, виходи якого з'єднані з шиною результату, виходи блока обчислення тривалості процесу з'єднані з першою групою схеми порівняння, друга шина даних з'єднана з другою групою входів схеми порівняння, вихід якої з'єднаний з керуючим входом комутатора та третім входом пристрою для керування.

Текст

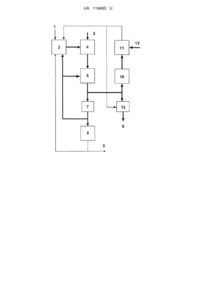

Реферат: Оптимізуючий процесор містить шину вихідних даних, вхід запуску, шину результату, пристрій для керування, блок генерації варіантів тотожних графів, формувач псевдорозкладів, аналізатор реалізованості розкладу, вихід готовності даних, елемент АБО, блок обчислення тривалості процесу. При цьому вхід запуску з'єднаний з першим входом пристрою для керування, виходи якого з'єднані з першою групою входів блока генерації варіантів тотожних графів. Шина вихідних даних з'єднана з другою групою входів блока генерації варіантів тотожних графів. Виходи блока генерації варіантів тотожних графів з'єднані з першою групою входів формувача псевдорозкладів, виходи якого з'єднані з входами аналізатора реалізованості розкладу та входами блока обчислення тривалості процесу. Виходи аналізатора реалізованості розкладу з'єднані з вхідною шиною пристрою для керування, входами елемента АБО та з другою групою входів формувача псевдорозкладів. Вихід елемента АБО з'єднаний з другим входом пристрою для керування та виходом готовності даних. Має схему порівняння, комутатор, другу шину даних, причому виходи формувача псевдорозкладів з'єднані з входами комутатора, виходи якого з'єднані з шиною результату. Виходи блока обчислення тривалості процесу з'єднані з першою групою схеми порівняння. Друга шина даних з'єднана з другою групою входів схеми порівняння, вихід якої з'єднаний з керуючим входом комутатора та третім входом пристрою для керування. UA 119493 U (54) ОПТИМІЗУЮЧИЙ ПРОЦЕСОР UA 119493 U UA 119493 U 5 10 15 20 25 30 35 40 45 50 55 60 Корисна модель належить до автоматики та обчислювальної техніки та призначена для рішення задач теорії розкладів і може бути використана в спеціалізованих обчислювальних пристроях автоматизованих систем керування технологічними процесами і систем автоматизованого проектування, для апаратного рішення задач теорії розкладів. Відомий пристрій для рішення задач теорії розкладів [а.с. СРСР № 1832296, кл. G06F 15/20, опубл. 1993, бюл. № 29], що містить шину вихідних даних, вхід запуску, шину результату, пристрій керування. Недоліком відомого пристрою є обмежені функціональні можливості. Відомий оптимізуючий процесор [патент України № 60102, G06F 15/00, опубл. 15.09.2003, бюл. № 9], що містить шину вихідних даних, вхід запуску, шину результату, пристрій керування, блок генерації варіантів тотожних графів, формувач псевдорозкладів, аналізатор реалізованості розкладу, вихід готовності даних, елемент АБО. Недоліком відомого пристрою є обмежені функціональні можливості. Найбільш близьким по технічній суті і результату, що досягається є оптимізуючий процесор [патент України № 58104, G06F 15/00, заявл. 15.11.2010, опубл. 25.03.2011, бюл. № 6], що містить шину вихідних даних, вхід запуску, шину результату, пристрій керування, блок генерації варіантів тотожних графів, формувач псевдорозкладів, аналізатор реалізованості розкладу, вихід готовності даних, елемент АБО, блок обчислення тривалості процесу, причому вхід запуску з'єднаний з першим входом пристрою керування, виходи якого з'єднані з першою групою входів блока генерації варіантів тотожних графів, шина вихідних даних з'єднана з другою групою входів блока генерації варіантів тотожних графів, виходи блока генерації варіантів тотожних графів з'єднані з першою групою входів формувача псевдорозкладів, виходи якого з'єднані з входами аналізатора реалізованості розкладу та входами блока обчислення тривалості процесу, виходи аналізатора реалізованості розкладу з'єднані з вхідною шиною пристрою керування, входами елемента АБО та з другою групою входів формувача псевдорозкладів, вихід елемента АБО з'єднаний з другим входом пристрою керування та виходом готовності даних. Недоліком відомого пристрою є обмежені функціональні можливості. В основу корисної моделі поставлено задачу удосконалення оптимізуючого процесора шляхом введення нового складу елементів та нової організації взаємозв'язків між ними, при цьому забезпечити ширші функціональні можливості. Поставлена задача вирішується тим, що оптимізуючий процесор, що містить шину вихідних даних, вхід запуску, шину результату, пристрій для керування, блок генерації варіантів тотожних графів, формувач псевдорозкладів, аналізатор реалізованості розкладу, вихід готовності даних, елемент АБО, блок обчислення тривалості процесу, причому вхід запуску з'єднаний з першим входом пристрою для керування, виходи якого з'єднані з першою групою входів блока генерації варіантів тотожних графів, шина вихідних даних з'єднана з другою групою входів блока генерації варіантів тотожних графів, виходи блока генерації варіантів тотожних графів з'єднані з першою групою входів формувача псевдорозкладів, виходи якого з'єднані з входами аналізатора реалізованості розкладу та входами блока обчислення тривалості процесу, виходи аналізатора реалізованості розкладу з'єднані з вхідною шиною пристрою для керування, входами елемента АБО та з другою групою входів формувача псевдорозкладів, вихід елемента АБО з'єднаний з другим входом пристрою для керування та виходом готовності даних, згідно з корисною моделлю має схему порівняння, комутатор, другу шину даних, причому виходи формувача псевдорозкладів з'єднані з входами комутатора, виходи якого з'єднані з шиною результату, виходи блока обчислення тривалості процесу з'єднані з першою групою схеми порівняння, друга шина даних з'єднана з другою групою входів схеми порівняння, вихід якої з'єднаний з керуючим входом комутатора та третім входом пристрою для керування. Заявлений оптимізуючий процесор має новий склад елементів та нову організацію взаємозв'язків між ними, тобто містить нову сукупність ознак, які забезпечують нові технічні властивості пристрою. Технічний результат, як наслідок цих властивостей, - розширені функціональні можливості, спроможність відбору рішень з заданою тривалістю процесу. На кресленні представлена функціональна схема оптимізуючого процесора, який містить вхід запуску 1, шину вихідних даних 2, пристрій для керування 3, блок генерації варіантів тотожних графів 4, формувач псевдорозкладів 5, шину результату 6, аналізатор реалізованої розкладу 7, елемент АБО 8, вихід готовності даних 9, блок 10 обчислення тривалості процесу, схему порівняння 11, комутатор 12, другу шину даних 13, причому вхід запуску 1 з'єднаний з першим входом пристрою для керування 3, виходи якого з'єднані з першою групою входів блока генерації варіантів тотожних графів 4, шина вихідних даних з'єднана з другою групою входів блока генерації варіантів тотожних графів 4, виходи блока генерації варіантів тотожних графів 4 1 UA 119493 U 5 10 15 20 25 з'єднані з першою групою входів формувача псевдорозкладів 5, виходи якого з'єднані з входами аналізатора реалізованості розкладу 7 та входами блока обчислення тривалості процесу 10, виходи аналізатора реалізованості розкладу 7 з'єднані з вхідною шиною пристрою для керування 3, входами елемента АБО 8 та з другою групою входів формувача псевдорозкладів 5, вихід елемента АБО 8 з'єднаний з другим входом пристрою для керування 3 та виходом готовності даних 9, виходи формувача псевдорозкладів 5 з'єднані з входами комутатора 12, виходи якого з'єднані з шиною результату 6, виходи блока обчислення тривалості процесу 10 з'єднані з першою групою схеми порівняння 11, друга шина даних 13 з'єднана з другою групою входів схеми порівняння 11, вихід якої з'єднаний з керуючим входом комутатора 12 та третім входом пристрою для керування 3. Пристрій працює в такий спосіб. На шину вихідних даних 2 подаються характеристики просторово-часових графів, для яких потрібно побудувати розклад. На другу шину даних 13 подається значення допустимої тривалості процесу. На вхід запуску подається сигнал запуску. Блок генерації варіантів тотожних графів 4 згідно з сигналами пристрою для керування 3 формує варіант просторовочасових графів, тотожних заданим. Формувач псевдорозкладів 5 формує псевдорозклад у вигляді композиції тотожних просторово-часових графів. Аналізатор реалізованості розкладу 7 проводить перевірки реалізованості псевдорозкладу та формує множину результатів по кожній. Якщо перевірка виконується, то відповідне значення "0", у противному разі "1". Таким чином, псевдорозклад є розкладом, якщо усі перевірки виконуються, тобто сигнал на виході елемента АБО 8 (і відповідно на виході готовності даних 9) "0" і на шині 6 - результат. Якщо перевірки не виконуються, то на виході елемента АБО 8 сигнал "1" і пристрій для керування 3 подає відповідні сигнали на блок генерації варіантів тотожних графів і вказаний процес повторюється. Псевдорозклади формуються з урахуванням результатів перевірок. Блок 10 обчислює загальну тривалість процесу, значення якої порівнюється зі значенням допустимої тривалості процесу схемою порівняння 11. Якщо загальна тривалість процесу не перевищує значення допустимої тривалості процесу, то схема порівняння 11 формує сигнал "1", який надходить на третій вхід пристрою для керування 3 (закінчує процес рішення) та на керуючий вхід комутатора 12 і на шину результату передається результат. 30 ФОРМУЛА КОРИСНОЇ МОДЕЛІ 35 40 45 Оптимізуючий процесор, що містить шину вихідних даних, вхід запуску, шину результату, пристрій для керування, блок генерації варіантів тотожних графів, формувач псевдорозкладів, аналізатор реалізованості розкладу, вихід готовності даних, елемент АБО, блок обчислення тривалості процесу, причому вхід запуску з'єднаний з першим входом пристрою для керування, виходи якого з'єднані з першою групою входів блока генерації варіантів тотожних графів, шина вихідних даних з'єднана з другою групою входів блока генерації варіантів тотожних графів, виходи блока генерації варіантів тотожних графів з'єднані з першою групою входів формувача псевдорозкладів, виходи якого з'єднані з входами аналізатора реалізованості розкладу та входами блока обчислення тривалості процесу, виходи аналізатора реалізованості розкладу з'єднані з вхідною шиною пристрою для керування, входами елемента АБО та з другою групою входів формувача псевдорозкладів, вихід елемента АБО з'єднаний з другим входом пристрою для керування та виходом готовності даних, який відрізняється тим, що має схему порівняння, комутатор, другу шину даних, причому виходи формувача псевдорозкладів з'єднані з входами комутатора, виходи якого з'єднані з шиною результату, виходи блока обчислення тривалості процесу з'єднані з першою групою схеми порівняння, друга шина даних з'єднана з другою групою входів схеми порівняння, вихід якої з'єднаний з керуючим входом комутатора та третім входом пристрою для керування. 2 UA 119493 U Комп’ютерна верстка А. Крижанівський Міністерство економічного розвитку і торгівлі України, вул. М. Грушевського, 12/2, м. Київ, 01008, Україна ДП “Український інститут інтелектуальної власності”, вул. Глазунова, 1, м. Київ – 42, 01601 3

ДивитисяДодаткова інформація

МПК / Мітки

МПК: G06F 15/00

Мітки: процесор, оптимізуючий

Код посилання

<a href="https://ua.patents.su/5-119493-optimizuyuchijj-procesor.html" target="_blank" rel="follow" title="База патентів України">Оптимізуючий процесор</a>