Адаптивний діагностичний процесор

Номер патенту: 109772

Опубліковано: 12.09.2016

Автори: Савельєв Анатолій Семенович, Дергачов Володимир Андрійович, Павлик Ганна Володимирівна, Цеховський Максим Володимирович

Формула / Реферат

Адаптивний діагностичний процесор, що містить групу інформаційних входів, блок пам'яті, двійковий лічильник, схему порівняння, елемент І, генератор, керуючий вхід, вихідну шину, другий та третій блоки пам'яті, другу та третю схеми порівняння, елемент АБО, демультиплексор, блок тригерів, мультиплексор, причому керуючий вхід з'єднаний з першим входом елемента І, вихід генератора з'єднаний з другим входом елемента І, вихід якого з'єднаний з рахунковим входом двійкового лічильника, виходи двійкового лічильника з'єднані з першою групою входів блока пам'яті, група інформаційних входів з'єднана з відповідними інформаційними входами мультиплексора, виходи першого блока пам'яті з'єднані з адресними входами мультиплексора, з адресними входами другого блока пам'яті та з адресними входами демультиплексора, виходи мультиплексора з'єднані з першою групою входів другої схеми порівняння та з першою групою входів третьої схеми порівняння, перша група виходів другого блока пам'яті з'єднана з другою групою входів другої схеми порівняння, друга група виходів блока пам'яті з'єднана з другою групою входів третьої схеми порівняння, вихід другої схеми порівняння з'єднаний з першим входом елемента АБО, вихід третьої схеми порівняння з'єднаний з другим входом елемента АБО, вихід якого з'єднаний з інформаційним входом демультиплексора, виходи якого з'єднані з відповідними входами блока тригерів, виходи блока тригерів з'єднані з вихідною шиною, з другою групою адресних входів першого блока пам'яті та з адресними входами третього блока пам'яті, виходи третього блока пам'яті з'єднані з першою групою входів першої схеми порівняння, вихід якої з'єднаний з входом "Скид" двійкового лічильника, виходи якого з'єднані з другою групою входів першої схеми порівняння, який відрізняється тим, що має другий демультиплексор, другий блок тригерів, другу вихідну шину, причому вихід третьої схеми порівняння з'єднаний з інформаційним входом другого мультиплексора, виходи першого блока пам'яті з'єднані з адресними входами другого мультиплексора, виходи якого з'єднані з відповідними входами другого блока тригерів, виходи другого блока тригерів з'єднані з другою вихідною шиною.

Текст

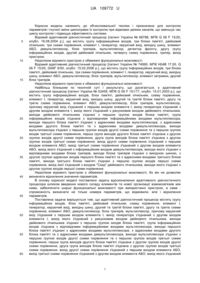

Реферат: Адаптивний діагностичний процесор містить групу інформаційних входів, блок пам'яті, двійковий лічильник, схему порівняння, елемент І, генератор, керуючий вхід, вихідну шину, другий та третій блоки пам'яті, другу та третю схеми порівняння, елемент АБО, демультиплексор, блок тригерів, мультиплексор, причому керуючий вхід з'єднаний з першим входом елемента І, вихід генератора з'єднаний з другим входом елемента І, вихід якого з'єднаний з рахунковим входом двійкового лічильника, виходи двійкового лічильника з'єднані з першою групою входів блока пам'яті, група інформаційних входів з'єднана з відповідними інформаційними входами мультиплексора, виходи першого блока пам'яті з'єднані з адресними входами мультиплексора, з адресними входами другого блока пам'яті та з адресними входами демультиплексора, виходи мультиплексора з'єднані з першою групою входів другої схеми порівняння та з першою групою входів третьої схеми порівняння, перша група виходів другого блока пам'яті з'єднана з другою групою входів другої схеми порівняння, друга група виходів блока пам'яті з'єднана з другою групою входів третьої схеми порівняння, вихід другої схеми порівняння з'єднаний з першим входом елемента АБО, вихід третьої схеми порівняння з'єднаний з другим входом елемента АБО, вихід якого з'єднаний з інформаційним входом демультиплексора, виходи якого з'єднані з відповідними входами блока тригерів, виходи блока тригерів з'єднані з вихідною шиною, з другою групою адресних входів першого блока пам'яті та з адресними входами третього блока пам'яті, виходи третього блока пам'яті з'єднані з першою групою входів першої схеми порівняння, вихід якої з'єднаний з входом "Скид" двійкового лічильника, виходи якого з'єднані з другою групою входів першої схеми порівняння, причому має другий демультиплексор, другий блок тригерів, другу вихідну шину, причому вихід третьої схеми порівняння з'єднаний з інформаційним входом другого мультиплексора, виходи першого блока пам'яті з'єднані з адресними входами другого мультиплексора, виходи якого з'єднані з відповідними входами другого блока тригерів, виходи другого блока тригерів з'єднані з другою вихідною шиною. UA 109772 U (12) UA 109772 U UA 109772 U 5 10 15 20 25 30 35 40 45 50 55 60 Корисна модель належить до обчислювальної техніки і призначена для контролю параметрів і гнучкої зміни циклограми їх контролю при відмовах деяких каналів, що зменшує час циклу контролю і підвищує ефективність системи. Відомий адаптивний діагностичний процесор [патент України № 68788, МПК G 06 F 15/20, опубл. 16.08.2004 р.], що містить групу інформаційних входів, три блоки пам'яті, двійковий лічильник, три схеми порівняння, елемент І, генератор, керуючий вхід, вихідну шину, елемент АБО, демультиплексор, блок тригерів, мультиплексор, детектор фронту, другу групу інформаційних входів, другий двійковий лічильник, четверту схему порівняння, тригер, вихід пристрою. Недоліком відомого пристрою є обмежені функціональні можливості. Відомий адаптивний діагностичний процесор [патент України № 74995, МПК Н04В 17.00, G 06 F 15/20, G06F 9/00, опубл. 15.02.2006 р.], що містить групу Інформаційних входів, три блоки пам'яті, двійковий лічильник, три схеми порівняння, елемент І, генератор, керуючий вхід, вихідну шину, елемент АБО, демультиплексор, блок тригерів, мультиплексор, елемент затримки, другий блок тригерів. Недоліком відомого пристрою є обмежені функціональні можливості. Найбільш близьким по технічній суті і результату, що досягається, є адаптивний діагностичний процесор [патент України № 53459, МПК G 06 F 15/177, опубл. 15.01.2003 р.], що містить групу інформаційних входів, блок пам'яті, двійковий лічильник, схему порівняння, елемент І, генератор, керуючий вхід, вихідну шину, другий та третій блоки пам'яті, другу та третю схеми порівняння, елемент АБО, демультиплексор, блок тригерів, мультиплексор, причому керуючий вхід з'єднаний з першим входом елемента І, вихід генератора з'єднаний з другим входом елемента І, вихід якого з'єднаний з рахунковим входом двійкового лічильника, виходи двійкового лічильника з'єднані з першою групою входів блока пам'яті, група інформаційних входів з'єднана з відповідними інформаційними входами мультиплексора, виходи першого блока пам'яті з'єднані з адресними входами мультиплексора, з адресними входами другого блока пам'яті та з адресними входами демультиплексора, виходи мультиплексора з'єднані з першою групою входів другої схеми порівняння та з першою групою входів третьої схеми порівняння, перша група виходів другого блока пам'яті з'єднана з другою групою входів другої схеми порівняння, друга група виходів блока пам'яті з'єднана з другою групою входів третьої схеми порівняння, вихід другої схеми порівняння з'єднаний з першим входом елемента АБО, вихід третьої схеми порівняння з'єднаний з другим входом елемента АБО, вихід якого з'єднаний з інформаційним входом демультиплексора, виходи якого з'єднані з відповідними входами блока тригерів, виходи блока тригерів з'єднані з вихідною шиною, з другою групою адресних входів першого блока пам'яті та з адресними входами третього блока пам'яті, виходи третього блока пам'яті з'єднані з першою групою входів першої схеми порівняння, вихід якої з'єднаний з входом "Скид" двійкового лічильника, виходи якого з'єднані з другою групою входів першої схеми порівняння. Недоліком відомого пристрою є обмежені функціональні можливості, бо він не дозволяє визначати відхилення значення параметрів. В основу корисної моделі поставлено задачу вдосконалення адаптивного діагностичного процесора шляхом введення нового складу елементів та нової організації взаємозв'язків між ними, забезпечити ширші функціональні можливості при використанні пристрою, а саме спроможність визначати не тільки номера параметрів, що відмовили, але і відхилення параметрів. Поставлена задача вирішується тим, що адаптивний діагностичний процесор містить групу інформаційних входів, блок пам'яті, двійковий лічильник, схему порівняння, елемент І, генератор, керуючий вхід, вихідну шину, другий та третій блоки пам'яті, другу та третю схеми порівняння, елемент АБО, демультиплексор, блок тригерів, мультиплексор, причому керуючий вхід з'єднаний з першим входом елемента І, вихід генератора з'єднаний з другим входом елемента І, вихід якого з'єднаний з рахунковим входом двійкового лічильника, виходи двійкового лічильника з'єднані з першою групою входів блока пам'яті, група інформаційних входів з'єднана з відповідними інформаційними входами мультиплексора, виходи першого блока пам'яті з'єднані з адресними входами мультиплексора, з адресними входами другого блока пам'яті та з адресними входами демультиплексора, виходи мультиплексора з'єднані з першою групою входів другої схеми порівняння та з першою групою входів третьої схеми порівняння, перша група виходів другого блока пам'яті з'єднана з другою групою входів другої схеми порівняння, друга група виходів блока пам'яті з'єднана з другою групою входів третьої схеми порівняння, вихід другої схеми порівняння з'єднаний з першим входом елемента АБО, вихід третьої схеми порівняння з'єднаний з другим входом елемента АБО, вихід якого з'єднаний 1 UA 109772 U 5 10 15 20 25 30 35 40 45 50 55 60 з інформаційним входом демультиплексора, виходи якого з'єднані з відповідними входами блока тригерів, виходи блока тригерів з'єднані з вихідною шиною, з другою групою адресних входів першого блока пам'яті та з адресними входами третього блока пам'яті, виходи третього блока пам'яті з'єднані з першою групою входів першої схеми порівняння, вихід якої з'єднаний з входом "Скид" двійкового лічильника, виходи якого з'єднані з другою групою входів першої схеми порівняння, згідно з корисною моделлю містить другий демультиплексор, другий блок тригерів, другу вихідну шину, причому вихід третьої схеми порівняння з'єднаний з інформаційним входом другого мультиплексора, виходи першого блока пам'яті з'єднані з адресними входами другого мультиплексора, виходи якого з'єднані з відповідними входами другого блока тригерів, виходи другого блока тригерів з'єднані з другою вихідною шиною. Заявлений пристрій має новий склад елементів та нову організацію взаємозв'язків між ними, тобто містить нову сукупність ознак, які забезпечують нові технічні властивості пристрою. Технічний результат, як наслідок цих властивостей - ширші функціональні можливості при використанні пристрою, а саме - спроможність визначати не тільки номера параметрів, що відмовили, але і відхилення параметрів. На кресленні представлена функціональна схема адаптивного діагностичного процесора. Адаптивний діагностичний процесор містить групу інформаційних входів 1 і (і=1…n), вихідну шину 2, керуючий вхід 3, елемент І 4, генератор 5, двійковий лічильник 6, перший блок пам'яті 7, другий блок пам'яті 8, третій блок пам'яті 9, першу схему порівняння 10, другу схему порівняння 11, третю схему порівняння 12, елемент АБО 13, демультиплексор 14, блок тригерів 15, мультиплексор 16, другий демультиплексор 17, другий блок тригерів 18, другу вихідну шину 19, причому керуючий вхід 3 з'єднаний з першим входом елемента І 4, вихід генератора 5 з'єднаний з другим входом елемента І 4, вихід якого з'єднаний з рахунковим входом двійкового лічильника 6, виходи двійкового лічильника 6 з'єднані з першою групою входів блока пам'яті 7, другий та третій блоки пам'яті 8, 9, другу та третю схеми порівняння 11, 12, група інформаційних входів lі (i=1…n) з'єднана з відповідними інформаційними входами мультиплексора 16, виходи першого блока пам'яті 7 з'єднані з адресними входами мультиплексора 16, з адресними входами другого блока пам'яті 8 та з адресними входами демультиплексора 14, виходи мультиплексора 16 з'єднані з першою групою входів другої схеми порівняння 11 та з першою групою входів третьої схеми порівняння 12, перша група виходів другого блока пам'яті 8 з'єднана з другою групою входів другої схеми порівняння 11, друга група виходів блока пам'яті 8 з'єднана з другою групою входів третьої схеми порівняння 12, вихід другої схеми порівняння 11 з'єднаний з першим входом елемента АБО 13, вихід третьої схеми порівняння 12 з'єднаний з другим входом елемента АБО 13, вихід якого з'єднаний з інформаційним входом демультиплексора 14, виходи якого з'єднані з відповідними входами блока тригерів 15, виходи блока тригерів 15 з'єднані з вихідною шиною 2, з другою групою адресних входів першого блока пам'яті 7 та з адресними входами третього блока пам'яті 9, виходи третього блока пам'яті 9 з'єднані з першою групою входів першої схеми порівняння 10, вихід якої з'єднаний з входом "Скид" двійкового лічильника 6, виходи якого з'єднані з другою групою входів першої схеми порівняння 10, вихід третьої схеми порівняння 12 з'єднаний з інформаційним входом другого мультиплексора 17, виходи першого блока пам'яті 7 з'єднані з адресними входами другого мультиплексора 17, виходи якого з'єднані з відповідними входами другого блока тригерів 18, виходи другого блока тригерів 18 з'єднані з другою вихідною шиною 19. Працює адаптивний діагностичний процесор таким чином. Спочатку всі елементи пам'яті схеми пристрою знаходяться у стані "0". На інформаційні входи 1 надходять значення інформаційних сигналів. У блоці пам'яті 7 записані послідовності опитування каналів в залежності від відмов каналів. У блоці пам'яті 8 записані допускові значення відповідних параметрів. У блоці пам'яті 9 записані двійкові коди довжини циклу опитування для відповідної кількості каналів, що відмовили. При подачі сигнала "1" на керуючий вхід 3 імпульси з виходу генератора 5 надходять на другий вхід елемента І 4 та проходять на рахунковий вхід двійкового лічильника 6, змінюючи його стан. Двійковий код на виходах двійкового лічильника 6 та двійковий код на виходах блока тригерів є адресними входами блока пам'яті 7 і на його виходах формується відповідний двійковий код адреси мультиплексора 16. Сигнали з виходу мультиплексора 16 подаються на перші групи входів схеми порівняння 11 та схеми порівняння 12. На другі групи входів цих схем порівняння подаються з блока пам'яті 8 відповідні допускові значення. Якщо значення параметра, що контролюється, виходять за межі, то на виході елемента АБО 13 формується сигнал "1", який через демультиплексор 14 записується у відповідний тригер, що входить у блок тригерів 15. При цьому на блоки пам'яті 7 та 9 подаються нові двійкові коди і вибирається нова програма контролю (у блоці 7) та відповідна довжина циклу (у блоці 9). Якщо під час циклу контролю не було відмов, то на виході 2 UA 109772 U 5 10 15 20 25 30 35 схеми порівняння 10 формується одиничний сигнал, який переводить двійковий лічильник 6 у початковий стан і процес повторюється. Якщо значення параметра, що контролюється, виходять за межі, то на виході третьої схеми порівняння 12 формується сигнал "1", який через демультиплексор 17 записується у відповідний тригер, що входить у блок тригерів 18, та видається на вихідну шину 19. Таким чином, заявлений адаптивний діагностичний процесор проводить контроль параметрів і гнучко змінює циклограму контролю при відмовах деяких каналів, при цьому видає інформацію про номера параметрів, що відмовили, але і відхилення їх параметрів. ФОРМУЛА КОРИСНОЇ МОДЕЛІ Адаптивний діагностичний процесор, що містить групу інформаційних входів, блок пам'яті, двійковий лічильник, схему порівняння, елемент І, генератор, керуючий вхід, вихідну шину, другий та третій блоки пам'яті, другу та третю схеми порівняння, елемент АБО, демультиплексор, блок тригерів, мультиплексор, причому керуючий вхід з'єднаний з першим входом елемента І, вихід генератора з'єднаний з другим входом елемента І, вихід якого з'єднаний з рахунковим входом двійкового лічильника, виходи двійкового лічильника з'єднані з першою групою входів блока пам'яті, група інформаційних входів з'єднана з відповідними інформаційними входами мультиплексора, виходи першого блока пам'яті з'єднані з адресними входами мультиплексора, з адресними входами другого блока пам'яті та з адресними входами демультиплексора, виходи мультиплексора з'єднані з першою групою входів другої схеми порівняння та з першою групою входів третьої схеми порівняння, перша група виходів другого блока пам'яті з'єднана з другою групою входів другої схеми порівняння, друга група виходів блока пам'яті з'єднана з другою групою входів третьої схеми порівняння, вихід другої схеми порівняння з'єднаний з першим входом елемента АБО, вихід третьої схеми порівняння з'єднаний з другим входом елемента АБО, вихід якого з'єднаний з інформаційним входом демультиплексора, виходи якого з'єднані з відповідними входами блока тригерів, виходи блока тригерів з'єднані з вихідною шиною, з другою групою адресних входів першого блока пам'яті та з адресними входами третього блока пам'яті, виходи третього блока пам'яті з'єднані з першою групою входів першої схеми порівняння, вихід якої з'єднаний з входом "Скид" двійкового лічильника, виходи якого з'єднані з другою групою входів першої схеми порівняння, який відрізняється тим, що має другий демультиплексор, другий блок тригерів, другу вихідну шину, причому вихід третьої схеми порівняння з'єднаний з інформаційним входом другого мультиплексора, виходи першого блока пам'яті з'єднані з адресними входами другого мультиплексора, виходи якого з'єднані з відповідними входами другого блока тригерів, виходи другого блока тригерів з'єднані з другою вихідною шиною. 3 UA 109772 U Комп’ютерна верстка Г. Паяльніков Державна служба інтелектуальної власності України, вул. Урицького, 45, м. Київ, МСП, 03680, Україна ДП “Український інститут промислової власності”, вул. Глазунова, 1, м. Київ – 42, 01601 4

ДивитисяДодаткова інформація

МПК / Мітки

МПК: G06F 15/00

Мітки: діагностичний, процесор, адаптивний

Код посилання

<a href="https://ua.patents.su/6-109772-adaptivnijj-diagnostichnijj-procesor.html" target="_blank" rel="follow" title="База патентів України">Адаптивний діагностичний процесор</a>

Попередній патент: Функціональний перетворювач

Наступний патент: Каретка фурменого пристрою з уловлювачем

Випадковий патент: Гідровузол сироти