Аналізатор реалізованості процесу

Номер патенту: 119815

Опубліковано: 10.10.2017

Автори: Губка Сергій Олексійович, Дергачов Володимир Андрійович, Федорович Олег Євгенович

Формула / Реферат

Аналізатор реалізованості процесу, що містить керуючий вхід, генератор імпульсів, два елементи "І", двійковий лічильник, тригер, два блоки пам'яті, три схеми порівняння, арифметичний пристрій, регістр, дешифратор, три шини даних, шину результату, причому вихід генератора з'єднаний з першим входом першого елемента "І", керуючий вхід з'єднаний з одиничним входом тригера, вихід тригера з'єднаний із другим входом першого елемента "І", вихід якого з'єднаний з рахунковим входом двійкового лічильника, перша шина даних з'єднана з першою групою входів першої схеми порівняння, вихід якої з'єднаний з нульовим входом тригера, виходи дешифратора з'єднані з входами регістра, виходи якого з'єднані із шиною результату, виходи першого блока пам'яті з'єднані з першою групою входів арифметичного пристрою, виходи якого з'єднані з першою групою входів третьої схеми порівняння, виходи другого блока пам'яті з'єднані з першою групою входів другої схеми порівняння, друга шина даних з'єднана з другою групою входів другої схеми порівняння і з другою групою входів арифметичного пристрою, третя шина даних з'єднана з другою групою третьої схеми порівняння, виходи другої схеми порівняння та виходи третьої схеми порівняння з'єднані з входами другого елемента "І", вихід якого з'єднаний з керуючим входом регістра, який відрізняється тим, що має четверту шину даних, вихід готовності результату, функціональний аналізатор, причому виходи двійкового лічильника з'єднані з першою групою входів функціонального аналізатора, четверта шина даних з'єднана з другою групою входів функціонального аналізатора, виходи якого з'єднані з входами першого блока пам'яті та другого блока пам'яті, входами дешифратора та другою групою входів першої схеми порівняння, вихід тригера з’єднаний з виходом готовності результату.

Текст

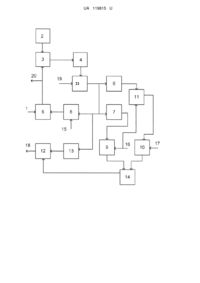

Реферат: Аналізатор реалізованості процесу містить керуючий вхід, генератор імпульсів, два елементи "І", двійковий лічильник, тригер, два блоки пам'яті, три схеми порівняння, арифметичний пристрій, регістр, дешифратор, чотири шини даних, шину результату, функціональний аналізатор. UA 119815 U (54) АНАЛІЗАТОР РЕАЛІЗОВАНОСТІ ПРОЦЕСУ UA 119815 U UA 119815 U 5 10 15 20 25 30 35 40 45 50 55 Корисна модель належить до автоматики та обчислювальної техніки, призначена для аналізу реалізованості процесів і може бути використана в спеціалізованих обчислювальних пристроях автоматизованих систем керування технологічними процесами і систем автоматизованого проектування, для апаратного рішення задач теорії розкладів. Відомий пристрій для моделювання процесу передачі інформації [патент України № 23270 А, G06F 15/20, опубл. 31.08.98, бюл. № 4], що містить керуючий вхід, генератор, елемент "І", двійковий лічильник, блок пам'яті, тригер, дешифратор, регістр, шину результату, причому вихід генератора з'єднаний з першим входом першого елемента "І", керуючий вхід з'єднаний з одиничним входом тригера, вихід тригера з'єднаний із другим входом першого елемента "І", вихід якого з'єднаний з рахунковим входом двійкового лічильника, виходи двійкового лічильника з'єднані з входами блока пам'яті. Недоліком відомого пристрою є обмежені функціональні можливості. Найбільш близьким по технічній суті і результату, що досягається, є аналізатор реалізованості процесу [патент України № 62167 А, G06F 15/16, опубл. 15.12.2003, бюл. № 12, 2003 р, автори Федорович О.Є., Губка О.С.], що містить керуючий вхід, генератор імпульсів, два елементи "І", двійковий лічильник, тригер, два блоки пам'яті, три схеми порівняння, арифметичний пристрій, регістр, дешифратор, три шини даних, шину результату, причому вихід генератора з'єднаний з першим входом першого елемента "І", керуючий вхід з'єднаний з одиничним входом тригера, вихід тригера з'єднаний із другим входом першого елемента "І", вихід якого з'єднаний з рахунковим входом двійкового лічильника, перша шина даних з'єднана з першою групою входів першої схеми порівняння, вихід якої з'єднаний з нульовим входом тригера, виходи дешифратора з'єднані з входами регістра, виходи якого з'єднані із шиною результату, виходи першого блока пам'яті з'єднані з першою групою входів арифметичного пристрою, виходи якого з'єднані з першою групою входів третьої схеми порівняння, виходи другого блока пам'яті з'єднані з першою групою входів другої схеми порівняння, друга шина даних з'єднана з другою групою входів другої схеми порівняння і з другою групою входів арифметичного пристрою, третя шина даних з'єднана з другою групою третьої схеми порівняння, виходи другої схеми порівняння та виходи третьої схеми порівняння з'єднані з входами другого елемента "І", вихід якого з'єднаний з керуючим входом регістра. Недоліком відомого пристрою є обмежені функціональні можливості. В основу корисної моделі поставлено задачу створити аналізатор реалізованості процесу шляхом введення нового складу елементів та нової організації взаємозв'язків між ними забезпечити ширші функціональні можливості при використанні корисної моделі, а саме спроможність аналізувати реалізованість процесів. Поставлена задача вирішується тим, що аналізатор реалізованості процесу, що містить керуючий вхід, генератор імпульсів, два елементи "І", двійковий лічильник, тригер, два блоки пам'яті, три схеми порівняння, арифметичний пристрій, регістр, дешифратор, три шини даних, шину результату, причому вихід генератора з'єднаний з першим входом першого елемента "І", керуючий вхід з'єднаний з одиничним входом тригера, вихід тригера з'єднаний із другим входом першого елемента "І", вихід якого з'єднаний з рахунковим входом двійкового лічильника, перша шина даних з'єднана з першою групою входів першої схеми порівняння, вихід якої з'єднаний з нульовим входом тригера, виходи дешифратора з'єднані з входами регістра, виходи якого з'єднані із шиною результату, виходи першого блока пам'яті з'єднані з першою групою входів арифметичного пристрою, виходи якого з'єднані з першою групою входів третьої схеми порівняння, виходи другого блока пам'яті з'єднані з першою групою входів другої схеми порівняння, друга шина даних з'єднана з другою групою входів другої схеми порівняння і з другою групою входів арифметичного пристрою, третя шина даних з'єднана з другою групою третьої схеми порівняння, виходи другої схеми порівняння та виходи третьої схеми порівняння з'єднані з входами другого елемента "І", вихід якого з'єднаний з керуючим входом регістра, згідно з корисною моделлю, має четверту шину даних, вихід готовності результату, функціональний аналізатор, причому виходи двійкового лічильника з'єднані з першою групою входів функціонального аналізатора, четверта шина даних з'єднана з другою групою входів функціонального аналізатора, виходи якого з'єднані з входами першого блока пам'яті та другого блока пам'яті, входами дешифратора та другою групою входів першої схеми порівняння, вихід тригера з'єднаний з виходом готовності результату. Заявлений аналізатор реалізованості процесу має новий склад елементів та нову організацію взаємозв'язків між ними, тобто містить нову сукупність ознак, які забезпечують нові технічні властивості корисної моделі. Технічний результат, як наслідок цих властивостей розширені функціональні можливості. 1 UA 119815 U 5 10 15 20 25 30 35 40 На кресленні представлена функціональна схема аналізатора реалізованості процесу. Пристрій містить керуючий вхід 1, генератор імпульсів 2, два елементи "І" 3 та 14, двійковий лічильник 4, тригер 5, два блоки пам'яті 6 та 7, три схеми порівняння 8, 9, 10, арифметичний пристрій 11, регістр 12, дешифратор 13, три шини даних 15, 16, 17, шину результату 18, четверту шину даних 19, вихід готовності результату 20, функціональний аналізатор 21, причому вихід генератора 2 з'єднаний з першим входом першого елемента "І" 3, керуючий вхід 1 з'єднаний з одиничним входом тригера 5, вихід тригера 5 з'єднаний із другим входом першого елемента "І" 3, вихід якого з'єднаний з рахунковим входом двійкового лічильника 4, перша шина даних 15 з'єднана з першою групою входів першої схеми порівняння 8, вихід якої з'єднаний з нульовим входом тригера 5, виходи дешифратора 13 з'єднані з входами регістра 12, виходи якого з'єднані із шиною результату 18, виходи першого блока пам'яті 6 з'єднані з першою групою входів арифметичного пристрою 11, виходи якого з'єднані з першою групою входів третьої схеми порівняння 10, виходи другого блока пам'яті 7 з'єднані з першою групою входів другої схеми порівняння 9, друга шина даних 16 з'єднана з другою групою входів другої схеми порівняння 9 і з другою групою входів арифметичного пристрою 11, третя шина даних 17 з'єднана з другою групою третьої схеми порівняння 10, виходи другої схеми порівняння 9 та виходи третьої схеми порівняння 10 з'єднані з входами другого елемента "І" 14, вихід якого з'єднаний з керуючим входом регістра 12, виходи двійкового лічильника 4 з'єднані з першою групою входів функціонального аналізатора 21, четверта шина даних 19 з'єднана з другою групою входів функціонального аналізатора 21, виходи якого з'єднані з входами першого 6 блока пам'яті та другого блока пам'яті 7, входами дешифратора 13 та другою групою входів першої схеми порівняння 8, вихід тригера 5 з'єднаний з виходом готовності результату 20. Пристрій працює в такий спосіб. У вихідному стані двійковий лічильник 4, тригер 5, регістр 12 знаходяться в нульовому стані. У блоках пам'яті 6 і 7 по адресах з першої по К-ту записана інформація про простій відповідного устаткування (Тк і Тн). На першу шину 15 подається двійковий код числа К. На шини даних 16 і 17 подається інформація про процес, що аналізується: можливий час початку виконання процесу Тв (шина даних 16) і тривалість процесу Д (шина даних 17). На керуючий вхід 1 подається одиничний імпульс для запуску пристрою. При цьому тригер 5 переводиться в стан "1" і відкриває елемент "І" 3. Імпульси з виходу генератора проходять на рахунковий вхід двійкового лічильника 4, послідовно змінюючи його стан. Для кожного стану (який є адресою устаткування) відбувається зчитування з блоків пам'яті 6 і 7 відповідно значень Тн і Тк. Арифметичний пристрій 11 визначає тривалість простою устаткування Дп=Тк-Тв. Схеми порівняння 9 і 10 перевіряють виконання умов ТвТн і ДпД. Якщо умови виконуються, то на виході елемента "І" 14 формується сигнал "1", що відкриває регістр 12 для запису одиничних значень на виходах дешифратора 13. Регістр 12 реалізований на RS тригерах із синхронізацією, причому виходи дешифратора 13 з'єднані з S входами відповідних тригерів, що входять до складу регістра 12. Зазначений процес повторюється для всіх адрес устаткування. По закінченні процесу аналізу схема порівняння 8 формує одиничний сигнал, що переводить тригер 5 у стан "0" і робота пристрою зупиняється. У регістрі 12 зберігається інформація про устаткування, на якому можна реалізувати аналізований процес у відповідному розряді регістра значення "1". ФОРМУЛА КОРИСНОЇ МОДЕЛІ 45 50 55 60 Аналізатор реалізованості процесу, що містить керуючий вхід, генератор імпульсів, два елементи "І", двійковий лічильник, тригер, два блоки пам'яті, три схеми порівняння, арифметичний пристрій, регістр, дешифратор, три шини даних, шину результату, причому вихід генератора з'єднаний з першим входом першого елемента "І", керуючий вхід з'єднаний з одиничним входом тригера, вихід тригера з'єднаний із другим входом першого елемента "І", вихід якого з'єднаний з рахунковим входом двійкового лічильника, перша шина даних з'єднана з першою групою входів першої схеми порівняння, вихід якої з'єднаний з нульовим входом тригера, виходи дешифратора з'єднані з входами регістра, виходи якого з'єднані із шиною результату, виходи першого блока пам'яті з'єднані з першою групою входів арифметичного пристрою, виходи якого з'єднані з першою групою входів третьої схеми порівняння, виходи другого блока пам'яті з'єднані з першою групою входів другої схеми порівняння, друга шина даних з'єднана з другою групою входів другої схеми порівняння і з другою групою входів арифметичного пристрою, третя шина даних з'єднана з другою групою третьої схеми порівняння, виходи другої схеми порівняння та виходи третьої схеми порівняння з'єднані з входами другого елемента "І", вихід якого з'єднаний з керуючим входом регістра, який відрізняється тим, що має четверту шину даних, вихід готовності результату, функціональний 2 UA 119815 U 5 аналізатор, причому виходи двійкового лічильника з'єднані з першою групою входів функціонального аналізатора, четверта шина даних з'єднана з другою групою входів функціонального аналізатора, виходи якого з'єднані з входами першого блока пам'яті та другого блока пам'яті, входами дешифратора та другою групою входів першої схеми порівняння, вихід тригера з’єднаний з виходом готовності результату. Комп’ютерна верстка В. Мацело Міністерство економічного розвитку і торгівлі України, вул. М. Грушевського, 12/2, м. Київ, 01008, Україна ДП “Український інститут інтелектуальної власності”, вул. Глазунова, 1, м. Київ – 42, 01601 3

ДивитисяДодаткова інформація

МПК / Мітки

МПК: G06F 15/16

Мітки: аналізатор, процесу, реалізованості

Код посилання

<a href="https://ua.patents.su/5-119815-analizator-realizovanosti-procesu.html" target="_blank" rel="follow" title="База патентів України">Аналізатор реалізованості процесу</a>

Попередній патент: Віскозиметр

Наступний патент: Спосіб визначення фази хронічного алкогольного, неалкогольного стеатогепатиту та вірусного гепатиту с

Випадковий патент: Спосіб безстічного водопостачання ливарно-прокатного комплексу