Паралельно-послідовний аналого-цифровий перетворювач

Номер патенту: 120057

Опубліковано: 25.10.2017

Автори: Бортник Геннадій Григорович, Бортник Олександр Геннадійович, Васильківський Микола Володимирович

Формула / Реферат

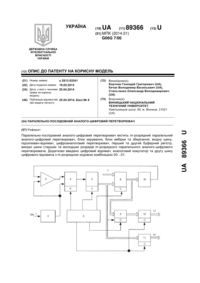

Паралельно-послідовний аналого-цифровий перетворювач, який містить m-розрядний паралельний АЦП старших розрядів, аналоговий вхід якого під'єднано до виходу блока вибірки та зберігання, вхід якого під'єднано до шини джерела вхідного сигналу, який підлягає перетворенню, виходи m-розрядного паралельного АЦП під'єднано до першої вхідної шини буферного регістра, виходи якого є відповідно вихідною розрядною шиною пристрою, перетворювач коду, 2l-1 компараторів, виходи яких під'єднано до відповідних входів перетворювача коду, виходи якого під'єднано до другої вхідної шини буферного регістра, який відрізняється тим, що в нього введено 2l-1 ЦАП з n-розрядними вхідними шинами, причому старші m розряди вхідних шин ЦАП під'єднано до відповідних виходів паралельного АЦП старших розрядів, а на молодших l розрядах вхідних шин ЦАП встановлено відповідні цифрові коди N2, де N2 - двійковий номер кожного з 2l-1 ЦАП, виходи ЦАП під'єднано до відповідних інвертувальних входів 2l-1 компараторів, а неінвертувальні входи яких під'єднано до виходу блока вибірки та зберігання.

Текст

Реферат: Паралельно-послідовний аналого-цифровий перетворювач містить m-розрядний паралельний АЦП старших розрядів, аналоговий вхід якого під'єднано до виходу блока вибірки та зберігання, вхід якого під'єднано до шини джерела вхідного сигналу, який підлягає перетворенню, виходи m-розрядного паралельного АЦП під'єднано до першої вхідної шини буферного регістра, l виходи якого є відповідно вихідною розрядною шиною пристрою, перетворювач коду, 2 -1 компараторів, виходи яких під'єднано до відповідних входів перетворювача коду, виходи якого l під'єднано до другої вхідної шини буферного регістра. Введено 2 -1 ЦАП з n-розрядними вхідними шинами, причому старші m розрядів вхідних шин ЦАП під'єднано до відповідних виходів паралельного АЦП старших розрядів. На молодших l розрядах вхідних шин ЦАП l встановлено відповідні цифрові коди N2, де N2 - двійковий номер кожного з 2 -1 ЦАП, виходи l ЦАП під'єднано до відповідних інвертувальних входів 2 -1 компараторів, а неінвертувальні входи яких під'єднано до виходу блока вибірки та зберігання. UA 120057 U (54) ПАРАЛЕЛЬНО-ПОСЛІДОВНИЙ АНАЛОГО-ЦИФРОВИЙ ПЕРЕТВОРЮВАЧ UA 120057 U UA 120057 U 5 10 15 20 Корисна модель належить до інформаційно-вимірювальної техніки і призначена для спектрометричних вимірювань високої швидкодії в контрольно-вимірювальній техніці, радіолокації, експериментальній фізиці. m-1 Відомий паралельно-послідовний аналого-цифровий перетворювач (АЦП), який містить 2 пристроїв порівняння, де m - кількість розрядів вихідного коду, яка визначається за один вимірювальний такт перетворювача, перші входи яких з'єднані з шиною джерела вхідного сигналу, другі входи - з відповідними виходами резистивного подільника, а виходи з'єднані з цифровими входами блока керування, перший вихід блока керування з'єднаний з першим входом першого перетворювача код-струм, вихід якого з'єднаний з першим виходом резистивного подільника, другий вихід блока керування з'єднаний з першим входом другого m перетворювача код-струм, вихід якого з'єднаний з 2 -1 виходом резистивного подільника, а вхід резистивного подільника з'єднаний з шиною джерела початкового зміщення, третій вихід блока керування з'єднаний з входом блока пам'яті, перший вихід якого через цифро-аналоговий перетворювач (ЦАП) з'єднаний з другими входами першого і другого перетворювачів код-струм, другий вихід блока пам'яті з'єднаний з першими входами додаткових перетворювачів код-струм, m вихід одного з яких з'єднаний з першим входом резистивного подільника, а вихід другого з 2 -1 виходом резистивного подільника [А.С. СРСР № 651475, МПК Η03К 13/17 бюлетень № 9, 1979 р.]. Недоліком цього АЦП є низька швидкодія. Відомий паралельно-послідовний 8-розрядний АЦП, який містить два 4-розрядних АЦП, m 25 30 35 40 45 50 55 60 кожен з яких містить послідовно з'єднані джерело опорних напруг і набір 2 2 1 компараторів, де m - кількість розрядів вихідного коду, різницевий пристрій, перші входи компараторів першого 4-розрядного АЦП з'єднані з шиною джерела вхідного сигналу, що підлягає перетворенню, виходи компараторів першого 4-розрядного АЦП з'єднані з входами елементів пам'яті через групу елементів І та АБО, виходи елементів пам'яті під'єднані до шин старших розрядів і до входів ЦАП, вихід якого з'єднаний з другим входом різницевого пристрою, перший вхід якого під'єднаний до шини джерела вхідного сигналу, що підлягає перетворенню, вихід різницевого пристрою з'єднаний з першими входами компараторів другого 4-розрядного АЦП, другі входи яких і другі входи першого 4-розрядного АЦП під'єднані до шини джерела опорних напруг, виходи компараторів другого 4-розрядного АЦП через групу елементів І та АБО під'єднані до шин молодших розрядів [патент США № 41248224, кл. 330/252 МПК Н03К 13/17]. Недоліком даного перетворювача є низька швидкодія. Найбільш близьким аналогом є n-розрядний паралельно-послідовний АЦП, який містить mрозрядний паралельний АЦП старших розрядів, аналоговий вхід якого під'єднано до виходу блока вибірки та зберігання, вхід якого під'єднано до шини джерела вхідного сигналу, який підлягає перетворенню, виходи m-розрядного паралельного АЦП під'єднано до першої вхідної шини буферного регістра та до відповідних входів ЦАП, вихід якого з'єднано з першим входом l підсилювача-віднімача, вихід якого під'єднано до неінвертувальних входів 2 -1 компараторів, де 1=n-m - число молодших розрядів иаралельно-послідовного АЦП, а інвертувальні входи l компараторів під'єднано до відповідних виходів резистивної матриці, що складається з 2 -1 резисторів, вхід резистивної матриці під'єднано до шини джерела опорної напруги, другий вхід l підсилювача-віднімача під'єднано до виходу блоку вибірки та зберігання, виходи 2 -1 компараторів під'єднано до відповідних входів перетворювача унітарного коду у позиційний двійковий код, в подальшому перетворювач коду, виходи якого під'єднано до другої вхідної шини буферного регістра, виходи якого є відповідно вихідною розрядною шиною пристрою. [Кестер У. Аналого-цифровое преобразование. - М.: Техносфера, 2007, С. 239, рис. 3.65]. Недоліком даного пристрою є низька швидкодія. Обмеження швидкодії обумовлене насамперед великим часом встановлення вихідної напруги підсилювача-віднімача з допустимими похибками. А це звужує робочу частотну смугу вхідних аналогових сигналів АЦП, що обмежує їх використання в радіолокації, експериментальній фізиці та іншій контрольновимірювальній апаратурі, пов'язаній зі спектральним аналізом радіо- та широкосмугових відеосигналів. В основу корисної моделі поставлено задачу створення паралельно-послідовного АЦП, в якому за рахунок введення нових блоків та зв'язків зменшується час перетворення вхідного сигналу, що сприяє підвищенню швидкодії. Поставлена задача вирішується тим, що в n-розрядний паралельно-послідовний АЦП, який містить m-розрядний паралельний АЦП старших розрядів, аналоговий вхід якого під'єднано до виходу блока вибірки та зберігання, вхід якого під'єднано до шини джерела вхідного сигналу, який підлягає перетворенню, виходи m-розрядного паралельного АЦП під'єднано до першої вхідної шини буферного регістра, виходи якого є відповідно вихідною розрядною шиною 1 UA 120057 U l 5 10 15 20 25 30 35 40 45 50 пристрою, перетворювач коду, 2 -1 компараторів, виходи яких під'єднано до відповідних входів перетворювача коду, виходи якого під'єднано до другої вхідної шини буферного регістра, l введено 2 -1 ЦАП з n-розрядними вхідними шинами, причому старші m розрядів вхідних шин ЦАП під'єднано до відповідних виходів паралельного АЦП старших розрядів, а на молодших l розрядах вхідних шин ЦАП встановлено відповідні цифрові коди N2, де Ν2 - двійковий номер l l кожного з 2 -1 ЦАП, виходи ЦАП під'єднано до відповідних інвертувальних входів 2 -1 l компараторів, а неінвертувальні входи 2 -1 компараторів під'єднано до виходу блока вибірки та зберігання. На кресленні наведена структурна електрична схема паралельно-послідовного аналогоцифрового перетворювача. Пристрій містить шину 1 джерела вхідного сигналу Uвх, блок вибірки та зберігання 2, ml l розрядний паралельний АЦП старших розрядів 3, l-розрядні вхідні шини 4 ЦАП, 2 -1 ЦАП 5, 2 -1 компараторів 6, перетворювач коду 7, буферний регістр 8, вихід якого під'єднано до вихідної шини АЦП 9, аналоговий вхід m-розрядного паралельного АЦП старших розрядів 3 під'єднано до виходу блока вибірки та зберігання 2, вхід якого під'єднано до шини джерела вхідного сигналу 1, який підлягає перетворенню, виходи m-розрядного паралельного АЦП старших розрядів 3 під'єднано до першої вхідної шини буферного регістра 8 та старших m розрядів вхідних шин ЦАП 5, а на молодших l розрядах вхідних шин ЦАП 5 встановлено відповідні l цифрові коди N2, виходи ЦАП 5 під'єднано до відповідних інвертувальних входів 2 -1 компараторів 6, неінвертувальні входи компараторів 6 під'єднано до виходу блока вибірки та зберігання 2, а виходи компараторів 6 під'єднано до відповідних входів перетворювача коду 7, виходи якого під'єднано до другої вхідної шини буферного регістра 8. Аналого-цифровий перетворювач працює наступним чином. Вхідний сигнал, який перетворюється Uвх, через шину джерела вхідного сигналу 1 подається на вхід блока вибірки та зберігання 2. З виходу блока вибірки та зберігання 2 дискретні відліки сигналу спрямовуються на аналоговий вхід m-розрядного паралельного АЦП 3 старших розрядів та неінвертувальні l входи 2 -1 компараторів 6. На виходах паралельного АЦП 3 формуються m-розрядні коди старших розрядів, які надходять до першої вхідної шини буферного регістра 8 та до старших m розрядів вхідних шин ЦАП 5. Ці m-розрядні коди старших розрядів керують діапазоном вихідних l рівнів ЦАП 5, які у свою чергу є опорними значеннями напруг для 2 -1 компараторів 6. Кожен код старших розрядів та цифрові коди N2 на молодших l розрядах вхідних шин ЦАП 5 формують l опорні значення напруг, що подаються на відповідні неінвертувальні входи 2 -1 компараторів 6. l На виходах 2 -1 компараторів 6 формується унітарний код, який перетворюється у позиційний двійковий код молодших розрядів за допомогою перетворювача коду 7. З виходу перетворювача коду 7 цифровий l-розрядний код молодших розрядів надходить до другої вхідної шини буферного регістра 8, з виходу якого до вихідної шини АЦП 9 надходить nрозрядний код. Таким чином, n-розрядний вихідний код, формується за допомогою m-розрядного l паралельного АЦП 3 старших розрядів та l-розрядного АЦП молодших розрядів, що містить 2 -1 l ЦАП 5, 2 -1 компараторів і перетворювач коду 7. При цьому в запропонованій схемі паралельнопослідовного АЦП не використовується підсилювач-віднімач для формування різницевого сигналу, що усуває з часового балансу АЦП часову затримку на встановлення напруги, що l подається на неінвертувальні входи 2 -1 компараторів 6. Виконання паралельно-послідовного АЦП згідно схеми корисної моделі з використанням одного m-розрядного паралельного АЦП 3 старших розрядів та l-розрядного АЦП молодших l l розрядів, що містить 2 -1 ЦАП 5, 2 -1 компараторів і перетворювача коду 7, дає можливість без застосування підсилювача-віднімача отримати вихідний n-розрядний код. Тому загальний час перетворення сигналу в запропонованому паралельно-послідовному АЦП зменшується і відповідно зростає швидкодія АЦП, що дає змогу розширити частотну смугу вхідних аналогових сигналів АЦП. ФОРМУЛА КОРИСНОЇ МОДЕЛІ 55 60 Паралельно-послідовний аналого-цифровий перетворювач, який містить m-розрядний паралельний АЦП старших розрядів, аналоговий вхід якого під'єднано до виходу блока вибірки та зберігання, вхід якого під'єднано до шини джерела вхідного сигналу, який підлягає перетворенню, виходи m-розрядного паралельного АЦП під'єднано до першої вхідної шини буферного регістра, виходи якого є відповідно вихідною розрядною шиною пристрою, l перетворювач коду, 2 -1 компараторів, виходи яких під'єднано до відповідних входів перетворювача коду, виходи якого під'єднано до другої вхідної шини буферного регістра, який 2 UA 120057 U l 5 відрізняється тим, що в нього введено 2 -1 ЦАП з n-розрядними вхідними шинами, причому старші m розряди вхідних шин ЦАП під'єднано до відповідних виходів паралельного АЦП старших розрядів, а на молодших l розрядах вхідних шин ЦАП встановлено відповідні цифрові l коди N2, де N2 - двійковий номер кожного з 2 -1 ЦАП, виходи ЦАП під'єднано до відповідних l інвертувальних входів 2 -1 компараторів, а неінвертувальні входи яких під'єднано до виходу блока вибірки та зберігання. Комп’ютерна верстка О. Гергіль Міністерство економічного розвитку і торгівлі України, вул. М. Грушевського, 12/2, м. Київ, 01008, Україна ДП “Український інститут інтелектуальної власності”, вул. Глазунова, 1, м. Київ – 42, 01601 3

ДивитисяДодаткова інформація

МПК / Мітки

МПК: H03M 1/00

Мітки: перетворювач, паралельно-послідовний, аналого-цифровий

Код посилання

<a href="https://ua.patents.su/5-120057-paralelno-poslidovnijj-analogo-cifrovijj-peretvoryuvach.html" target="_blank" rel="follow" title="База патентів України">Паралельно-послідовний аналого-цифровий перетворювач</a>

Попередній патент: Спосіб забору крові з латеральної хвостової вени у лабораторних щурів

Наступний патент: Спосіб виробництва сиру бринза із бактеріальним препаратом “геробактерин”

Випадковий патент: Апарат високого тиску і температури