Синхронний детектор в.п.аркушина

Формула / Реферат

Синхронный детектор, содержащий первый и второй интеграторы со входами установки в нуль, входы которых соединены и являются входом синхронного детектора, а выходы соединены с прямым и инверсным входами вычитающего сумматора, выход которого является выходом синхронного детектора, блок управления установкой интеграторов в нуль, выходы которого соединены с входами установки в нуль соответствующих интеграторов, отличающийся тем, что введены третий и четвертый интеграторы со входами установки в нуль, входы которых соединены и подключены к входам первого и второго интеграторов, а выходы - к соответствующим прямому и инверсному входам вычитающего сумматора, при этом блок управления установкой интеграторов в нуль выполнен с двумя дополнительными выходами, которые подключены к входам установки в нуль, соответственно, третьего и четвертого интеграторов.

Текст

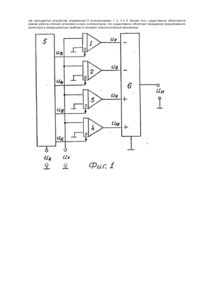

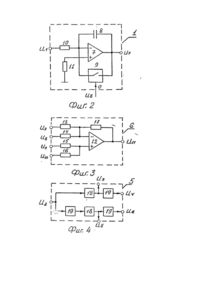

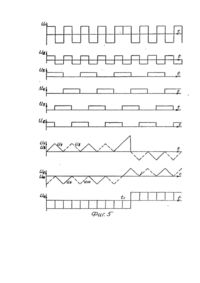

Изобретение относится к радиотехнике и может использоваться в измерительной технике, устройствах преобразования сигналов первичных датчиков систем автоматического управления, следящих системах, автоматизированном электроприводе - в тех областях техники, где широко применяются устройства амплитудной (AM), широтной (ШМ), фазовой (ФМ), частотной (ЧМ), амплитудной и фазовой одновременно (АФМ) модуляции периодических, несущи х определенную информацию сигналов. В основу изобретения поставлена задача создать синхронный детектор с расширенной рабочей полосой частот. Расширение рабочей полосы частот детектора связано с тем, что в нем, вместо сброса интеграторов в нуль короткими, в сравнении с периодом несущей, импульсами, сброс интеграторов в нуль осуществляется импульсами длительностью, равной периоду несуще го сигнала. Суть изобретения поясняется чертежами, где на фиг.1 приведена функциональная схема синхронного детектора, на фиг.2 -возможная реализация интегратора со сбросом в нуль выходного напряжения, на фиг.3 функциональная схема блока управления интеграторами, обеспечивающего поочередную установку интеграторов в нуль, на фиг.5 - временные диаграммы работы детектора. Предлагаемый синхронный детектор содержит интеграторы 1,2,3 и 4, входы интегрирования которых соединены и подключены к источнику входного сигнала U 1, блок управления установкой интеграторов нуль 5, вход которого подключен к источнику опорного сигнала U2, а выходы, с которых снимаются сигналы U3, U4, U5, U6 подключены ко входам установки интеграторов в нуль соответствующих интеграторов и вычитающий сумматор 6, ко входам которого подключены выходы интеграторов с сигналами U7, U8, U9, U10. Выходной сигнал детектора U11 снимается с выхода вычитающего сумматора 6. Интеграторы могут быть выполнены по схеме приведенной на фиг.2 на основе операционного усилитепя 7 с конденсатором 8 в цепи обратной связи и полупроводниковым ключом 9, соединяющим выход усилителя с его инвертирующим входом. Сигнал U1 на вход операционного усилителя подается через резистор 10. Резистор 11 соединяет инвертирующий вход с общей точкой источника питания усилителя. Вычитающий сумматор 6 (фиг.3) также может быть выполнен на основе операционного усилителя 12. Через резисторы 13 и 14 сигналы интеграторов 1 и 2 подаются на инвертирующий вход усилителя. Этим обеспечивается вычитание из суммы сигналов U9+U10 суммы сигналов U7+U8. Резистором 17 устанавливается коэффициент передачи сумматора. Блок управления установкой в нуль интеграторов (управлением ключами 9) (фиг.4) реализуется следующим образом. В канале формирования сигналов из и U4 также используются делитель частоты на два 18 и инвертора 19. Делитель частоты срабатывает либо по фронту, либо по срезу сигнала. В канале формирования сигналов U7 и U6 также используется делитель частоты на два и инвертор. Для обеспечения сдвига импульсов из и U4 на полпериода опорной частоты сигнал U2 подается на вход делителя частоты через инвертор. Функциональные узлы детектора могут иметь и иное исполнение. Синхронный детектор работает следующим образом. На входы интеграторов 1,2,3,4 подается амплитудно- либо фазомодулированиое напряжение (сигнал U1). Если на входе установки интегратора в нуль отсутствует сигнал сброса интегратора в нуль, интегратор интегрирует входной сигнал и на его выходе формируется напряжение, текущее значение которого пропорционально интегралу от момента размыкания ключа до текущего момента времени. В зависимости от конкретного выполнения интегратора установка его в нуль может осуществляться либо сигналом высокого уровня (логической единицей), либо сигналом низкого уровня (логическим нулем). Выходные напряжения U7 U8 интеграторов 1 и 2 подаются на инвертирующие входы сумматора 6. Выходные напряжения U9 и U11 инзерторов 3 и 4 подаются на неинвертирующие входы сумматора 6. При таком подключении выходов интеграторов 1, 2, 3, 4 ко входам сумматора выходное напряжение U11 синхронного детектора формируется как разность суммы напряжений U9+U10 и U7+U8, Т.е. С целью упрощения построения временных диаграмм работы, иллюстрирующих работу детектора, в качестве входного сигнала U11 принят сигнал прямоугольной формы (прямоугольный синус), фаза которого ступенчато изменяется в момент t1 на 180°. На фиг.5 опорный сигнал U2 принят (для удобства), также прямоугольным. Для управления работой четырех интеграторов устройство управления 5 формирует из опорного синхронизирующего сигнала U2 четыре последовательности импульсов управления U3, U4, U5 . U6. Частота следованияимпульсов управления в два раза меньше частоты опорного и входного сигналов. Последовательности импульсов управления U3 и U4 сдвинуты по фазе на 180°. Последовательности импульсов U5 и U6 также сдвинуты на 180°. В свою очередь U 4 и U5, U3 и U6 сдвинуты по фазе на полпериода опорного сигнала. На фиг.5 принято, что интеграторы устанавливаются в нуль низким уровнем сигнала (логическим нулем). При таком управлении установкой интеграторов в нуль каждый интегратор интегрирует входной сигнал в течение одного периода входного сигнала, а в течение следующего выходной сигнал интегратора поддерживается равным нулю. При подаче на вход детектора прямоугольного сигнала на выходах интеграторов образуются последовательности треугольных импульсов длительностью в один период несущего сигнала и паузами между ними также в один период несущего сигнала. Суммы сигналов U7+U8 и U9+U10 приведены на фиг.5. Если из суммы U9+U10 вычесть сумму сигналов U7+U8, то на выходе вычитающего сумматора 6 будет сформирован выходной сигнал U11 показанный на фиг.5. Из диаграммы фиг.5 следует, что на выходе синхронного детектора формируется сглаженный сигнал и что при изменении фазы выходного сигнала на 180° знак выходного сигнала изменяется на противоположный. Запаздывание изменения выходного сигнала, как следует из фиг.5 составляет половину периода несущего (опорного) сигнала. При подаче на вход синхронного детектора сигнала непрямоугольной формы, форма выходного сигнала Un не изменится. Изменится лишь форма сигнала на выходах интеграторов. Э то следует из того, что выходной сигнал Un на любом полупериоде равен разности сигналов двух интеграторов (на выходах двух др уги х интеграторов сигналы равны нулю. Интеграторы сброшены на нуль и поддерживаются в этом состоянии). Например, на интервале времени отТ/2 до Τ tи - постоянная времени интегрирования интеграторов. В выражении (2) принято, что коэффициенты передачи сумматора по всем входам по модулю равны единице. Из выражения (2) следует, что сигнал на выходе пропорционален среднему за полупериод значению входного сигнала. Если входной сигнал детектора прямоугольной формы, т.е. где Um - Um(t) - текущее значение амплитуды входного сигнала U1, а j = φ(t) - фаза входного сигнала, то при где - частота несущего сигнала. Если входной сигнал синусоидален, т.е. то При изменении амплитуды входного сигнала во времени выходной сигнал во времени выходной сигнал детектора аппроксимирует среднее значение входного сигнала ступенчатой кривой. При постоянной амплитуде и изменяющейся во времени фазе выходной сигнал детектора также имеет ступенчатую форму. Следует отметить, что синхронный детектор может быть использован в качестве модулятора входного сигнала. При этом амплитуда выходного прямоугольного сигнала будет пропорциональна среднему значению входного сигнала, а пульсации кратные частоте опорного сигнала будут полностью подавлены таким модулятором. Если на вход предлагаемого детектора подать входной периодический сигнал с частотой, отличной от частоты опорного сигнала, то на выходе детектора формируется периодический сигнал разностной частоты - аппроксимирования ступенчато синусоида низкой частоты. Таким образом, предлагаемый синхронный детектор может широко использоваться и для других целей обработки сигналов на периодической несущей. Из описания работы детектора, временных диаграмм и формулы (2) следует, что результат вычитания сигналов интеграторов 1, 2 из сигналов интеграторов 3, 4 периодически, с сдвигом в полпериода несущей устанавливаемых в н уль и поддерживаемых в этом состоянии в течение периода, оказывается эквивалентным выборке и запоминанию результата интегрирования сигнала в течение полупериода несущей частоты. Таким образом, в предлагаемом синхронном детекторе исключается необходимость использования устройств выборки -запоминания (хранения) сигнала, что существенно упрощает синхронный детектор в целом, так как для получения необходимой точности УВХ в них входит не менее двух усилителей. Надежность работы предлагаемого синхронного детектора возрастает в связи со значительным облегчением режима работы ключей установки интеграторов в нуль. Как следует из временных диаграмм фиг.5 сброс интеграторов в нуль осуществляется в моменты времени, когда выходной сигнал интегратора равен нулю, напряжение на конденсаторе 8 (фиг.2) равно нулю, конденсатор разряжен. Если на входе детектора сигнал U1 - периодическое напряжение, не содержащее постоянной составляющей, то интеграл такого входного сигнала за период равен нулю. Такой режим работы существенно снижает требования к величине их сопротивления в замкнутом состоянии. Из описания и временных диаграмм работы детектора следует, что управление интеграторами осуществляется не короткими импульсами, а импульсами длительностью в период несущей частоты. Что значительно снижает требования к быстродействию устройства управления ключей. Предельно упрощается схема управления ключами из-за исключения необходимости в формирователях коротких импульсов. Удлинение времени замыкания ключей до одного периода несущего сигнала при использовании в интеграторах одной и той же, для известного и предлагаемого детектора, элементной базы существенно расширяет, по сравнению с детектором-прототипом, диапазон частот несущего сигнала, в котором можно с успехом использовать предложенный детектор. Увеличение числа интеграторов не усложняет детектор, так как упрощается устройство управления 5 интеграторами 1, 2, 3 и 4. Кроме того, существенно облегчается режим работы ключей установки в нуль интеграторов, что существенно облегчает внедрение предлагаемого детектора в промышленные приборы и системы технологической автоматики.

ДивитисяДодаткова інформація

Назва патенту англійськоюАv.p.arkushyns sinchronous detector

Автори англійськоюArkushyn Vasyl Prokopovych

Назва патенту російськоюСинхронный детектор в.п.аркушина

Автори російськоюАркушин Василий Прокофьевич

МПК / Мітки

МПК: H03D 3/00

Мітки: в.п.аркушина, детектор, синхронний

Код посилання

<a href="https://ua.patents.su/5-18761-sinkhronnijj-detektor-vparkushina.html" target="_blank" rel="follow" title="База патентів України">Синхронний детектор в.п.аркушина</a>

Попередній патент: Пристрій для поздовжнього переміщення рейок залізничної колії

Наступний патент: Блок повітронагрівників доменної печі

Випадковий патент: Комплекс переробки вугільних шламів