Ldo стабілізатор постійної напруги з високим коефіцієнтом подавлення вхідних пульсацій

Номер патенту: 54329

Опубліковано: 17.02.2003

Автори: Чапічо Аркадій Давидович, Ліпатов Валерій Павлович, Піронер Ян Михайлович, Дрьомов Сергій Тимофійович

Формула / Реферат

1. LDO стабілізатор постійної напруги з високим коефіцієнтом подавления вхідних пульсацій, що містить регулюючий елемент, колектор керуючого транзистора якого через послідовно з'єднані переходи база-емітер узгоджуючого та силового транзисторів сполучений з вхідним виводом, емітер безпосередньо з'єднаний з колектором узгоджуючого транзистора, а через напівпровідниковий елемент сполучений з колектором силового транзистора, вихідним виводом та емітером струмозадавального транзистора, а база з'єднана з колектором запускаючого транзистора, база якого сполучена з виходом джерела позитивного зміщення, а емітер через перший емітерний резистор з'єднаний з вхідним виводом, підсилювач зворотного зв'язку виконаний за диференціальною схемою, колектор вхідного транзистора якого безпосередньо з'єднаний з базою струмозадавального транзистора, й через вирівнюючий резистор підключений до його емітера, база з'єднана з виходом джерела опорної напруги, емітер через другий емітерний резистор сполучений з загальною шиною і безпосередньо з'єднаний з емітером вихідного транзистора, база якого підключена до виходу вимірювального подільника вихідної напруги, а також другий обмежувальний резистор і оптоелектронний прилад, світлодіод якого ввімкнутий поміж колекторами запускаючого та вихідного транзисторів, колектор фототранзистора сполучений з емітером запускаючого транзистора, а емітер через послідовно з'єднані третій обмежувальний резистор та орган індикації сполучений з загальною шиною, який відрізняється тим, що другий вивід першого обмежувального резистора через джерело опорної напруги сполучений з загальною шиною, а колектор струмозадавального транзистора через другий обмежувальний резистор з'єднаний з базою керуючого транзистора.

2. LDO стабілізатор постійної напруги з високим коефіцієнтом подавлення вхідних пульсацій за п. 1, який відрізняється тим, що джерело опорної напруги виконано на малошумливому опорному напівпровідниковому елементі з низькою та термостабільною напругою.

Текст

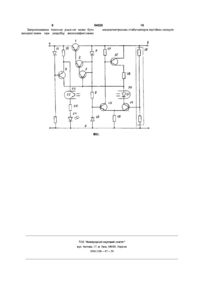

1 LDO стабілізатор постійної напруги з високим коефіцієнтом подавления вхідних пульсацій, що містить регулюючий елемент, колектор керуючого транзистора якого через послідовно з'єднані переходи база-емітер узгоджуючого та силового транзисторів сполучений з вхідним виводом, емітер безпосередньо з'єднаний з колектором узгоджуючого транзистора, а через напівпровідниковий елемент сполучений з колектором силового транзистора, вихідним виводом та емітером струмозадавального транзистора, а база з'єднана з колектором запускаючого транзистора, база якого сполучена з виходом джерела позитивного зміщення, а емітер через перший емітерний резистор з'єднаний з вхідним виводом, підсилювач зворотного зв'язку виконаний за диференціальною схемою, колектор вхідного транзистора якого безпосередньо з'єднаний з базою струмозадавально го транзистора, и через вирівнюючий резистор підключений до його емітера, база з'єднана з виходом джерела опорної напруги, емітер через другий емітерний резистор сполучений з загальною шиною і безпосередньо з'єднаний з емітером вихідного транзистора, база якого підключена до виходу вимірювального подільника вихідної напруги, а також другий обмежувальний резистор і оптоелектронний прилад, світлодюд якого ввімкнутий поміж колекторами запускаючого та вихідного транзисторів, колектор фототранзистора сполучений з емітером запускаючого транзистора, а емітер через послідовно з'єднані третій обмежувальний резистор та орган індикації сполучений з загальною шиною, який відрізняється тим, що другий вивід першого обмежувального резистора через джерело опорної напруги сполучений з загальною шиною, а колектор струмозадавального транзистора через другий обмежувальний резистор з'єднаний з базою керуючого транзистора 2 LDO стабілізатор постійної напруги з високим коефіцієнтом подавления вхідних пульсацій за п 1, який відрізняється тим, що джерело опорної напруги виконано на малошумливому опорному напівпровідниковому елементі з низькою та термостабільною напругою со Ю Запропонований винахід відноситься до галузі електротехніки і може бути використаним при проектуванні джерел електроживлення високоточної радіоелектронної апаратури ВІДОМІ стабілізатори постійної напруги, які володіють малим мінімальним падінням напруги, високою якістю вихідної напруги та достатньо ефективними захисними характеристиками В одному з відомих стабілізаторів (див авт св СРСР № 593204, кл GO5 F1/56.1976), який містить в собі регулюючий складений транзистор, ввімкнений в силовому колі, підсилювач зворотнього зв'язку, виконаний по диференціальній схемі, джерело опорної напруги та вимірювальний подільник вихідної напруги, верхнє плече якого виконано у вигляді двох послідовно з'єднаних резисторів, висока якість вихідної напруги забезпечується шляхом підключення колектора одного із транзисторів підсилювача зворотнього зв'язку до точки з'єднання резисторів верхнього плеча вимірювального подільника вихідної напруги Недоліками відомого стабілізатора є складність настроювання, оскільки в деяких випадках потребується підбір опору одного із резисторів верхнього плеча вимірювального подільника вихідної напруги, а також велика потужність розсіяння регулюючого транзистора В другому відомому стабілізаторі (див авт св 54329 CPCP № 714379, кл G05 F1/58, 1977), який складається з регулюючого елементу, виконаного на транзисторах, підсилювача зворотнього зв'язку, джерела опорної напруги, а також вузла захисту, включаючого захисний транзистор і датчик струму в силовому колі, якість вихідної напруги покращена шляхом виконання датчика струму на двох послідовно сполучених резисторах та підключення до їх точки з'єднання джерела опорної напруги Недоліками другого відомого стабілізатора є недостатньо висока якість вихідної напруги та велика потужність розсіяння регулюючого елемента В відомому стабілізаторі (див авт св СРСР № 832543, кп GO5 F1/56, 1978), який включає регулюючий елемент, виконаний на силовому, узгоджуючому та керуючому транзисторах з розділеними вихідними колекторними та емітерними ланцюгами, підсилювач зворотнього зв'язку з джерелом опорної напруги, вимірювальним подільником вихідної напруги та стабілізатором струму в якості вихідного навантаження, суттєво зменшені мінімальне падіння напруги і потужність розсіяння шляхом розділення вихідних колекторних та емітерних ланцюгів транзисторів регулюючого елемента Недоліками стабілізатора є невисока якість вихідної напруги оскільки підсилювач зворотнього зв'язку живиться через стабілізатор струму вхідною нестабілізованою напругою, недостатньо мала величина мінімального падіння напруги, великий струм короткого замикання та значна залежність його величини від температури навколишнього середовища Із відомих стабілізаторів більш близьким за технічною суттю і прийнятим за прототип (див патент України № 45669А, кл G 05F 1/56, 2001 р) є LDO стабілізатор постійної напруги з високим коефіцієнтом подавления вхідних пульсацій, що містить у собі регулюючий елемент, колектор керуючого транзистора якого через послідовно з'єднані переходи база-емітер узгоджуючого та силового транзисторів сполучений з вхідним виводом, емітер безпосередньо з'єднаний з колектором узгоджуючого транзистора та одним із виводів першого обмежувального резистора, а через напівпровідниковий елемент сполучений з колектором силового транзистора вихідним виводом та емітером струмозадавального транзистора, база з'єднана з колектором запускаючого транзистора, база якого сполучена з виходом джерела позитивного зміщення, а емітер через перший емітерний резистор з'єднаний з вхідним виводом, підсилювач зворотнього зв'язку, виконаний по диференціальній схемі, колектор вхідного транзистора якого безпосередньо з'єднаний з базою струмозадавального транзистора, а через вирівнюючий резистор підключений до його емітера, база з'єднана з виходом джерела опорної напруги, емітер через другий емітерний резистор сполучений з загальною шиною і безпосередньо з'єднаний з емітером вихідного транзистора, база якого підключена до виходу вимірювального подільника вихідної напруги, а також другий обмежувальний резистор і оптоелектронний прилад, світлодюд якого ввімкнутий поміж колекторами запускаючого та вихідного транзисторів, колектор фототранзистора сполучений з емітером запускаючого транзи стора, а емітер через послідовно з єднані третій обмежувальний резистор та орган індикації сполучений з загальною шиною Даний стабілізатор характеризується одночасно малим мінімальним падінням напруги оскільки роз'єднані колекторні та емітерні ВИХІДНІ ланцюги силового, узгоджуючого та керуючого транзисторів, підвищеною якістю вихідної напруги внаслідок живлення базового ланцюга керуючого транзистора стабільною напругою, малим струмом короткого замикання, а також високоточною індикацією номінального значення вихідної напруги Однак суттєвими недоліками стабілізатора, які обмежують його застосування, є недостатньо мала величина мінімального падіння напруги, недостатньо високий коефіцієнт подавления вхідних пульсацій, підвищені величина вихідного опору та струм короткого замикання Недостатньо мала величина мінімального падіння напруги та недостатньо високий коефіцієнт подавления вхідних пульсацій пояснюються тим, що внаслідок розкиду параметрів струмозадавальний транзистор в момент входження стабілізатора в нормальний режим роботи може знаходитись в режимі насичення і шунтувати напівпровідниковий елемент, обмежуючи його функцію Підвищені вихідний опір стабілізатора, а також струм короткого замикання пояснюється, ВІДПОВІДНО, обмеженим коефіцієнтом підсилення підсилювача зворотнього зв'язку та підвищеним падінням напруги на обмежувальному резисторі в режимі короткого замикання і складністю його регулювання В основу винаходу поставлена задача створення LDO стабілізатора постіної напруги з високим коефіцієнтом подавления вхідних пульсацій, в якому шляхом виключення можливості шунтування напівпровідникового елементу струмозадавальним транзистором в режимі мінімального падіння напруги зменшена величина мінімального падіння напруги та підвищений коефіцієнт подавления вхідних пульсацій, шляхом зниження напруги на джерелі опорної напруги при зниженні навантаження зменшена величина вихідного опору, а шляхом зменшення падіння напруги на першому обмежувальному резисторі в режимі короткого замикання та забезпеченням можливості його регулювання знижений струм короткого замикання Поставлена задача вирішується тим, що в LDO стабілізаторі постійної напруги з високим коефіцієнтом подавления вхідних пульсацій, колектор керуючого транзистора якого через послідовно з'єднані переходи база-емітер узгоджуючого та силового транзисторів сполучений з вхідним виводом, емітер безпосередньо з'єднаний з колектором узгодженого транзистора та одним із виводів першого обмежувального резистора, а через напівпровідниковий елемент сполучений з колектором силового транзистора, вихідним виводом та емітером струмозадавального транзистора, база з'єднана з колектором запускаючого транзистора, база якого сполучена з виходом джерела позитивного зміщення, а емітер через перший емітерний резистор з'єднаний з вхідним виводом, підсилювач зворотнього зв'язку, виконаний по диференціальній схемі, колектор вхідного транзистора якого 54329 безпосередньо з'єднаний з базою струмозадавального транзистора, а через вирівнюючий резистор підключений до його емітера, база з'єднана з виходом джерела опорної напруги, емітер через другий емітерний резистор сполучений з загальною шиною і безпосередньо з'єднаний з емітером вихідного транзистора, база якого підключена до виходу вимірювального подільника вихідної напруги, а також другий обмежувальний резистор, оптовоелектронний прилад, світлодюд якого ввімкнутий поміж колекторами запускаючого та вихідного транзисторів, колектор фототранзистора сполучений з емітером запускаючого транзистора, а його емітер через послідовно з'єднані третій обмежувальний резистор та орган індикації сполучений з загальною шиною 1) другий вивід першого обмежувального резистора через джерело опорної напруги сполучений з загальною шиною, а колектор струмозадавального транзистора через другий обмежувальний резистор з'єднаний з базою керуючого транзистора регулюючого елемента, 2) джерело опорної напруги виконано на малошумливому опорному напівпровідниковому елементі з низькою та термостабільною напругою В момент входження стабілізатора в нормальний режим роботи, коли струмозадавальний резистор знаходиться в режимі насичення, наявність другого обмежувального резистора в колекторному ланцюгу струмозадавального транзистора виключає можливість шунтування напівпровідникового елементу Крім цього другий обмежувальний резистор з опорним напівпровідниковим елементом в значній мірі визначають струм короткого замикання стабілізатора При зниженні навантаження одночасно зменшується напруга опорного напівпровідникового елементу, ВІДПОВІДНО зменшується і вихідний опір стабілізатора Аналіз науково-технічної та патентної літератури не виявив аналогічних технічних рішень На фіг показана електрична схема запропонованого LDO стабілізатора постійної напруги з високим коефіцієнтом подавления вхідних пульсацій Запропонований LDO стабілізатор постійної напруги містить в собі регулюючий елемент, виконаний на силовому 1, узгоджувальному 2 та керуючому 3 транзисторах, вхідний вивід 4, вихідний вивід 5, загальну шину 6, напівпровідниковий елемент 7, перший обмежувальний резистор 8, запускаючий, транзистор 9, перший емітерний резистор 10, джерело 11 позитивного зміщення, струмозадавальний транзистор 12, вхідний 13 та вихідний 14 транзистори диференціального підсилювача зворотнього зв'язку, другий емітерний резистор 15, джерело 16 опорної напруги, вирівнюючий резистор 17, другий обмежувальний резистор 18, вимірювальний подільник 19 вихідної напруги, а також оптоелектронний елемент 20, який складається з світодюда 21 та фототранзистора 22, третій обмежувальний резистор 23 і орган індикації 24 Колектор керуючого транзистора 3 регулюючого елементу через переходи база-емітер узгоджуючого 2 та силового 1 транзисторів з'єднаний з вхід ним виводом 4, емітер його безпосередньо сполучений з колектором узгоджуючого транзистора 2, через напівпровідниковий елемент 7 з'єднаний з колектором силового транзистора 1, вихідним виводом 5 та емітером струмозадавального транзистора 12, а послідовно сполучені перший обмежувальний резистор 8 та джерело 16 опорної напруги з'єднаний з загальною шиною 6, база безпосередньо сполучена з колектором запускаючого транзистора 9, а через другий обмежувальний резистор 18 з'єднана з колектором струмозадавального транзистора 12 Емітер запускаючого транзистора 9 через перший емітерний резистор 10 з'єднаний з вхідним виводом 4, а його база сполучена з виходом джерела 11 позитивного зміщення Колектор вхідного транзистора 13 диференціального підсилювача зворотнього зв'язку безпосередньо з'єднаний з базою струмозадавального транзистора 12, а через вирівнюючий резистор 17 підключений до його емітера, база з'єднана з виходом джерела 16 опорної напруги, емітер через другий емітерний резистор 15 сполучений з загальною шиною 6 і безпосередньо з'єднаний з емітером вихідного транзистора 14, база якого підключена до виходу вимірювального подільника 19 вихідної напруги, колектор через світлодюд 21 оптоелектронного приладу 20 з'єднаний з базою керуючого транзистора 3 Фототранзистор 22 оптоелектронного приладу 20 послідовно з третім обмежувальним резистором 23 та органом індикації 24, виконаним на СВІТЛОДІОДІ, включений в ланцюг закривання запускаючого транзистора 9 - поміж його емітером та загальною шиною Запропонований LDO стабілізатор постійної напруги з високим коефіцієнтом подавления вхідних пульсацій працює наступним чином При вмиканні вхідної напруги запускаючий транзистор 9 під впливом джерела 11 позитивного зміщення знаходиться у відкритому стані і забезпечує проходження запускаючого базового струму керуючого транзистора 3, фототранзистор 22 при цьому знаходиться в закритому стані В цей період відбувається включення стабілізатора і підвищення його вихідної напруги до номінальної величини В той момент, коли вихідна напруга стабілізатора досягає своєї номінальної величини, а падіння напруги на ньому має мінімальну величину, відкривається вихідний транзистор 14 підсилювача зворотнього зв'язку, з'являється його колекторний струм, що приводить до включення світлодюда 21, та, ВІДПОВІДНО, фототранзистора 22 оптоелектронного приладу 20 В подальшому струм, який починає протікати через ланцюг, що складається з першого емітерного резистора 10, фототранзистора 22, третього обмежувального резистора 23 і органа індикації 24, одночасно забезпечує спрацювання органа індикації 24 та закриття запускаючого транзистора 9 Спрацювання органа індикації 24 свідчить про ВІДПОВІДНІСТЬ вихідної напруги як номінальній величині так і високій її якості, а також про нормальну роботу елементів стабілізатора Висока якість вихідної напруги стабілізатора пояснюється тим, що після закриття запускаючого транзистора 9, базове коло керуючого транзистора З та колекторне коло вихідного транзистора 14 підсилювача зворотнього зв'язку живляться стабіль 54329 ним струмом Із 14 з виходу стабілізатора Величина струму Ь и визначається наступним виразом U 7 - UJe63 І, R 3,14 18 +Rei

ДивитисяДодаткова інформація

Назва патенту англійськоюDirect-voltage regulator with low output voltage drop and an increased input voltage ripple suppression factor

Автори англійськоюDriomov Serhii Tymofiiovych, Lipatov Valerii Pavlovych, Pironer Yan Mykhailovych

Назва патенту російськоюСтабилизатор постоянного напряжения с низким падением выходного напряжения и повышенным коэффициентом подавления пульсаций входного напряжения

Автори російськоюДремов Сергей Тимофеевич, Липатов Валерий Павлович, Пиронер Ян Михайлович

МПК / Мітки

МПК: G05F 1/56

Мітки: вхідних, високим, стабілізатор, пульсацій, коефіцієнтом, напруги, постійної, подавлення

Код посилання

<a href="https://ua.patents.su/5-54329-ldo-stabilizator-postijjno-naprugi-z-visokim-koeficiehntom-podavlennya-vkhidnikh-pulsacijj.html" target="_blank" rel="follow" title="База патентів України">Ldo стабілізатор постійної напруги з високим коефіцієнтом подавлення вхідних пульсацій</a>

Попередній патент: Спосіб одержання хірургічного шовного матеріалу із біологічної сировини

Наступний патент: Спосіб оцінки метаболічних порушень у ротовій порожнині при хронічному рецидивуючому афтозному стоматиті

Випадковий патент: Трансформаторна підстанція