Перетворювач коду

Номер патенту: 50077

Опубліковано: 17.05.2004

Автори: Жуков Ігор Анатолійович, Гамаюн Володимир Петрович, Візор Ярослав Євстахович

Формула / Реферат

Перетворювач коду, який містить N вхідних та N вихідних шин та модулі, кожний з яких має елемент АБО та елемент І, входи яких з'єднані з входами модуля, вихід елемента АБО підключений до першого виходу модуля, вихід елемента І - до другого виходу модуля, по чотири модулі розміщені у вузлах прямокутних матриць 2х2 та по одному модулю - у вузлах пірамідальних матриць, при цьому виходи прямокутних матриць підключені до входів пірамідальних матриць, в прямокутних матрицях входи модулів першого стовпця та виходи модулів останнього стовпця з'єднані відповідно з входами та виходами цих матриць, а в другому стовпці входи модулів першого рядка підключені до перших виходів модулів першого та другого рядків першого стовпця, входи модуля другого рядка з'єднані з другими виходами модулів першого рядка, в пірамідальних матрицях перший та четвертий входи відповідно з'єднані з першим та четвертим виходами цих матриць, другий та третій входи підключені до входів модуля першого стовпця, при цьому виходи цього модуля підключені до другого та третього виходів пірамідальних матриць відповідно, який відрізняється тим, що в нього додатково введені перший стовпець ![]() елементів АБО (

елементів АБО (![]() - кількість вхідних та вихідних шин :

- кількість вхідних та вихідних шин : ![]() , де

, де ![]() ), який містить по два елементи з двома, трьома, ...,

), який містить по два елементи з двома, трьома, ..., ![]() входами та один елемент з

входами та один елемент з ![]() входами, виходи N-1 елементів АБО підключені до перших N-1 виходів перетворювача коду, перший стовпець N/2 блоків елементів І, причому виходи N/2 елементів І кожного блока підключені до N/2 виходів кожного блока, а N входів елементів кожного блока підключені до N входів кожного блока, перший вихід першого блока елементів І підключений до другого елемента АБО першого стовпця елементів АБО (номер елемента АБО в стовпці елементів АБО вибирається, як сума номера блока елементів І та номера його виходу №АБО=№бл.+№в), N/2-й вихід першого блока елементів І підключений до (N/2+1)-го елемента АБО першого стовпця елементів АБО,

входами, виходи N-1 елементів АБО підключені до перших N-1 виходів перетворювача коду, перший стовпець N/2 блоків елементів І, причому виходи N/2 елементів І кожного блока підключені до N/2 виходів кожного блока, а N входів елементів кожного блока підключені до N входів кожного блока, перший вихід першого блока елементів І підключений до другого елемента АБО першого стовпця елементів АБО (номер елемента АБО в стовпці елементів АБО вибирається, як сума номера блока елементів І та номера його виходу №АБО=№бл.+№в), N/2-й вихід першого блока елементів І підключений до (N/2+1)-го елемента АБО першого стовпця елементів АБО, ![]() -й вихід

-й вихід ![]() -гo блока елементів І підключений до (

-гo блока елементів І підключений до (![]() )-гo елемента АБО першого стовпця елементів АБО, (

)-гo елемента АБО першого стовпця елементів АБО, (![]() )-й вихід

)-й вихід ![]() -гo блока елементів І підключений до (

-гo блока елементів І підключений до (![]() )-го елемента АБО,

)-го елемента АБО, ![]() -й вихід

-й вихід ![]() -го блока елементів І підключений до

-го блока елементів І підключений до ![]() -го виходу перетворювача коду, перший управляючий та перший операційний пристрої, кожний з яких містить

-го виходу перетворювача коду, перший управляючий та перший операційний пристрої, кожний з яких містить ![]() входи та

входи та ![]() виходи, причому

виходи, причому ![]() входи першого управляючого пристрою підключені до перших

входи першого управляючого пристрою підключені до перших ![]() входів перетворювача коду, перший вихід першого управляючого пристрою підключений до перших входів

входів перетворювача коду, перший вихід першого управляючого пристрою підключений до перших входів ![]() елементів І першого блока елементів І та до першого елемента АБО першого стовпця елементів АБО,

елементів І першого блока елементів І та до першого елемента АБО першого стовпця елементів АБО, ![]() -й вихід управляючого пристрою підключений до перших входів

-й вихід управляючого пристрою підключений до перших входів ![]() елементів І

елементів І ![]() -го блока елементів І та до

-го блока елементів І та до ![]() -го елемента АБО першого стовпця елементів АБО,

-го елемента АБО першого стовпця елементів АБО, ![]() вихід управляючого пристрою підключений до перших входів

вихід управляючого пристрою підключений до перших входів ![]() елементів І та до

елементів І та до ![]() елемента АБО першого стовпця елементів АБО, перший вихід операційного пристрою підключений до другого входу першого елемента І кожного блока елементів І та до першого елемента АБО першого стовпця елементів АБО,

елемента АБО першого стовпця елементів АБО, перший вихід операційного пристрою підключений до другого входу першого елемента І кожного блока елементів І та до першого елемента АБО першого стовпця елементів АБО, ![]() -й вихід операційного пристрою підключений до другого входу

-й вихід операційного пристрою підключений до другого входу ![]() -го елемента І кожного блока елементів І та до

-го елемента І кожного блока елементів І та до ![]() -го елемента АБО першого стовпця елементів АБО,

-го елемента АБО першого стовпця елементів АБО, ![]() -й вихід операційного пристрою підключений до другого входу

-й вихід операційного пристрою підключений до другого входу ![]() -гo елемента І кожного блока елементів І та до

-гo елемента І кожного блока елементів І та до ![]() -го елемента АБО першого стовпця елементів АБО, крім того перший управляючий та перший операційний пристрої містять другі перетворювачі коду, виходи яких підключені до виходів, а входи - до входів першого управляючого та першого операційного пристроїв відповідно, причому кожний другий перетворювач коду містить другий стовпець

-го елемента АБО першого стовпця елементів АБО, крім того перший управляючий та перший операційний пристрої містять другі перетворювачі коду, виходи яких підключені до виходів, а входи - до входів першого управляючого та першого операційного пристроїв відповідно, причому кожний другий перетворювач коду містить другий стовпець ![]() елементів АБО, другий стовпець

елементів АБО, другий стовпець ![]() блоків елементів І, кожний з яких містить

блоків елементів І, кожний з яких містить ![]() елементів І, другий управляючий та другий операційний пристрої, причому

елементів І, другий управляючий та другий операційний пристрої, причому ![]() -і входи другого управляючого пристрою та

-і входи другого управляючого пристрою та ![]() -і входи другого операційного пристрою підключені до

-і входи другого операційного пристрою підключені до ![]() -х входів других перетворювачів коду в першому управляючому та в першому операційному пристроях, виходи других управляючих та операційних пристроїв підключені до входів других стовпців елементів І та других стовпців елементів АБО, виходи других стовпців елементів І підключені до входів других стовпців елементів АБО, виходи других стовпців елементів АБО підключені до виходів других перетворювачів коду в першому управляючому та в першому операційному пристроях, крім того

-х входів других перетворювачів коду в першому управляючому та в першому операційному пристроях, виходи других управляючих та операційних пристроїв підключені до входів других стовпців елементів І та других стовпців елементів АБО, виходи других стовпців елементів І підключені до входів других стовпців елементів АБО, виходи других стовпців елементів АБО підключені до виходів других перетворювачів коду в першому управляючому та в першому операційному пристроях, крім того ![]() -і (

-і (![]() ) управляючі та

) управляючі та ![]() -і операційні пристрої містять (

-і операційні пристрої містять (![]() )-і перетворювачі коду, виходи яких підключені до виходів, а входи - до входів

)-і перетворювачі коду, виходи яких підключені до виходів, а входи - до входів ![]() -го управляючого та

-го управляючого та ![]() -го операційного пристроїв відповідно, причому кожний (

-го операційного пристроїв відповідно, причому кожний (![]() )-й перетворювач коду містить (

)-й перетворювач коду містить (![]() )-й стовпець

)-й стовпець ![]() елементів АБО, (

елементів АБО, (![]() )-й стовпець

)-й стовпець ![]() блоків елементів І, кожний з яких містить по

блоків елементів І, кожний з яких містить по ![]() елементів І, (

елементів І, (![]() )-й управляючий та (

)-й управляючий та (![]() )-й операційний пристрої, причому

)-й операційний пристрої, причому ![]() -і входи (

-і входи (![]() )-го управляючого пристроїв та

)-го управляючого пристроїв та ![]() -і входи (

-і входи (![]() )-го операційного пристроїв підключені до

)-го операційного пристроїв підключені до ![]() входів (

входів (![]() )-х перетворювачів коду в

)-х перетворювачів коду в ![]() -му управляючому та в

-му управляючому та в ![]() -му операційному пристроях, виходи (

-му операційному пристроях, виходи (![]() )-х управляючих та операційних пристроїв підключені до входів (

)-х управляючих та операційних пристроїв підключені до входів (![]() )-х стовпців елементів І та до (

)-х стовпців елементів І та до (![]() )-х стовпців елементів АБО, виходи (

)-х стовпців елементів АБО, виходи (![]() )-х стовпців елементів І підключені до входів (

)-х стовпців елементів І підключені до входів (![]() )-х стовпців елементів АБО, виходи (

)-х стовпців елементів АБО, виходи (![]() )-х стовпців елементів АБО підключені до виходів (

)-х стовпців елементів АБО підключені до виходів (![]() )-х перетворювачів коду в

)-х перетворювачів коду в ![]() -му управляючому та в

-му управляючому та в ![]() -му операційному пристроях, крім того передостанні управляючі та операційні пристрої містять останні перетворювачі коду, вісім виходів яких підключені до восьми виходів, а вісім входів - до восьми входів передостанніх управляючих та операційних пристроїв відповідно,

-му операційному пристроях, крім того передостанні управляючі та операційні пристрої містять останні перетворювачі коду, вісім виходів яких підключені до восьми виходів, а вісім входів - до восьми входів передостанніх управляючих та операційних пристроїв відповідно, ![]() останніх перетворювачів коду підключені до

останніх перетворювачів коду підключені до ![]() входів перетворювача коду, причому кожний останній перетворювач коду містить останній стовпець сімох елементів АБО, останній стовпець чотирьох блоків елементів І, кожний з яких містить по чотири елементи І, останні управляючі та останні операційні пристрої, причому по чотири входи останніх управляючих пристроїв підключені до восьми входів останніх перетворювачів коду в передостанніх управляючих та в передостанніх операційних пристроях і підключені до входів останніх стовпців елементів І та до останніх стовпців елементів АБО, виходи останніх стовпців елементів І підключені до входів останніх стовпців елементів АБО, виходи останніх стовпців елементів АБО підключені до виходів останніх перетворювачів коду в передостанніх управляючих та в передостанніх операційних пристроях, крім того останні управляючі та операційні пристрої містять прямокутні та пірамідальні матриці модулів елементів АБО та І, причому чотири входи прямокутних матриць модулів елементів АБО та І підключені до чотирьох входів останніх управляючих та операційних пристроїв, а чотири виходи прямокутних та пірамідальних матриць підключені до чотирьох виходів управляючих та операційних пристроїв.

входів перетворювача коду, причому кожний останній перетворювач коду містить останній стовпець сімох елементів АБО, останній стовпець чотирьох блоків елементів І, кожний з яких містить по чотири елементи І, останні управляючі та останні операційні пристрої, причому по чотири входи останніх управляючих пристроїв підключені до восьми входів останніх перетворювачів коду в передостанніх управляючих та в передостанніх операційних пристроях і підключені до входів останніх стовпців елементів І та до останніх стовпців елементів АБО, виходи останніх стовпців елементів І підключені до входів останніх стовпців елементів АБО, виходи останніх стовпців елементів АБО підключені до виходів останніх перетворювачів коду в передостанніх управляючих та в передостанніх операційних пристроях, крім того останні управляючі та операційні пристрої містять прямокутні та пірамідальні матриці модулів елементів АБО та І, причому чотири входи прямокутних матриць модулів елементів АБО та І підключені до чотирьох входів останніх управляючих та операційних пристроїв, а чотири виходи прямокутних та пірамідальних матриць підключені до чотирьох виходів управляючих та операційних пристроїв.

Текст

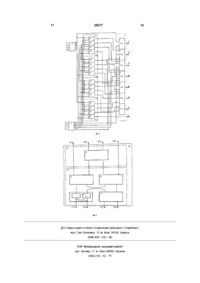

Перетворювач коду, який містить N вхідних та N вихідних шин та модулі, кожний з яких має елемент „АБО" та елемент „І", входи яких з'єднані з входами модуля, вихід елементу „АБО" підключений до першого виходу модуля, вихід елементу „І" - до другого виходу модуля, по 4 модулі розміщені у вузлах прямокутних матриць 2x2 та по 1-му модулю - у вузлах пірамідальних матриць, при цьому виходи прямокутних матриць підключені до входів пірамідальних матриць, в прямокутних матрицях входи модулів першого стовпця та виходи модулів останнього стовпця з'єднані ВІДПОВІДНО з входами та виходами цих матриць, а в другому стовпці входи модулів першого рядка підключені до перших виходів модулів першого та другого рядків першого стовпця, входи модуля другого рядка з'єднані з другими виходами модулів першого рядка, в пірамідальних матрицях перший та четвертий входи ВІДПОВІДНО з'єднані з першими та четвертим виходами цих матриць, другий та третій входи підключені до входів модуля першого стовпця, при цьому виходи цього модуля підключені до другого та третього виходів пірамідальних матриць ВІДПОВІДНО, ЯКИЙ відрізняється тим, що додатково введені 1-й стовпець N-1 елементів „АБО" (N - КІЛЬКІСТЬ ВХІДНИХ та вихідних шин N=2m, де т = 3 , 4, 5, 6 ), який МІСТИТЬ по 2 елементи з 2-ма, 3-ма, , N/2-ма вхо дами та один елемент з ( І % +1) входами, виходи N-1 елементів „АБО" підключені до перших N-1 виходів перетворювача коду, 1-й стовпець N/2 блоків елементів „І", причому виходи N/2 елементів „І" кожного блока підключені до N/2 виходів кожного блока, а N входів елементів кожного блока підключені до N входів кожного блока, перший вихід першого блока елементів „І" підключений до другого елементу „АБО" 1-го стовпця елементів „АБО" (номер елементу „АБО" в стовпці елементів „АБО" вибирається як сума номера блока елементів „І" та номер його виходу), N/2 вихід першого блока елементів „І" підключений до (1 + '%) елементу „АБО" 1-го стовпця елементів „АБО", k вихід І блока елементів „І" підключений до (к + І)-го елементу „АБО" 1-го стовпця елементів „АБО", ( ' % 1)-й вихід N/2-го блока елементів „І" підключений до N-1 елементу „АБО", N/2-й вихід N/2 блока елементів „І" підключений до N-ro виходу перетворювача коду, 1-й управляючий та 1-й операційний пристрої, кожний з яких містить N/2 входи та N/2 виходи, причому N/2 входи 1-го управляючого пристрою підключені до перших N/2 входів елементів „І" першого блока елементів „І" та до 1-го елементу „АБО" 1-го стовпця елементів „АБО", f-й вихід управляючого пристрою підключений до перших входів N/2 елементів „І" f-ro блока елементів „І" та до f-ro елементу „АБО" 1-го стовпця елементів „АБО", N/2-й вихід управляючого пристрою підключений до перших входів N/2 елементів „І" та до N/2 елементу „АБО" 1-го стовпця елементів „АБО", перший вихід операційного пристрою підключений до другого входу першого елементу „І" кожного блока елементів „І" та до першого елементу „АБО" 1-го стовпця елементів „АБО", п-й вихід операційного пристрою підключений до другого входу п-го елементу „І" кожного блока елементів „І" та до п-го елементу „АБО" 1-го стовпця елементів „АБО", N/2-й вихід операційного пристрою підключений до другого входу N/2-го елементу „І" кожного блока елементів „І" та до N/2-го елементу „АБО" 1-го стовпця елементів „АБО", крім того 1-й управляючий та 1-й операційний пристрої містять 2-п перетворювачі коду, виходи яких підключені до виходів, а входи до входів 1-го управляючого та 1-го операційного пристроїв ВІДПОВІДНО, причому кожний другий перетворювач коду містить 2-й стовпець N/2-1 елементів „АБО", 2-й стовпець N/4 блоків елементів „І", кожний з яких містить N/4 елементів „І", 2-й управляючий та 2-й операційний пристрої, причому N/4 входи 2-го управляючого пристрою та N/4 входи другого операційного пристрою підключені до N/2 входів 2-х перетворювачів коду в 1-му управляючому та 1-му операційному пристроях, виходи 2-х управляючих та операційних пристроїв підключені до входів 2-х стовпців елементів „І" та 2-х стовпців елементів „АБО", виходи 2-х стовпців О о ю 50077 елементів „І" підключені до входів 2-х стовпців елементів „АБО", виходи 2-х стовпців елементів „АБО" підключені до виходів 2-х перетворювачів коду в 1 -му управляючому та в 1 -му операційному пристроях, крім того р-ті (р=2, 3, 4, ) управляючі та р-ті операційні пристрої містять (р+1)-і перетворювачі коду, виходи яких підключені до виходів, а входи до входів р-го управляючого та р-го операційного пристроїв ВІДПОВІДНО, причому кожний (р+1)-й перетворювач коду містить (р+1)-й сто- 1 елементів „АБО", (р+1)-й стовпець впець N/p /2 блоків елементів містить по yyL +1 кожний з яких елементів „І", (р+1)-й управ ляючий та (р+1)-й операційний пристрої, причому /Р "і L +1 входи (р+1)-го управляючого пристроїв та І |Ч)Л' +1 входи (р+1)-го операційного пристроїв підключені до ' рювачів коду в р-му управляючому та р-му опевходів (р+1)-х перетвораційному пристроях, виходи (р+1)-х управляючих та операційних пристроїв підключені до входів (р+1)-х стовпців елементів „І" та до (р+1)-х стовпців елементів „АБО", виходи (р+1)-х стовпців елементів „І" підключені до входів (р+1)-х стовпців елементів „АБО", входи (р+1)-х стовпців елементів Запропонований пристрій відноситься до обчислювальної техніки і може використовуватися для реалізації технічних засобів обчислювальної техніки та дискретної автоматики Відомо пристрій перетворювача двійкового коду в ущільнений код (А С СССР №1562975), який складається з прямокутної та пірамідальної матриць, кожний з яких має елемент "И" та елемент "ИЛИ" Спільними ознаками аналога та запропонованого пристрою є наявність модулів з елементами "И" та "ИЛИ", та спосіб підключення цих елементів до вхідних та вихідних шин модуля Причиною, яка перешкоджає підвищити швидкодію перетворювача є наявність великої КІЛЬКОСТІ СТОВПЦІВ модулів з елементами "И" та "ИЛИ" Відомо пристрій перетворювача кодів (А С СССР №869030), який має N вхідних та N вихідних шин та модулі, кожний з яких має елемент "ИЛИ" та елемент "И", входи яких з'єднані з входами модуля, вихід елементу "ИЛИ" підключений до першого виходу модуля, вихід елементу "И" - до другого виходу модуля, N' модулів розміщені у N вузлах прямокутної матриці о v N тз 2 модулів -у вузлах пірамідальної матриці з ,,АБО" підключені до виходів (р+1)-х перетворювачів коду в р-му управляючому та в р-му операційному пристроях, крім того передостанні управляючі та операційні пристрої містять останні перетворювачі коду, 8 виходів яких підключені до 8 виходів, а 8 входів до 8 входів передостанніх управляючих та операційних пристроїв ВІДПОВІДНО, N/8 останніх перетворювачів коду підключені до N входів перетворювача коду, причому кожний останній перетворювач коду містить останній стовпець 7-х елементів „АБО", останній стовпець 4-х блоків елементів „І", кожний з яких містить по 4 елементи „І", останні управляючі та останні операційні пристрої, причому 4 входи останніх управляючих пристроїв та 4 входи останніх операційних пристроїв підключені до 8 входів останніх перетворювачів коду в передостанніх управляючому та в передостанніх операційних пристроях підключені до входів останніх стовпців елементів „І" та до останніх стовпців елементів „АБО", виходи останніх стовпців елементів „АБО" підключені до виходів останніх перетворювачів коду в передостанніх управляючих та в передостанніх операційних пристроях, крім того останні управляючі та операційні пристрої містять прямокутні та пірамідальні матриці модулів елементів „АБО" та „І", причому 4 входи прямокутних матриць модулів елементів „АБО" та „І" підключені до 4-х входів останніх управляючих та операційних пристроїв, а 4 виходи прямокутних та пірамідальних матриць підключені до 4 виходів управляючих та операційних пристроїв модулів розміщені у вузлах СТОВПЦІВ, а (N-1) 4 ч прямокутної матриці з стовпців та N + 1Г N + 1 -1 (N рядків та ^ модулів розміщених у вузлах пірамідальної матриці N+1 -1 СТОВПЦІВ ВІДПОВІДНО при парному та непарному N, при цьому входи прямокутної матриці з'єднані з вхідними шинами, а виходи підключені до входів пірамідальної матриці, виходи якої з'єднані з вихідними шинами, в прямокутній матриці входи модулів першого стовпця та виходи модулів останнього стовпця з'єднані ВІДПОВІДНО З входами та виходами цієї матриці, а в і-му стовпці входи модулів першого рядка підключені до перших виходів модулів першого та другого рядків (і - 1)-го стовпця, входи модуля j-ro рядка з'єднані з другим виходом модуля (| - 1)-го рядка та першим виходом модуля Q + 1)-го рядка (і - 1)-го стовпця, входи модуля останнього рядка підключені до других виходів модулів передостаннього та останнього рядків (і - 1)-го стовпця, пірамідальній матриці перший та останній входи ВІДПОВІДНО з'єднані з першим та останнім виходами цієї матриці, а другі попарно підключені 50077 до входів модулів першого стовпця при цьому в іму стовпці перший вихід першого модуля, та другий вихід останнього модуля з'єднані з однойменними виходами матриці, а другий вихід модуля Q 1)-го рядка та перший вихід модуля j-ro рядка підключені до входів ВІДПОВІДНОГО модуля (і + 1)-го стовпця Цей пристрій, за сукупністю ознак, найбільш ближче підходить до запропонованого пристрою, тому він вибраний в якості прототипу Спільними ознаками прототипу та запропонованого пристрою являється наявність модулів з елементами "ИЛИ" та "И", спосіб підключення елементів "ИЛИ", "И" в модулі, наявність прямокутної, пірамідальних матриць модулів та спосіб їх утворення Причиною, яка перешкоджає підвищити швидкодію перетворювача є наявність N - 1 стовпців модулів з елементами "ИЛИ" та "И" В основу винаходу покладено завдання удосконалити такий перетворювач коду, в якому введення нових стовпців елементів "ИЛИ","И" та нових зв'язків МІЖ НИМИ, ДОЗВОЛИЛО зменшити загальну КІЛЬКІСТЬ СТОВПЦІВ елементів і за рахунок ЦЬОГО ПІДВИЩИТИ ШВИДКОДІЮ Покладене завдання удосконалити винахід вирішується тим, що перетворювач коду містить N вхідних та N вихідних шин та модулі, кожний з яких має елемент "ИЛИ" та елемент "И", входи яких з'єднані з входами модуля, вихід елементу "ИЛИ" підключений до першого виходу модуля, вихід елементу "И" - до другого виходу модуля, по 4 модулі розміщені у вузлах прямокутних матриць 2 x 2 та по 1-му модулю - у вузлах пірамідальних матриць, при цьому виходи прямокутних матриць підключені до входів пірамідальних матриць, в прямокутних матрицях входи модулів першого стовпця та виходи модулів останнього стовпця з'єднані ВІДПОВІДНО з входами та виходами цих матриць, а в другому стовпці входи модулів першого рядка підключені до перших виходів модулів першого та другого рядків першого стовпця, входи модуля другого рядка з'єднані з другими виходами модулів першого рядка, в пірамідальних матрицях перший та четвертий входи ВІДПОВІДНО з'єднані з першим та четвертим виходами цих матриць, 2-й та 3-й входи підключені до входів модуля першого стовпця, при цьому виходи цього модуля підключені до 2-го та 3-го виходів пірамідальних матриць ВІДПОВІДНО, згідно з винаходом додатково введені 1-й стовпець N - 1 елементів "ИЛИ" (N - КІЛЬКІСТЬ ВХІДНИХ та вихідних шин N = 2 т де т = 3, 4, 5, 6 ), який МІСТИТЬ по 2 елемента з 2-ма, 3-ма, входами та один елемент з , N/2-ма входами, ви ходи N - 1 елементів "ИЛИ" підключені до перших N - 1 виходів перетворювача коду, 1-й стовпець N/2 блоків елементів "И", причому виходи N/2 елементів "И" кожного блоку підключені до N/2 виходів кожного блоку, а N входів елементів кожного блоку підключені до N входів кожного блоку, перший вихід першого блоку елементів «И» підключений до другого елементу "ИЛИ" 1-го стовпця елементів "ИЛИ" (номер елементу "ИЛИ" в стовпці елементів "ИЛИ" вибирається, як сума номера блоку елементів "И" та номер його виходу № ИЛи №бл + №в), N/2 вихід першого блоку елементів "И" підключений до (N/2 + 1) елементу "ИЛИ" 1-го стовпця елементів "ИЛИ", K-й вихід L-го блоку елементів "И" підключений до (К + І_)-го елементу "ИЛИ" 1-го стовпця елементів "ИЛИ", (N/2 - 1)-й вихід N/2го блоку елементів "И" підключений до N - 1 елементу "ИЛИ", N/2 вихід N/2 блоку елементів «И» підключений до N-ro виходу перетворювача коду, 1-й управляючий та 1-й операційний пристрої, кожний з яких містить N/2 входи та N/2 виходи, причому N/2 входи 1-го управляючого пристрою підключені до перших N/2 входів перетворювача коду, перший вихід 1-го управляючого пристрою підключений до перших входів N/2 елементів "И" першого блоку елементів "И" та до 1-го елементу "ИЛИ" 1-го стовпця елементів "ИЛИ", F-й вихід управляючого пристрою підключений до перших входів N/2 елементів «И» F-ro блоку елементів "И" та до F-ro елементу "ИЛИ" 1-го стовпця елементів "ИЛИ", N/2 вихід управляючого пристрою підключений до перших входів N/2 елементів "И" та до N/2 елементу "ИЛИ" 1-го стовпця елементів "ИЛИ", перший вихід операційного пристрою підключений до другого входу першого елементу "И" кожного блоку елементів "И" та до першого елементу "ИЛИ" 1-го стовпця елементів "ИЛИ", S-й вихід операційного пристрою підключений до другого входу 8-го елементу "И" кожного блоку елементів "И" та до 8-го елементу "ИЛИ" 1 -го стовпця елементів "ИЛИ", N/2 вихід операційного пристрою підключений до другого входу N/2-го елементу "И" кожного блоку елементів "И" та до N/2-го елементу "ИЛИ" 1-го стовпця елементів "ИЛИ", крім того 1-й управляючий та 1-й операційний пристрої містять 2-п перетворювачі коду, виходи яких підключені до виходів, а входи до входів 1-го управляючого та 1го операційного пристроїв ВІДПОВІДНО, причому кожний другий перетворювач коду містить 2-й стовпець N/2 - 1 елементів "ИЛИ, 2-й стовпець N/4 блоків елементів «И», кожний з яких містить N/4 елементів "И", 2-й управляючий та 2-й операційний пристрої, причому N/4 входи 2-го управляючого пристрою та N/4 входи другого операційного пристрою підключені до N/2 входів 2-х перетворювачів коду в 1-му управляючому та в1-му операційному пристроях, виходи 2-х управляючих та операційних пристроїв підключені до входів 2-х стовпців елементів "И" та других стовпців елементів "ИЛИ", виходи 2-х стовпців елементів "И" підключені до входів 2-х стовпців елементів "ИЛИ", виходи 2-х стовпців елементів "ИЛИ" підключені до виходів 2-х перетворювачів коду в 1-му управляючому та в 1-му операційному пристроях, крім того Р-ті (Р = 2, 3, 4, ) управляючі та Р-ті операційні пристрої містять (Р + 1)-ті перетворювачі коду, виходи яких підключені до виходів, а входи до входів Р-го управляючого та Р-го операційного пристроїв ВІДПОВІДНО, причому кожний (Р + 1)-й перетворювач коду містить (Р + 1)-й стовпець елементів "ИЛИ" (Р + 1)-й стовпець 2 Р блоків елементів «И», кожний з яких міс 50077 N тить по | т^~ + "1 І елементів «И», (Р + 1)-й управляючий та (Р + 1)-й операційний пристрої, причому входи (Р + 1)-го управляючого пристроїв P 2 та 8 и вузлах Кожний модуль 9 містить елемент "ИЛИ" 7 та елемент «И» 8 Перетворювач містить чотири входи 1і - І4 або І5 - Is та чотири виходи 2і - 2^ або Зі - З4, в залежності від того, яку функцію виконує управляючу чи операційну ВІДПОВІДНО Перетворювач коду містить (Фіг1) ВІСІМ ВХІДНИХ 1-і - Is, ВІСІМ вихідних 6і - 6s шин та модулі _N_ 2 Р входи (Р + 1)-го операційного пристроN їв підключені до — входів (Р + 1)-х перетворювачів коду в Р-му управляючому та в Р-му операційному пристроях, виходи (Р + 1)-х управляючих та операційних пристроїв підключені до входів (Р + 1)-х стовпців елементів «И» та до (Р + 1)-х стовпців елементів "ИЛИ", виходи (Р + 1)-х стовпців елементів "И" підключені до входів (Р + 1)-х стовпців елементів "ИЛИ", виходи (Р + 1)-х стовпців елементів "ИЛИ" підключені до виходів (Р + 1)-х перетворювачів коду в Р-му управляючому та в Рму операційному пристроях, крім того передостанні управляючі та операційні пристрої містять останні перетворювачі коду, 8 виходів яких підключені до 8 виходів, а 8 входів до 8 входів передостанніх управляючих та операційних пристроїв ВІДПОВІДНО, N/8 останніх перетворювачів коду підключені до N входів перетворювача коду, причому кожний останній перетворювач коду містить останній стовпець 7-х елементів "ИЛИ", останній стовпець 4-х блоків елементів "И", кожний з яких містить по 4 елементи «И», останні управляючі та останні операційні пристрої, причому по 4 входи останніх управляючих пристроїв підключені до 8 входів останніх перетворювачів коду в передостанніх управляючому та в передостанніх операційних пристроїв підключені до входів останніх стовпців елементів «И» та до останніх стовпців елементів "ИЛИ", виходи останніх стовпців елементів "И" підключені до входів останніх стовпців елементів "ИЛИ", виходи останніх стовпців елементів "ИЛИ", виходи останніх стовпців елементів "ИЛИ" підключені до виходів останніх перетворювачів коду в передостанніх управляючих та в передостанніх операційних пристроях, крім того останні управляючі та операційні пристрої містять прямокутні та пірамідальні матриці модулів елементів "ИЛИ" та "И", причому 4 входи прямокутних матриць модулів елементів "ИЛИ" та "И" підключені до 4-х входів останніх управляючих та операційних пристроїв, а 4 виходи прямокутних та пірамідальних матриць підключені до 4 виходів управляючих та операційних пристроїв На Фіг 1 приведена схема перетворювача коду для одержання 8-ми розрядного ущільненого коду Пристрій містить входи 1, 4-х розрядний управляючий пристрій 2, 4-х розрядний операційний пристрій 3, стовпець 4 елементів "И", розміщених в 4х блоках 4 1, 4 2, 4 3, 4 4, стовпець 5 елементів "ИЛИ" та виходи 6 На Фіг 2 приведена схема 4-х розрядного перетворювача коду, який реалізує управляючий пристрій 2 та операційний пристрій 3 Цей перетворювач коду містить пірамідальну матрицю 11, яка складається з одного модуля 9 та прямокутну матрицю 10 з чотирма модулями 9, які розміщені в 9 (Фіг 2), кожний з яких має елемент 7 "ИЛИ" та елемент 8 "И", входи яких з'єднані з входами модуля 9, вихід елементу "ИЛИ" підключений до першого виходу модуля 9, вихід елементу "И" - до другого виходу модуля 9, по чотири модулі 9 розміщені у вузлах прямокутних (2 х 2) матриць Ю т а по 1-му модулю - у вузлах пірамідальних матриць 11, при цьому виходи прямокутних матриць 10 підключені до входів пірамідальних матриць 11, в прямокутних матрицях 10 входи модулів першого стовпця та виходи модулів останнього стовпця з'єднані ВІДПОВІДНО з входами та виходами цих матриць, а в другому стовпці входи модулів першого рядка підключені до перших виходів модулів першого та другого рядків першого стовпця, входи модуля другого рядка з'єднані з другими виходами модулів першого рядка, в пірамідальних матрицях перший та четвертий входи ВІДПОВІДНО з'єднані з першим 2і та четвертим 24 виходами управляючого пристрою 2 або з першим Зі та четвертим З4 виходами операційного пристрою 3, 2-й та 3-й входи прямокутних матриць 10 підключені до входів модуля першого стовпця пірамідальних матриць 11, при цьому виходи цього модуля підключені до 22-го та 2з-го виходів в управляючому пристрої 2 та до Зг-го та Зз-го виходів в операційному пристрої 3 ВІДПОВІДНО, входи прямокутних матриць підключені до входів (1і - І4) управляючого пристрою 2 та до входів (І5 - 1s) операційного пристрою 3 Крім того, перетворювач коду містить (Фіг1) один стовпець 5 з 7-ми елементів "ИЛИ", який має по 2 елемента з 2-ма (елем 5-і, 67), 3-ма (елем 5г, 5є), 4-ма (елем 5з, 5s) входами та один елемент 54 з 5-ма входами, виходи 7-ми елементів "ИЛИ" підключені до перших 7-ми виходів (6і - 67) перетворювача коду, містить один стовпець 4 з 4-х блоків елементів "И" (4і - 44), причому виходи 4-х елементів "И" кожного блоку підключені до 4-х виходів кожного блоку, а 8 входів елементів кожного блоку підключені до 8 входів кожного блоку, перший вихід першого блоку елементів "И" підключений до елементу 52 стовпця 5 елементів "ИЛИ", 4й вихід першого блоку елементів "И" підключений до елементу 5б стовпця 5 елементів "ИЛИ", г-й вихід s-ro блоку (г = 1, 2, 3, 4, s = 1, 2, 3 ,4) елементів "И" підключений до елементу 5 r + s стовпця 5 елементів "ИЛИ", 3-й вихід блоку 44 елементів "И" підключений до елементу 57 стовпця 5 елементів "ИЛИ", 4-й вихід блоку 44 елементів "И" підключений до виходу 6s перетворювача коду, містить управляючий 2 та операційний 3 пристрої, кожний з яких містить 4 входи та 4 виходи, причому 4 входи управляючого пристрою 2 підключені до перших 4-х входів (1і - І4) перетворювача коду, перший вихід 2і управляючого пристрою 2 підключений до перших входів 4-х елементів "И" блоку 4і елементів "И" та до елементу 5і стовпця 5 елементів "ИЛИ", вихід 1j управляючого пристрою 2 підключений до перших входів 4-х елеме 507 07 Kx=N-l (3) нтів "И" блоку 4г елементів "И" та до елементу 5г стовпця 5 елементів "ИЛИ", вихід 2з управляючого пристрою 2 підключений до перших входів 4-х елементів "И" блоку 4з елементів "И" та до елементу 5з стовпця 5 елементів "ИЛИ", вихід 1&, управляючого пристрою 2 підключений до перших входів 4-х елементів "И" блоку А&, елементів "И" та до 4-го елементу 54 стовпця 5 елементів "ИЛИ", g-й вихід (д = 1, 2, 3, 4) операційного пристрою 3 підключений до другого входу g-го елементу "И" кожного блоку (4і - А&) стовпця 4 елементів "И" та до елементу 5д стовпця 5 елементів "ИЛИ" Перетворювач коду працює слідуючим чином Якщо на входи 1 (Фіг 1) подати 8-ми розрядний двійковий код, то на виходах управляючого 2 та операційного 3 пристроях одержимо два 4-х розрядних коди, в яких всі ЛОГІЧНІ " 1 " будуть ущільнені та зсунуті вверх Після проходження цих кодів через стовпець 4 елементів "И" та стовпець 5 елементів "ИЛИ" на виходах 6 одержимо ущільнений код, в якому всі ЛОГІЧНІ " 1 " будуть зсунуті вверх, а всі ЛОГІЧНІ "0" будуть зсунуті вниз Запропонований пристрій дозволяє зменшити часові витрати в порівнянні з прототипом При побудові N-розрядного (N = 2 т , т = 3, 4, 5, 6 ) перетворювача коду, необхідно використати два N/2 розрядних, описаних в прототипі, перетворювача, один з яких буде управляючим, а другий операційним, а також стовпець елементів "И" та стовпець елементів "ИЛИ" Якщо t - час спрацювання одного елементу "И" чи "ИЛИ", то часові витрати Т для перетворювача будуть визначатися з формули T = Krt, (1) де К, - КІЛЬКІСТЬ стовпців елементів "И" та "ИЛИ" В запропонованому пристрої К, = «2 і обчислюється як А в прототипі К, = 1 0 ВІДПОВІДНО часові витрати для кожного з пристроїв будуть обчислюватися з формул та Обчислимо границю відношення Т lim — = lim N-1 (4) Як видно з формули (4), часові витрати в запропонованому пристрої, при збільшенні розрядності пристрою, мають значно менші значення , ніж в прототипі Оцінимо апаратні витрати в обох пристроях В запропонованому пристрої апаратні витрати визначаються по формулі Z, h •+К, 2 1С (5) N В прототипі z, = І де Z1.Z2 - КІЛЬКІСТЬ двовходових елементів "И" та "ИЛИ " Якщо підставити в формули (5) та (6) значення N, то можна помітити, що витрати в апаратурі не перевищують 15% від витрат в прототипі для кожного значення N Запропонований перетворювач коду , як видно з опису, можливо реалізувати в промислових умовах, оскільки в пристрої застосована елементна база широкого вжитку 11 50077 ДП «Український інститут промислової власності» (Укрпатент) вул Сім'ї Хохлових, 15, м Київ, 04119, Україна ( 0 4 4 ) 4 5 6 - 2 0 - 90 ТОВ "Міжнародний науковий комітет" вул Артема, 77, м Київ, 04050, Україна (044)216-32-71 12

ДивитисяДодаткова інформація

Назва патенту англійськоюCode converter

Автори англійськоюZhukov Ihor Anatoliiovych, Hamaiun Volodymyr Petrovych

Назва патенту російськоюПреобразователь кода

Автори російськоюЖуков Игорь Анатольевич, Гамаюн Владимир Петрович

МПК / Мітки

МПК: H03M 7/00

Мітки: коду, перетворювач

Код посилання

<a href="https://ua.patents.su/6-50077-peretvoryuvach-kodu.html" target="_blank" rel="follow" title="База патентів України">Перетворювач коду</a>