Відбивач струму

Номер патенту: 89903

Опубліковано: 12.05.2014

Автори: Діденко Михайло Володимирович, Богомолов Сергій Віталійович, Азаров Олексій Дмитрович

Формула / Реферат

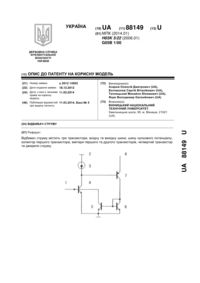

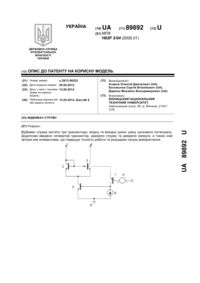

Відбивач струму, який містить два транзистори, вхідну та вихідну шини, шину нульового потенціалу, причому вхідну шину з'єднано з колектором та базою першого транзистора, а також з базою другого транзистора, емітери першого та другого транзисторів з'єднано з шиною нульового потенціалу, колектор другого транзистора з'єднано з вихідною шиною, який відрізняється тим, що у нього введено п'ять транзисторів, джерело струму та джерело напруги, причому бази першого, другого та четвертого транзисторів з'єднано між собою, емітери першого та другого транзисторів з'єднано з колектором третього транзистора, емітери четвертого та п'ятого транзисторів з'єднано з другим виводом джерела струму, база п'ятого транзистора з'єднано з другим виводом джерела напруги, перший вивід джерела напруги з'єднано з шиною нульового потенціалу, колектор четвертого транзистора з'єднано з колектором сьомого транзистора та базами шостого та сьомого транзисторів, колектор п'ятого транзистора з'єднано з колектором шостого та базою третього транзистора, перший вивід джерела струму та емітери третього, шостого, сьомого транзисторів з'єднано з шиною нульового потенціалу.

Текст

Реферат: UA 89903 U UA 89903 U 5 10 15 20 25 30 35 40 45 50 55 60 Корисна модель належить до аналогової техніки і може бути використана в двотактних підсилювальних схемах. Відомо відбивач струму (U.S. Patent, Current mirror for low supply voltage operation, Craig M. Brannon et al.; Fig 2; Patent Number 5,311,146; Data of Patent May. 10, 1994), який містить три транзистори, вхідну та вихідну шини, шину нульового потенціалу, два резистори причому, вхідну шину з'єднано з колектором першого транзистора, а також з базою третього транзистора, емітери першого та другого транзисторів відповідно з'єднані з першим виводом першого та другого резисторів, другі виводи першого та другого резисторів об'єднано та з'єднано з шиною нульового потенціалу, бази першого та другого транзисторів об'єднано та з'єднано з емітером другого транзистора, колектор третього транзистора з'єднано з шиною нульового потенціалу, колектор другого транзистора з'єднано з вихідною шиною. Таким чином схема забезпечує засіб отримання опорного струму, що не залежить від параметрів приладів, проте недоліком є обмежена функціональна можливість. За прототип вибрано відбивач струму (U.S. Patent, Current mirror circuit, Carsten Rasmussen et al.; Fig 2; Patent Number 6,657,481 B2; Data of Patent Dec. 2, 2003), який містить шину нульового потенціалу, вхідну та вихідну шини, два транзистори, два резистора та джерело струму, причому вхідну шину з'єднано з першим виводом джерела струму, другий вивід джерела струму з'єднано з колектором та базою першого транзистора, а також з базою другого транзистора, емітери першого та другого транзисторів з'єднано з першим виводом першого та другого резисторів відповідно, другі виводи першого та другого резисторів з'єднано з шиною нульового потенціалу, колектор другого транзистора з'єднано з вихідною шиною. Таким чином схема забезпечує засіб отримання опорного струму, проте недоліком є велика похибка передачі сигналу. Недоліком прототипу є низька точність роботи пристрою та високий вхідний опір. В основу корисної моделі поставлено задачу створення відбивача струму, в якому за рахунок введення нових елементів та зв'язків між ними, за умови, що генератор вхідного сигналу має обмежений опір, підвищується точність роботи, це розширює галузь використання корисної моделі у різноманітних пристроях імпульсної та обчислювальної техніки, автоматики тощо. Поставлена задача вирішується тим, що у відбивач струму, який містить два транзистори, вхідну та вихідну шини, шину нульового потенціалу, причому вхідну шину з'єднано з колектором та базою першого транзистора, а також з базою другого транзистора, емітери першого та другого транзисторів з'єднано з шиною нульового потенціалу, колектор другого транзистора з'єднано з вихідною шиною, введено п'ять транзисторів, джерело струму та джерело напруги, причому бази першого, другого та четвертого транзисторів з'єднано між собою, емітери першого та другого транзисторів з'єднано з колектором третього транзистора, емітери четвертого та п'ятого транзисторів з'єднано з другим виводом джерела струму, база п'ятого транзистора з'єднано з другим виводом джерела напруги, перший вивід джерела напруги з'єднано з шиною нульового потенціалу, колектор четвертого транзистора з'єднано з колектором сьомого транзистора та базами шостого та сьомого транзисторів, колектор п'ятого транзистора з'єднано з колектором шостого та базою третього транзистора, перший вивід джерела струму та емітери третього, шостого, сьомого транзисторів з'єднано з шиною нульового потенціалу. На кресленні представлено схему відбивача струму. Пристрій мітить сім транзисторів, вхідну 1 та вихідну 2 шини, шину нульового потенціалу 8, джерело струму 9 та джерело напруги 12, причому вхідну шину 1 з'єднано з колектором та базою першого транзистора 2, а також з базою другого транзистора 5, колектор якого з'єднано з вихідною шиною 4, бази першого 1, другого 5 та четвертого 6 транзисторів з'єднано між собою, емітери першого 2 та другого 5 транзисторів з'єднано з колектором третього транзистора 3, емітери четвертого 6 та п'ятого 10 транзисторів з'єднано з другим виводом джерела струму 9, база п'ятого 10 транзистора з'єднано з другим виводом джерела напруги 12, перший вивід джерела напруги 12 з'єднано з шиною нульового потенціалу 8, колектор четвертого транзистора 6 з'єднано з колектором сьомого транзистора 11 та базами шостого 7 та сьомого 11 транзисторів, колектор п'ятого транзистора 10 з'єднано з колектором шостого транзистора 7 та базою третього транзистора 3, перший вивід джерела струму 9 та емітери третього 3, шостого 7, сьомого 11 транзисторів з'єднано з шиною нульового потенціалу 8. Пристрій працює таким чином. Вхідний сигнал у вигляді струму надходить на вхідну шину 1. Якщо вхідний струм втікає у схему, то збільшується падіння напруги на першому транзисторі 2 у діодному вмиканні, та базовий струм другого 5, четвертого 6 транзисторів. При цьому другий транзистор 5 привідкривається і струм вихідної шини 4 збільшується. Збільшення базового струму четвертого 1 UA 89903 U 5 10 15 20 25 транзистора 6 призводить до його призакривання та зменшення його колекторного струму, що у свою чергу призводить до збільшення колекторного струму п'ятого транзистора 10, при цьому він привідкривається, що призводить до збільшення базового струму третього транзистора 3. При зменшенні колекторного струму четвертого транзистора 6 зменшується падіння напруги на сьомому транзисторі 11 у діодному вмиканні та, відповідно, зменшується базовий струм шостого транзистора 7, при цьому він призакривається. При цьому збільшується базовий струм третього транзистора 3 і він привідкривається, що призводить до збільшення колекторного струму третього транзистора 3. Це призводить до врівноваження падіння напруги на першому транзисторі 2 у діодному вмиканні. Якщо вхідний струм витікає зі схеми, то зменшується падіння напруги на першому транзисторі 2 у діодному вмиканні, та базовий струм другого 5, четвертого 6 транзисторів. При цьому другий транзистор 5 призакривається і струм вихідної шини 4 зменшується. Зменшення базового струму четвертого транзистора 6 призводить до його привідкривання та збільшення його колекторного струму, що у свою чергу призводить до зменшення колекторного струму п'ятого транзистора 10, при цьому він призакривається, що призводить до зменшення базового струму третього транзистора 3. При збільшенні колекторного струму четвертого транзистора 6 збільшується падіння напруги на сьомому транзисторі 11 у діодному вмиканні та, відповідно, збільшується базовий струм шостого транзистора 7, при цьому він привідкривається. При цьому зменшується базовий струм третього транзистора 3 і він призакривається, що призводить до зменшення колекторного струму третього транзистора 3. Це призводить до врівноваження падіння напруги на першому транзисторі 2 у діодному вмиканні. Джерело напруги 12 слугує для завдання базової напруги п'ятого транзистора 10. Джерело струму 9 задає робочий струм для роботи четвертого 6 та п'ятого 10 транзисторів. Точка об'єднання емітерів третього 3, шостого 7, сьомого 11 транзисторів, першого вивода джерела струму 9 та першого вивода джерела напруги 9 утворюють шину нульового потенціалу 8. Джерела струму 9 та напруги 12, четвертий 6, п'ятий 10, шостий 7, сьомий 11 та третій 3 транзистори утворюють коло від'ємного зворотного зв'язку між базою другого 5 та емітером першого 2 транзисторів. Введення цього від'ємного зворотного зв'язку зменшує вхідний опір схеми. Це призведе до збільшення точності роботи схеми. 30 ФОРМУЛА КОРИСНОЇ МОДЕЛІ 35 40 45 Відбивач струму, який містить два транзистори, вхідну та вихідну шини, шину нульового потенціалу, причому вхідну шину з'єднано з колектором та базою першого транзистора, а також з базою другого транзистора, емітери першого та другого транзисторів з'єднано з шиною нульового потенціалу, колектор другого транзистора з'єднано з вихідною шиною, який відрізняється тим, що у нього введено п'ять транзисторів, джерело струму та джерело напруги, причому бази першого, другого та четвертого транзисторів з'єднано між собою, емітери першого та другого транзисторів з'єднано з колектором третього транзистора, емітери четвертого та п'ятого транзисторів з'єднано з другим виводом джерела струму, база п'ятого транзистора з'єднано з другим виводом джерела напруги, перший вивід джерела напруги з'єднано з шиною нульового потенціалу, колектор четвертого транзистора з'єднано з колектором сьомого транзистора та базами шостого та сьомого транзисторів, колектор п'ятого транзистора з'єднано з колектором шостого та базою третього транзистора, перший вивід джерела струму та емітери третього, шостого, сьомого транзисторів з'єднано з шиною нульового потенціалу. 2 UA 89903 U Комп’ютерна верстка А. Крулевський Державна служба інтелектуальної власності України, вул. Урицького, 45, м. Київ, МСП, 03680, Україна ДП “Український інститут промислової власності”, вул. Глазунова, 1, м. Київ – 42, 01601 3

ДивитисяДодаткова інформація

Автори англійськоюAzarov Oleksii Dmytrovych, Bohomolov Serhii Vitaliiovych

Автори російськоюАзаров Алексей Дмитриевич, Богомолов Сергей Витальевич

МПК / Мітки

МПК: H03F 3/04

Код посилання

<a href="https://ua.patents.su/5-89903-vidbivach-strumu.html" target="_blank" rel="follow" title="База патентів України">Відбивач струму</a>

Попередній патент: Відбивач струму

Наступний патент: Пристрій для газодинамічного нанесення покриттів з осьовою подачею порошкового матеріалу

Випадковий патент: Пристрій очищення мастильно-охолодної рідини від механічних домішок