Пристрій канального кодування

Номер патенту: 10481

Опубліковано: 15.11.2005

Автори: Кадук Олександр Володимирович, Марценюк Валерій Пантелеймонович

Формула / Реферат

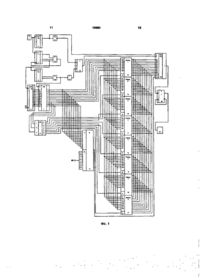

Пристрій канального кодування, який містить генератор синхроімпульсів, перший, другий та третій лічильники імпульсів, інвертор, елемент І, схему 2І-НІ, формувач імпульсів, перший та другий лічильні тригери, перший та другий регістри зсуву, дешифратор, паралельний регістр, перший, другий, третій та четвертий блоки пам'яті, блок запису, цифровий компаратор, шину опорного коду та вхідну шину, причому вхідна шина під'єднана до інформаційного входу першого регістра зсуву, вхід синхронізації якого з'єднаний зі входом синхронізації третього лічильника імпульсів третім виходом другого лічильника імпульсів, вихід генератора синхроімпульсів під'єднано до входів синхронізації першого та другого лічильника імпульсів, вхід інвертора з'єднано з входом синхронізації паралельного регістра, а вихід першого інвертора під'єднано до входу синхронізації першого лічильного тригера, вихід якого під'єднано до входу встановлення режиму роботи другого регістра зсуву, а вхід встановлення нуля зв'язано з виходом формувача імпульсів, перший-десятий входи паралельного регістра під'єднано до першого-десятого виходів першого регістра зсуву, а перший-десятий виходи паралельного регістра з'єднано з першим-десятим входами цифрового компаратора, входи якого також з'єднано з шиною опорного коду, перший-восьмий виходи паралельного регістра з'єднано з першим-восьмим входами першого та другого блока пам'яті, перші-десяті виходи першого та другого блока пам'яті під'єднано до першого-десятого інформаційного входу другого регістра зсуву, вихід цифрового компаратора під'єднано до одинадцятого входу третього регістра, вихід якого з'єднано з входом синхронізації другого тригера, прямий вихід якого під'єднано до блока запису, а інверсний - до свого інформаційного входу, перший-другий вихід третього лічильника імпульсів під'єднано до першого-другого входу схеми 2І-НІ, виходи якої з'єднано з входом синхронізації паралельного регістра та формувача імпульсів, вихід першого лічильника імпульсів під'єднано до входу інвертора, перший-третій виходи другого лічильника імпульсів під'єднано до першого-третього входів елемента І відповідно, вихід якого з'єднано з входом встановлення в одиницю другого лічильника імпульсів, дев'ятий-десятий виходи другого регістра під'єднано відповідно до першого-другого входів дешифратора, перший-четвертий виходи якого під'єднано до входів управління режимами першого, другого, третього та четвертого блоків пам'яті, дешифратор, до першого-третього входів якого під'єднані дев'ятий-одинадцятий виходи паралельного регістра, який відрізняється тим, що в пристрій канального кодування введено п'ятий, шостий, сьомий та восьмий блоки пам'яті, перший-восьмий виходи дешифратора під'єднано до входів управління режимами першого, другого, третього та четвертого, п'ятого, шостого, сьомого, восьмого блоків пам'яті, причому в даній схемі використовується трирозрядний дешифратор.

Текст

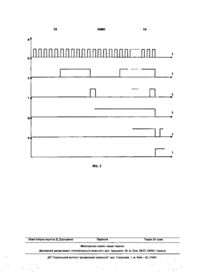

Пристрій канального кодування, який містить генератор синхроімпульсів, перший, другий та третій лічильники імпульсів, інвертор, елемент І, схему 2І-НІ, формувач імпульсів, перший та другий лічильні тригери, перший та другий регістри зсуву, дешифратор, паралельний регістр, перший, другий, третій та четвертий блоки пам'яті, блок запису, цифровий компаратор, шину опорного коду та вхідну шину, причому вхідна шина під'єднана до інформаційного входу першого регістра зсуву, вхід синхронізації якого з'єднаний зі входом синхронізації третього лічильника імпульсів третім виходом другого лічильника імпульсів, вихід генератора синхроімпульсів під'єднано до входів синхронізації першого та другого лічильника імпульсів, вхід інвертора з'єднано з входом синхронізації паралельного регістра, а вихід першого інвертора під'єднано до входу синхронізації першого лічильного тригера, вихід якого під'єднано до входу встановлення режиму роботи другого регістра зсуву, а вхід встановлення нуля зв'язано з виходом формувача імпульсів, перший-десятий входи паралельного регістра під'єднано до першого-десятого виходів першого регістра зсуву, а перший-десятий виходи паралельного регістра з'єднано з першим-десятим входами цифрового компаратора, входи якого також з'єднано з шиною опорного коду, перший восьмий виходи паралельного регістра з'єднано з першим-восьмим входами першого та другого блока пам'яті, перші-десяті виходи першого та другого блока пам'яті під'єднано до першогодесятого інформаційного входу другого регістра зсуву, вихід цифрового компаратора під'єднано до одинадцятого входу третього регістра, вихід якого з'єднано з входом синхронізації другого тригера, прямий вихід якого під'єднано до блока запису, а інверсний - до свого інформаційного входу, перший-другий вихід третього лічильника імпульсів під'єднано до першого-другого входу схеми 2І-НІ, виходи якої з'єднано з входом синхронізації паралельного регістра та формувача імпульсів, вихід першого лічильника імпульсів під'єднано до входу інвертора, перший-третій виходи другого лічильника імпульсів під'єднано до першого-третього входів елемента І відповідно, вихід якого з'єднано з входом встановлення в одиницю другого лічильника імпульсів, дев'ятий-десятий виходи другого регістра під'єднано відповідно до першого-другого входів дешифратора, перший-четвертий виходи якого під'єднано до входів управління режимами першого, другого, третього та четвертого блоків пам'яті, дешифратор, до першого-третього входів якого під'єднані дев'ятий-одинадцятий виходи паралельного регістра, який відрізняється тим, що в пристрій канального кодування введено п'ятий, шостий, сьомий та восьмий блоки пам'яті, першийвосьмий виходи дешифратора під'єднано до входів управління режимами першого, другого, третього та четвертого, п'ятого, шостого, сьомого, восьмого блоків пам'яті, причому в даній схемі використовується трирозрядний дешифратор. ео 00 О> Корисна модель відноситься до обчислювальної техніки, а саме до пристроїв формування сигналів для високощільного запису цифрової інформації на магнітний носій. Відомий пристрій канального кодування [патент України № 36869 м. кл., G11B 5/09, 16.04.2001, бюл. №3-2001], який розрахований на збільшення щільності магнітного запису за рахунок перекодування інформації в канальний код КаутсаФібоначчі з параметрами n=9, m=10, d=0, k=3. Даний пристрій складається з генератора, під'єднаного виходом до лічильного входу першого і другого лічильника імпульсів. Вихід першого лічильника з'єднаний з синхровходом другого регістра 10481 зсуву і через інвертор з синхровходом другого тригера, під'єднаного виходом до керуючого входу регістра зсуву, вихід якого з'єднаний з лічильним входом першого тригера, інверсний вихід якого з'єднано з інформаційним входом цього тригера, а прямим виходом - до блоку запису, який з'єднується з магнітною головкою. Виходи лічильника імпульсів зв'язані через елемент І з його входом скидання в нуль. При цьому один з виходів другого лічильника поєднується через третій лічильник імпульсів, другий інвертор і формувач до входу встановлення в одиницю другого тригера, а також до синхровходу першого регістра зсуву, що зв'язаний через паралельний регістр і перший та другий блоки пам'яті з відповідними входами регістра зсуву. До інформаційного входу Д першого регістра зсуву підключена вхідна шина. Відповідні виходи паралельного регістра з'єднані через цифровий компаратор 18 з одним із входів регістру зсуву, при цьому інші входи цифровогокомпаратора підключені до шини опорного сигналу. Недоліком пристрою є невисока щільність запису внаслідок малого значення вікна детектування. За найближчий аналог обрано пристрій канального кодування [патент України № 36869А м. кл. G11B5/09, 16.04.2001, бюл. № 3], який збільшує вікно детектування при збереженні умови самосинхронізації. Перетворення двійкового коду в канальний код КФ здійснюється із застосуванням генератора синхроімпульсів, першого, другого та третього лічильників імпульсів, інвертора, схеми І, схеми 2І-НІ, другого інвертора, формувача імпульсів, першого та другого лічильного тригера, першого та другого регістрів зсуву, дешифратора, паралельного регістра, першого, другого, третього та четвертого блоків пам'яті, блоку запису, цифрового компаратора, шини опорного коду та вхідної шини, причому вхідна шина під'єднана до інформаційного входу першого регістра зсуву, вхід синхронізації якого з'єднаний зі входом синхронізації третього лічильника імпульсів третім виходом другого лічильника імпульсів, вихід генератора синхроімпульсів під'єднано до входів синхронізації першого та другого лічильника імпульсів, вхід інвертора з'єднано з входом синхронізації паралельного регістра, а вихід першого інвертора під'єднано до входу синхронізації першого лічильного тригера, вихід якого під'єднано до входу встановлення режиму роботи другого регістра зсуву, а вхід встановлення нуля зв'язано з виходом формувача імпульсів, перший-десятий входи паралельного регістру під'єднано до першого-десятого виходів першого регістра зсуву, а перший-десятий виходи паралельного регістра з'єднано з першим-десятим входами цифрового компаратора, входи якого також з'єднано з шиною опорного коду, першийвосьмий виходи паралельного регістра з'єднано з першим-восьмим входами першого та другого блока пам'яті, перші-десяті виходи першого та другого блока пам'яті під'єднано до першогодесятого інформаційного входу другого регістра зсуву, вихід цифрового компаратора під'єднано до одинадцятого входу третього регістра, вихід якого з'єднано з входом синхронізації другого тригера, прямий вихід якого під'єднано до блока запису, а інверсний до свого інформаційного входу, першийдругий вихід третього лічильника імпульсів під'єднано до першого-другого входу схеми 2І-НІ, виходи якої з'єднано з входом синхронізації паралельного регістра та формувача імпульсів, а перший та другий входи першого елемента "І" з'єднано з першим та другим виходами першого лічильника імпульсів, вихід першого елемента "І" під'єднано до входу інвертора, перший-третій виходи другого лічильника імпульсів під'єднано до першоготретього входів другого елемента "І" відповідно, вихід якого з'єднано з входом встановлення в одиницю другого лічильника імпульсів, дев'ятийдесятий виходи другого регістра під'єднано відповідно до першого-другого входів дешифратора, перший-четвертий виходи якого під'єднано до входів управління режимами першого, другого, третього та четвертого блоків пам'яті. Недолік пристрою - недостатня щільність запису цифрової інформації на магнітний носій. В основу винаходу поставлено задачу розробки пристрою канального кодування, в якому за рахунок введення нових блоків та зв'язків між ними досягається збільшення щільності запису інформації на магнітний носій при збереженні умов самосинхронізації, що дозволяє збільшити кількість інформації, яка записується на звичайну магнітну стрічку при використанні перекодування в код Каутса-Фібоначчі з параметрами n=11, m=12, d=0, k=3. Поставлена задача досягається тим, що в пристрій канального кодування, який містить генератор синхроімпульсів, перший, другий та третій лічильники імпульсів, інвертор, схему І, схему 2ІНІ, другий інвертор, формувач імпульсів, перший та другий лічильні тригери, перший та другий регістри зсуву, дешифратор, паралельний регістр, перший, другий, третій та четвертий блоки пам'яті, блок запису, цифровий компаратор, шину опорного коду та вхідну шину, причому вхідна шина під'єднана до інформаційного входу першого регістра зсуву, вхід синхронізації якого з'єднаний зі входом синхронізації третього лічильника імпульсів третім виходом другого лічильника імпульсів, вихід генератора синхроімпульсів під'єднано до входів синхронізації першого та другого лічильника імпульсів, вхід інвертора з'єднано з входом синхронізації паралельного регістра, а вихід першого інвертора під'єднано до входу синхронізації першого лічильного тригера, вихід якого під'єднано до входу встановлення режиму роботи другого регістра зсуву, а вхід встановлення нуля зв'язано з виходом формувача імпульсів, перший-десятий входи паралельного регістру під'єднано до першогодесятого виходів першого регістра зсуву, а перший-десятий виходи паралельного регістра з'єднано з першим-десятим входами цифрового компаратора, входи якого також з'єднано з шиною опорного коду, перший-восьмий виходи паралельного регістра з'єднано з першим-восьмим входами першого та другого блока пам'яті, перші-десяті виходи першого та другого блока пам'яті під'єднано до першого-десятого інформаційного входу другого регістра зсуву, вихід цифрового компара 10481 тора під'єднано до одинадцятого входу третього регістра, вихід якого з'єднано з входом синхронізації другого тригера, прямий вихід якого під'єднано до блока запису, а інверсний до свого інформаційного входу, перший-другий вихід третього лічильника імпульсів під'єднано до першогодругого входу схеми 2І-НІ виходи якої з'єднано з входом синхронізації паралельного регістра та формувача імпульсів, а перший та другий входи першого елемента "І" з'єднано з першим та другим виходами першого лічильника імпульсів, вихід першого елемента "І" під'єднано до входу інвертора, перший-третій виходи другого лічильника імпульсів під'єднано до першого-третього входів другого елемента "І" ВІДПОВІДНО, вихід якого з'єднано з входом встановлення в одиницю другого лічильника імпульсів, дев'ятий-десятий виходи другого регістра під'єднано ВІДПОВІДНО ДО першого-другого входів дешифратора, перший-четвертий виходи якого під'єднано до входів управління режимами першого, другого, третього та четвертого блоків пам'яті введено дешифратор більшої розрядності та п'ятий, шостий, сьомий та восьмий блоки пам'яті, причому дев'ятий-одинадцятий виходи другого регістра під'єднано ВІДПОВІДНО ДО першоготретього входів дешифратора, перший-восьмий виходи якого під'єднано до входів управління режимами першого, другого, третього та четвертого, п'ятого, шостого, сьомого, восьмого блоків пам'яті На Фіг 1 представлено функціональну схему пристрою канального кодування На Фіг 2 представлені часові діаграми роботи пристрою канального кодування Пристрій складається з генератора 1, під'єднаного виходом до лічильного входу першого 2 і другого 3 лічильника імпульсів Вихід першого лічильника 2 з'єднаний з входом інвертора 8 та синхровходом другого регістра зсуву 22, вихід інвертора 8 з єднаний з синхровходом першого тригера 12, вихід якого під'єднаного до керуючого входу другого регістра зсуву 22, вихід якого з'єднаний з лічильним входом другого тригера 23, інверсний вихід якого з'єднано з інформаційним входом цього тригера, а прямий вихід з'єднано з входом блоку запису 24 Вихід блоку запису 24 з'єднується з магнітною головкою (не показаний) Виходи другого лічильника імпульсів 3 зв'язані через елемент "І" 9 з його входом скидання в нуль При цьому один з виходів другого лічильника 3 під'єднаний до синхровходу третього лічильника імпульсів 4 та синхровходу першого регістру 5 Виходи третього лічильника імпульсів 4 під'єднані до входу схеми 2ІНІ 10, вихід якої з'єднано з формувачем імпульсів 11 та синхровходом паралельного регістру 7 Вихід формувача імпульсів 11 з'єднано з входом встановлення в одиницю першого тригера 12 До інформаційного входу D першого регістру 5 підключена вхідна шина 25, перший-одинадцятий інформаційні виходи першого регістру 5 під'єднані до першого-одинадцятого інформаційних входів паралельного регістру 7 Перший-одинадцятий виходи паралельного регістру 7 з'єднані з першимодинадцятим А входами компаратора 13, а входи (В) цифрового компаратора 13 під єднані до шини опорного сигналу 26, вихід цифрового компарато ра 13 з'єднаний з інформаційним входом D12 другого регістра зсуву 22 Перший-восьмий виходи паралельного регістру 7 під'єднані до першоговосьмого адресних входів (А1-А8) першого 14, другого 15, третього 16, четвертого 17, п'ятого 18, шостого 19, сьомого 20 та восьмого 21 блоків пам'яті, виходи яких під єднані до першогоодинадцятого інформаційних входів другого регістра зсуву 22 Дев'ятий, десятий та одинадцятий виходи паралельного регістра 7 під'єднані до входів дешифратора 6, виходи якого з'єднані з входами установки режиму роботи Е ВІДПОВІДНО ДО першого 14, другого 15, третього 16, четвертого 17, п'ятого 18, шостого 19, сьомого 20 та восьмого 21 блоків пам'яті В запропонованому пристрої кодування двійкового одинадцятирозрядного коду в дванадцятирозрядний код Каутса-Фібоначі інформаційне одинадцятирозрядне слово розвертається за допомогою першого регістра 5 з послідовної двійкової форми в паралельну В подальшому за допомогою елементів 14, 15, 16, 17, 18, 19, 20, 21 це слово перетворюється в дванадцятирозрядне кодове слово Каутса-Фібоначі За допомогою третього регістра 22 паралельне кодове дванадцятирозрядне слово Каутса-Фібоначі також переводиться в послідовну форму і подається на блок залису 22 для подальшої реєстрації на магнітний носій (стрічка, диск) Пристрій працює таким чином Вхідний двійковий код розділяють на рівномірні часові ПОСЛІДОВНОСТІ по одинадцять бітових інтервалів, перетворюють за допомогою канальних кодів КаутсаФібоначі в дванадцятисимвольні ПОСЛІДОВНОСТІ І В подальшому в струм запису Сигнал тактової частоти (Фіг 2а), сформований генератором 1 ділиться на 11 за допомогою першого лічильника імпульсів 2 (Фіг 26) та на дванадцять за допомогою другого лічильника імпульсів 3 (Фіг2в) Інформаційні сигнали в двійковому коді з виходу першого регістра 5 записуються в другий регістр 7 в момент позитивного перепаду сигналу, який надходить з виходу схеми 2І-НІ 10 (Фіг 2г) ВИХІДНІ імпульси формувача імпульсів 12 (Фіг2д) надходять на вхід встановлення в одиницю першого тригера 12, вихідний сигнал (Фіг2е) якого подасться на вхід установки режиму роботи Е третього регістра зсуву 22 і встановлює режим паралельного чи послідовного зсуву В блоках пам'яті 14, 15, 16, 17, 18, 19, 20, 21 виконується перекодування інформації з одинадцятирозрядного двійкового коду в дванадцятирозрядний код Каутса-Фібоначчі Третій регістр зсуву 22 перетворює паралельний запис цього коду в послідовний зсув кодової інформації, яка після перетворення надходить в блок запису 24 для формування сигналів запису на магнітний носій В загальному випадку канального кодування інформаційні комбінації з п - символів двійкового вхідного коду замішується групою з m - символів канального коду При цьому відношення числа символів п до m визначає параметр, який називають кодовою швидкістю Vk = n/m Параметр кодової швидкості характеризує 11 10481 12 Фіг. 1 13 10481 ппппппппппп 14 д д в*: Фіг. 2 Комп'ютерна верстка Д. Дорошенко Підписне Тираж 26 прим. Міністерство освіти і науки України Державний департамент інтелектуальної власності, вул. Урицького, 45, м. Київ, МСП, 03680, Україна ДП "Український інститут промислової власності", вул. Глазунова, 1, м. Київ-42, 01601

ДивитисяДодаткова інформація

Назва патенту англійськоюDevice for coding data in a communication channel

Автори англійськоюMartseniuk Valerii Panteleimonovych, Kaduk Oleksandr Volodymyrovych

Назва патенту російськоюУстройство для кодирования данных в канале связи

Автори російськоюМарценюк Валерий Пантелеймонович, Кадук Александр Владимирович

МПК / Мітки

МПК: G11B 5/09

Мітки: пристрій, канального, кодування

Код посилання

<a href="https://ua.patents.su/6-10481-pristrijj-kanalnogo-koduvannya.html" target="_blank" rel="follow" title="База патентів України">Пристрій канального кодування</a>

Попередній патент: Головка циліндрів для двигуна внутрішнього згорання

Наступний патент: Спосіб захисту овочевих культур від шкідливих організмів

Випадковий патент: Система управління автомийкою самообслуговування