Співпроцесор для обчислення значень “прямих” та “обернених” функцій

Номер патенту: 111808

Опубліковано: 10.06.2016

Автори: Лукашенко Валентина Максимівна, Лукашенко Володимир Андрійович, Рудаков Костянтин Сергійович, Зубко Ігор Анатолійович, Лукашенко Андрій Германович, Лукашенко Дмитро Андрійович

Формула / Реферат

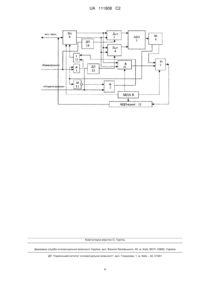

Сопроцесор для обчислення значень "прямих" та "обернених" функцій, що містить перший блок керуючих елементів І, перший вхід якого підключено до керуючого входу "пряма функція", другий блок керуючих елементів І, перший вхід якого підключено до керуючого входу "обернена функція", дешифратор х, дешифратор у, кодові входи яких з'єднані, а виходи підключені через блок елементів АБО до відповідних входів числового блока пам'яті, перші виходи якого підключені до кодових входів регістра, керуючий вхід якого підключено до відповідного керуючого виходу мікропрограмного автомата (ΜΠΑ), зміщуючий регістр входу, кодовий вхід якого є входом пристрою, а вихід підключено до з'єднаних входів дешифраторів х, у та до інформаційних входів блока вентилів, керуючі входи якого підключені до відповідного виходу ΜΠΑ, виходи блока вентилів підключені до лічильних входів регістра, перший керуючий вхід зміщуючого регістра входу підключено до відповідного виходу ΜΠΑ, другий вхід першого блока керуючих елементів І підключено до другого виходу числового блока пам'яті, другий вхід другого блока керуючих елементів І підключено до другого виходу числового блока пам'яті через елемент НІ, крім того, блок МДП-ключів, керуючий вхід якого підключений до відповідного виходу ΜΠΑ, вихід блока МДП-ключів підключений до входу пристрою, який є входом/виходом сопроцесора для обчислення значень "прямих" та "обернених" функцій, який відрізняється тим, що додатково введено елемент АБО , перший вхід якого підключений до виходу першого блока керуючих елементів І, а другий вхід підключений до виходу другого блока керуючих елементів І, вихід елемента АБО підключено до другого керуючого входу зміщуючого регістра входу, також додатково введені перший та другий диференціюючі ланцюги, де вхід першого диференціюючого ланцюга підключений до керуючого входу "пряма функція", а вихід підключений до керуючого входу дешифратора х, вхід другого диференціюючого ланцюга підключений до керуючого входу "обернена функція", а вихід підключений до керуючого входу дешифратора у, крім того, вхід блока МДП-ключів підключено до виходу регістра.

Текст

Реферат: Винахід належить до області обчислювальної техніки. Співпроцесор для обчислення значень "прямих" та "обернених" містить перший блок керуючих елементів І, другий блок керуючих елементів І, дешифратор х та дешифратор у, блок елементів АБО, числовий блок пам'яті, регістр, мікропрограмний автомат, зміщуючий регістр входу, блок вентилів, елемент НІ, елемент затримки, блок МДП-ключів, з відповідними зв'язками, додатково введено елемент АБО перший вхід якого підключений до виходу першого блока керуючих елементів І, а другий вхід підключений до виходу другого блока керуючих елементів І, вихід елемента АБО підключено до другого керуючого входу зміщуючого регістра входу, додатково введено перший UA 111808 C2 (12) UA 111808 C2 та другий диференціюючі ланцюги (ДЛ), вхід першого ДЛ підключений до керуючого входу "пряма функція", а вихід підключений до керуючого входу дешифратора Дш х, вхід другого ДЛ підключений до керуючого входу "обернена функція", а його вихід підключений до керуючого входу дешифратора Дш у, крім того, вихід елемента затримки підключено до третього керуючого входу зміщуючого регістра входу ЗРг, вхід блока МДП-ключів підключено до виходу регістра Рг. Технічним результатом, що досягається даним винаходом, є зменшення потужності споживання щонайменше в 1,5 разу. UA 111808 C2 5 10 15 20 25 30 35 40 45 50 55 60 Винахід належить до обчислювальної техніки й призначається для використання в інформаційних обчислювальних системах, у функціонально-орієнтованих системах спеціального призначення. Відомий пристрій, що вміщує блок пам'яті, регістр, дешифратор функцій, дешифратор аргументу, блок керування, групу елементів "I", розподільний блок, блок комутаторів, групу елементів "АБО" [1] з відповідними зв'язками. Однак при збільшенні точності відтворення прямих та обернених функцій зростає об'єм пам'яті й кількість комутаторів, це збільшує апаратні витрати, збільшує габарити пристрою, зменшує надійність і збільшує вартість пристрою. Найбільш близьким до пропонованого по технічній суті є цифровий пристрій для обчислення прямих та обернених функцій [2], що містить перший блок керуючих елементів І, перший вхід якого підключено до керуючого входу "пряма функція", другий блок керуючих елементів І, перший вхід якого підключено до керуючого входу "обернена функція", дешифратор х, дешифратор у, кодові входи яких з'єднані, а виходи підключені через блок елементів АБО до відповідних входів числового блока пам'яті, перші виходи якого підключені до кодових входів регістра, керуючий вхід якого підключено до відповідного керуючого виходу мікропрограмного автомата (ΜΠΑ), зміщуючий регістр входу, кодовий вхід якого є входом пристрою, а вихід підключено до з'єднаних входів дешифраторів х, у та до інформаційних входів блока вентилів, керуючі входи якого підключені до відповідного виходу ΜΠΑ, а виходи блока вентилів підключені до лічильних входів регістра, перший керуючий вхід зміщуючого регістра входу підключено до відповідного виходу ΜΠΑ, другий вхід першого блока керуючих елементів І підключено до другого виходу числового блока пам'яті, другий вхід другого блока керуючих елементів І підключено до другого виходу числового блока пам'яті через елемент НІ, крім того, блок МДП-ключів, керуючий вхід якого підключений до відповідного виходу ΜΠΑ, вихід блока МДП-ключів підключений до входу пристрою, який є входом/виходом співпроцесора для обчислення значень "прямих" та "обернених" функцій. Проте при збільшенні точності зростає число розрядів і, як наслідок, зростає кількість тригерів у регістрах, що збільшує енергоспоживання пристрою, збільшується нагрів кристалу і, як наслідок, погіршуються умови експлуатації пристрою. Це може призвести до зменшення часу напрацювання на відмову пристрою. Недоліком даного пристрою є велике енергоспоживання. Задача винаходу - зменшення енергоспоживання. Зазначена задача вирішується тим, що в основу винаходу співпроцесора для обчислювання "прямих" та "обернених" функцій поставлено задачу зменшення енергоспоживання при відтворенні значень "прямих" та "обернених" функцій шляхом схемотехнічного рішення. Поставлена задача вирішується тим, що додатково введено елемент АБО 13 перший вхід якого підключений до виходу першого блока керуючих елементів І 1, а другий вхід підключений до виходу другого блока керуючих елементів І 2, вихід елемента АБО 13 підключено до другого керуючого входу зміщуючого регістра входу 9, додатково введені перший 14 та другий 15 диференціюючі ланцюги, вхід першого 14 підключений до керуючого входу "пряма функція", а вихід підключений до керуючого входу дешифратора х 3, вхід другого 15 додатково введеного диференціюючого ланцюга підключений до керуючого входу "обернена функція", а вихід підключений до керуючого входу дешифратора у 4, крім того, вхід блока МДП-ключів 12 підключено до виходу регістра 7. Отже, забезпечується надпідсумковий позитивний ефект, зумовлений сукупністю вказаних ознак, що задовольняє критерію "суттєві відмінності". На фіг. 1 зображена структурна схема співпроцесора для обчислення значень "прямих" та "обернених" функцій. Співпроцесор для обчислення значень "прямих" та "обернених" функцій, що містить перший блок керуючих елементів І 1, перший вхід якого підключено до керуючого входу "пряма функція", другий блок керуючих елементів І 2, перший вхід якого підключено до керуючого входу "обернена функція", дешифратор х 3, дешифратор у 4, кодові входи яких з'єднані, а виходи підключені через блок елементів АБО 5 до відповідних входів числового блока пам'яті 6, перші виходи якого підключені до кодових входів регістра 7, керуючий вхід якого підключено до відповідного керуючого виходу мікропрограмного автомата (ΜΠΑ) 8, зміщуючий регістр входу 9, кодовий вхід якого є входом пристрою, а вихід підключено до з'єднаних входів дешифраторів х 3, у 4 та до інформаційних входів блока вентилів 10, керуючі входи якого підключені до відповідного виходу ΜΠΑ 8, а виходи блока вентилів 10 підключені до лічильних входів регістра 7, перший керуючий вхід зміщуючого регістра входу 9 підключено до відповідного виходу ΜΠΑ 8, другий вхід першого блока керуючих елементів І 1 підключено до другого виходу числового 1 UA 111808 C2 5 10 15 20 25 30 35 40 45 50 55 60 блока пам'яті 6, другий вхід другого блока керуючих елементів І 2 підключено до другого виходу числового блока пам'яті 6 через елемент НІ 11, крім того, блок МДП-ключів 12, керуючий вхід якого підключений до відповідного виходу ΜΠΑ 8, вихід блока МДП-ключів 12 підключений до входу пристрою, який є входом/виходом співпроцесора для обчислення значень "прямих" та "обернених" функцій, додатково введено елемент АБО 13, перший вхід якого підключений до виходу першого блока керуючих елементів І 1, а другий вхід підключений до виходу другого блока керуючих елементів І 2, вихід елемента АБО 13 підключено до другого керуючого входу зміщуючого регістра входу 9, додатково введені перший 14 та другий 15 диференціюючі ланцюги, вхід першого 14 підключений до керуючого входу "пряма функція", а вихід підключений до керуючого входу дешифратора х 3, вхід другого 15 додатково введеного диференціюючого ланцюга підключений до керуючого входу "обернена функція", а вихід підключений до керуючого входу дешифратора у 4, крім того, вхід блока МДП-ключів 12 підключено до виходу регістра 7. Відомо, що потужність споживання одного тригера Ртр. адекватна сумі потужностей споживання чотирьох логічних елементів [3] і нехай дорівнює 40μΒт. Припустимо, розрядність інформаційних операндів, що обробляються, дорівнює n=32, тоді кількість тригерів у одному регістрі Νтр.=n, тоді у прототипі, функціональна схема якого має три регістри, кількість тригерів дорівнює Νпрот.=3Νтр.=3•32=96. При цьому загальна потужність споживання тригерів у прототипі дорівнює Рпрот.=96•40=3840 μΒт. Потрібно відмітити, що порівняння потужностей споживання у прототипі та у запропонованому винаході проводиться при ідентичних умовах формування елементів конструкції, технології виготовлення тригерів. Враховуючі, що у запропонованому співпроцесорі відповідно до структурної схеми (фіг. 1), кількість тригерів складає Nвинах.=2•32=64, тобто на 32 тригерів менше, тоді потужність споживання Рвинах. у запропонованому сопроцесорі зменшується на 40•(Νпрот.-Nвинах.)-40•32=1280 μΒτ. Отже, завдяки оригінальному схемотехнічному рішенню у запропонованому співпроцесорі потужність споживання зменшується в Рпрот./Рвинах.=3840/(3840-1280)=1,5 разу. Співпроцесор для обчислення "прямих" та "обернених" функцій працює таким чином: Після обнуління регістра (Рг), 7 зміщуючого регістра (ЗРг) 9 входу та виходу, вхідна інформація аргументу х записується в регістр ЗРг 9. Команда відтворення операції "пряма функція" надходить одночасно на перший вхід блока керуючих елементів І 1 та на диференціюючий ланцюг (Дл) 14, вихідний імпульс якого приходить на керуючий вхід Дш х 3, на відповідному виході якого з'явиться імпульс, який через блок елементів АБО 5 збуджує відповідну шину числового блока пам'яті 6. Відповідні корегуючі константи з перших виходів числового блока пам'яті 6 надходять на кодовівходи регістра Рг 7 і одиниці коду записуються у відповідні тригери регістра Рг 7. При цьому константа управління зсувом коду інформації для відтворення значень "прямої" функції, з'являється на другому виході числового блока пам'яті 6. Своєчасний зсув вхідної інформації аргументу х в ЗРг 9 на j розрядів праворуч або ліворуч (у залежності від знака j) забезпечується елементами І 1, "АБО" 13. Трансформована по цілих степенях двійки вхідна інформація під дією керуючого імпульсу ΜΠΑ 8 передається через блок вентилів I 10 і надходить на лічильні входи регістра Рг 7, на виході якого з'являється значення "прямої" функції відповідно коду аргументу х, яка надходить на вхід/вихід пристрою з Рг 7 через блок МДПключів 12 під дією керуючого імпульсу, який надходить з відповідного виходу ΜΠΑ 8. Формування значення обернених функцій відрізняється тим, що після обнуління Рг 7, ЗРг 9, вхідна інформація аргументу у записується в ЗРг 9. Одночасно надходить команда відтворення "обернена функція" на перші входи блока керуючих елементів "І" 2 та на вхід диференціюючого ланцюга (Дл) 15, вихідний імпульс якого приходить на керуючий вхід Дш "у" 4, на виході якого з'явиться імпульс, який через блок елементів "АБО" 5 збуджує відповідну шину числового блока пам'яті 6. Відповідні корегуючі константи з перших виходів числового блока пам'яті 6 надходять на кодові входи регістра Рг 7 і одиниці коду записуються у відповідні тригери регістра Рг 7. При цьому константа управління зсувом коду інформації для відтворення "оберненої" функції, з'являється на другому виході числового блока пам'яті 6. Своєчасний зсув інформації в регістрі ЗРг 9 на j розрядів ліворуч або праворуч (тобто протилежно спрямований знаку j) забезпечується елементами НІ 11, І 2, АБО 13. Трансформована по цілих степенях двійки вхідна інформація під дією керуючого імпульсу ΜΠΑ 8 передається через блок вентилів І 10 і 2 UA 111808 C2 5 10 15 надходить на лічильні входи регістра Рг 7, у результаті на виході Рг 7 відтворюється значення "оберненої" функції, яка надходить на вхід/вихід пристрою через блок МДП-ключів 12 під дією керуючого імпульсу, який надходить з відповідного виходу ΜΠΑ 8. Отже, в запропонованому співпроцесорі для обчислення значень "прямих" та "обернених" функцій потужність споживання зменшується в 1,5 разу завдяки оригінальному схемотехнічному рішенню. Джерела інформації: 1. Пат. 53966 А Україна, МПК G06G07/26. Цифровий пристрій для обчислення функцій / В.М. Лукашенко, Д.А. Лукашенко, В.А. Жицький ЧДТУ UA - № 2002042664; Заявл. 03.04.2002; Опубл. 17.02.2003; Бюл. № 2. 2. Пат. 53450 України, МПК G06G 7/00 G06G 7/00. Цифровий пристрій для обчислення прямих та обернених функцій / Лукашенко А.Г., Лукашенко Д.А., Лукашенко В.А., Лукашенко В.М.; заявник Черкаський державний технологічний університет. - № u 201003337; заявл. 22.03.2010; опубл. 11.10.2010, Бюл. № 19 (прототип). 3. Самофалов К.Г., Корнейчук В.І., Тарасенко В.П. Электронные цифровые вычислительные машины. К.: Вища школа, 1986. - 480 с. ФОРМУЛА ВИНАХОДУ 20 25 30 35 40 Співпроцесор для обчислення значень "прямих" та "обернених" функцій, що містить перший блок керуючих елементів І, перший вхід якого підключено до керуючого входу "пряма функція", другий блок керуючих елементів І, перший вхід якого підключено до керуючого входу "обернена функція", дешифратор х, дешифратор у, кодові входи яких з'єднані, а виходи підключені через блок елементів АБО до відповідних входів числового блока пам'яті, перші виходи якого підключені до кодових входів регістра, керуючий вхід якого підключено до відповідного керуючого виходу мікропрограмного автомата (ΜΠΑ), зміщуючий регістр входу, кодовий вхід якого є входом пристрою, а вихід підключено до з'єднаних входів дешифраторів х, у та до інформаційних входів блока вентилів, керуючі входи якого підключені до відповідного виходу ΜΠΑ, виходи блока вентилів підключені до лічильних входів регістра, перший керуючий вхід зміщуючого регістра входу підключено до відповідного виходу ΜΠΑ, другий вхід першого блока керуючих елементів І підключено до другого виходу числового блока пам'яті, другий вхід другого блока керуючих елементів І підключено до другого виходу числового блока пам'яті через елемент НІ, крім того, блок МДП-ключів, керуючий вхід якого підключений до відповідного виходу ΜΠΑ, вихід блока МДП-ключів підключений до входу пристрою, який є входом/виходом співпроцесора для обчислення значень "прямих" та "обернених" функцій, який відрізняється тим, що додатково введено елемент АБО, перший вхід якого підключений до виходу першого блока керуючих елементів І, а другий вхід підключений до виходу другого блока керуючих елементів І, вихід елемента АБО підключено до другого керуючого входу зміщуючого регістра входу, також додатково введені перший та другий диференціюючі ланцюги, де вхід першого диференціюючого ланцюга підключений до керуючого входу "пряма функція", а вихід підключений до керуючого входу дешифратора х, вхід другого диференціюючого ланцюга підключений до керуючого входу "обернена функція", а вихід підключений до керуючого входу дешифратора у, крім того, вхід блока МДП-ключів підключено до виходу регістра. 3 UA 111808 C2 Комп’ютерна верстка О. Гергіль Державна служба інтелектуальної власності України, вул. Василя Липківського, 45, м. Київ, МСП, 03680, Україна ДП “Український інститут інтелектуальної власності”, вул. Глазунова, 1, м. Київ – 42, 01601 4

ДивитисяДодаткова інформація

МПК / Мітки

МПК: G06F 5/01, G06F 17/10, H03K 19/003, G06F 17/14, H03K 19/20, G06F 7/544, G06F 7/38, H03K 19/173, G05F 5/00, G06G 7/00, G06F 7/00, G06F 9/30

Мітки: функцій, значень, обчислення, прямих, співпроцесор, обернених

Код посилання

<a href="https://ua.patents.su/6-111808-spivprocesor-dlya-obchislennya-znachen-pryamikh-ta-obernenikh-funkcijj.html" target="_blank" rel="follow" title="База патентів України">Співпроцесор для обчислення значень “прямих” та “обернених” функцій</a>

Попередній патент: Спосіб антиоксидантного омолодження шкіри обличчя за індріксоном

Наступний патент: Спосіб “плазмон” контролю зносу механізмів і машин

Випадковий патент: Пристрій для гранулювання подрібненої деревини