Аналого-цифровий перетворювач

Номер патенту: 22910

Опубліковано: 05.05.1998

Автори: Ротштейн Олександр Петрович, Ракитянська Ганна Борисівна, Азаров Олексій Дмитрович

Формула / Реферат

Аналого-цифровой преобразователь, содержащий схему сравнения, сумматор аналоговых сигналов, логический блок, цифроаналоговые преобразователи положительного и отрицательного компенсирующих сигналов и регистр, первые выходы которого подключены к входам цифроаналогового преобразователя положительного компенсирующего сигнала, выход которого подключен к первому входу сумматора аналоговых сигналов, выход которого подключен к первому входу схемы сравнения, второй вход которой подключен к аналоговому входу аналого-цифрового преобразователя, выходы которого подключены к выходам логического блока, первые и вторые входы которого подключены к входам цифроаналоговых преобразователей, соответственно, положительного и отрицательного компенсирующих сигналов, а выход цифроаналогового преобразователя отрицательного компенсирующего сигнала подключен ко второму входу сумматора аналоговых сигналов, отличающийся тем, что в аналого-цифровой преобразователь введены блок формирования длительностей импульсов, дешифратор и счетчик, выходы которого подключены к первым входам блока формирования длительностей импульсов, вторые входы которого подключены к выходам дешифратора, входы которого подключены к выходам счетчика, вход запуска которого подключен к входу запуска аналого-цифрового преобразователя и к входу запуска блока формирования длительностей импульсов, выход которого подключен к управляющему входу схемы сравнения, к входу управления записью регистра и к счетному входу счетчика, первый и второй выходы схемы сравнения подключены, соответственно, к информационному входу регистра и к входу останова записи регистра, вторые выходы которого подключены к входам цифроаналогового преобразователя отрицательного компенсирующего сигнала, выходы дешифратора подключены к входам выбора ячеек регистра.

Текст

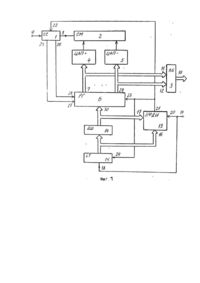

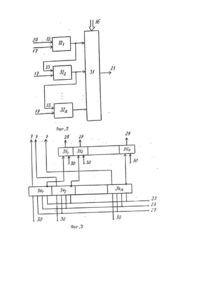

Изобретение относится к вычислительной и цифровой измерительной технике и может быть использовано для преобразования аналоговых величин в цифровые. Известен аналого-цифровой преобразователь [Гитис Э.И., Пискулов Е.А. Аналого-цифровые преобразователи. М., Энергоиздат, 1981, с. 235, рис. 6-7а], содержащий схему сравнения, первый вход которой является входной шиной, второй вход подключен к выходу цифроаналогового преобразователя положительного компенсирующего сигнала, выход - к информационному входу регистра последовательного приближения, первый управляющий вход которого является шиной "запуск", второй управляющий вход подключен к шине тактовых импульсов, выходы подключены к соответствующим входам цифроаналогового преобразователя положительного компенсирующего сигнала. Недостатками данного аналого-цифрового преобразователя являются низкая точность, поскольку не учитываются отклонения весов разрядов от требуемых значений, и низкое быстродействие за счет выбора неоптимальных длительностей тактов уравновешивания и необходимости полной компенсации (до младшего разряда) входной величины компенсирующим сигналом. Известен аналого-цифровой преобразователь [Авт. св. №1221750, М., кл. Н 03 М S 1/26, оп ублик. 1986], содержащий схему сравнения, первый вход которой является входной шиной, второй вход подключен к выходу цифроаналогового преобразователя положительного компенсирующего сигнала, выход - к информационному входу регистра последовательного приближения, первый управляющий вход которого является шиной "запуск", второй управляющий вход подключен к шине тактовых импульсов, выходы подключены к соответствующим входам цифроаналогового преобразователя положительного компенсирующего си гнала, причем аналого-цифровой преобразователь дополнительно содержит блок постоянной памяти, блок суммирования, регистр и счетчик адреса, первый управляющий вход которого объединен с первым управляющим входом регистра и вторым управляющим входом регистра последовательного приближения, второй управляющий вход объединен с вторым управляющим входом регистра и первым управляющим входом регистра последовательного приближения, выходы подключены к соответствующим адресным входам блока постоянной памяти, управляющий вход которого подключен к выходу схемы сравнения, выходы - к соответствующим первым входам блока суммирования, выходы которого подключены к соответствующим информационным входам регистра, выходы которого подключены к соответствующим вторым входам блока суммирования и являются выходными шинами. Недостатком является низкое быстродействие за счет выбора неоптимальных длительностей тактов и необходимости полной компенсации (до младшего разряда) входной величины компенсирующим сигналом. Наиболее близким по технической сущности к заявляемому аналого-цифровому преобразователю является аналого-цифровой преобразователь [Азаров О.Д. Прискорене аналого-цифрове перетворення на основі надлишкових позиційних систем числення // Вісник ВПІ. - 1993. - №1. - С. 22-27], содержащий схему сравнения, сумматор аналоговых сигналов, цифроаналоговые преобразователи положительного и отрицательного компенсирующих сигналов, логический блок, два регистра и блок управления, вход которого подключен к выходу схемы сравнения, первый вход которой подключен к входу аналого-цифрового преобразователя, а второй вход - к выходу сумматора аналоговых сигналов, первый вход которого подключен к выходу генератора форсирующего аналогового сигнала, входы которого подключены к первым выходам блока управления, второй и третий входы сумматора аналоговых сигналов подключены, соответственно, к выходам цифроаналоговых преобразователей положительного и отрицательного компенсирующих сигналов, входы которых подключены, соответственно, к выходам первого и второго регистров, входы которых подключены, соответственно, ко вторым и третьим выходам блока управления, выходы первого и второго регистров подключены, соответственно, к первым и вторым входам логического блока, выходы которого подключены к выходам аналого-цифрового преобразователя. Недостатком данного аналого-цифрового преобразователя является низкое быстродействие из-за необходимости полного перебора всех разрядов регистров и выбора неоптимальных длительностей тактов кодирования. Задача данного изобретения состоит в разработке аналого-цифрового преобразователя, в котором за счет введения новых блоков и связей достигается повышение быстродействия. Решение поставленной задачи достигается путем выбора оптимальных длительностей тактов уравновешивания, а также за счет фиксации момента равенства входного и компенсирующего аналоговых сигналов, что позволяет досрочно завершить процесс преобразования, что повышает быстродействие. Решение поставленной задачи достигается тем, что в аналого-цифровой преобразователь, содержащий схему сравнения, сумматор аналоговых сигналов, логический блок, цифроаналоговые преобразователи положительного и отрицательного компенсирующих сигналов и регистр, первые выходы которого подключены к входам цифроаналогового преобразователя положительного компенсирующего сигнала, вы ход которого подключен к первому входу сумматора аналоговых сигналов, выход которого подключен к первому входу схемы сравнения, второй вход которой подключен к аналоговому входу аналого-цифрового преобразователя, выходы которого подключены к выходам логического блока, первые и вторые входы которого подключены к входам цифроаналоговых преобразователей, соответственно, положительного и отрицательного компенсирующи х сигналов, а вы ход цифроаналогового преобразователя отрицательного компенсирующего сигнала подключен ко второму входу сумматора аналоговых сигналов, введены: блок формирования длительностей импульсов, дешифратор и сче тчик, вы ходы которого подключены к першім входам блока формирования длительностей импульсов, вторые входы которого подключены к выходам дешифратора, входы которого подключены к выходам счетчика, вход запуска которого подключен к входу запуска аналогоцифрового преобразователя и к входу запуска блока формирования длительностей импульсов, выход которого подключен к управляющему входу схемы сравнения, к входу управления записью регистра, к счетному входу счетчика, первый и второй выходы схемы сравнения подключены, соответственно, к информационному входу регистра и к входу останова записи регистра, вторые выходы которого подключены к входам цифроаналогового преобразователя отрицательного компенсирующего сигнала, вы ходы дешифратора подключены к входам выбора ячеек регистра. На фиг. 1 представлена структурная схема аналого-цифрового преобразователя; на фиг. 2 функциональная схема блока формирования длительностей импульсов; на фиг. 3 - функциональная схема регистра. Аналого-цифровой преобразователь (фиг. 1) содержит схему 1 сравнения (СС), сумматор 2 аналоговых сигналов (СМ), логический блок (Л Б) 3, цифроаналоговый преобразователь (ЦАП) 4 положительного компенсирующего сигнала (ЦАП+) и цифро-аналоговый преобразователь 5 отрицательного компенсирующего сигнала (ЦАП-) и регистр (РГ) 6, первые выходы 7 которого подключены к входам ЦАП 4 положительного компенсирующего сигнала, выход которого подключен к первому входу сумматора 2 аналоговых сигналов, выход которого подключен к первому входу 8 СС 1, второй вход которого подключен к аналоговому входу 9 аналого-цифрового преобразователя, выходы 10 которого подключены к выходам ЛБ 3, первые и вторые входы 11, 12 которого подключены к входам ЦАП 4, 5, соответственно, положительного и отрицательного компенсирующего сигналов, а выход ЦАП 5 отрицательного компенсирующего сигнала подключен ко второму входу сумматора 2 аналоговых сигналов, причем аналого-цифровой преобразователь дополнительно содержит блок 13 формирования длительностей импульсов (БФДИ), дешифратор 14 (ДШ) и счетчик (СТ) 15, выходы которого подключены к первым входам 16 БФДИ 13, вторые входы 17 которого подключены к выходам ДШ 14, входы которого подключены к выходам счетчика 15, вход 18 запуска которого подключен к входу 19 запуска аналого-цифрового преобразователя и к входу 20 запуска БФДИ 13, выход 21 которого подключен к управляющему входу 22 схемы 1 сравнения, к входу 23 управления записью регистра 6, к счетному входу 24 счетчика 15. первый и второй выходы 25, 26 СС 1 подключены, соответственно, к информационному входу 27 регистра бик входу 28 останова записи регистра 6, вторые выходы 29 которого подключены к входам ЦАП 5 отрицательного компенсирующего сигнала, выходы ДШ 14 подключены к входам 30 выбора ячеек регистра 6. БФДИ 13 (фиг. 2) содержит коммутатор 31 и группу одновибраторов 321, 322,.... 32n, первые входы которых подключены к соответствующим вторым входам 17 блока 13, а выходы - к соответствующим входам коммутатора 31, входы управления которого подключены к первым входам 16 блока 13, причем выход каждого предыдущего одновибратора 32j подключен ко второму входу 33 каждого последующего одновибратора 32і+1, а вход 20 запуска блока 13 подключен ко второму входу 33 первого одновибратора 32i. Регистр 6 (фиг. 3) содержит группу ячеек 341, 342.....34n , первые входы которых подключены к соответствующим входам 30 выбора ячеек регистра, вторые - к информационному входу 27 регистра, третьи к входу 28 останова записи, четвертые - к входу 23 управления записью, причем первые выходы ячеек 34 подключены к первым выходам 7 регистра 6, вторые выходы ячеек 34 подключены к первым входам соответствующи х элементов И 35, вторые входы элементов И 35 подключены к соответствующим входам 30 выбора ячеек регистра 6, выходы элементов И 351, 352,..., 35n подключены ко вторым выходам 29 регистра 6. ЦАП 4, 5, соответственно положительного и отрицательного компенсирующи х сигналов, должны быть выполнены на основе избыточных измерительных кодов (ПИК). В ПИК любое действительное число можно представить в виде где i - номер разряда; n - количество разрядов преобразователя; аi Î {1, -1} - разрядный коэффициент, ai = 1 соответствует суммированию веса i-го разряда, аі = -1 вычитанию веса і-го разряда. a - основание системы счисления, причем 1.6 < a Ак , то на первом выходе 25 СС 1 присутствует логическая "1", поступающая на информационный вход 27 регистра 6. а если Авх < Ак , то на первом выходе 25 СС 1 присутствует логический "0". Если же Авх = Ак , то, независимо от первого выхода 25, на втором выходе 26 СС 1 появляется единичный сигнал, поступающий на вход 28 останова записи регистра 6. Код счетчика 15 задает номер ячейки регистра 6, в которую необходимо записать разрядный коэффициент "-1" или "1". Конкретная ячейка задается кодом на выходах ДШ 14, поступающего на входы 30 регистра 6 и, если на информационном входе 27 регистра 6 присутствует логическая "1", то ячейка готова к записи "1". Если на информационном входе 27 - логический "0", то ячейка готова к записи "-1". При этом на первых выходах 7 регистра 6 будет присутствова ть код, в котором "1" кодируется как "1", "-1" кодируется как "0", а "0" остается "0". На вторых вы ходах 29 регистра 6 будет присутствовать код, в котором "-1" кодируется как "1", а "1" и "0" кодируются как нули в соответствующих ячейках регистра 6. Например, если код результата преобразования имеет вид 1 -1 1 1 -1 0 0 0, то он разбивается соответственно на следующие коды: 1 0 1 1 0 0 0 0 - код на первых вы ходах 7, 0 1 0 0 1 0 0 0 - код на вторых вы ходах 29. Каждой ячейке регистра 6 соответствует вес разряда выбранной системы счисления. Эти коды поступают, соответственно, на входы ЦАП 4, 5 положительного и отрицательного компенсирующи х сигналов. Кроме того, коды с положительными разрядными коэффициентами поступают по первому входу 11, а коды с отрицательными разрядными коэффициентами - по второму входу 12 ЛБ 3, который осуществляет суммирование (вычитание) двоичных кодов весов разрядов. Коды весов с положительными разрядными коэффициентами суммируются, а коды весов с отрицательными разрядными коэффициентами вычитаются из общей суммы. Результирующий код поступает на цифровые выходы 10 аналого-цифрового преобразователя. По окончании импульса на выходе 21 БФДИ 13, т.е. по окончании такта уравновешивания, регистр 6 будет содержать промежуточный результат преобразования. Содержимое счетчика 15 по заднему фронту импульса на его входе 24 увеличивается на единицу. Код с выхода счетчика 15 поступает на первый вход 16 БФДИ 13. Дешифратор ДШ 14 подготавливает к записи очередную ячейку регистра 6. По переднему фронту сигнала на активном выходе ДШ 14, поступающего на соответствующий вход 17 БФДИ 13 на выходе 21 последнего появляется единичный импульс с длительностью, соответствующей длительности такта с номером, который указывает код счетчика 15 на данный момент времени. СС 1 срабатывает по переднему фронту импульса на ее управляющем входе 22. и, поскольку соответствующая ячейка регистра 6 готова к записи информации, в нее записывается результат сравнения с выхода 25 схемы 1 сравнения. Таким образом, начинается следующий такт преобразования и аналого-цифровой преобразователь начинает функционировать по принципу, описанному выше. В начале каждого такта СС 1 сравнивает суммарный компенсирующий сигнал с выхода сумматора 2 с входным осуществляется запись разрядного коэффициента в ячейку регистра 6, номер которой задан кодом счетчика 15, и в течение такта уравновешивания формируется компенсирующий сигнал. Если Авх = Ак , то на втором выходе 26 СС 1 появляется единичный сигнал, поступающий на вход 28 останова записи, что запрещает дальнейшую запись информации в регистр 6, при этом ранее записанная информация сохраняется. В этом случае прекращается процесс преобразования, и на цифровых вы ходах 10 будет присутствовать код результата преобразования. Если на протяжении процесса преобразования не было случая, когда Авх = Ак , то работа устройства продолжается до полного заполнения всех ячеек регистра 6. БФДИ 13 функционирует следующим образом (фиг. 3). Все одновибраторы 32 настроены на формирование импульса определенно заданной длительности. Запуск каждого одновибратора осуществляется по соответствующему входу 17 и входу 33 запуска. При этом на вход 17 должен прийти передний фронт импульса с соответствующего активного выхода ДШ 14, а на вход 33 запуска должен прийти перед этим задний фронт импульса от предыдущего одновибратора 32. Запуск первого одновибратора 321 осуществляется по переднему фронту сигнала на входе 20 запуска. Код на входах 16 коммутатора 31 указывает на подключение выхода соответствующего одновибратора 32 к выходу 21 блока 13. Длительность импульсов на выходах одновибраторов 321, 322.....32n формируется по следующим зависимостям Регистр 6 (фиг. 3) функционирует следующим образом. Код на выходах 30 кодирует в единично позиционном виде ячейку 34, в которую необходимо записать информацию. На соответствующем входе 30 будет присутствовать логическая "1", а на остальных - логический "0". В выбранную ячейку 34 записывается сигнал с информационного входа 27 регистра. Разрешение на запись дает присутствие логической "1" на входе 23 управления записью. Присутствие логической "1" на входе 28 блокирует дальнейшую запись информации в ячейки 34. На первых 7 и вторых 29 выходах регистра 6 формируются коды соответственно для ЦАП 4, 5 положительного и отрицательного компенсирующих сигналов. Сравнение суммарного компенсирующего сигнала и входного аналогового сигнала на равенство позволяет уменьшить время, затрачиваемое на получение результата преобразования, что достигается путем блокирования записи информации в регистре 6. Повысить быстродействие позволяет также введение БФДИ 13, управляющего схемой 1 сравнения, счетчиком 15 и регистром 6. При этом БФДИ 13 разбивает процесс преобразования (формирования кода) на заранее заданные оптимальные временные интервалы, длительности которых получены по выше приведенным формулам.

ДивитисяДодаткова інформація

Автори англійськоюRotshtein Oleksandr Petrovych, Azarov Oleksii Dmytrovych

Автори російськоюРотштейн Александр Петрович, Азаров Алексей Дмитриевич

МПК / Мітки

МПК: H03M 1/22

Мітки: аналого-цифровий, перетворювач

Код посилання

<a href="https://ua.patents.su/6-22910-analogo-cifrovijj-peretvoryuvach.html" target="_blank" rel="follow" title="База патентів України">Аналого-цифровий перетворювач</a>

Попередній патент: Живильник камерний

Наступний патент: Спосіб визначення вмісту альфа-амінного азоту в буряках

Випадковий патент: Пальник для камери згоряння турбіни внутрішнього згоряння з низькими забруднюючими викидами