Вхідний пристрій схеми порівняння струмів

Номер патенту: 25471

Опубліковано: 10.08.2007

Автори: Гарнага Володимир Анатолійович, Кадук Олександр Володимирович, Решетнік Олександр Олександрович, Азаров Олексій Дмитрович, Богомолов Сергій Віталійович

Формула / Реферат

Вхідний пристрій схеми порівняння струмів, який містить сорок транзисторів, три джерела струму, вхідну шину, шини додатного і від'ємного живлення, шину нульового потенціалу, вихідну шину, причому перше джерело струму своїми виводами з'єднане з колекторами п'ятнадцятого і шістнадцятого транзисторів відповідно та базами тринадцятого і чотирнадцятого транзисторів відповідно, бази п'ятнадцятого і шістнадцятого транзисторів з'єднані з емітерами тринадцятого і чотирнадцятого транзисторів відповідно та з колекторами сімнадцятого і вісімнадцятого транзисторів відповідно, емітери п'ятнадцятого і шістнадцятого транзисторів з'єднані з емітерами третього і четвертого транзисторів відповідно, бази третього і четвертого транзисторів з'єднані з колекторами і базами п'ятого і шостого транзисторів відповідно, а також з базами сімнадцятого і вісімнадцятого транзисторів відповідно, а також з базами сьомого і восьмого транзисторів відповідно, колектори тринадцятого і чотирнадцятого транзисторів з'єднані з базами двадцять дев'ятого і тридцятого транзисторів відповідно, а також з колекторами першого і другого транзисторів відповідно, колектор третього, емітер п'ятого, емітер сімнадцятого, колектор двадцять дев'ятого, емітер сьомого транзисторів з'єднані з шиною додатного живлення, колектор четвертого, емітер шостого, емітер вісімнадцятого, колектор тридцятого, емітер восьмого транзисторів з'єднані з шиною від'ємного живлення, емітер першого транзистора з'єднаний з емітером другого транзистора та шиною нульового потенціалу, бази першого і другого транзисторів з'єднані з базами тридцять третього, першого вхідного та тридцять четвертого, другого вхідного транзисторів відповідно, емітери тридцять третього і тридцять четвертого транзисторів об'єднані між собою, їх колектори з'єднані з базами і колекторами тридцять першого і тридцять другого транзисторів відповідно, а також з базами тридцять п'ятого і тридцять шостого транзисторів відповідно, колектори першого вхідного і другого вхідного транзисторів з'єднані з колекторами сьомого і тридцять п'ятого та восьмого і тридцять шостого транзисторів відповідно, а також з базами дев'ятого і десятого транзисторів відповідно, емітери першого вхідного і другого вхідного транзисторів об'єднані між собою і з'єднані з емітером двадцять шостого та базою і колектором двадцять сьомого транзисторів, емітери тридцять першого, тридцять п'ятого і колектор дев'ятого транзисторів з'єднані з шиною додатного живлення, емітери тридцять другого, тридцять шостого і колектор десятого транзисторів з'єднані з шиною від'ємного живлення, третє джерело струму своїми виводами з'єднано з емітерами дев'ятого і десятого транзисторів відповідно, а також колекторами дев'ятнадцятого і двадцятого транзисторів відповідно, а також з базами двадцять третього і двадцять четвертого транзисторів відповідно, бази дев'ятнадцятого і двадцятого транзисторів з'єднані з базами і колекторами двадцять першого і двадцять другого транзисторів відповідно, а також з емітерами двадцять третього і двадцять четвертого транзисторів відповідно, колектор двадцять третього транзистора з'єднаний з базами і колекторами двадцять п'ятого і одинадцятого та з базою першого вихідного транзисторів, колектор двадцять четвертого транзистора з'єднаний з емітером двадцять восьмого та базою і колектором дванадцятого транзисторів, а також з другим вихідним транзистором, емітери одинадцятого і дванадцятого транзисторів об'єднані між собою, емітери двадцять п'ятого і двадцять сьомого транзисторів з'єднані з базами і колекторами двадцять шостого і двадцять восьмого транзисторів відповідно, емітери дев'ятнадцятого і двадцять першого транзисторів та колектор першого вихідного транзистора з'єднані з шиною додатного живлення, емітери двадцятого і двадцять другого транзисторів та колектор другого вихідного транзистора з'єднані з шиною від'ємного живлення, емітери першого вихідного і другого вихідного транзисторів об'єднані між собою і з'єднані з другим виводом першого резистора, а також з вихідною шиною, який відрізняється тим, що в нього введено шість транзисторів і другий резистор, причому емітери двадцять дев'ятого і тридцятого транзисторів з'єднані з базами і колекторами тридцять сьомого, тридцять дев'ятого та тридцять восьмого, сорок другого транзисторів відповідно, емітери тридцять сьомого і тридцять восьмого транзисторів з'єднані з базами першого і другого транзисторів відповідно, емітери тридцять дев'ятого і сорок другого транзисторів з'єднані з базами і колекторами сорокового і сорок першого транзисторів відповідно, а також з відповідними виводами другого джерела струму, емітери сорокового і сорок першого транзисторів об'єднані, а також з'єднані з першим виводом першого резистора, вхідною шиною і першим виводом другого резистора, другий вивід другого резистора з'єднаний з емітерами першого вхідного і другого вхідного транзисторів.

Текст

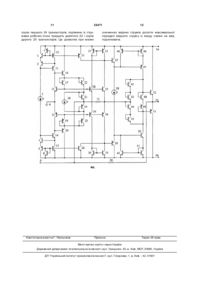

Вхідний пристрій схеми порівняння струмів, який містить сорок транзисторів, три джерела струму, вхідн у шину, шини додатного і від'ємного живлення, шину нульового потенціалу, ви хідну шину, причому перше джерело струму своїми виводами з'єднане з колекторами п'ятнадцятого і шістнадцятого транзисторів відповідно та базами тринадцятого і чотирнадцятого транзисторів відповідно, бази п'ятнадцятого і шістнадцятого транзисторів з'єднані з емітерами тринадцятого і чотирнадцятого транзисторів відповідно та з колекторами сімнадцятого і вісімнадцятого транзисторів відповідно, емітери п'ятнадцятого і шістнадцятого транзисторів з'єднані з емітерами третього і четвертого транзисторів відповідно, бази третього і четвертого транзисторів з'єднані з колекторами і базами п'ятого і шостого транзисторів відповідно, а також з базами сімнадцятого і вісімнадцятого транзисторів відповідно, а також з базами сьомого і восьмого транзисторів відповідно, колектори тринадцятого і чотирнадцятого транзисторів з'єднані з базами двадцять дев'ятого і тридцятого транзисторів відповідно, а також з колекторами першого і другого транзисторів відповідно, колектор третього, емітер п'ятого, емітер сімнадцятого, колектор двадцять дев'ятого, емітер сьомого транзисторів з'єднані з шиною додатного живлення, колектор четвертого, емітер шостого, емітер вісімнадцятого, колектор тридцятого, емітер восьмого транзисторів з'єднані з шиною від'ємного живлення, емітер першого транзистора з'єднаний з емітером другого транзистора та шиною нульового потенціалу, бази першого і другого транзисторів з'єднані з базами тридцять третього, першого вхідного та тридцять четвертого, другого вхідного транзисторів відповідно, емітери тридцять третього і тридцять четвертого транзисторів 2 (19) 1 3 25471 4 резистора, а також з вихідною шиною, який відрізняється тим, що в нього введено шість транзисторів і другий резистор, причому емітери двадцять дев'ятого і тридцятого транзисторів з'єднані з базами і колекторами тридцять сьомого, тридцять дев'ятого та тридцять восьмого, сорок другого транзисторів відповідно, емітери тридцять сьомого і тридцять восьмого транзисторів з'єднані з базами першого і другого транзисторів відповідно, емітери тридцять дев'ятого і сорок другого транзисторів з'єднані з базами і колекторами сорокового і сорок першого транзисторів відповідно, а також з відповідними виводами другого джерела струму, емітери сорокового і сорок першого транзисторів об'єднані, а також з'єднані з першим виводом першого резистора, вхідною шиною і першим виводом другого резистора, другий вивід другого резистора з'єднаний з емітерами першого вхідного і другого вхідного транзисторів. Корисна модель відноситься до імпульсної техніки і може бути використана в аналогово - цифрових перетворювачах і цифрових вимірювальних приладах. Відомий вхідний пристрій схеми порівняння струмів [А.С. №13110 Н 03 К 5/24, G 05 В 1/01, 2006], який містить вхідну шин у яка з'єднана з емітерами першого та другого вхідних транзисторів, їх бази - з колекторами та базами першого і другого транзисторів, та з колекторами тринадцятого і чотирнадцятого транзисторів, колектори першого і другого вхідних транзисторів з'єднані з колекторами сьомого і восьмого транзисторів і базами дев'ятого і десятого транзисторів, емітери першого і другого транзисторів з'єднані з шиною нульового потенціалу, бази тринадцятого і чотирнадцятого транзисторів з'єднані з колекторами п'ятнадцятого і шістнадцятого та з першим і другим виводами другого резистора відповідно, а емітери тринадцятого і чотирнадцятого транзисторів з'єднані з базами п'ятнадцятого і шістнадцятого та колекторами сімнадцятого та вісімнадцятого транзисторів відповідно, емітери п'ятнадцятого і шістнадцятого транзисторів з'єднані з емітерами третього і четвертого транзисторів відповідно, бази третього і четвертого транзисторів з'єднані з базами і колекторами п'ятого і шостого, базами сімнадцятого та вісімнадцятого, базами сьомого і восьмого транзисторів відповідно, колектори третього і четвертого, емітери п'ятого і шостого, емітери сімнадцятого та вісімнадцятого, емітери сьомого і восьмого транзисторів з'єднані з шинами додатного і від'ємного живлення відповідно, колектори дев'ятого та десятого транзисторів з'єднані з шиною нульового потенціалу, а їх емітери - з колекторами дев'ятнадцятого і двадцятого та базами двадцять третього і двадцять четвертого транзисторів відповідно, тоді як бази дев'ятнадцятого і двадцятого транзисторів з'єднані з базами і колекторами двадцять першого і двадцять другого та емітерами двадцять третього і двадцять четвертого транзисторів відповідно, емітери дев'ятнадцятого і двадцятого та двадцять першого і двадцять другого транзисторів з'єднані з шинами додатного і від'ємного живлення відповідно, колектори двадцять третього і двадцять четвертого транзисторів з'єднано з колекторами і базами одинадцятого і дванадцятого транзисторів, а також з базами першого і другого вихідних транзисторів відповідно, крім того колектор двадцять третього транзистора підключений до колек тора і бази двадцять п'ятого транзистора, а колектор двадцять четвертого з'єднаний з емітером двадцять восьмого транзистора, емітери одинадцятого і дванадцятого транзисторів об'єднані між собою, колектори першого та другого вихідних транзисторів приєднані до шин додатного та від'ємного живлення відповідно, а їх емітери об'єднані між собою та є ви ходом пристрою, чотири транзистори, з двадцять п'ятого по двадцять восьмий, включені у діодному режимі, тобто з'єднано їх бази та колектори, і ці транзистори з'єднані послідовно: емітер двадцять п'ятого з'єднано з базою і колектором двадцять шостого, емітер двадцять шостого з'єднано з базою і колектором двадцять сьомого, емітер двадцять сьомого з'єднано з базою і колектором двадцять восьмого, а точка об'єднання емітера двадцять шостого транзистора та бази і колектора двадцять сьомого транзистора з'єднана з шиною вхідного сигналу, вихідна шина з'єднана з вхідною шиною через перший резистор та з шиною нульового потенціалу через третій резистор. Недоліком пристрою є виникнення значних динамічних похибок за умови збільшення рівня вхідного сигналу, що обмежує динамічний діапазон вхідного сигналу. За найближчий аналог обрано вхідний пристрій схеми порівняння струмів [Патент України на корисну модель №20246, Бюл. №1, 2007p.], який містить перше джерело струму, яке своїми виводами з'єднане з колекторами п'ятнадцятого і шістнадцятого транзисторів відповідно та базами тринадцятого і чотирнадцятого транзисторів відповідно, бази п'ятнадцятого і шістнадцятого транзисторів з'єднані з емітерами тринадцятого і чотирнадцятого транзисторів відповідно та з колекторами сімнадцятого і вісімнадцятого транзисторів відповідно, емітери п'ятнадцятого і шістнадцятого транзисторів з'єднані з емітерами третього і четвертого транзисторів відповідно, бази третього і четвертого транзисторів з'єднані з колекторами і базами п'ятого і шостого транзисторів відповідно, а також з базами сімнадцятого і вісімнадцятого транзисторів відповідно, а також з базами сьомого і восьмого транзисторів відповідно, колектори тринадцятого і чотирнадцятого транзисторів з'єднані з базами двадцять дев'ятого і тридцятого транзисторів відповідно, а також з колекторами першого і другого транзисторів відповідно, колектор третього, емітер п'ятого, емітер сімнадцятого, колектор двадцять дев'ятого, емітер сьомого транзисторів 5 25471 з'єднані з шиною додатного живлення, колектор четвертого, емітер шостого, емітер вісімнадцятого, колектор тридцятого, емітер восьмого транзисторів з'єднані з шиною від'ємного живлення, емітер першого транзистора з'єднаний з емітером другого транзистора та шиною нульового потенціалу, емітери двадцять дев'ятого і тридцятого транзисторів з'єднані з виводами другого джерела струму, а також з базами першого, тридцять третього та другого, тридцять четвертого транзисторів відповідно, а також з базами першого вхідного та другого вхідного транзисторів відповідно, емітери тридцять третього і тридцять четвертого об'єднані між собою, їх колектори з'єднані з базами і колекторами тридцять першого і тридцять другого транзисторів відповідно, а також з базами тридцять п'ятого і тридцять шостого транзисторів відповідно, колектори першого вхідного і другого вхідного транзисторів з'єднані з колекторами сьомого і тридцять п'ятого та восьмого і тридцять шостого транзисторів відповідно, а також з базами дев'ятого і десятого транзисторів відповідно, емітери першого і другого вхідних транзисторів об'єднані між собою і з'єднані з емітером двадцять шостого та базою і колектором двадцять сьомого транзисторів, а також з вхідною шиною та з першим виводом першого резистора, емітери тридцять першого, тридцять п'ятого і колектор дев'ятого транзисторів з'єднано з шиною додатного живлення, емітери тридцять другого, тридцять шостого і колектор десятого транзисторів з'єднано з шиною від'ємного живлення, третє джерело струму своїми виводами з'єднано з емітерами дев'ятого і десятого транзисторів відповідно, а також колекторами дев'ятнадцятого і двадцятого транзисторів відповідно, а також з базами двадцять третього і двадцять четвертого транзисторів відповідно, бази дев'ятнадцятого і двадцятого транзисторів з'єднано з базами і колекторами двадцять першого і двадцять другого транзисторів відповідно, а також з емітерами двадцять третього і двадцять четвертого транзисторів відповідно, колектор двадцять третього транзистора з'єднано з базами і колекторами двадцять п'ятого і одинадцятого та з базою першого вихідного транзисторів, емітер двадцять четвертого транзистора з'єднано з емітером двадцять восьмого та базою і колектором дванадцятого транзисторів, а також з другим вихідним транзистором, емітери одинадцятого і дванадцятого транзисторів об'єднані між собою, емітери двадцять п'ятого і двадцять сьомого транзисторів з'єднано з базами і колекторами двадцять шостого і двадцять восьмого транзисторів відповідно, емітери дев'ятнадцятого і двадцять першого транзисторів та колектор першого вихідного транзистора з'єднано з шиною додатного живлення, емітери двадцятого і двадцять другого транзисторів та колектор другого ви хідного транзистора з'єднано з шиною від'ємного живлення, емітери першого і другого вихідних транзисторів об'єднані між собою і з'єднано з другим виводом першого резистора, а також з вихідною шиною. Недоліком найближчого аналогу є вузький динамічний діапазон вхідного сигналу, що призво 6 дить до виникнення динамічних похибок за умови збільшення рівня вхідного сигналу. В основу корисної моделі поставлено задачу створення вхідного пристрою схеми порівняння струмів, в якому за рахунок введення схеми обмеження вхідного сигналу досягається розширення динамічного діапазону вхідного сигналу, що призводить зменшення динамічних похибок і запобігання перевантаженню підсилювальних каскадів, що розширює галузь використання корисної моделі у різноманітних пристроях імпульсної та обчислювальної техніки і автоматики. Поставлена задача досягається тим, що в вхідний пристрій схеми порівняння струмів, який містить сорок транзисторів, три джерела струму, вхідну шин у, шини додатного і від'ємного живлення, шину н ульового потенціалу, вихідн у шину, причому перше джерело струму своїми виводами з'єднане з колекторами п'ятнадцятого і шістнадцятого транзисторів відповідно та базами тринадцятого і чотирнадцятого транзисторів відповідно, бази п'ятнадцятого і шістнадцятого транзисторів з'єднані з емітерами тринадцятого і чотирнадцятого транзисторів відповідно та з колекторами сімнадцятого і вісімнадцятого транзисторів відповідно, емітери п'ятнадцятого і шістнадцятого транзисторів з'єднані з емітерами третього і четвертого транзисторів відповідно, бази третього і четвертого транзисторів з'єднані з колекторами і базами п'ятого і шостого транзисторів відповідно, а також з базами сімнадцятого і вісімнадцятого транзисторів відповідно, а також з базами сьомого і восьмого транзисторів відповідно, колектори тринадцятого і чотирнадцятого транзисторів з'єднані з базами двадцять дев'ятого і тридцятого транзисторів відповідно, а також з колекторами першого і другого транзисторів відповідно, колектор третього, емітер п'ятого, емітер сімнадцятого, колектор двадцять дев'ятого, емітер сьомого транзисторів з'єднані з шиною додатного живлення, колектор четвертого, емітер шостого, емітер вісімнадцятого, колектор тридцятого, емітер восьмого транзисторів з'єднані з шиною від'ємного живлення, емітер першого транзистора з'єднаний з емітером другого транзистора та шиною нульового потенціалу, бази першого і другого транзисторів з'єднано з базами тридцять третього, першого вхідного та тридцять четвертого, др угого вхідного транзисторів відповідно, емітери тридцять третього і тридцять четвертого транзисторів об'єднані між собою, їх колектори з'єднані з базами і колекторами тридцять першого і тридцять другого транзисторів відповідно, а також з базами тридцять п'ятого і тридцять шостого транзисторів відповідно, колектори першого вхідного і другого вхідного транзисторів з'єднані з колекторами сьомого і тридцять п'ятого та восьмого і тридцять шостого транзисторів відповідно, а також з базами дев'ятого і десятого транзисторів відповідно, емітери першого вхідного і другого вхідного транзисторів об'єднані між собою і з'єднані з емітером двадцять шостого та базою і колектором двадцять сьомого транзисторів, емітери тридцять першого, тридцять п'ятого і колектор дев'ятого транзисторів з'єднано з шиною додатного живлення, емітери тридцять другого, тридцять 7 25471 шостого і колектор десятого транзисторів з'єднано з шиною від'ємного живлення, третє джерело струму своїми виводами з'єднано з емітерами дев'ятого і десятого транзисторів відповідно, а також колекторами дев'ятнадцятого і двадцятого транзисторів відповідно, а також з базами двадцять третього і двадцять четвертого транзисторів відповідно, бази дев'ятнадцятого і двадцятого транзисторів з'єднано з базами і колекторами двадцять першого і двадцять другого транзисторів відповідно, а також з емітерами двадцять третього і двадцять четвертого транзисторів відповідно, колектор двадцять третього транзистора з'єднано з базами і колекторами двадцять п'ятого і одинадцятого та з базою першого вихідного транзисторів, колектор двадцять четвертого транзистора з'єднано з емітером двадцять восьмого та базою і колектором дванадцятого транзисторів, а також з другим вихідним транзистором, емітери одинадцятого і дванадцятого транзисторів об'єднані між собою, емітери двадцять п'ятого і двадцять сьомого транзисторів з'єднано з базами і колекторами двадцять шостого і двадцять восьмого транзисторів відповідно, емітери дев'ятнадцятого і двадцять першого транзисторів та колектор першого вихідного транзистора з'єднано з шиною додатного живлення, емітери двадцятого і двадцять другого транзисторів та колектор другого вихідного транзистора з'єднано з шиною від'ємного живлення, емітери першого вихідного і другого вихідного транзисторів об'єднані між собою і з'єднано з другим виводом першого резистора, а також з вихідною шиною, згідно корисної моделі введено шість транзисторів і другий резистор, причому емітери двадцять дев'ятого і тридцятого транзисторів з'єднано з базами і колекторами тридцять сьомого, тридцять дев'ятого та тридцять восьмого, сорок другого транзисторів відповідно, емітери тридцять сьомого і тридцять восьмого транзисторів з'єднано з базами першого і другого транзисторів відповідно, емітери тридцять дев'ятого і сорок другого транзисторів з'єднано з базами і колекторами сорокового і сорок першого транзисторів відповідно, а також з відповідними виводами другого джерела струму, емітери сорокового і сорок першого транзисторів об'єднано, а також з'єднано з першим виводом першого резистора, вхідною шиною і першим виводом другого резистора, другий вивід другого резистора з'єднано з емітерами першого вхідного і другого вхідного транзисторів. На Фіг. представлено принципову схему вхідного пристрою схеми порівняння струмів. Пристрій містить перше джерело струму 3, яке своїми виводами з'єднане з колекторами п'ятнадцятого 2 і шістнадцятого 4 транзисторів відповідно та базами тринадцятого 11 і чотирнадцятого 14 транзисторів відповідно, бази п'ятнадцятого 1 і шістнадцятого 4 транзисторів з'єднані з емітерами тринадцятого 11 і чотирнадцятого 14 транзисторів відповідно та з колекторами сімнадцятого 10 і вісімнадцятого 15 транзисторів відповідно, емітери п'ятнадцятого 2 і шістнадцятого 4 транзисторів з'єднані з емітерами третього 1 і четвертого 5 транзисторів відповідно, бази третього 1 і четвертого 5 транзисторів з'єднані з колекторами і базами 8 п'ятого 7 і шостого 8 транзисторів відповідно, а також з базами сімнадцятого 10 і вісімнадцятого 15 транзисторів відповідно, а також з базами сьомого 21 і восьмого 26 транзисторів відповідно, колектори тринадцятого 11 і чотирнадцятого 14 транзисторів з'єднані з базами двадцять дев'ятого 16 і тридцятого 20 транзисторів відповідно, а також з колекторами першого 12 і другого 13 транзисторів відповідно, колектор третього 1, емітер п'я того 7, емітер сімнадцятого 10, колектор двадцять дев'ятого 16, емітер сьомого 21 транзисторів з'єднані з шиною додатного живлення 54, колектор четвертого 5, емітер шостого 8, емітер вісімнадцятого 15, колектор тридцятого 20, емітер восьмого 26 транзисторів з'єднані з шиною від'ємного живлення 56, емітер першого 12 транзистора з'єднаний з емітером другого 3 транзистора та шиною нульового потенціалу 9, бази першого 12 і другого 13 транзисторів з'єднано з базами тридцять третього 28 та тридцять четвертого 29 транзисторів відповідно, а також з базами першого вхідного 33 і другого вхідного 34 транзисторів відповідно, а також з емітерами тридцять сьомого 17 і тридцять восьмого 19 транзисторів відповідно, емітери двадцять дев'ятого 16 і тридцятого 20 транзисторів з'єднано з базами і колекторами тридцять сьомого 17, тридцятьдев'ятого 22 та тридцять восьмого 19, сорок другого 25 транзисторів відповідно, емітери тридцять дев'ятого 22 і сорок другого 25 транзисторів з'єднано з базами і колекторами сорокового 23 і сорок першого 24 транзисторів відповідно, а також з відповідними виводами другого 18 джерела струму, емітери сорокового 23 і сорок першого 24 транзисторів об'єднано, а також з'єднано з першим виводом першого 26 резистора, вхідною шиною 6 і першим виводом другого 31 резистора, другий вивід другого 31 резистора з'єднано з емітерами першого вхідного 33 і другого вхідного 34 транзисторів, емітери тридцять третього 28 і тридцять четвертого 29 транзисторів об'єднані між собою, їх колектори з'єднані з базами і колекторами тридцять першого 27 і тридцять другого 30 транзисторів відповідно, а також з базами тридцять п'ятого 32 і тридцять шостого 35 транзисторів відповідно, колектори першого вхідного 33 і другого вхідного 34 транзисторів з'єднані з колекторами сьомого 21 і тридцять п'ятого 32 та восьмого 26 і тридцять шостого 35 транзисторів відповідно, а також з базами дев'ятого 37 і десятого 39 транзисторів відповідно, емітери першого вхідного 33 і другого вхідного 34 транзисторів з'єднані з емітером двадцять шостого 43 та базою і колектором двадцять сьомого 44 транзисторів, емітери тридцять першого 27, тридцять п'ятого 32 і колектор дев'ятого 37 транзисторів з'єднано з шиною додатного живлення 54, емітери тридцять другого 30, тридцять шостого 35 і колектор десятого 39 транзисторів з'єднано з шиною від'ємного живлення 56, третє 38 джерело струму своїми виводами з'єднано з емітерами дев'ятого 37 і десятого 39 транзисторів відповідно, а також колекторами дев'ятнадцятого 40 і двадцятого 41 транзисторів відповідно, а також з базами двадцять третього 47 і двадцять четвертого 50 транзисторів відповідно, бази дев'ятнадцятого 40 і двадцятого 41 транзис 9 25471 торів з'єднано з базами і колекторами двадцять першого 46 і двадцять другого 51 транзисторів відповідно, а також з емітерами двадцять третього 47 і двадцять четвертого 50 транзисторів відповідно, колектор двадцять третього 47 транзистора з'єднано з базами і колекторами двадцять п'ятого 42 і одинадцятого 48 та з базою першого вихідного 52 транзисторів, колектор двадцять четвертого 50 транзистора з'єднано з емітером двадцять восьмого 45 та базою і колектором дванадцятого 49 транзисторів, а також з другим вихідним транзистором 53, емітери одинадцятого 48 і дванадцятого 49 транзисторів об'єднані між собою, емітери двадцять п'ятого 42 і двадцять сьомого 44 транзисторів з'єднано з базами і колекторами двадцять шостого 43 і двадцять восьмого 45 транзисторів відповідно, емітери дев'ятнадцятого 40 і двадцять першого 46 транзисторів та колектор першого вихідного 52 транзистора з'єднано з шиною додатного живлення 54, емітери двадцятого 41 і двадцять другого 51 транзисторів та колектор другого вихідного 53 транзистора з'єднано з шиною від'ємного живлення 56, емітери першого вихідного 52 і другого ви хідного 53 транзисторів об'єднані між собою і з'єднано з другим виводом першого 36 резистора, а також з вихідною шиною 55. Пристрій працює таким чином. Вхідний сигнал у вигляді стр уму поступає на вхідну шину 6 . Якщо вхідний струм втікає у схему, то др угий вхідний 34 транзистор привідкривається, а перший вхідний 33 призакривається. У цьому випадку десятий 39 транзистор призакривається, а дев'ятий 37 транзистор привідкривається, при цьому частина струму, яка поступає від третього 38 джерела струму на вхід відбивача струму побудованого на двадцятому 41, двадцять другому 51, двадцять четвертому 50 транзисторах збільшується, а частина струму, яка поступає від третього 38 джерела струму на вхід відбивача струму побудованого на дев'ятнадцятому 40, двадцять першому 46, двадцять третьому 47 транзисторах зменшується. При цьому колекторний струм двадцять третього 47 транзистора зменшується, а двадцять четвертого 50 транзистора збільшується. При цьому потенціал точки об'єднання емітерів одинадцятого 48 та дванадцятого 49 транзисторів зменшується і прямує у від'ємну зону напруги. Оскільки потенціал виходу схеми повторює потенціал одинадцятого 48 та дванадцятого 49 транзисторів, то і напруга на виході схеми також прямує у від'ємну зону. Напруга на виході схеми стає від'ємною. Якщо вхідний струм витікає зі схему, то перший вхідний 33 транзистор привідкривається, а другий вхідний 34 призакривається. У цьому випадку дев'ятий 37 транзистор призакривається, а десятий 39 транзистор привідкривається, при цьому частина струму, яка поступає від третього 38 джерела струму на вхід відбивача стр уму побудованого на дев'ятнадцятому 40, двадцять першому 46, двадцять третьому 47 транзисторах збільшується, а частина струму, яка поступає від третього 38 джерела струму на вхід відбивача струму побудованого на двадцятому 41, двадцять другому 51, двадцять четвертому 50 транзисторах зменшується. При цьому колекторний струм двадцять четве 10 ртого 50 транзистора зменшується, а двадцять третього 47 транзистора збільшується. При цьому потенціал точки об'єднання емітерів одинадцятого 48 та дванадцятого 49 транзисторів збільшується і прямує у додатну зону напруги. Оскільки потенціал виходу схеми повторює потенціал одинадцятого 48 та дванадцятого 49 транзисторів, то і напруга на виході схеми також прямує у додатну зону. Напруга на виході схеми стає додатною. Забезпечення потрібної робочої точки вхідного каскаду схеми побудованого на першому 12 і другому 13 вхідних транзисторах здійснюють тридцять третій 28 і тридцять четвертий 29 транзистори, через колектори яких протікає наскрізний струм, що рівний колекторним тринадцятого 11 і чотирнадцятого 14 транзисторів. Колекторний струм тридцять четвертого 29 транзистора відбитий через струмове дзеркало, яке побудоване на тридцять другому 30 та тридцять шостому 35 транзисторах, компенсує колекторний струм другого вхідного 34 транзистора. Колекторний струм тридцять третього 28 транзистора відбитий через струмове дзеркало, яке побудоване на тридцять першому 27 і тридцять п'ятому 32 транзисторах, компенсує колекторний струм першого вхідного 33 транзистора. Відбивачі струму на сьомому 21 та восьмому 26 транзисторах задають базові струми дев'ятого 37 та десятого 39 транзисторів відповідно. Якщо напруга на ви ході схеми зменшується і входить у від'ємну зону, то двадцять сьомий 44 і двадцять восьмий 45 транзистори у діодному вмиканні привідкриваються, а двадцять п'ятий 42 та двадцять шостий 43 транзистори у діодному вмиканні призакриваються, при цьому струм, який подається на вхід схеми, компенсується колекторним струмом двадцять четвертого 50 транзистора. Якщо напруга на виході зростає і потрапляє у додатну зону, то двадцять п'ятий 42 та двадцять шостий 43 транзистори призакриваються і компенсують струм, який втікає із входу схеми. Мінімізація похибки зміщення нуля по входу підсилювача у вигляді або DIв х0 або DUв х0 досягається таким чином. Двоярусні схеми відбивачів струму, що побудовані на третьому 1, п'ятому 7, сімнадцятому 10, п'ятнадцятому 2, тринадцятому 11 транзисторах, а також четвертому 16, шостому 8, вісімнадцятому 15, шістнадцятому 4, чотирнадцятому 14 транзисторах, а також давачі струму на першому 12 та другому 13 транзисторах забезпечують мінімізацію похибки зміщення нуля по входу підсилювача. Тридцять сьомий 17 і тридцять восьмий 19 транзистори у діодному вмиканні забезпечують розширення динамічного діапазону вхідного сигналу шляхом обмеження його великих значень у вхідному колі схеми. Тридцять сьомий 17 і тридцять восьмий 19 транзистори призначені для завдання режиму по постійному струму тридцять дев'ятого 22, сорокового 23, сорок першого 24, сорок другого 25 транзисторів у діодному вмиканні. Друге 18 джерело струму призначене для завдання режиму по постійному струму двадцять дев'ятого 16 і тридцятого 20 транзисторів, а також зменшення струмів робочих точок сорокового 23 і 11 25471 сорок першого 24 транзисторів, порівняно із струмами робочих точок тридцять дев'ятого 22 і сорок другого 25 транзисторів. Це дозволяє при малих Комп’ютерна в ерстка Г. Паяльніков 12 значеннях вхідних струмів досягти максимальної передачі вхідного струм у із входу схеми на вхід підсилювача. Підписне Тираж 26 прим. Міністерство осв іт и і науки України Держав ний департамент інтелектуальної в ласності, вул. Урицького, 45, м. Київ , МСП, 03680, Україна ДП “Український інститут промислов ої в ласності”, вул. Глазунова, 1, м. Київ – 42, 01601

ДивитисяДодаткова інформація

Назва патенту англійськоюInput device of current comparator circuit

Автори англійськоюAzarov Oleksii Dmytrovych, Kaduk Oleksandr Volodymyrovych,Bohomolov Serhii Vitaliiovych, Harnaha Volodymyr Anatoliiovych, Reshetnik Oleksandr Oleksandrovych

Назва патенту російськоюВходное устройство схемы сравнения токов

Автори російськоюАзаров Алексей Дмитриевич, Кадук Александр Владимирович, Богомолов Сергей Витальевич, Гарнага Владимир Анатольевич, Решетник Александр Александрович

МПК / Мітки

Мітки: порівняння, схемі, струмів, пристрій, вхідний

Код посилання

<a href="https://ua.patents.su/6-25471-vkhidnijj-pristrijj-skhemi-porivnyannya-strumiv.html" target="_blank" rel="follow" title="База патентів України">Вхідний пристрій схеми порівняння струмів</a>

Попередній патент: 3-метил-7-(b-гідроксі-g-ізопропокси)пропіл-8-n-b-фенілетиламіноксантин, який виявляє діуретичну дію

Наступний патент: Ексцентриковий пристрій для уловлювання стрічки похилого конвеєра

Випадковий патент: Спосіб одержання кремнію