Вхідний пристрій схеми порівняння струмів

Номер патенту: 19379

Опубліковано: 15.12.2006

Автори: Богомолов Сергій Віталійович, Тарасова Ольга Миколаївна, Лукащук Олександр Олександрович, Захарченко Сергій Михайлович, Азаров Олексій Дмитрович

Формула / Реферат

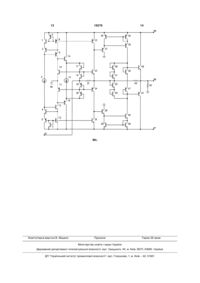

Вхідний пристрій схеми порівняння струмів, що містить два вхідні транзистори, шину додатного живлення, шину від'ємного живлення, шину нульового потенціалу, двадцять вісім транзисторів, перший та другий вихідні транзистори, три резистори, шину входу, шину виходу, причому емітери першого і другого транзисторів з'єднано з шиною нульового потенціалу, їх колектори з'єднано з колекторами тринадцятого і чотирнадцятого транзисторів відповідно, а їх бази з'єднано з базами першого і другого вхідних транзисторів відповідно, бази тринадцятого і чотирнадцятого транзисторів з'єднано з колекторами п'ятнадцятого і шістнадцятого транзисторів відповідно, їх емітери - з базами п'ятнадцятого і шістнадцятого транзисторів відповідно, а також з колекторами сімнадцятого і вісімнадцятого транзисторів відповідно, емітери п'ятнадцятого і шістнадцятого транзисторів з'єднано з емітерами третього і четвертого транзисторів відповідно, бази третього і четвертого транзисторів з'єднано з базами і колекторами п'ятого і шостого транзисторів відповідно, а також з базами сімнадцятого і вісімнадцятого транзисторів відповідно, а також з базами сьомого і восьмого транзисторів відповідно, колектор третього, емітер п'ятого, емітер сімнадцятого, емітер сьомого транзисторів з'єднані з шиною додатного живлення, колектор четвертого, емітер шостого, емітер вісімнадцятого, емітер восьмого транзисторів з'єднані з шиною від'ємного живлення, емітери першого і другого вхідних транзисторів з'єднані з першим виводом першого резистора, а також з емітером двадцять шостого та з базою і колектором двадцять сьомого транзисторів, колектори першого і другого вхідних транзисторів з'єднані з колекторами сьомого і восьмого транзисторів відповідно, а також базами дев'ятого і десятого транзисторів відповідно, колектори дев'ятого і десятого транзисторів з'єднано з шиною нульового потенціалу, їх емітери з'єднано з колекторами дев'ятнадцятого і двадцятого транзисторів відповідно, а також з базами двадцять третього і двадцять четвертого транзисторів відповідно, бази дев'ятнадцятого і двадцятого транзисторів з'єднано з базами та колекторами двадцять першого і двадцять другого транзисторів відповідно, а також з емітерами двадцять третього і двадцять четвертого транзисторів відповідно, емітери дев'ятнадцятого і двадцять першого транзисторів з'єднано з шиною додатного живлення, емітери двадцятого і двадцять другого з'єднано з шиною від'ємного живлення, колектори двадцять третього і двадцять четвертого транзисторів з'єднано з колекторами та базами одинадцятого і дванадцятого транзисторів відповідно, а також з колектором і базою двадцять п'ятого та з емітером двадцять восьмого транзисторів відповідно, а також з базами першого і другого вихідних транзисторів відповідно, емітер двадцять п'ятого транзистора з'єднано з колектором і базою двадцять шостого транзистора, емітер двадцять сьомого транзистора з'єднано з колектором і базою двадцять восьмого транзистора, емітери одинадцятого і дванадцятого транзисторів об’єднано, колектори першого і другого вихідних транзисторів з’єднано з шинами додатного і від'ємного живлення відповідно, емітери першого і другого вихідних транзисторів об'єднано та з'єднано з другим виводом першого резистора, а також з вихідною шиною, а також першим виводом третього резистора, другий вивід третього резистора з'єднано з шиною нульового потенціалу, який відрізняється тим, що в нього введено шість транзисторів та два джерела струму, причому перший і другий виводи першого джерела струму з'єднані з базами тринадцятого і чотирнадцятого транзисторів відповідно та з колекторами п'ятнадцятого і шістнадцятого транзисторів відповідно, бази двадцять дев'ятого і тридцятого транзисторів з'єднані з колекторами тринадцятого і чотирнадцятого транзисторів відповідно та з колекторами першого і другого транзисторів відповідно, а їх колектори приєднані до шин додатного та від'ємного живлення відповідно, емітери цих транзисторів з'єднані з першим і другим виводами другого джерела струму, а також з базами і колекторами тридцять першого і тридцять четвертого транзисторів відповідно, бази першого і другого транзисторів з'єднано з базами першого і другого вхідних транзисторів відповідно, а також з емітерами тридцять першого і тридцять четвертого транзисторів відповідно, а також з базами і колекторами тридцять другого і тридцять третього транзисторів відповідно, емітери тридцять другого і тридцять третього транзисторів об'єднано та з'єднано з шиною вхідного сигналу та з першим виводом другого резистора, другий вивід другого резистора з'єднаний з емітерами першого та другого вхідних транзисторів, а також з базою і колектором двадцять сьомого транзистора, а також з емітером двадцять шостого транзистора, а також з другим виводом першого резистора.

Текст

Вхідний пристрій схеми порівняння струмів, що містить два вхідні транзистори, шину додатного живлення, шину від'ємного живлення, шину нульового потенціалу, двадцять вісім транзисторів, перший та другий вихідні транзистори, три резистори, шину входу, шину виходу, причому емітери першого і другого транзисторів з'єднано з шиною нульового потенціалу, їх колектори з'єднано з колекторами тринадцятого і чотирнадцятого транзисторів відповідно, а їх бази з'єднано з базами першого і другого вхідних транзисторів відповідно, бази тринадцятого і чотирнадцятого транзисторів з'єднано з колекторами п'ятнадцятого і шістнадцятого транзисторів відповідно, їх емітери - з базами п'ятнадцятого і шістнадцятого транзисторів відповідно, а також з колекторами сімнадцятого і вісімнадцятого транзисторів відповідно, емітери п'ятнадцятого і шістнадцятого транзисторів з'єднано з емітерами третього і четвертого транзисторів відповідно, бази третього і четвертого транзисторів з'єднано з базами і колекторами п'ятого і шостого транзисторів відповідно, а також з базами сімнадцятого і вісімнадцятого транзисторів відповідно, а також з базами сьомого і восьмого транзисторів відповідно, колектор третього, емітер п'ятого, емітер сімнадцятого, емітер сьомого транзисторів з'єднані з шиною додатного живлення, колектор четвертого, емітер шостого, емітер вісімнадцятого, емітер восьмого транзисторів з'єднані з шиною від'ємного живлення, емітери першого і другого вхідних транзисторів з'єднані з першим виводом першого резистора, а також з емітером двадцять шостого та з базою і колектором двадцять сьомого транзисторів, колектори першого і другого вхідних транзисторів з'єднані з колекторами сьомого і восьмого транзисторів відповідно, а також базами дев'ятого і десятого транзисторів відповідно, коле 2 (19) 1 3 19379 4 з базами і колекторами тридцять першого і тридцять другого і тридцять третього транзисторів дцять четвертого транзисторів відповідно, бази об'єднано та з'єднано з шиною вхідного сигналу та першого і другого транзисторів з'єднано з базами з першим виводом другого резистора, другий вивід першого і другого вхідних транзисторів відповідно, другого резистора з'єднаний з емітерами першого а також з емітерами тридцять першого і тридцять та другого вхідних транзисторів, а також з базою і четвертого транзисторів відповідно, а також з баколектором двадцять сьомого транзистора, а тазами і колекторами тридцять другого і тридцять кож з емітером двадцять шостого транзистора, а третього транзисторів відповідно, емітери тритакож з другим виводом першого резистора. Корисна модель відноситься до імпульсної техніки і може бути використана в аналоговоцифрових перетворювачах і цифрових вимірювальних приладах. Відомо вхідний пристрій схеми порівняння струмів [А.с. №1529434 СССР, Н03К5/24, G05В1/01, 1987], який містить чотири резистора, два вхідних транзистора, двадцять два транзистора, два вихідних транзистора, шину додатного живлення, шину від'ємного живлення, вхідну та вихідну шини, шину нульового потенціалу, два діоди, які ввімкнено зустрічно та паралельно. До вхідної шини підключені перші виводи першого резистора і двох зустрічно включених діодів а також емітер першого вхідного транзистора, емітер другого вхідного транзистора, база якого з'єднана з базою і колектором першого транзистора і з базою другого транзистора, емітер якого з'єднаний з колектором третього транзистора, а колектор - з першими виводами другого і третього резисторів, шиною нульового потенціалу, емітерами першого і четвертого транзисторів і з колектором п'ятого транзистора, емітер якого з'єднаний з колектором шостого транзистора, а база - з колектором і базою четвертого транзистора і базою першого вхідного транзистора, колектор якого з'єднаний з базою дванадцятого транзистора, колектор якого з'єднаний з колектором і базою восьмого транзистора і базами n перших вихідних транзисторів, колектори яких з'єднані з шиною додатного живлення, емітерами сьомого і шостого транзисторів, емітером дев'ятого транзистора, колектор і база якого з'єднані між собою, базою шостого транзистора і першим виводом четвертого резистора, другий вивід якого з'єднаний з колектором і базою десятого транзистора і базою третього транзистора, емітер якого з'єднаний з шиною від'ємного живлення, емітером десятого транзистора, колекторами n других вихідних транзисторів і емітером одинадцятого транзистора, база якого з'єднана з колектором другого вхідного транзистора, а колектор - з колектором і базою дванадцятого транзистора і базами n других вихідних транзисторів, емітери яких з'єднані з другим виводом третього резистора, вихідною шиною, емітерами n перших вихідних транзисторів і другими виводами першого резистора і двох ввімкнених зустрічно та паралельно діодів, емітери восьмого і дванадцятого транзисторів з'єднані між собою і другим виводом другого резистора, а база третього транзистора - з базою тринадцятого транзистора, колектор якого з'єднаний з емітером чотирнадцятого транзистора, база якого з'єднана з базою п'ятнадцятого транзи стора, з колектором і базою шістнадцятого транзистора, емітер якого з'єднаний з шиною додатного живлення, емітерами сімнадцятого і вісімнадцятого, колектором чотирнадцятого і емітером п'ятнадцятого транзисторів, колектор п'ятнадцятого транзистора з'єднаний з колектором першого вхідного транзистора, колектор сімнадцятого транзистора з'єднаний з колектором шостого транзистора, а база - з базою шостого і вісімнадцятого транзисторів, колектор вісімнадцятого транзистора з'єднаний з емітером дев'ятнадцятого транзистора, база якого з'єднана з базою двадцятого транзистора, колектором і базою двадцять першого транзистора, емітер якого з'єднаний з шиною від'ємного живлення, емітерами тринадцятого і двадцять другого транзисторів, з колектором дев'ятнадцятого транзистора і з емітером двадцятого транзистора, колектор якого з'єднаний з колектором другого вхідного транзистора, колектор двадцять другого транзистора з'єднаний з колектором третього транзистора, база двадцять другого транзистора - з базою третього транзистора. До недоліків слід віднести велику статичну адитивну похибку, яка обумовлена великим вхідним струмом зміщення нуля і великою вхідною напругою зміщення нуля. Що стосується швидкодії прототипу то вона потенційно буде нижчою ніж у схеми, яка заявляється, за умови реалізації пристрою на однакових транзисторах. За прототип обрано вхідний пристрій схеми порівняння струмів [А.С. №13110 Н03К5/24, G05В1/01, 2006] який містить вхідну шину яка з'єднана з емітерами першого та другого вхідних транзисторів, їх бази - з колекторами та базами першого і другого транзисторів, та з колекторами тринадцятого і чотирнадцятого транзисторів, колектори першого і другого вхідних транзисторів з'єднані з колекторами сьомого і восьмого транзисторів і базами дев'ятого і десятого транзисторів, емітери першого і другого транзисторів з'єднані з шиною нульового потенціалу, бази тринадцятого і чотирнадцятого транзисторів з'єднані з колекторами п'ятнадцятого і шістнадцятого та з першим і другим виводами другого резистора відповідно, а емітери тринадцятого і чотирнадцятого транзисторів з'єднані з базами п'ятнадцятого і шістнадцятого та колекторами сімнадцятого та вісімнадцятого транзисторів відповідно, емітери п'ятнадцятого і шістнадцятого транзисторів з'єднані з емітерами третього і четвертого транзисторів відповідно, бази третього і четвертого транзисторів з'єднані з базами і колекторами п'ятого 6 і шостого, базами сімнадцятого та вісімнадцятого, базами сьомого і 5 19379 6 восьмого транзисторів відповідно, колектори тредругого транзисторів з'єднано з шиною нульового тього і четвертого, емітери п'ятого і шостого, еміпотенціалу, їх колектори з'єднано з колекторами тери сімнадцятого та вісімнадцятого, емітери сьотринадцятого і чотирнадцятого транзисторів відмого і восьмого транзисторів з'єднані з шинами повідно, а їх бази з'єднано з базами першого і друдодатного і від'ємного потенціалів відповідно, когого вхідних транзисторів відповідно, бази триналектори дев’ятого та десятого транзисторів дцятого і чотирнадцятого транзисторів з'єднано з з’єднані з шиною нульового потенціалу, а їх емітеколекторами п'ятнадцятого і шістнадцятого транри - з колекторами дев'ятнадцятого і двадцятого зисторів відповідно, їх емітери - з базами п'ятнадта базами двадцять третього і двадцять четвертоцятого і шістнадцятого транзисторів відповідно, а го транзисторів відповідно, тоді як бази дев'ятнатакож з колекторами сімнадцятого і вісімнадцятого дцятого і двадцятого транзисторів з'єднані з базатранзисторів відповідно, емітери п'ятнадцятого і ми і колекторами двадцять першого і двадцять шістнадцятого транзисторів з'єднано з емітерами другого та емітерами двадцять третього і двадцятретього і четвертого транзисторів відповідно, бать четвертого транзисторів відповідно, емітери зи третього і четвертого транзисторів з'єднано з дев'ятнадцятого і двадцятого та двадцять першого базами і колекторами п'ятого і шостого транзистоі двадцять другого транзисторів з'єднані з шинами рів відповідно, а також з базами сімнадцятого і додатного і від'ємного живлення відповідно, колеквісімнадцятого транзисторів відповідно, а також з тори двадцять третього і двадцять четвертого базами сьомого і восьмого транзисторів відповідтранзисторів з'єднано з колекторами і базами одино, колектор третього, емітер п'ятого, емітер сімнадцятого і дванадцятого транзисторів, а також з надцятого, емітер сьомого транзисторів з'єднані з базами першого і другого вихідних транзисторів шиною додатного живлення, колектор четвертого, відповідно, крім того колектор двадцять третього емітер шостого, емітер вісімнадцятого, емітер вотранзистора підключений до колектора і бази двасьмого транзисторів з'єднані з шиною від'ємного дцять п'ятого транзистора, а колектор двадцять живлення, емітери першого і другого вхідних транчетвертого з'єднаний з емітером двадцять восьмозисторів з'єднані з першим виводом першого резиго транзистора, емітери одинадцятого і дванадцястора, а також з емітером двадцять шостого та з того транзисторів об'єднані між собою, колектори базою і колектором двадцять сьомого транзистопершого та другого вихідних транзисторів приєдрів, колектори першого і другого вхідних транзиснані до шин додатного та від'ємного живлення торів з'єднані з колекторами сьомого і восьмого відповідно, а їх емітери об'єднані між собою та є транзисторів відповідно, а також базами дев'ятого виходом пристрою, чотири транзистори, з двадцяі десятого транзисторів відповідно, колектори деть п'ятого по двадцять восьмий, включені у діодв'ятого і десятого транзисторів з'єднано з шиною ному режимі, тобто з'єднано їх бази та колектори, і нульового потенціалу, їх емітери з'єднано з колекці транзистори з'єднані послідовно: емітер двадцяторами дев'ятнадцятого і двадцятого транзисторів ть п'ятого з'єднано з базою і колектором двадцять відповідно, а також з базами двадцять третього і шостого, емітер двадцять шостого з'єднано з бадвадцять четвертого транзисторів відповідно, бази зою і колектором двадцять сьомого, емітер двадев'ятнадцятого і двадцятого транзисторів з'єднадцять сьомого з'єднано з базою і колектором двано з базами та колекторами двадцять першого і дцять восьмого, а точка об'єднання емітера двадцять другого транзисторів відповідно, а також двадцять шостого транзистора та бази і колектора з емітерами двадцять третього і двадцять четвердвадцять сьомого транзистора з'єднана з шиною того транзисторів відповідно, емітери дев'ятнадцявхідного сигналу, вихідна шина з'єднана з вхідною того і двадцять першого транзисторів з'єднано з шиною через перший резистор та з шиною нульошиною додатного живлення, емітери двадцятого і вого потенціалу через третій резистор. двадцять другого з'єднано з шиною від'ємного жиНедоліком прототипу є виникнення значних влення, колектори двадцять третього і двадцять динамічних похибок за умови збільшення рівня четвертого транзисторів з'єднано з колекторами та вхідного сигналу, що погіршує швидкодію схеми, а базами одинадцятого і дванадцятого транзисторів також обмежує динамічний діапазон вхідного сигвідповідно, а також з колектором і базою двадцять налу. п'ятого та з емітером двадцять восьмого транзисВ основу корисної моделі поставлено задачу торів відповідно, а також з базами першого і другостворення вхідного пристрою схеми порівняння го вихідних транзисторів відповідно, емітер дваструмів, в якому за рахунок введення нових еледцять п'ятого транзистора з'єднано з колектором і ментів та зв'язків між ними збільшується динамічбазою двадцять шостого транзистора, емітер дваний діапазон вхідного сигналу, а також покращудцять сьомого транзистора з'єднано з колектором і ються перехідні процеси схеми в режимі великих базою двадцять восьмого транзистора, емітери струмів на вході, це розширює галузь використанодинадцятого і дванадцятого транзисторів об'єдня корисної моделі у різноманітних пристроях імнано, колектори першого і другого вихідних транпульсної та обчислювальної техніки, автоматики зисторів з'єднано з шинами додатного і від'ємного тощо. живлення відповідно, емітери першого і другого Поставлена задача досягається тим, що у вхівихідних транзисторів об'єднано та з'єднано з друдний пристрій схеми порівняння струмів, який місгим виводом першого резистора, а також з вихідтить два вхідні транзистори, шину додатного живною шиною, а також першим виводом третього лення, шину від'ємного живлення, шину нульового резистора, другий вивід третього резистора з'єдпотенціалу, двадцять вісім транзисторів, перший нано з шиною нульового потенціалу, введено та другий вихідні транзистори, три резистори, шишість транзисторів та два джерела струму, причону входу, шину виходу, причому емітери першого і му перший і другий виводи першого джерела 7 19379 8 струму з'єднані з базами тринадцятого і чотирнадвідповідно, а також з емітерами тридцять першого цятого транзисторів відповідно, та з колекторами 17 та тридцять четвертого 20 транзисторів відпоп'ятнадцятого і шістнадцятого транзисторів відповідно, а також з базами першого 23 та другого 24 відно, бази двадцять дев'ятого і тридцятого транвхідних транзисторів відповідно, емітери тридцять зисторів з'єднані з колекторами тринадцятого і другого 18 і тридцять третього 19 транзисторів чотирнадцятого транзисторів відповідно, та з коз'єднано з вхідною шиною 45, а також першим вилекторами першого і другого транзисторів відповіводом другого резистора 21, колектори першого дно, а їх колектори приєднані до шин додатного та 23 та другого 24 вхідних транзисторів з'єднані з від'ємного живлення відповідно, емітери цих транбазами дев'ятого 27 і десятого 28 транзисторів зисторів з'єднані з першим і другим виводами друвідповідно, а також з колекторами сьомого 22 і гого джерела струму, а також з базами і колектовосьмого 25 транзисторів відповідно, емітери рами тридцять першого і тридцять четвертого першого 23 і другого 24 вхідних транзисторів об'єтранзисторів відповідно, бази першого і другого днані між собою і з'єднані з другим виводом друготранзисторів з'єднано з базами першого і другого го резистора 21, а також з колектором і базою вхідних транзисторів відповідно, а також з емітедвадцять сьомого 32 транзистора, а також з емітерами тридцять першого і тридцять четвертого траром двадцять шостого 31 транзистора, а також з нзисторів відповідно, а також з базами і колектопершим виводом першого резистора 43, колектори рами тридцять другого і тридцять третього дев'ятого 27 і десятого 28 транзисторів з'єднані з транзисторів відповідно, емітери тридцять другого шиною нульового потенціалу 44, емітери дев'ятого і тридцять третього транзисторів об'єднано та 27 і десятого 28 транзисторів з'єднані з колектоз'єднано з шиною вхідного сигналу та з першим рами дев'ятнадцятого 26 і двадцятого 29 транзисвиводом другого резистора, другий вивід другого торів відповідно, а також з базами двадцять тререзистора з'єднаний з емітерами першого та друтього 35 і двадцять четвертого 38 транзисторів гого вхідних транзисторів, а також з базою і колеквідповідно, бази дев'ятнадцятого 26 двадцятого 29 тором двадцять сьомого транзистора, а також з транзисторів з'єднані з колекторами і базами дваемітером двадцять шостого транзистора, а також з дцять першого 34 і двадцять другого 39 транзисдругим виводом першого резистора. торів відповідно, а також з емітерами двадцять На кресленні представлено принципову схему третього 35 і двадцять четвертого 38 транзисторів вхідного пристрою схеми порівняння струмів. відповідно, колектори двадцять третього 35 і дваПристрій містить перше джерело струму 3, яке дцять четвертого 38 транзисторів з'єднані з базою своїми виводами з'єднане з колекторами п'ятнаді колектором двадцять п'ятого 30 і емітером двацятого 2 і шістнадцятого 4 транзисторів відповідно дцять восьмого 33 транзисторів відповідно, а тата базами тринадцятого 9 і чотирнадцятого 12 кож з базами і колекторами одинадцятого 36 і дватранзисторів відповідно, бази п'ятнадцятого 2 і надцятого 37 транзисторів відповідно, а також з шістнадцятого 4 транзисторів з'єднані з емітерами базами першого 40 і другого 41 вихідних транзистринадцятого 9 і чотирнадцятого 12 відповідно та з торів відповідно, емітери двадцять п'ятого 30 і колекторами сімнадцятого 8 і вісімнадцятого 13 двадцять сьомого 32 транзисторів з'єднані з базатранзисторів відповідно, емітери п'ятнадцятого 2 і ми і колекторами двадцять шостого 31 і двадцять шістнадцятого 4 транзисторів з'єднані з емітерами восьмого 33 транзисторів відповідно, емітери одитретього 1 і четвертого 5 транзисторів відповідно, надцятого 36 і дванадцятого 37 транзисторів об'єбази третього 1 і четвертого 5 транзисторів з'єднаднані між собою, емітери дев'ятнадцятого 26 і ні з колекторами і базами п'ятого 6 і шостого 7 двадцять першого 34 транзисторів, колектор пертранзисторів відповідно, а також з базами сімнадшого вихідного транзистора 40 з'єднані з шиною цятого 8 і вісімнадцятого 13 транзисторів відповіддодатного живлення,емітери двадцятого 29 і двано, а також з базами сьомого 22 і восьмого 25 традцять другого 39 транзисторів, колектор другого нзисторів відповідно, колектори тринадцятого 9 і вихідного транзистора 41 з'єднані з шиною від'ємчотирнадцятого 12 транзисторів з'єднані з базами ного живлення 47, емітери першого 40 і другого 41 двадцять дев'ятого 14 і тридцятого 16 транзистовихідних транзисторів об'єднані між собою і з'єдрів відповідно, а також з колекторами першого 10 і нані з першим виводом третього резистора 42 і другого 11 транзисторів відповідно, колектор тредругим виводом першого резистора 43, а також з тього 1, емітер п'ятого 6, емітер сімнадцятого 8, вихідною шиною 48, другий вивід третього резисколектор двадцять дев'ятого 14, емітер сьомого 22 тора 42 з'єднаний з шиною нульового потенціатранзисторів з'єднані з шиною додатного живленлу 44. ня 46, колектор четвертого 5, емітер шостого 7, Пристрій працює таким чином. Вхідний струм емітер вісімнадцятого 13, колектор тридцятого 16, спочатку надходить до обмежувача струмів, який емітер восьмого 25 транзистора з'єднані з шиною побудовано на другому джерелі струму 15, двавід'ємного живлення 47, емітер першого 10 трандцять дев'ятому 14, тридцятому 16, тридцять перзистора з'єднаний з емітером другого 11 транзисшому 17, тридцять другому 18, тридцять третьому тора та шиною нульового потенціалу 44, емітери 19, тридцять четвертому 20 та другому резисторі двадцять дев'ятого 14 і тридцятого 16 транзисто21. Струм робочої точки визначається колекторрів з'єднані з виводами другого джерела струму ними струмами тринадцятого транзистора 9 та 15, а також з базами і колекторами тридцять перчотирнадцятого транзистора 12. При цьому шого 17 і тридцять четвертого 20 транзисторів Ізм Ік9 Ік12 Ік10 Ік11 , відповідно, бази першого 10 та другого 11 транзисер сторів з'єднано з колекторами та базами тридцять другого 18 і тридцять третього 19 транзисторів 9 19379 10 де Ізм - струм першого джерела струму 3, 24 збільшується, і десятий транзистор 28 привідкривається. Водночас колекторний струм першого npn pnp . вхідного транзистора 23 зменшується і дев'ятий сер 2 транзистор 27 призакривається. Емітерний струм Друге джерело струму 15 призначено для задесятого транзистора 28 подається на вхід відбивдання робочої точки емітерних переходів двадцявача струму побудованого на двадцятому 29, двать дев'ятого 14 та тридцятого 16 транзисторів. дцять четвертому 38, двадцять другому 39 транНаскрізний струм, який протікає через тридцять зисторах. Відбитий струм з колектора двадцять перший 17, тридцять другий 18, тридцять третій четвертого транзистора 38 протікає через коло 19, тридцять четвертий 20 транзистори у діодному одинадцятого 36 і дванадцятого 37 транзисторів. вмиканні, а також наскрізний струм вхідного каскаЕмітерний струм дев'ятого транзистора 27 витікає ду схеми, побудованого на першому вхідному 23 з відбивача струму побудованого на дев'ятнадцята другому вхідному транзисторах 24, також дорівтому 26, двадцять першому 34, двадцять третьому нюють струму робочої точки. При цьому опір на 35 транзисторах, відбитий струм з колектора двавхідному обмежувачі струмів дорівнює дцять третього транзистора 35 протікає через коло rобм=2·rp-n(npn)||2·rp-n(pnp)≈rpn, одинадцятого 36 і дванадцятого 37 транзисторів. де Оскільки Ік38 більше Ік35 то потенціал точки об'єдT , нання емітерів одинадцятого 36 і дванадцятого 37 rpn IPT транзисторів зменшується, наближаючись до потенціалу шини від'ємного живлення. Водночас, де φТ=25мВ - термопотенціал, ІРТ - струм роодинадцятий 36 та дванадцятий 37 транзистори бочої точки. Вхідний опір схеми при цьому дорівзадають не тільки струм спокою вихідного каскаду, нює побудованого на першому та другому вихідних rвх=rрn/2. транзисторах 40, 41, а і визначають потенціал виНапруга на вході обмежувача дорівнює хідної шини схеми. Таким чином напруга Uвих поUoбм=Івх·(roбм||R2+rвх), вторює потенціал точки об'єднання емітерів одиде Івх - вхідний струм на шині 45, R2 - опір друнадцятого 36 і дванадцятого 37 транзисторів, гого резистора 21. тобто зменшується і наближається до - Uживл. Тоді струм, що втікає на емітери вхідних транЯкщо вхідний струм витікає із схеми в обмезисторів дорівнює жувач, то другий вхідний транзистор 24 призакриrобм R2 rвх Iвх вається, а перший вхідний транзистор 23 привідкUобм rобм R2 rвх rобм . I'вх Iвх ривається, колекторний струм другого вхідного R2 rвх R2 rвх rобм R2 rвх транзистора 24 зменшується, і десятий транзистор Таким чином коефіцієнт передачі вхідного 28 призакривається. Водночас колекторний струм струму на вхід підсилювача дорівнює першого вхідного транзистора 23 збільшується і I'вх rобм дев'ятий транзистор 27 привідкривається. ЕмітерKП . I'вх rобм R2 rвх ний струм десятого транзистора 28 подається на вхід відбивача струму побудованого на двадцятоВраховуючи, що rобм=rpn, rвх=rpn/2 отримаємо му 29, двадцять четвертому 38, двадцять другому кінцевий вираз для коефіцієнту передачі вхідного 39 транзисторах. Відбитий струм з колектора дваструму на вхід підсилювача дцять четвертого транзистора 38 протікає через rpn коло одинадцятого 36 і дванадцятого 37 транзисKП . rpn R2 rpn / 2 торів. Емітерний струм дев'ятого транзистора 27 витікає з відбивача струму побудованого на деЯкщо Івх, що подається на вхідну шину 45 в'ятнадцятому 26, двадцять першому 34, двадцять менший за струм робочої точки, то опір обмежуватретьому 35 транзисторах, відбитий струм з колекча змінюється незначно, і значна частина вхідного тора двадцять третього транзистора 35 протікає струму через другий резистор 21 потрапляє на через коло одинадцятого 36 і дванадцятого 37 вхід підсилювача. Якщо Івх, що подається на вхідну транзисторів. Оскільки Ік38 менше Ік35 то потенціал шину 45 більший за струм робочої точки, то це точки об'єднання емітерів одинадцятого 36 і двазначно зменшує опір обмежувача, і менша частина надцятого 37 транзисторів збільшується, наблиструму через другий резистор 21 потрапляє на жаючись до потенціалу шини додатного живлення. вхід підсилювача. При цьому якщо вхідний струм, Напруга Uвих повторює потенціал точки об'єднання що є більшим за струм робочої точки, втікає в обемітерів одинадцятого 36 і дванадцятого 37 транмежувач, то надлишковий струм відтікає на шину зисторів, тобто збільшується і наближається до від'ємного живлення 47 через тридцять третій 19, +Uживл. тридцять четвертий 20 та тридцятий 16 транзисЛанцюг транзисторів з двадцять п'ятого по тори. Якщо вхідний струм, що є більшим за струм двадцять восьмий у діодному вмиканні 30-33 утворобочої точки, витікає з обмежувача, то струм, рюють коло нелінійного від'ємного зворотного зв'яякого не вистачає, береться з шини додатного зку, мета уведення якого - обмежити амплітуду живлення 46 через двадцять дев'ятий 14, тризмінення напруги на виході схеми. При цьому якщо дцять перший 17 та тридцять другий 18 транзисструм що втікає у схему збільшується, то потенцітори. ал вихідної шини зменшується. Транзистори дваЯкщо струм втікає з обмежувача у схему, то дцять сьомий 32 та двадцять восьмий 33 привідкдругий вхідний транзистор 24 привідкривається, а риваються, а транзистори двадцять п'ятий 30 та перший вхідний транзистор 23 призакривається, двадцять шостий 31 призакриваються. При цьому колекторний струм другого вхідного транзистора 11 19379 12 через двадцять сьомий 32 та двадцять восьмий 33 33 транзисторів закривається, або група з двадцятранзистори в коло колектора двадцять четвертоть сьомого 32 та двадцять восьмого 33 транзистого транзистора 38 втікає струм який компенсує рів відкривається, а група з двадцять п'ятого 30 та вхідний струм схеми. По мірі збільшення Івх двадвадцять шостого 31 транзисторів закривається. дцять сьомий 32 та двадцять восьмий 33 транзисТаким чином на виході схеми виникає перепад тори привідкриваються сильніше, опори переходів напруг ±Up-n:Uвих(Івх)=[Rм||2rp-n]·Івх, де Uвих - вихідна колектор-емітер зменшуються, а глибина зворотнапруга, Івх - вхідний струм, Rм - опір першого реного зв'язку збільшується. Опір вказаного кола зистора 43, rp-n - опір р-n переходу. При малих вхітранзисторів починає істотно шунтувати загальний дних струмах опір rp-n різко зростає і значно переопір зворотного зв'язку, який визначається з форвищує Rм, при цьому чутливість схеми є максимальною. При великих Івх опір rp-n значно t , де φ - термопотенціал, і - знамули rp n t е зменшується, шунтує Rм і чутливість зменшується ie пропорційно збільшенню Івх. чення струму емітера, і зменшує змінення ампліМінімізація похибки зміщення нуля по входу туди на виході схеми. підсилювача у вигляді або ΔІвх0 або ΔUвх0 досягаЯкщо струм, що витікає із схеми, збільшуєтьється таким чином. За допомогою двоярусних ся, то потенціал вихідної шини збільшується. Трасхем відбивачів струму, а саме побудованих на нзистори двадцять сьомий 32 та двадцять восьтретьому 1, п'ятому 6, сімнадцятому 8, п'ятнадцямий 33 призакриваються, а транзистори двадцять тому 2, тринадцятому 9 транзисторах а також шосп'ятий 30 та двадцять шостий 31 привідкриваютьтому 7, четвертому 5, вісімнадцятому 13, шістнася. При цьому через двадцять п'ятий 30 та двадцятому 4, чотирнадцятому 12 транзисторах, на дцять шостий 31 транзистори з кола колектора перший 10 та другий 11 транзистори, які з двадцядвадцять третього транзистора 35 витікає струм ть дев'ятим 14 та тридцятим 16 транзисторами є який компенсує вхідний струм схеми. По мірі збідавачами струму, подаються струми відповідно І': льшення Івх який витікає із схеми двадцять п'ятий 1 1 30 та двадцять шостий 31 транзистори привідкриI' Ік 9 Ізм , ваються сильніше, опори переходів колекторp n p n p n емітер зменшуються, а глибина зворотного зв'язку а також I": знову ж таки збільшується. Опір кола двадцять п'ятий 30 та двадцять шостий 31 транзисторів по1 1 I" Ік12 Ізм , чинає істотно шунтувати загальний опір зворотноn p n p n p го зв'язку і зменшує змінення амплітуди на виході де Ік9, Ік12 - колекторні струми транзисторів 9 та схеми. 12 відповідно, Ізм - струм зміщення першого джеОскільки коло транзисторів з двадцять п'ятого рела струму 3. по двадцять восьмий у діодному вмиканні 30-33 Тобто Ік9≈Ік12. Позначимо підключені паралельно колу одинадцятого 36 та дванадцятого 37 транзисторів, то в стані спокою, 1 1 Iк 9 Ік12 І* . Тоді тобто коли Івх=0 транзистори кола 30-33 знахозм Ізм n p n p n p дяться на порозі відпирання. Якщо вхідний струм приймає максимальне значення, то залежно від струм спокою вхідного каскаду, побудованого на напрямку вхідного струму або група з двадцять вхідних транзисторах 23, 24 буде дорівнювати п'ятого 30 та двадцять шостого 31 відпирається, а Іспокою≈І*зм. Визначимо колекторні струми Ік27 та Ік28: група з двадцять сьомого 32 та двадцять восьмого Iб27 Іспокою Ік 22 * І* зм Іб1 Ізм Ізм / 1 Ізм Iб28 Іспокою Ік 25 І* зм Іб5 І* зм Ізм / 5 Ік27=Іб27·β27=Іб27·βp-n-p=Ізм/βp-n-p·βp-n-p=Ізм, Ік28=Іб28·β28=Іб28·βn-p-n=Ізм/βn-p-n·βn-p-n=Ізм. Бачимо, що Ік27=Ік28=Ізм. Оскільки коефіцієнт передачі відбивачів струму дорівнює одиниці, то Ік35=Ік27, а Ік38=Ік28 і приблизно рівні Ізм. Ізм 1 1 n p n p n p 1 1 n p n p n p Ізм n p n Ізм , p n p Ізм p n p Ізм , n p n Оскільки струм спокою вхідних транзисторів 23, 24 дорівнює Ік9 і Ік12, то падіння напруг на базових р-n переходах Uбе 23=Uбе 10, a Uбе 24=Uбе 11. Таким чином ΔUвх мінімізується, прямуючи до нуля. 13 Комп’ютерна верстка В. Мацело 19379 Підписне 14 Тираж 26 прим. Міністерство освіти і науки України Державний департамент інтелектуальної власності, вул. Урицького, 45, м. Київ, МСП, 03680, Україна ДП “Український інститут промислової власності”, вул. Глазунова, 1, м. Київ – 42, 01601

ДивитисяДодаткова інформація

Назва патенту англійськоюInput unit of a current comparator

Автори англійськоюAzarov Oleksii Dmytrovych, Lukaschuk Oleksandr Oleksandrovych, Zakharchenko Serhii Mykhailovych, Bohomolov Serhii Vitaliiovych, Tarasova Olha Mykolaivna

Назва патенту російськоюВходное устройство схемы сравнения токов

Автори російськоюАзаров Алексей Дмитриевич, Лукащук Александр Александрович, Захарченко Сергей Михайлович, Богомолов Сергей Витальевич, Тарасова Ольга Николаевна

МПК / Мітки

Мітки: струмів, вхідний, пристрій, порівняння, схемі

Код посилання

<a href="https://ua.patents.su/7-19379-vkhidnijj-pristrijj-skhemi-porivnyannya-strumiv.html" target="_blank" rel="follow" title="База патентів України">Вхідний пристрій схеми порівняння струмів</a>

Попередній патент: Поліциклоалкілпурини як антагоністи аденозинових рецепторів

Наступний патент: Спосіб керування процесом експлуатації шарошкового долота

Випадковий патент: Горілка особлива "вишиванка"