Мон-пристрій включення високих напруг на напівпровідниковій інтегральній схемі

Формула / Реферат

1. МОН-пристрій включення високих напруг на напівпровідниковій інтегральній схемі, який відрізняється тим, що він містить перший транзистор, що розташований послідовно з другим транзистором між першим виводом для позитивних напруг і другим виводом для високої негативної напруги, третій транзистор, що розташований послідовно з четвертим транзистором між першим виводом та другим виводом, причому перший і третій транзистори з'єднані безпосередньо з першим виводом, виводи затворів другого і четвертого транзисторів з'єднані з другим виводом, вивід затвора першого транзистора з'єднаний з точкою, що утворює вихідний вивід з'єднання третього та четвертого транзисторів, вивід затвора третього транзистора з'єднаний з точкою з'єднання першого і другого транзисторів, причому п'ятий транзистор своєю навантажувальною ділянкою включений паралельно навантажувальній ділянці першого транзистора і вивід затвора цього п'ятого транзистора утворює керувальний вивід для вхідного сигналу, причому виконані в n-ванні транзистори та підкладка є р – провідними, причому транзистори мають такі параметри, що при /подаванні позитивної напруги на перший вивід, негативної напруги на другий вивід та позитивної напруги на керувальний вивід спочатку точка з'єднання між першим та другим транзисторами підтягується до другого виводу.

2. МОН-пристрій за пунктов 1, який відрізняється тим, що паралельно до навантажувальної ділянки третього транзистора включена навантажувальна ділянка шостого транзистора, затвор якого через навантажувальну ділянку восьмого транзистора з'єднаний з виводом для інвертованого вхідного сигналу, що вивід затвора восьмого транзистора з'єднаний з керувальним виводом для вхідного сигналу, що між першим виводом і виводом затвора шостого транзистора утворена навантажувальна ділянка сьомого транзистора, вивід затвора якого з'єднаний з вихідним, виводом та шостий й сьомий транзистори виконані як транзистори того самого типу провідності, що й підкладка, і у ванні, а восьмий транзистор виконаний протилежного типу провідності.

3. МОН-пристрій включення високих напруг на напівпровідниковій інтегральній схемі, який відрізняється тим, що він містить перший транзистор, навантажувальна ділянка якого включена між вихідним виводом та другим виводом високої негативної напруги, другий транзистор, навантажувальна ділянка якого включена між виводом затвора першого транзистора і другим виводом, третій транзистор, навантажувальна ділянка якого включена паралельно навантажувальній ділянці другого транзистора і вивід затвора якого з'єднаний з виводом його витоку, причому виконані, принаймні, в одній ванні транзистори і напівпровідникова підкладка є р – провідними, а вивід затвора другого транзистора через схему інвертування напруги з'єднаний з виводом для високого позитивного імпульсу напруги.

4.МОН-пристрій за пунктом 3, який відрізняється тим, що вивід затвора другого транзистора через навантажувальну ділянку четвертого транзистора з'єднаний з керувальним виводом для інвертованого вхідного сигналу, що вивід затвора четвертого транзистора з'єднаний з керувальним виводом для вхідного сигналу і що транзистор виконаний того ж типу провідності, що і напівпровідникова підкладка, і у ванні.

5-МОН-пристрій за будь - яким з пунктів 3 або 4, який відрізняється тим, що схема інвертування напруги містить конденсатор, перший вивід якого утворює вхідний вивід схеми інвертування напруги і другий вивід якого з'єднаний через п'ятий транзистор, що включений як діод в прямому напрямку, з виводом корпусу та через шостий транзистор, що включений як діод у напрямку запирання, з вихідним виводом схеми інвертування напруги, і що транзистори виконані того ж типу провідності, що і напівпровідникова підкладка, і, принаймні, в одній ванні.

6.МОН-пристрій за будь-яким з пунктів 3-5, який відрізняється тим, що вихідний вивід через сьомий транзистор з'єднаний з пристроєм включення високих позитивних напруг, причому вивід затвора сьомого транзистора з'єднаний з керувальним виводом для керувального сигналу.

Текст

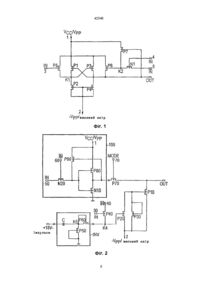

1 МОН-пристрій включення високих напруг на напівпровідниковій інтегральній схемі, який відрізняється тим, що він містить перший транзистор, що розташований послідовно з другим транзистором між першим виводом для позитивних напруг і другим виводом для високої негативної напруги, третій транзистор, що розташований послідовно з четвертим транзистором між першим виводом та другим виводом, причому перший і третій транзистори з'єднані безпосередньо з першим виводом, виводи затворів другого і четвертого транзисторів з'єднані з другим виводом, вивід затвора першого транзистора з'єднаний з точкою, що утворює вихідний вивід з'єднання третього та четвертого транзисторів, вивід затвора третього транзистора з'єднаний з точкою з'єднання першого і другого транзисторів, причому п'ятий транзистор своєю навантажувальною ділянкою включений паралельно навантажувальній ДІЛЯНЦІ першого транзистора і вивід затвора цього п'ятого транзистора утворює керувальний вивід для вхідного сигналу, причому виконані в n-ванні транзистори та підкладка є р-провідними, причому транзистори мають такі параметри, що при подаванні позитивної напруги на перший вивід, негативної напруги на другий вивід та позитивної напруги на керувальний вивід спочатку точка з'єднання між першим та другим транзисторами підтягується до другого виводу 2 МОН-пристрій за пунктом 1, який відрізняється тим, що паралельно до навантажувальної ділянки третього транзистора включена навантажувальна ділянка шостого транзистора, затвор якого через навантажувальну ділянку восьмого транзистора ю ІНТЕГРАЛЬНІЙ з єднаний з виводом для інвертованого вхідного сигналу, що вивід затвора восьмого транзистора з'єднаний з керувальним виводом для вхідного сигналу, що між першим виводом і виводом затвора шостого транзистора утворена навантажувальна ділянка сьомого транзистора, вивід затвора якого з'єднаний з вихідним виводом, та шостий й сьомий транзистори виконані як транзистори того самого типу провідності, що й підкладка, і у ванні, а восьмий транзистор виконаний протилежного типу провідності 3 МОН-пристрій включення високих напруг на напівпровідниковій інтегральній схемі, який відрізняється тим, що він містить перший транзистор, навантажувальна ділянка якого включена між вихідним виводом та другим виводом високої негативної напруги, другий транзистор, навантажувальна ділянка якого включена між виводом затвора першого транзистора і другим виводом, третій транзистор, навантажувальна ділянка якого включена паралельно навантажувальній ДІЛЯНЦІ другого транзистора і вивід затвора якого з'єднаний з виводом його витоку, причому виконані, принаймні, в одній ванні транзистори і напівпровідникова підкладка є р-провідними, а вивід затвора другого транзистора через схему інвертування напруги з'єднаний з виводом для високого позитивного імпульсу напруги 4 МОН-пристрій за пунктом 3, який відрізняється тим, що вивід затвора другого транзистора через навантажувальну ділянку четвертого транзистора з'єднаний з керувальним виводом для інвертованого вхідного сигналу, що вивід затвора четвертого транзистора з'єднаний з керувальним виводом для вхідного сигналу і що транзистор виконаний того ж типу провідності, що і напівпровідникова підкладка, і у ванні 5 МОН-пристрій за будь-яким з пунктів 3 або 4, який відрізняється тим, що схема інвертування напруги містить конденсатор, перший вивід якого утворює вхідний вивід схеми інвертування напруги і другий вивід якого з'єднаний через п'ятий транзистор, що включений як діод в прямому напрямку, з виводом корпусу та через шостий транзистор, що включений як діод у напрямку запирання, - з вихідним виводом схеми інвертування напруги, і що транзистори виконані того ж типу провідності, що і напівпровідникова підкладка, і, принаймні, в одній ванні о 00 О 42048 6 МОН-пристрій за будь-яким з пунктів 3-5, який відрізняється тим, що вихідний вивід через сьомий транзистор з'єднаний з пристроєм включення високих позитивних напруг, причому вивід затвора сьомого транзистора з'єднаний з керувальним виводом для керувального сигналу При реалізації електронних схем у вигляді інтегральної схеми на напівпровідниковому кристалі ІНОДІ є необхідним підключати більш високі, ніж напруга живлення, напруги на кристалі до схем або їх частин форми розвитку, винаходу, яким віддається перевага, наведені у залежних пунктах формули винаходу Особлива перевага ВІДПОВІДНОГО винаходу пристрою міститься в тому, що для технологічної реалізації немає потреби у жодній коштовній установці або, ВІДПОВІДНО, довшому часі нагріву для операції дифузного процесу Нема також потреби у жодній додатковій операції процесу, через те, що в КМОН-техніці транзистори того ж типу проводимості, що й підкладка, вже реалізовані у ванні, і, таким чином, така операція процесу при реалізації КМОН-техніки вже існує ВІДПОВІДНИЙ винаходу пристрій є особливо придатним для включення негативних або у формі подальшого розвитку також позитивних напруг програмування, або ВІДПОВІДНО напруг стирання, на ЛІНІЯХ слів флеш-накопичувача або також постійного накопичувача, що електронно стирається та програмується (EEPROM), причому кожного разу можна обрати лише одну ЛІНІЮ СЛІВ Винахід пояснюється нижче на прикладах виконання за допомогою фігур При цьому на фігурах показано Фігура 1- перший варіант ВІДПОВІДНОГО винаходу пристрою, Фігура 2 - другий варіант ВІДПОВІДНОГО винаходу пристрою та Фігура 3 - зображення прикладення напруг за першим варіантом, щоб отримати бажану вихідну напругу Пристрій, що показаний на Фігурі 1, дозволяє вмикати високу напругу Vpp, що прикладена на його першому виводі або прикладену на другому виводі негативну напругу -Vpp у залежності від вихідного сигналу IN, IN на керувальних виводах 3, 4, 5 на вихідний вивід OUT Приклад відноситься до реалізації пристрою у вигляді інтегральної схеми в р-підкладці з виконаними у п-ваннах р-канальними транзисторами Еквівалентним чином можуть реалізовуватися у п-підкладці п-канальні транзистори Між першим виводом 1 і другим виводом 2 включена перша послідовна схема з першого транзистора Р1 та другого транзистора Р2, а також паралельно їй друга послідовна схема з третього транзистора РЗ та четвертого транзистора Р4 Виводи затворів другого і четвертого транзисторів Р2, Р4 з'єднані також із другим виводом 2, так що обидва транзистори діють як реалізовані на діодах джерела струму Вивід затвора третього транзистора РЗ з'єднано з точкою з'єднання К1 першого та другого транзисторів Р1, Р2, а вивід затвора першого транзистора Р1 з'єднаний з утворюючою вихідний вивід OUT точкою з'єднання третього транзистора РЗ та четвертого транзистора Р4 Транзистори Р1-Р4 при цьому мають такі параметри, що у випадку, коли другий і четвертий транзистори Р2, Р4 включені так, що проводять, Ці ВИСОКІ ПОЗИТИВНІ або негативні напруги можуть при цьому або підводитися до кристала додатково до звичайних напруг живлення, або створюватися за допомогою насосів заряду на кристалі із напруг живлення В кожному випадку слід турбуватися про надійне і швидке включення, причому падіння напруги на перемикачі має бути якомога меншим В сучасних флеш-накопичувачах (flash-накопичувачі, що стираються світловим спалахом), а в майбутньому також і для стандартних постійних накопичувачів, що програмуються і електронно стираються (EEPROM), необхідно прикладати до них для вибору лінії слів негативну напругу лінії слів Не вибрані лінії слів утримуються в цьому випадку на потенціалі 0 В В ЕР 0 456 623 А2 негативно поляризують імпульсною позитивною високою напругою через конденсатор в схемі інвертування напруги затвор р-МОН-передавального транзистора, так що негативна напруга потрапляє від насоса заряду до лінії слів накопичувача Внаслідок струмів витоку в з'єднаннях ця схема повинна експлуатуватися в пакетному режимі роботи Це означає, що до кінця програмування потрібні імпульси, що повторюються, що призводить до високої потужності трат Так як на кристалі накопичувача окрім накопичувальних комірок у більшості випадків виконані додаткові ЛОГІЧНІ схеми в МОН-техніці і, таким чином, такі схеми ВІДПОВІДНО З стандартом експлуатуються з суто позитивними напругами, повинна бути гарантована ІЗОЛЯЦІЯ негативної напруги відносно підкладки напівпровідникової інтегральної схеми Це може бути досягнуто, наприклад, за допомогою ізольованих ванн, у так званій техніці «triple well» При цьому при р-підкладці р-ванна для п-канальних транзисторів розташована в глибокій пванні та ізольована нею від р-підкладки Така глибока ванна отримується за рахунок високоенергетичного упровадження, звичайно від 1 до 3 МеВ, з фосфором у якості легуючого матеріалу, або за рахунок більш низької енергії та екстремально низького часу дифузії Задачею винаходу є створення МОН-пристрою для включення негативних, а у формі подальшого розвитку також позитивних високих напруг через суто позитивний рівень включення на напівпровідниковій інтегральній схемі, що не потребує ніякої ізольованої ванни (ніяких ізольованих ванн) Ця задача вирішується пристроями згідно з пунктами 1 та 3 формули винаходу Подальші 42048 спочатку точка з'єднання К1 першого і другого транзисторів Р1, Р2 підтягується до другого виводу 2 так, що третій транзистор РЗ проводить і в такий спосіб підтягує вихідний вивід OUT до позитивного потенціалу, прикладеного на першому виводі 1, так що перший транзистор замикається Паралельно навантажувальній ДІЛЯНЦІ першого транзистора Р1 включена навантажувальна ділянка п'ятого транзистора Р5 Виведення затвора цього п'ятого транзистора Р5 з'єднане з управляючим виводом З З цією частиною наведеного на Фігурі 1 пристрою вже є можливість прикладену на виводі 2 високу негативну напругу -Vpp включати на вихідний вивід OUT за допомогою прикладеного на керувальному вході 3 вхідного сигналу IN, якщо на першому виводі 1 прикладена напруга живлення Vcc напівпровідникової інтегральної схеми Це подано на Фігурі 3 у позначених інтервалах часу Доки на керувальному виводі 3 стан вхідного сигналу IN відповідає високому логічному рівню High, а саме для КМОН-схем відповідає приблизно значенню позитивної напруги живлення Vcc, п'ятий транзистор Р5 замикається Через те, що другий та четвертий транзистори Р2, Р4 знаходяться у провідному стані, внаслідок підхожого вибору параметрів транзисторів Р1-Р4 точка з'єднання К1 першого і другого транзисторів підтягується до потенціалу -Vpp на другому виводі 2 так, що третій транзистор РЗ проводить і в такий спосіб підтягає вихідний вивід OUT до потенціалу напруги живлення Vcc, прикладеного на першому виводі 1, за рахунок чого перший транзистор Р1 замикається й пристрій за рахунок цього блоковано в цьому стані Цей стан подано в інтервалі часу І Фігури 3 Якщо тепер, як показано в інтервалі часу II Фігури 3, стан вхідного сигналу IN на керувальному вході 3 змінюється до низького логічного стану Low, тобто приймає таким чином значення 0 В, то п'ятий транзистор Р5 проводить, за рахунок чого точка з'єднання К1 підтягується до потенціалу напруги живлення Vcc і за рахунок цього третій транзистор РЗ замикається Тепер внаслідок провідного четвертого транзистора Р4 вихідний вивід OUT підтягується до прикладеного на другому виводі 2 високого негативного потенціалу -Vpp, за рахунок чого перший транзистор Р1 також проводить і за рахунок цього пристрій знов блокується в цьому стані Якщо також прикладена на першому виводі 1 висока позитивна напруга Vpp повинна приводити до відкривання вихідного виводу OUT, то описана дотепер схема повинна бути доповнена ВІДПОВІДНО пристрою згідно з Фігурою 1 Для цього паралельно до навантажувальної ділянки третього транзистора РЗ включена навантажувальна ділянка шостого транзистора Р6 Між першим виводом 1 та виводом затвора шостого транзистора Р6 включена навантажувальна ділянка сьомого транзистора Р7, вивід затвора якого з'єднаний з вихідним виводом OUT Виведення затвора шостого транзистора Р6 через навантажувальну ділянку першого n-канального транзистора N 1 з'єднане з керувальним виводом 6 для інвертованого вхідного сигналу IN , причому вивід затвора першого пканального транзистора N1 з'єднаний з керувальним входом 4 для вхідного сигналу IN Виведення затвора першого n-канального транзистора N1 могло б, звичайно, так само бути з'єднаним з керувальним входом 3 Через те, що перший п-канальний транзистор N1 на жодному зі своїх виводів не може прийти в контакт з високим негативним потенціалом -Vpp, немає потреби виконувати його в глибокій ванні Щоб подавати до вихідного виводу OUT високу позитивну напругу Vpp, її прикладають на першому виводі 1 замість напруги живлення Vcc Другий вивід 2 утримується в підвішеному стані, що може відбуватися або шляхом відключення джерела високого негативного потенціалу -Vpp, або за рахунок того, що вихід цього джерела приймає високоомний стан Поки вхідний сигнал IN і далі приймає низький логічний стан Low, вихідний вивід OUT залишається з'єднаним через четвертий транзистор Р4 із другим виводом 2 і таким чином також знаходиться у підвішеному стані Це наведено в інтервалі часу III на Фігурі 3 Якщо, проте, вхідний сигнал IN приймає високий логічний стан High, то п'ятий транзистор Р5 знову замикається, у той час як перший n-канальний транзистор N1 відкривається і тим самим до затвору шостого, транзистора Р6 прикладається низький логічний стан Low, у результаті чого він стає провідним і підтягає вихідний вивід OUT до високого позитивного потенціалу Vpp, прикладеного на першому виводі 1 За рахунок цього сьомий транзистор Р7 надійно замикається, так що шостий транзистор Р6 залишається в провідному стані Цей випадок наведено в інтервалі часу IV Фігури З При застосуванні наведенного на Фігурі 1 пристрою, ВІДПОВІДНО до винаходу, у флеш-накопичувачі кожній лінії слів надають ВІДПОВІДНО такий пристрій та через вибір стану вихідного сигналу IN прикладена на першому виведенні 1 висока позитивна напруга Vpp або прикладена на другому виводі 2 висока негативна напруга -Vpp може прикладатися до вихідного виводу OUT пристрою і у такий спосіб необхідна напруга стирання, або ВІДПОВІДНО напруга програмування прикладається до відповідної лінії слів флеш-накопичувача Фігура 2 показує інший ВІДПОВІДНИЙ винаходові пристрій, яким до вихідного виводу OUT цього пристрою може включатися або висока позитивна напруга Vpp або висока негативна напруга -Vpp Яка з цих напруг буде підключена залежить зновтаки від того, який стан приймає вихідний сигнал IN на керувальних входах 3-6 для цього вхідного сигналу IN або ВІДПОВІДНО інвертований сигнал IN , а також від стану керувального сигналу MODE, прикладеного до іншого вхідного виводу 7 Також і в цьому варіанті усі транзистори, що можуть прийти в контакт з високою негативною напругою -Vpp, є транзисторами того ж типу провідності, що й підкладка у прикладі на Фігурі 2, де обрана р-підкладка, наведені там транзистори є таким чином рканальними транзисторами Між вихідним виводом OUT та другим виводом 2 для високого негативного потенціалу -Vpp включена навантажувальна ділянка першого транзистора Р10 Між виводом затвора цього першого транзистора Р10 та другим виводом 2 включена навантажувальна ділянка другого транзистора Р20 і паралельно до нього навантажувальна ділянка третього транзистора РЗО Виведення затвора цього третього транзистора РЗО з'єднане з його виводом витоку, так що цей тран 42048 зистор включений у якості діода Якщо тепер на виводі затвора другого транзистора Р20 прикладена висока негативна напруга, то цей другий транзистор Р20 відкривається, за рахунок цього вивід затвора першого транзистора Р10 підтягується до прикладеного на другому виводі 2 високого негативного потенціалу -Vpp За рахунок цього, з одного боку, перший транзистор Р10 відкривається, внаслідок чого високий негативний потенціал -Vpp підключається до вихідного виводу OUT і, з іншого боку, включений у якості діода третій транзистор РЗО починає проводити, у результаті чого вивід затвора першого транзистора Р10 утримується на високому негативному потенціалі -Vpp За рахунок цього є можливість навантажувати вивід затвора другого транзистора Р20 тільки імпульсною негативною напругою Вона отримується з високого позитивного імпульсу напруги близько 18 В за допомогою схеми інвертування напруги INV Ця схема інвертування напруги INV утворена звичайним чином з конденсатора С, що включений послідовно з п'ятим транзистором Р50, включеним у якості діода в прямому напрямку, шостим транзистором Р60, включеним у якості діода в напрямку запирання, котрий з'єднаний з точкою з'єднання конденсатора С та п'ятого транзистора Р50 Не з'єднаний з транзисторами Р50, Р60 вивід конденсатора С утворює вхідний вивід, а анод включеного в напрямку запирання діода Р60 - вихідний вивід схеми інвертування напруги INV Якщо, наприклад, у флеш-накопичувачі одна з багатьох ЛІНІЙ слів повинна бути навантажена негативною напругою програмування, то кожна з ЛІНІЙ СЛІВ може бути з'єднана вихідним виводом такого ВІДПОВІДНОГО винаходу пристрою Щоб вибрати один з пристроїв, можна прикладати до пристрою, що підлягає вибору, або позитивний (наприклад, 18В) імпульс напруги, або з'єднувати вивід затвора другого транзистора Р20 через навантажувальну ділянку четвертого транзистора Р40 з керувальним виводом 40, що навантажений інвертованим вхідним сигналом IN Виведення затвора цього четвертого транзистора Р40 з'єднане при цьому з вхідним виводом ЗО,котрий навантажений нешвертованим вхідним сигналом IN Якщо вхідний сигнал приймає стан високого рівня High, то четвертий транзистор Р40 замикається так, що негативний імпульс напруги підводиться з виходу схеми інвертування напруги INV до виводу затво ра другого транзистора Р20 Проте, якщо вхідний сигнал приймає стан низького логічного рівня Low, то четвертий транзистор Р40 проводить, так що негативний імпульс напруги відводиться з виходу схеми інвертування напруги INV до вхідного виводу 40 через четвертий транзистор Р40 Шляхом вибору стану вхідного сигналу IN на приведених у ВІДПОВІДНІСТЬ різним ЛІНІЯМ слів флеш-накопичувача пристроях можуть бути вибрані ВІДПОВІДНІ пристрої й утакий спосіб лінії слів На Фігурі 2 наведений, крім того, пристрій 100 для включення високої позитивної напруги Vpp до вихідного виводу OUT, що, наприклад, відомо з публікації Proceedings ISSCC 1991, crop 260 Вихід ЦІЄЇ схеми з'єднаний через сьомий транзистор Р70 з вихідним виводом OUT, причому вивід затвора цього сьомого транзистора Р70 з'єднаний з вхідним виводом 70 для керувального сигнала MODE Якщо на вихідному виводі OUT повинна включатися висока негативна напруга -Vpp, то на вхідному виводі 70 керувальний сигнал MODE повинен приймати високий логічний стан High, так що сьомий транзистор Р70 замикається і цим висока позитивна напруга -Vpp від пристрою 100 для включення високих позитивних напруг ізольована, тому що вона містить також n-канальні транзистори, що не повинні виконуватися в глибоких ізолювальних ваннах У пристрої для включення високих позитивних напруг між першим виводом 1 для позитивних напруг та виводом корпусу включено послідовну схему з восьмого транзистора Р80 та першого пканального транзистора N10 Виводи затворів цих обох транзисторів з'єднані один з одним та через навантажувальну ділянку другого п-канального транзистора N20 - з керувальним виводом 50, до якого може прикладатися вхідний сигнал IN Виведення затвора цього другого п-канального транзистора N20 з'єднане з вхідним виводом 60, до якого може прикладатися інвертований вхідний сигнал IN Точка з'єднання восьмого транзистора Р80 та першого n-канальното транзистора N10 утворює вхідний вивід цього пристрою 100 для включення високих позитивних напруг і з'єднана з виводом затвора дев'ятого транзистора Р90, навантажувальна ділянка якого розташована між першим виводом 1 та точкою з'єднання виводів затвора восьмого транзистора Р80 і першого п-канального транзистора N10 42048 14 f P7 a P3,J UP1 N1 Ц.Р6 K2 K1 _гтт IN IN OUT LP2 p4i 2, -Vpp/високий опір Фіг. 1 OUT О—O-\ +18VІмпульси -Vpp/ високий опір Фіг. 2 42048 •Vpp П vcc -Vpp IN VCC •Vpp V OUT CC -Vpp ФІГ. 3 Тираж 50 екз Відкрите акціонерне товариство «Патент» Україна, 88000, м Ужгород, вул Гагаріна, 101 (03122) 3-72-89 (03122) 2-57-03

ДивитисяДодаткова інформація

Назва патенту англійськоюMos-device for high voltage connection at semiconductor integrated circuit

Автори англійськоюHanneberg Armin, Tempel Georg

Назва патенту російськоюМоп-устройство включения высоких напряжений на полупроводниковой интегральной схеме

Автори російськоюХаннеберг Армин, Темпель Георг

МПК / Мітки

МПК: H03K 17/10, H03K 17/693, G11C 16/06

Мітки: інтегральній, напруг, схемі, високих, напівпровідниковий, включення, мон-пристрій

Код посилання

<a href="https://ua.patents.su/6-42048-mon-pristrijj-vklyuchennya-visokikh-naprug-na-napivprovidnikovijj-integralnijj-skhemi.html" target="_blank" rel="follow" title="База патентів України">Мон-пристрій включення високих напруг на напівпровідниковій інтегральній схемі</a>

Попередній патент: Спосіб очищення внутрішньої поверхні теплообмінного обладнання

Наступний патент: Спосіб очистки висококонцентрованого водно-спиртового розчину

Випадковий патент: Композиції для лікування нудоти і блювання центрального походження