Мікропроцесорний контролер з паралельною обробкою інформації

Номер патенту: 47570

Опубліковано: 10.02.2010

Автори: Щербакова Ілона Олександрівна, Подлєсних Євгеній Геннадійович, Возненко Анатолій Дмитрович, Стасюк Олександр Іонович, Желєзняк Анатолій Леонідович, Гончарова Лідія Леонідівна, Опанасенко Володимир Миколайович

Формула / Реферат

Мікропроцесорний контролер з паралельною обробкою інформації, що містить блок пам'яті і регістр, який відрізняється тим, що в нього введено мікропроцесор, чотири дешифратори, чотирипортовий модуль, два регістри, шифратори дискретних сигналів, аналого-цифровий перетворювач, формувач аналогових сигналів, ключі, паралельний матричний процесор, формувачі управляючих сигналів, причому вихід шини адреси першого порту мікропроцесора підключений до входів двох регістрів і шини адреси чотирипортового модуля, вхід шини даних якого з'єднаний з входом шини даних блока пам'яті, паралельного матричного процесора, шифраторів дискретних сигналів, аналого-цифрового перетворювача, третього регістра і виходом шини даних другого порту мікропроцесора, вихід шини адреси третього порту мікропроцесора підключений n/3-старшими розрядами до входу адреси першого дешифратора, n/3-середніми розрядами до входу адреси другого дешифратора і n/3-молодшими розрядами до входу адреси третього дешифратора, стробуючі входи яких об'єднані і підключені до стробуючого виходу мікропроцесора, вихід першого регістра з'єднаний з входом шини адреси блока пам'яті, вихід другого регістра підключений до входу четвертого дешифратора, виходи якого з'єднані з відповідними входами вибору схеми аналого-цифрового перетворювача, блока пам'яті, паралельного матричного процесора і чотирипортового модуля, входи запису і читання якого з'єднані відповідно з входом запису і читання блока пам'яті, першого і третього регістрів, аналого-цифрового перетворювача, паралельного матричного процесора і виходами запису і читання мікропроцесора, вихід третього регістра з'єднаний з входом паралельного матричного процесора, перший і другий виходи першого дешифратора підключені відповідно до перших управляючих входів шифраторів дискретних сигналів, і перших управляючих входів електронних ключів, підключених своїм виходом через формувач аналогових сигналів до входу аналого-цифрового перетворювача, а формувачі управляючих сигналів виконані у вигляді матриці, перші управляючі входи кожного і (і=1, 2...) рядка якої з'єднані з і-м виходом третього дешифратора, другі управляючі входи формувачів управляючих сигналів кожного j-гo стовпця матриці підключені до j-гo виходу (j=1, 2,...m) другого дешифратора, (m+і)-й вихід якого підключений до других управляючих входів відповідно (m+і)-го ключа і шифратора дискретних сигналів.

Текст

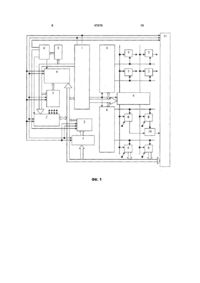

Мікропроцесорний контролер з паралельною обробкою інформації, що містить блок пам'яті і регістр, який відрізняється тим, що в нього введено мікропроцесор, чотири дешифратори, чотирипортовий модуль, два регістри, шифратори дискретних сигналів, аналого-цифровий перетворювач, формувач аналогових сигналів, ключі, паралельний матричний процесор, формувачі управляючих сигналів, причому вихід шини адреси першого порту мікропроцесора підключений до входів двох регістрів і шини адреси чотирипортового модуля, вхід шини даних якого з'єднаний з входом шини даних блока пам'яті, паралельного матричного процесора, шифраторів дискретних сигналів, аналого-цифрового перетворювача, третього регістра і виходом шини даних другого порту мікропроцесора, вихід шини адреси третього порту мікропроцесора підключений n/3старшими розрядами до входу адреси першого дешифратора, n/3-середніми розрядами до входу U 2 (19) 1 3 що містить блоки п'яті станів, схему порівняння, вузол логічного керування, лічильник адреси і модуль зв'язку, при цьому перший вхід контролера підключений до першого входу модуля зв'язку, перший вихід якого підключений до третього входу схеми порівняння, а другий вхід модуля зв'язку підключений до другого входу блока пам'яті переходів. Недоліком відомого пристрою є невисока швидкість обробки інформації в зв'язку з неможливістю її паралельної обробки, а тільки послідовної яку виконує відомий контролер і обмежені функціональні можливості, в зв'язку з тим, що в відомому пристрої не виконуються в реальному часі функції моніторингу технічного стану об'єкта управління, а також корегування його функціонування шляхом формування управлінських сигналів на основі первинної аналогової і дискретної інформації. Найбільш близьким за своєю технічною суттєвістю є програмований логічний контролер [3], що включає блок пам'яті, регістр, схему порівняння, регістр адреси, блок пам'яті заборонених станів, блок індикації та блок логічного керування, причому вихід регістра є виходом пристрою, а перший вхід з'єднаний з другим входом блока пам'яті та входом блока пам'яті заборонених станів, перший вихід якого підключений до четвертого входу блока логічного керування, а другий вхід з'єднаний з другим входом вихідного регістру. Недоліком даного пристрою є низька швидкодія, так як в відомому пристрої оброблюється тільки послідовно логічна інформація, яка і використовується для керування, а не обробляються паралельно математичні залежності на основі швидкодіючих матричних процесорів, а також значно обмежені функціональні можливості в зв'язку з тим, що в відомому пристрої не виконується з єдиних інформаційних позицій на основі первинної аналогової і дискретної інформації моніторинг технічного стану об'єкта керування з метою формування управлінських сигналів в реальному часі. За основу корисної моделі поставлена задача створення мікропроцесорного контролера з паралельною обробкою інформації надвисокої швидкодії з розширеними функціональними можливостями для проведення в реальному часі реєстрації аналогових і дискретних сигналі, що поступають з об'єктів керування, паралельної їх обробки на основі математичних і логічної залежностей в темпі надходження інформації, що стало можливим завдяки організації обчислювальної структури з використанням паралельних матричних процесорів, що досягається за рахунок введення нових блоків і зв'язків між ними завдяки чому відкрилась можливість організовувати обчислення з єдиних інформаційних позицій і реалізувати моніторинг технічного стану об'єктів керування, покращити глибину і рівень їх діагностування в процесі роботи, а також значно збільшити рівень надійність завдяки спроможності ідентифікувати передаварійні і аварійні режими їх роботи, а також формувати управлінські сигнали для стабільності функціонування об'єктів в штатному режимі і формувати файли експрес і повної інформації для передачі на всі рівні управління. 47570 4 Поставлена мета досягається шляхом включення до мікропроцесорного контролера з паралельною обробкою інформації мікропроцесора, чотирьох дешифраторів, чотирьох портового модуля, двох регістрів, шифраторів дискретних сигналів, аналого-цифрового перетворювача, формувача аналогових сигналів, ключів, паралельного матричного процесора, формувачів управляючих сигналів, причому вихід шини адреси першого порту мікропроцесора підключений до входів двох регістрів і шини адреси чотирьох портового модуля, вхід шини даних якого з'єднаний з входом шини даних блоку пам'яті, паралельного матричного процесора, шифраторів дискретних сигналів, аналого-цифрового перетворювача, третього регістра і виходом шини даних другого порту мікропроцесора, вихід шини адреси третього порту мікропроцесора підключений n/3-старшими розрядами до входу адреси першого дешифратора, n/3- середніми розрядами до входу адреси другого дешифратора і n/3- молодшими розрядами до входу адреси третього дешифратора, стробуючі входи яких об'єднані і підключені до стробуючого виходу мікропроцесора, вихід першого регістра з'єднаний з входом шини адреси блоку пам'яті, вихід другого регістра підключений до входу четвертого дешифратора, виходи якого з'єднані з відповідними входами вибору схеми аналого-цифрового перетворювача, блоку пам'яті, паралельного матричного процесора і чотирьох портового модуля, входи запису і читання якого з'єднані відповідно з входом запису і читання блоку пам'яті, першого і третього регістрів, аналого-цифрового перетворювача, паралельного матричного процесора і виходами запису і читання мікропроцесора, вихід третього регістра з'єднаний з входом паралельного матричного процесора, перший і другий виходи першого дешифратора підключені відповідно до перших управляючих входів шифраторів дискретних сигналів, і перших управляючих входів електронних ключів підключених своїм виходом через формувач аналогових сигналів до входу аналогоцифрового перетворювача, а формувачі управляючих сигналів виконані у вигляді матриці перші управляючі входи кожної і (і=1.2...), строчки якої з'єднані з і-м виходом третього дешифратора, другі управляючі входи формувачів управляючих сигналів кожного j-гo стовпця матриці підключені до jгo виходу (j=1,2,..m) другого дешифратора, (m+і)-й вихід якого підключений до других управляючих входів відповідно (m+і)-го ключа і шифратора дискретних сигналів. На Фіг.1 наведено структурну схему мікропроцесорного контролера з паралельною обробкою інформації. На Фіг.2 наведено блок - схемою алгоритму роботи мікропроцесорного контролера з паралельною обробкою інформації. Мікропроцесорний контролер з паралельною обробкою інформації (Фіг.1) включає мікропроцесор 1, чотирьох портовий модуль 2, паралельний матричний процесор 3, блок пам'яті 4, три регістра 5, чотири дешифратора 6, формувачі управляючих сигналів 7, ключі 8, шифратори дискретних сигналів 9, формувач аналогових сигналів 10, аналого-цифровий перетворювач 11. Вихід шини адреси першого 5 порту мікропроцесора 1 підключений до входів двох регістрів 5 і шини адреси чотирьох портового модуля 2, вхід шини даних якого з'єднаний з входом шини даних блоку пам'яті 4, паралельного матричного процесора 3, шифраторів, дискретних сигналів 9, аналого-цифрового перетворювача 11, третього регістра 5 і виходом шини даних другого порту мікропроцесора 1. Вихід шини адреси третього порту мікропроцесора 1 підключений n/3старшими розрядами до входу адреси першого дешифратора 6, n/3- середніми розрядами до входу адреси другого дешифратора 6 і n/3- молодшими розрядами до входу адреси третього дешифратора 6, стробуючі входи яких об'єднані і підключені до стробуючого виходу мікропроцесора 1. Вихід першого регістра 5 з'єднаний з входом шини адреси блоку пам'яті 4, вихід другого регістра 5 підключений до входу четвертого дешифратора 6, виходи якого з'єднані з відповідними входами вибору схеми аналого-цифрового перетворювача 11, блоку пам'яті 4, паралельного матричного процесора 3 і чотирьох портового модуля 2, входи запису і читання якого з'єднані відповідно з входом запису і читання блоку пам'яті 4, першого і третього регістрів 5, аналого-цифрового перетворювача 11, паралельного матричного процесора 3 і виходами запису і читання мікропроцесора 1. Вихід третього регістра 5 з'єднаний з входом паралельного матричного процесора 3. Перший і другий виходи першого дешифратора 6 підключені відповідно до перших управляючих входів шифраторів дискретних сигналів 9, і перших управляючих входів ключів 8 підключених своїм виходом через формувач аналогових сигналів 10 до входу аналого-цифрового перетворювача 11. Формувачі управляючих сигналів 7 виконані у вигляді матриці перші управляючі входи кожної і (і=1.2...), строчки якої з'єднані з і-м виходом третього дешифратора 6, другі управляючі входи формувачів управляючих сигналів 7 кожного j-гo стовпця матриці підключені до j-гo виходу (j=1,2,..m) другого дешифратора 6, (m+і)-й вихід якого підключений до других управляючих входів відповідно (m+і)-го ключа 8 і шифратора дискретних сигналів 9. Мікропроцесор 1 мікропроцесорного контролера з паралельною обробкою інформації виконаний, наприклад, у вигляді одно кристального мікропроцесора KM 1816 BE 51. Чотирьох портовий модуль 2 виконаний, наприклад, у вигляді інтегральної схеми ST16C554DCJ. Робота мікропроцесорного контролера з паралельною обробкою інформації (Фіг.1) проводиться у відповідності з наведеною блок-схемою алгоритму роботи на Фіг.2. Після запуску мікропроцесорного контролера з паралельною обробкою інформації він працює постійно і згідно алгоритму (Фіг.2) здійснює з єдиних інформаційних позицій в реальному часі моніторинг технічного стану об'єктів керування, ідентифікацію передаварійні і аварійні режимів їх роботи, а також реалізує формування управлінські сигнали для організації функціонування об'єктів в штатному і аварійному режимах, що дозволяє покращити глибину і рівень діагностування, а також значно збільшити рівень надій 47570 6 ність роботи завдяки можливості визначення граничних значень критичного ресурсу. Спочатку на інформаційні входи ключів 8 мікропроцесорного контролера з паралельною обробкою інформації подається аналогові сигнал з виходу датчика реєстрації даних, а на інформаційні входи шифраторів дискретних сигналів 9 подаються дискретні сигнали. Проводиться інсталяція мікропроцесорного контролера з паралельною обробкою інформації, а також обробляється процедура запуску в роботу. Після виконання названих процедур, проводиться аналіз на предмет наявності запиту на обміну інформацією з мікропроцесорним контролером з паралельною обробкою інформації. Якщо процедура обміну інформацією не проводиться, то на першому етапі проводиться постійне читання і реєстрація аналогових і дискретних сигналів на інформаційних входах ключів 8 і інформаційних входах шифраторів дискретних сигналів 9 мікропроцесорного контролера з паралельною обробкою інформації. Далі проводиться паралельна обробка первинних даних в паралельному матричному процесорі 3 і логічна обробка інформації в мікропроцесорі 1 мікропроцесорного контролера з паралельною обробкою інформації. На основі отриманих в результаті пара і логічної обробки даних в мікропроцесорі 1 реалізується визначення критеріїв функціонування об'єктів керування. Якщо об'єкти керування задовольняють вимогам критеріїв, то проводиться процедура визначення технічного стану об'єктів керування. При задовільному стані об'єктів керування формувачами управляючих сигналів 7 мікропроцесорного контролера з паралельною обробкою інформації формуються управлінські сигнали штатного режиму їх функціонування. Після цього вищезазначений процес повторюється до тих пір поки на основі результатів паралельної обробки первинних даних в паралельному матричному процесорі 3 і логічної обробки даних в мікропроцесорі 1 буде визначено, що об'єкти керування не задовольняють вимогам критеріїв, або технічний стан об'єктів , керування не задовільний. Тоді формувачами управляючих сигналів 7 мікропроцесорного контролера з паралельною обробкою інформації формуються аварійні управлінські сигнали не штатного режиму функціонування об'єкта або об'єктів керування. Проводиться реєстрація нештатного режиму функціонування об'єкта або об'єктів керування. Реалізується реєстрація доаварійного, і аварійного режимів до тих пір, поки не закінчиться аварійна ситуація. Після закінчення аварійного режиму мікропроцесором 1 мікропроцесорного контролера з паралельною обробкою інформації формується файл експресінформації і передається через чотирьох портовий модуля 2 на всі рівні управління. Потім на основі паралельної обробки первинних даних в паралельному матричному процесорі 3 і логічної обробки даних в мікропроцесорі 1 мікропроцесорного контролера з паралельною обробкою інформації реалізується оцінка відпрацьованого ресурсу кожного із об'єктів керування і визначається їх залишковий ресурс. Формується файл повної інформації нештатного режиму об'єкта або об'єктів керування їх технічний стан включаючи величину залишкового 7 ресурсу і передається через чотирьох портовий модуля 2 мікропроцесорного контролера з паралельною обробкою інформації на всі рівні управління. Виконується процедура кінця роботи і мікропроцесорний контролер з паралельною обробкою інформації зупиняється. В тому випадку коли при обробці процедури запиту на обміну інформацією необхідно виконувати обмін, то оброблюються процедури запис-читання, запистестування. Якщо необхідно виконувати запис, то в мікропроцесорний контролер з паралельною обробкою інформації передається пакет програм функціонування його і пакет програм нормативної інформації. Після передачі всіх даних виконується процедура кінця роботи і мікропроцесорний контролер з паралельною обробкою інформації готовий до функціонування. Якщо необхідно проводити тестування, то передається пакет тестів, виконується процедура тестування і після виконання тестів мікропроцесорний контролер з паралельною обробкою інформації готова до запуску. У випадку коли тести не виконуються, то формується і передається через чотирьох портовий модуля 2 мікропроцесорного контролера з паралельною обробкою інформації файл інформації про несправність. Якщо необхідно виконувати читання, то із блоку пам'яті 4 читається блок даних, формується експрес-інформація і передається через чотирьох портовий модуля 2 про прочитані дані і виконується процедура кінця читання. Завдяки введенню нових елементів та зв'язків між ними запропонований мікропроцесорний контролер з паралельною обробкою інформації вигідно відрізняється від прототипу. На відміну від прототипу, в якому в зв'язку з низькою швидкодією і обмеженими функціональними можливостями не можливо виконувати в реальному часі моніторинг технічного стану об'єктів керування і в процесі роботи неможливо реалізувати діагностику і ідентифікацію перед аварійних і аварійних режимів, а також формувати управлінські сигнали для стабі 47570 8 льності функціонування об'єктів в штатному режимі. У запропонованому мікропроцесорному контролері з паралельною обробкою інформації за рахунок введення нових блоків, паралельних матричних процесорів і зв'язків між ними стало можливим забезпечити надвисоку швидкодію обробки даних, значно розширити функціональні можливості і організовувати обчислення з єдиних інформаційних позицій, завдяки чому відкрилась можливість реалізувати реальному часі реєстрацію аналогових і дискретних сигналі, що поступають з об'єктів керування, забезпечити паралельну обробки інформації на основі математичних і логічної залежностей в темпі її надходження, реалізувати моніторинг технічного стану об'єктів керування, покращити глибину і рівень їх діагностування в процесі роботи, а також значно збільшити рівень надійність завдяки можливості визначення граничних значень критичного ресурсу, спроможності ідентифікувати перед аварійні і аварійні режими їх роботи і формувати управлінські сигнали для стабільності керуємих об'єктів. Крім того в запропонованому мікропроцесорному контролері з паралельною обробкою інформації стало можливим вести в процесі роботи інсталяцію, настройку і тестовий контроль, завдяки чому покращились такі характеристики як живучість, надійність, пошук та ремонт пошкодження. Джерела інформації: 1. Універсальна навчальна мікроконтролера система, G06F13/00, патент України №13540. Промислова власність, Офіційний бюлетень №4, 2006р. 2. Мережевий програмований контролер, G05В19/18, G05В19/04, G05В19/05, патент України №79363. Промислова власність, Офіційний бюлетень №8, 2007р. 3. Програмований логічний контролер, G05В19/05, G06F9/00 патент України №781200. Промислова власність, Офіційний бюлетень №5, 2006р. (прототип). 9 47570 10 11 47570 12 В описі до патенту на винахід графічні зображення та текст подаються в редакції заявника Комп’ютерна верстка В. Мацело Підписне Тираж 26 прим. Міністерство освіти і науки України Державний департамент інтелектуальної власності, вул. Урицького, 45, м. Київ, МСП, 03680, Україна ДП “Український інститут промислової власності”, вул. Глазунова, 1, м. Київ – 42, 01601

ДивитисяДодаткова інформація

Назва патенту англійськоюParallel data processing-microprocessor controller

Автори англійськоюScherbakova Ilona Oleksandrivna, Stasiuk Oleksandr Ionovych, Opanasenko Volodymyr Mykolaiovych, Honcharova Lidia Leonidivna, Voznenko Anatolii Dmytrovych, Zhelezniak Anatolii Leonidovych, Podlesnykh Yevhenii Hennadiiovych

Назва патенту російськоюМикропроцессорный контроллер с параллельной обработкой информации

Автори російськоюЩербакова Илона Александровна, Стасюк Александр Ионович, Опанасенко Владимир Николаевич, Возненко Анатолий Дмитриевич, Гончарова Лидия Леонидовна, Железняк Анатолий Леонидович, Подлесных Евгений Геннадиевич

МПК / Мітки

МПК: G06F 9/00

Мітки: інформації, паралельною, мікропроцесорний, обробкою, контролер

Код посилання

<a href="https://ua.patents.su/6-47570-mikroprocesornijj-kontroler-z-paralelnoyu-obrobkoyu-informaci.html" target="_blank" rel="follow" title="База патентів України">Мікропроцесорний контролер з паралельною обробкою інформації</a>

Попередній патент: Двосекційний лабораторний електрофільтр

Наступний патент: Роторний змішувач з гнучким тросовим ротором

Випадковий патент: Сорбційно-фільтрувальна суміш