Вхідний пристрій схеми порівняння струмів

Номер патенту: 53517

Опубліковано: 11.10.2010

Автори: Азаров Олексій Дмитрович, Богомолов Сергій Віталійович, Крупельницький Леонід Віталійович

Формула / Реферат

Вхідний пристрій схеми порівняння струмів, який містить перше та друге джерела струму, резистор зворотного зв'язку, тридцять чотири транзистори, шини додатного і від'ємного живлення, шину нульового потенціалу, вхідну і вихідну шини, причому вхідну шину з'єднано з базами тридцять першого і тридцять другого транзисторів, а також з першим виводом резистора зворотного зв'язку, колектори тридцять першого і тридцять другого транзисторів об'єднано та з'єднано з шиною нульового потенціалу, емітери тридцять першого і тридцять другого транзисторів з'єднано з емітерами першого і другого транзисторів відповідно, бази першого і другого транзисторів з'єднано з базами та колекторами п'ятого і шостого транзисторів відповідно, а також з колекторами сьомого і восьмого транзисторів відповідно, емітери п'ятого і шостого транзисторів з'єднано з емітерами двадцять дев'ятого і тридцятого транзисторів відповідно, бази та колектори двадцять дев'ятого і тридцятого транзисторів об'єднано та з'єднано з шиною нульового потенціалу, бази сьомого і восьмого транзисторів з'єднано з базами та колекторами дев'ятого і десятого транзисторів відповідно, а також з виводами першого джерела струму, емітери сьомого і дев'ятого транзисторів з'єднано з шиною додатного живлення, емітери восьмого і десятого транзисторів з'єднано з шиною від'ємного живлення, колектори першого і другого транзисторів з'єднано з базами п'ятнадцятого і шістнадцятого транзисторів відповідно, а також з колекторами третього і четвертого транзисторів відповідно, емітери третього, тридцять третього і одинадцятого транзисторів з'єднано з шиною додатного живлення, емітери четвертого, тридцять четвертого і чотирнадцятого транзисторів з'єднано з шиною від'ємного живлення, бази третього і четвертого транзисторів з'єднано з базами та колекторами одинадцятого, чотирнадцятого, тридцять третього, тридцять четвертого транзисторів відповідно, а також з колекторами дванадцятого і тринадцятого транзисторів відповідно, а також з виводами другого джерела струму відповідно, бази дванадцятого і тринадцятого транзисторів з'єднано з базами та колекторами двадцять сьомого і двадцять восьмого транзисторів відповідно, а також з колекторами п'ятнадцятого і шістнадцятого транзисторів відповідно, емітери двадцять сьомого і двадцять восьмого транзисторів об'єднано та з'єднано з шиною нульового потенціалу, емітери п'ятнадцятого і шістнадцятого транзисторів з'єднано з базами двадцять третього і двадцять четвертого транзисторів відповідно, а також з колекторами двадцять першого і двадцять другого транзисторів відповідно, бази двадцять першого і двадцять другого транзисторів з'єднано з базами та колекторами двадцять п'ятого і двадцять шостого транзисторів відповідно, а також з емітерами двадцять третього і двадцять четвертого транзисторів відповідно, емітери двадцять першого і двадцять п'ятого транзисторів з'єднано з шиною додатного живлення, емітери двадцять другого і двадцять шостого транзисторів з'єднано з шиною від'ємного живлення, колектори двадцять третього і двадцять четвертого транзисторів з'єднано з базами та колекторами сімнадцятого і вісімнадцятого транзисторів відповідно, а також з базою дев'ятнадцятого транзистора відповідно, емітери сімнадцятого і вісімнадцятого транзисторів об'єднано, який відрізняється тим, що у нього введено тридцять п'ятий, тридцять шостий, тридцять сьомий, тридцять восьмий транзистори та резистор, причому базу та колектор дев'ятнадцятого транзистора з'єднано з базою та колектором сімнадцятого транзистора та колектором двадцять третього транзистора, емітери дев'ятнадцятого, тридцять п'ятого, тридцять восьмого, тридцять шостого транзисторів з'єднано з базами та колекторами тридцять п'ятого, тридцять сьомого, тридцять шостого, двадцятого транзисторів відповідно, емітер двадцятого транзистора з'єднано з базою та колектором вісімнадцятого транзистора та з колектором двадцять четвертого транзистора, емітер тридцять сьомого транзистора з'єднано з базою та колектором тридцять восьмого транзистора, а також з другим виводом резистора зворотного зв'язку та з першим виводом резистора, другий вивід резистора з'єднано з емітерами сімнадцятого і вісімнадцятого транзисторів відповідно, а також з вихідною шиною.

Текст

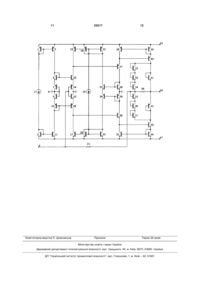

Вхідний пристрій схеми порівняння струмів, який містить перше та друге джерела струму, резистор зворотного зв'язку, тридцять чотири транзистори, шини додатного і від'ємного живлення, шину нульового потенціалу, вхідну і вихідну шини, причому вхідну шину з'єднано з базами тридцять першого і тридцять другого транзисторів, а також з першим виводом резистора зворотного зв'язку, колектори тридцять першого і тридцять другого транзисторів об'єднано та з'єднано з шиною нульового потенціалу, емітери тридцять першого і тридцять другого транзисторів з'єднано з емітерами першого і другого транзисторів відповідно, бази першого і другого транзисторів з'єднано з базами та колекторами п'ятого і шостого транзисторів відповідно, а також з колекторами сьомого і восьмого транзисторів відповідно, емітери п'ятого і шостого транзисторів з'єднано з емітерами двадцять дев'ятого і тридцятого транзисторів відповідно, бази та колектори двадцять дев'ятого і тридцятого транзисторів об'єднано та з'єднано з шиною нульового потенціалу, бази сьомого і восьмого транзисторів з'єднано з базами та колекторами дев'ятого і десятого транзисторів відповідно, а також з виводами першого джерела струму, емітери сьомого і дев'ятого транзисторів з'єднано з шиною додатного живлення, емітери восьмого і десятого транзисторів з'єднано з шиною від'ємного живлення, колектори першого і другого транзисторів з'єднано з базами п'ятнадцятого і шістнадцятого транзисторів відповідно, а також з колекторами третього і четвертого транзисторів відповідно, емітери третього, тридцять третього і одинадцятого транзисторів з'єднано з шиною додатного живлення, емітери четвертого, тридцять четвертого і чотирнадцятого транзисторів з'єднано з шиною від'ємного живлення, бази третього і четвертого транзисторів з'єднано з базами та колекторами одинадцятого, чотир 2 (19) 1 3 53517 4 ного зв'язку та з першим виводом резистора, другий вивід резистора з'єднано з емітерами сімнад цятого і вісімнадцятого транзисторів відповідно, а також з вихідною шиною. Корисна модель відноситься до імпульсної техніки і може бути використана в аналоговоцифрових перетворювачах і цифрових вимірювальних приладах. Відомо двотактний симетричний підсилювач струму [Патент України №18599, Н03К5/00, G05B1/00, бюл. №11, 2006р.], який містить коригуючий конденсатор, резистор зворотного зв'язку, джерело струму, шини додатного і від'ємного живлення, шину нульового потенціалу, вхідну і вихідну шини, двадцять вісім транзисторів, причому вхідну шину з'єднано з емітерами першого та другого транзисторів та першими виводами резистора зворотного зв'язку і коригуючого конденсатора, базу першого транзистора з'єднано з базою та колектором п'ятого транзистора, а також з колектором сьомого транзистора, який в свою чергу підключений базою до бази та колектора дев'ятого транзистора, сьомий та дев'ятий транзистори підключені емітерами до шини додатного живлення, колектор та база десятого та база восьмого транзисторів об'єднані, емітери десятого та восьмого транзисторів з'єднані з шиною від'ємного живлення, колектор восьмого транзистора з'єднано з колектором і базою шостого транзистора та базою другого транзистора, емітери п'ятого та шостого транзисторів підключені до шини нульового потенціалу, колектор першого транзистора з'єднано з базою п'ятнадцятого транзистора, а також з колектором третього транзистора, колектор другого транзистора з'єднано з базою шістнадцятого та колектором четвертого транзисторів, базу третього транзистора з'єднано з колектором і базою одинадцятого транзистора, а також з колектором дванадцятого транзистора, базу четвертого транзистора з'єднано з колектором та базою чотирнадцятого транзистора, а також з колектором тринадцятого транзистора, емітери дванадцятого та тринадцятого транзисторів об'єднано, емітери сімнадцятого та вісімнадцятого транзисторів об'єднано, емітери дев'ятнадцятого та двадцятого транзисторів об'єднано та з'єднано з вихідною шиною, а також з другими виводами резистора зворотного зв'язку і коригуючого конденсатора, емітери четвертого, чотирнадцятого та колектор двадцятого транзисторів з'єднано з шиною від'ємного живлення, емітери третього, одинадцятого та колектор дев'ятнадцятого транзисторів з'єднано з шиною додатного живлення, колектор двадцять першого транзистора з'єднано з базою двадцять третього транзистора, базу двадцять першого транзистора з'єднано з базою та колектором двадцять п'ятого транзистора та емітером двадцять третього транзистора, колектор двадцять третього транзистора з'єднано з базою та колектором сімнадцятого транзистора, а також з базою дев'ятна дцятого транзистора, колектор двадцять другого транзистора з'єднано з базою двадцять четвертого транзистора, базу двадцять другого транзистора з'єднано з базою та колектором двадцять шостого транзистора та емітером двадцять четвертого транзистора, колектор двадцять четвертого транзистора з'єднано з базою та колектором вісімнадцятого транзистора, а також з базою двадцятого транзистора, базу та колектор двадцять сьомого транзистора з'єднано з колектором п'ятнадцятого транзистора, а також з базою дванадцятого транзистора, базу та колектор двадцять восьмого транзистора з'єднано з колектором шістнадцятого транзистора, а також з базою тринадцятого транзистора, емітери двадцять сьомого та двадцять восьмого транзисторів об'єднано та з'єднано з шиною нульового потенціалу, джерело струму першим виводом з'єднано з базою та колектором дев'ятого транзистора, а також з базою сьомого транзистора, другий вивід джерела струму з'єднано з базою та колектором десятого транзистора, а також з базою восьмого транзистора. Основним недоліком є низька точність, що звужує галузь застосування пристрою. За прототип обрано двотактний симетричний підсилювач струму [Патент України №26493, Н03К5/22, G05B1/00, бюл. №15, 2007 р.], який містить перше ти друге джерела струму, резистор зворотного зв'язку, коригуючий конденсатор, тридцять чотири транзистори, шини додатного і від'ємного живлення, шину нульового потенціалу, вхідну і вихідну шини, причому вхідну шину з'єднано з базами тридцять першого і тридцять другого транзисторів, а також з першими виводами резистора зворотного зв'язку та коригуючого конденсатора, колектори тридцять першого і тридцять другого транзисторів об'єднано та з'єднано з шиною нульового потенціалу, емітери тридцять першого і тридцять другого транзисторів з'єднано з емітерами першого і другого транзисторів відповідно, бази першого і другого транзисторів з'єднано з базами та колекторами п'ятого і шостого транзисторів відповідно, а також з колекторами сьомого і восьмого транзисторів відповідно, емітери п'ятого і шостого транзисторів з'єднано з емітерами двадцять дев'ятого і тридцятого транзисторів відповідно, бази та колектори двадцять дев'ятого і тридцятого транзисторів об'єднано та з'єднано з шиною нульового потенціалу, бази сьомого і восьмого транзисторів з'єднано з базами та колекторами дев'ятого і десятого транзисторів відповідно, а також з виводами першого джерела струму, емітери сьомого і дев'ятого транзисторів з'єднано з шиною додатного живлення, емітери восьмого і десятого транзисторів з'єднано з шиною від'ємного живлення, колектори першого і другого транзисторів з'єднано з 5 базами п'ятнадцятого і шістнадцятого транзисторів відповідно, а також з колекторами третього і четвертого транзисторів відповідно, емітери третього, тридцять третього і одинадцятого транзисторів з'єднано з шиною додатного живлення, емітери четвертого, тридцять четвертого і чотирнадцятого транзисторів з'єднано з шиною від'ємного живлення, бази третього і четвертого транзисторів з'єднано з базами та колекторами одинадцятого, чотирнадцятого, тридцять третього, тридцять четвертого транзисторів відповідно, а також з колекторами дванадцятого і тринадцятого транзисторів відповідно, а також з виводами другого джерела струму відповідно, бази дванадцятого і тринадцятого транзисторів з'єднано з базами та колекторами двадцять сьомого і двадцять восьмого транзисторів відповідно, а також з колекторами п'ятнадцятого і шістнадцятого транзисторів відповідно, емітери двадцять сьомого і двадцять восьмого транзисторів об'єднано та з'єднано з шиною нульового потенціалу, емітери п'ятнадцятого і шістнадцятого транзисторів з'єднано з базами двадцять третього і двадцять четвертого транзисторів відповідно, а також з колекторами двадцять першого і двадцять другого транзисторів відповідно, бази двадцять першого і двадцять другого транзисторів з'єднано з базами та колекторами двадцять п'ятого і двадцять шостого транзисторів відповідно, а також з емітерами двадцять третього і двадцять четвертого транзисторів відповідно, емітери двадцять першого і двадцять п'ятого транзисторів з'єднано з шиною додатного живлення, емітери двадцять другого і двадцять шостого транзисторів з'єднано з шиною від'ємного живлення, колектори двадцять третього і двадцять четвертого транзисторів з'єднано з базами та колекторами сімнадцятого і вісімнадцятого транзисторів відповідно, а також з базами дев'ятнадцятого і двадцятого транзисторів відповідно, емітери сімнадцятого і вісімнадцятого транзисторів об'єднано та з'єднано з другим виводом коригуючого конденсатора, колектори дев'ятнадцятого і двадцятого транзисторів з'єднано з шинами додатного і від'ємного живлення, емітери дев'ятнадцятого і двадцятого транзисторів об'єднано та з'єднано з другим виводом резистора зворотного зв'язку, а також з вихідною шиною. Недоліком є низька точність, що звужує галузь застосування пристрою. В основу корисної моделі поставлено задачу створення вхідного пристрою схеми порівняння струмів, в якому за рахунок введення нових елементів та зв'язків між ними підвищується точність роботи схеми, це розширює галузь використання корисної моделі у різноманітних пристроях імпульсної та обчислювальної техніки, автоматики тощо. Поставлена задача досягається тим, що у вхідний пристрій схеми порівняння струмів, який містить перше ти друге джерела струму, резистор зворотного зв'язку, тридцять чотири транзистори, шини додатного і від'ємного живлення, шину нульового потенціалу, вхідну і вихідну шини, причому вхідну шину з'єднано з базами тридцять першого і тридцять другого транзисторів, а також з першим виводом резистора зворотного зв'язку, 53517 6 колектори тридцять першого і тридцять другого транзисторів об'єднано та з'єднано з шиною нульового потенціалу, емітери тридцять першого і тридцять другого транзисторів з'єднано з емітерами першого і другого транзисторів відповідно, бази першого і другого транзисторів з'єднано з базами та колекторами п'ятого і шостого транзисторів відповідно, а також з колекторами сьомого і восьмого транзисторів відповідно, емітери п'ятого і шостого транзисторів з'єднано з емітерами двадцять дев'ятого і тридцятого транзисторів відповідно, бази та колектори двадцять дев'ятого і тридцятого транзисторів об'єднано та з'єднано з шиною нульового потенціалу, бази сьомого і восьмого транзисторів з'єднано з базами та колекторами дев'ятого і десятого транзисторів відповідно, а також з виводами першого джерела струму, емітери сьомого і дев'ятого транзисторів з'єднано з шиною додатного живлення, емітери восьмого і десятого транзисторів з'єднано з шиною від'ємного живлення, колектори першого і другого транзисторів з'єднано з базами п'ятнадцятого і шістнадцятого транзисторів відповідно, а також з колекторами третього і четвертого транзисторів відповідно, емітери третього, тридцять третього і одинадцятого транзисторів з'єднано з шиною додатного живлення, емітери четвертого, тридцять четвертого і чотирнадцятого транзисторів з'єднано з шиною від'ємного живлення, бази третього і четвертого транзисторів з'єднано з базами та колекторами одинадцятого, чотирнадцятого, тридцять третього, тридцять четвертого транзисторів відповідно, а також з колекторами дванадцятого і тринадцятого транзисторів відповідно, а також з виводами другого джерела струму відповідно, бази дванадцятого і тринадцятого транзисторів з'єднано з базами та колекторами двадцять сьомого і двадцять восьмого транзисторів відповідно, а також з колекторами п'ятнадцятого і шістнадцятого транзисторів відповідно, емітери двадцять сьомого і двадцять восьмого транзисторів об'єднано та з'єднано з шиною нульового потенціалу, емітери п'ятнадцятого і шістнадцятого транзисторів з'єднано з базами двадцять третього і двадцять четвертого транзисторів відповідно, а також з колекторами двадцять першого і двадцять другого транзисторів відповідно, бази двадцять першого і двадцять другого транзисторів з'єднано з базами та колекторами двадцять п'ятого і двадцять шостого транзисторів відповідно, а також з емітерами двадцять третього і двадцять четвертого транзисторів відповідно, емітери двадцять першого і двадцять п'ятого транзисторів з'єднано з шиною додатного живлення, емітери двадцять другого і двадцять шостого транзисторів з'єднано з шиною від'ємного живлення, колектори двадцять третього і двадцять четвертого транзисторів з'єднано з базами та колекторами сімнадцятого і вісімнадцятого транзисторів відповідно, а також з базою дев'ятнадцятого транзистора відповідно, емітери сімнадцятого і вісімнадцятого транзисторів об'єднано, введено тридцять п'ятий, тридцять шостий, тридцять сьомий, тридцять восьмий транзистори та резистор, причому базу та колектор дев'ятнадцятого транзистора з'єднано з базою та колектором сімнадцятого тра 7 нзистора та колектором двадцять третього транзистора, емітери дев'ятнадцятого, тридцять п'ятого, тридцять восьмого, тридцять шостого транзисторів з'єднано з базами та колекторами тридцять п'ятого, тридцять сьомого, тридцять шостого, двадцятого транзисторів відповідно, емітер двадцятого транзистора з'єднано з базою та колектором вісімнадцятого транзистора та з колектором двадцять четвертого транзистора, емітер тридцять сьомого транзистора з'єднано з базою та колектором тридцять восьмого транзистора, а також з другим виводом резистора зворотного зв'язку та з першим виводом резистора, другий вивід резистора з'єднано з емітерами сімнадцятого і вісімнадцятого транзисторів відповідно, а також з вихідною шиною. На кресленні представлено принципову схему двотактного симетричного підсилювача струму. Пристрій містить вхідну шину 4, яку з'єднано з базами тридцять першого 14 і тридцять другого 15 транзисторів, а також з першим виводом резистора зворотного зв'язку 21, колектори тридцять першого 14 і тридцять другого 15 транзисторів об'єднано та з'єднано з шиною нульового потенціалу 8, емітери тридцять першого 14 і тридцять другого 15 транзисторів з'єднано з емітерами першого 13 і другого 16 транзисторів відповідно, бази першого 13 і другого 16 транзисторів з'єднано з базами та колекторами п'ятого 6 і шостого 10 транзисторів відповідно, а також з колекторами сьомого 5 і восьмого 11 транзисторів відповідно, емітери п'ятого 6 і шостого 10 транзисторів з'єднано з емітерами двадцять дев'ятого 7 і тридцятого 9 транзисторів відповідно, бази та колектори двадцять дев'ятого 7 і тридцятого 9 транзисторів об'єднано та з'єднано з шиною нульового потенціалу 8, бази сьомого 5 і восьмого 11 транзисторів з'єднано з базами та колекторами дев'ятого 1 і десятого 3 транзисторів відповідно, а також з виводами першого джерела струму 2, емітери сьомого 5 і дев'ятого 1 транзисторів з'єднано з шиною додатного живлення 45, емітери восьмого 11 і десятого 3 транзисторів з'єднано з шиною від'ємного живлення 47, колектори першого 13 і другого 16 транзисторів з'єднано з базами п'ятнадцятого 27 і шістнадцятого 30 транзисторів відповідно, а також з колекторами третього 12 і четвертого 17 транзисторів відповідно, емітери третього 12, тридцять третього 18 і одинадцятого 22 транзисторів з'єднано з шиною додатного живлення 45, емітери четвертого 17, тридцять четвертого 20 і чотирнадцятого 25 транзисторів з'єднано з шиною від'ємного живлення 47, бази третього 12 і четвертого 17 транзисторів з'єднано з базами та колекторами одинадцятого 22, чотирнадцятого 25, тридцять третього 18, тридцять четвертого 20 транзисторів відповідно, а також з колекторами дванадцятого 23 і тринадцятого 24 транзисторів відповідно, а також з виводами другого джерела струму 19 відповідно, бази дванадцятого 23 і тринадцятого 24 транзисторів з'єднано з базами та колекторами двадцять сьомого 28 і двадцять восьмого 29 транзисторів відповідно, а також з колекторами п'ятнадцятого 27 і шістнадцятого 30 транзисторів відповідно, емітери двадцять сьомого 28 і двадцять восьмого 29 тран 53517 8 зисторів об'єднано та з'єднано з шиною нульового потенціалу 8, емітери п'ятнадцятого 27 і шістнадцятого 30 транзисторів з'єднано з базами двадцять третього 40 і двадцять четвертого 43 транзисторів відповідно, а також з колекторами двадцять першого 26 і двадцять другого 31 транзисторів відповідно, бази двадцять першого 26 і двадцять другого 31 транзисторів з'єднано з базами та колекторами двадцять п'ятого 39 і двадцять шостого 44 транзисторів відповідно, а також з емітерами двадцять третього 40 і двадцять четвертого 43 транзисторів відповідно, емітери двадцять першого 26 і двадцять п'ятого 39 транзисторів з'єднано з шиною додатного живлення 45, емітери двадцять другого 31 і двадцять шостого 44 транзисторів з'єднано з шиною від'ємного живлення 47, колектори двадцять третього 40 і двадцять четвертого 43 транзисторів з'єднано з базами та колекторами сімнадцятого 41 і вісімнадцятого 42 транзисторів відповідно, а також з базою та колектором дев'ятнадцятого 32 та емітером двадцятого 37 транзисторів відповідно, емітери сімнадцятого 41 і вісімнадцятого 42 транзисторів об'єднано, емітери дев'ятнадцятого 32, тридцять п'ятого 33, тридцять восьмого 35, тридцять шостого 36 транзисторів з'єднано з базами та колекторами тридцять п'ятого 33, тридцять сьомого 34, тридцять шостого 36, двадцятого 37 транзисторів відповідно, емітер тридцять сьомого 34 транзистора з'єднано з базою та колектором тридцять восьмого 35 транзистора, а також з другим виводом резистора зворотного зв'язку 21 та з першим виводом резистора 38, другий вивід резистора 38 з'єднано з емітерами сімнадцятого 41 і вісімнадцятого 42 транзисторів відповідно, а також з вихідною шиною 46. Пристрій працює таким чином. Вхідний сигнал у вигляді струму поступає на вхідну шину 4. Якщо вхідний струм втікає у схему, то тридцять другий 15 транзистор привідкривається, а тридцять перший 14 транзистор призакривається, відповідно другий 16 транзистор привідкривається, а перший 13 транзистор призакривається. При цьому базовий струм шістнадцятого 30 транзистора збільшується, що призводить до його привідкривання, а базовий струм п'ятнадцятого 27 транзистора зменшується, що призводить до його призакривання. При цьому потенціал точки об'єднання емітерів сімнадцятого 41 і вісімнадцятого 42 транзисторів зменшується і прямує до -Eж. Якщо вхідний струм витікає із схеми, то тридцять другий 15 транзистор призакривається, а тридцять перший 14 транзистор привідкривається, відповідно другий 16 транзистор призакривається, а перший 13 транзистор привідкривається. При цьому базовий струм шістнадцятого 30 транзистора зменшується, що призводить до його призакривання, а базовий струм п'ятнадцятого 27 транзистора збільшується, що призводить до його привідкривання. При цьому потенціал точки об'єднання емітерів сімнадцятого 41 і вісімнадцятого 42 транзисторів збільшується і прямує до Eж. Перше 2 і друге 19 джерела струму та перший 13, другий 16, п'ятий 6, шостий 10, сьомий 5, восьмий 11, дев'ятий 1, десятий 3, двадцять дев'ятий 9 7, тридцятий 9 транзистори утворюють схему завдання режиму по постійному струму. Тридцять перший 14 і тридцять другий 15 транзистори утворюють двотактний підсилювальний вхідний каскад. Дванадцятий 23, тринадцятий 24, двадцяти сьомий 28, двадцяти восьмий 29 транзистори утворюють двонаправлений відбивач струму, який через відбивачі струму, які побудовано на третьому 12, четвертому 17, одинадцятому 22, чотирнадцятому 25, тридцять третьому 18, тридцять четвертому 20 транзисторах відповідно, задає базові струми проміжних підсилювальних каскадів, які побудовано на п'ятнадцятому 27 і шістнадцятому 30 транзисторах відповідно. Двадцять перший 26, двадцять другий 31, двадцять третій 40, двадцять четвертий 43, двадцять п'ятий 39, двадцять шостий 44 транзистори утворюють відбивачі Уїлсона, які забезпечують передачу підсиленого сигналу, через сімнадцятий 41 і вісімнадцятий 42 транзистори у діодному вмиканні на вихід пристрою. Ланцюг транзисторів з дев'ятнадцятого 32, двадцятого 37 та з тридцять п'ятого по тридцять восьмий 33-36 транзисторів у діодному вмиканні та резистор 38 утворюють коло нелінійного від'ємного зворотного зв'язку, мета уведення якого обмежити амплітуду змінення напруги на виході схеми, що призводить до підвищення точності роботи схеми. При цьому якщо струм що втікає у схему збільшується, то потенціал вихідної шини 46 зменшується, то транзистори тридцять восьмий 35, тридцять шостий 36 і двадцятий 37 привідкриваються, а транзистори дев'ятнадцятий 32, тридцять п'ятий 33, тридцять сьомий 34 призакриваються. При цьому через тридцять восьмий 35, тридцять шостий 36 і двадцятий 37 транзистори в коло колектора двадцять четвертого транзистора втікає струм, який компенсує вхідний струм схеми. По мірі збільшення вхідного струму тридцять восьмий 35, тридцять шостий 36 і двадцятий 37 при 53517 10 відкриваються сильніше, опори переходів колектор-емітер зменшуються, а глибина зворотного зв'язку збільшаться. Якщо струм що втікає у схему зменшується, то потенціал вихідної шини 46 збільшується, то транзистори тридцять восьмий 35, тридцять шостий 36 і двадцятий 37 призакриваються, а транзистори дев'ятнадцятий 32, тридцять п'ятий 33, тридцять сьомий 34 привідкриваються. При цьому через дев'ятнадцятий 32, тридцять п'ятий 33, тридцять сьомий 34 в коло колектора двадцять третього 40 транзистора витікає струм, який компенсує вхідний струм схеми. По мірі зменшення вхідного струму дев'ятнадцятий 32, тридцять п'ятий 33, тридцять сьомий 34 привідкриваються сильніше, опори переходів колектор-емітер зменшуються, а глибина зворотного зв'язку збільшаться. Оскільки ланцюг транзисторів з дев'ятнадцятого 32, двадцятого 37 та з тридцять п'ятого по тридцять восьмий 33-36 транзисторів у діодному вмиканні підключені паралельно колу сімнадцятого 41 і вісімнадцятого 42 транзисторів, то в стані спокою, тобто коли Івх = 0 ланцюг транзисторів з дев'ятнадцятого 32, двадцятого 37 та з тридцять п'ятого по тридцять восьмий 33-36 транзисторів знаходяться на порозі відпирання. Якщо вхідний струм приймає максимальне значення, то залежно від напрямку вхідного струму або група з дев'ятнадцятого 32, тридцятьп'ятого 33, тридцять сьомого 34 транзисторів відпирається, а група з тридцять восьмого 35, тридцять шостого 36 і двадцятого 37 транзисторів закривається, або група з тридцять восьмого 35, тридцять шостого 36 і двадцятого 37 транзисторів відкривається, а група з дев'ятнадцятого 32, тридцять п'ятого 33, тридцять сьомого 34 транзисторів закривається. Резистор зворотного зв'язку 21 задає коефіцієнт підсилення. Шини додатного 45 і від'ємного 47 живлення, а також шина нульового потенціалу 8 забезпечують потрібний рівень напруги для живлення схеми. 11 Комп’ютерна верстка Л. Ціхановська 53517 Підписне 12 Тираж 26 прим. Міністерство освіти і науки України Державний департамент інтелектуальної власності, вул. Урицького, 45, м. Київ, МСП, 03680, Україна ДП “Український інститут промислової власності”, вул. Глазунова, 1, м. Київ – 42, 01601

ДивитисяДодаткова інформація

Назва патенту англійськоюInput device for current comparator circuit

Автори англійськоюAzarov Oleksii Dmytrovych, Bohomolov Serhii Vitaliiovych, Krupelnytskyi Leonid Vitaliiovych

Назва патенту російськоюВходное устройство схемы сравнения токов

Автори російськоюАзаров Алексей Дмитриевич, Богомолов Сергей Витальевич, Крупельницкий Леонид Витальевич

МПК / Мітки

Мітки: вхідний, схемі, пристрій, струмів, порівняння

Код посилання

<a href="https://ua.patents.su/6-53517-vkhidnijj-pristrijj-skhemi-porivnyannya-strumiv.html" target="_blank" rel="follow" title="База патентів України">Вхідний пристрій схеми порівняння струмів</a>

Попередній патент: Пристрій для обробки деталей

Наступний патент: Пристрій для усунення міофункціональних порушень

Випадковий патент: Пристрій для одержання емульсій