Комірка суматора за змінним модулем

Номер патенту: 61647

Опубліковано: 25.07.2011

Автори: Тесленко Олександр Кирилович, Тарасенко Володимир Петрович, Роговенко Андрій Іванович

Формула / Реферат

Комірка суматора за змінним модулем, що містить від першого до третього первинні входи операндів, первинний вихід результату, логічну схему формування сигналу SUB, первинні входи та первинні виходи перенесення в старші розряди, первинні входи та первинні виходи перенесення в молодші розряди, яка відрізняється тим, що містить від першої до шостої схеми формування кодованих сигналів перенесення у старші розряди, селекторну схему активування схем формування кодованих сигналів перенесення, першу та другу логічні схеми формування результату, селекторну схему вибору результату, від першої до четвертої схеми формування кодованих сигналів перенесення у молодші розряди, первинний вхід сигналу SUB, первинний вихід сигналу SUB, при цьому другий та третій входи усіх логічних схем формування кодованих сигналів перенесення у старші розряди під'єднані до першого та другого первинних входів перенесення з молодших розрядів, третій вхід від першої до шостої схем формування кодованих сигналів перенесення у старші розряди під'єднані від першого до шостого виходу селекторної схеми активування схем формування кодованих сигналів перенесення, перші виходи кожної з шести логічних схем формування кодованих сигналів перенесення у старші розряди об'єднані за схемою "монтажне АБО" та під'єднані до першого виходу перенесення у старші розряди, другі виходи кожної з шести логічних схем формування кодованих сигналів перенесення у старші розряди об'єднані за схемою "монтажне АБО" та під'єднані до другого виходу перенесення у старші розряди, три входи селекторної схеми активування схем формування кодованих сигналів перенесення під'єднані до первинних входів операндів комірки, перший та п'ятий виходи цієї схеми під'єднані до третього та четвертого входів першої схеми формування кодованих сигналів перенесення у молодші розряди, другий та шостий виходи цієї схеми під'єднані до третього та четвертого входів другої схеми формування кодованих сигналів перенесення у молодші розряди, третій вихід цієї схеми під'єднано до третього входу третьої схеми формування кодованих сигналів перенесення у молодші розряди, четвертий вихід цієї схеми під'єднано до третього входу четвертої схеми формування кодованих сигналів перенесення у молодші розряди, перші виходи схем формування кодованих сигналів перенесення у молодші розряди об'єднані за схемою "монтажне АБО" та під'єднані до першого первинного виходу перенесення у молодші розряди, а також до першого входу схеми формування сигналу SUB, другі виходи схем формування кодованих сигналів перенесення у молодші розряди об'єднані за схемою "монтажне АБО" та під'єднані до другого первинного виходу перенесення у молодші розряди, а також до другого входу схеми формування сигналу SUB, третій та четвертий входи схеми формування сигналу SUB підключені до першого та другого первинних входів перенесення з молодших розрядів, вихід логічної схеми формування сигналу SUB під'єднано до первинного виходу сигналу SUB, первинний вхід сигналу SUB під'єднано до адресного входу селекторної схеми вибору результату, вихід якої під'єднано до первинного виходу результату, а перший та другий входи - відповідно до виходів першої та другої логічних схем формування результату, перший та другий входи обох логічних схем формування результату під'єднано відповідно до першого та другого первинних входів перенесення з молодших розрядів, третій, четвертий та п'ятий входи першої схеми формування результату з'єднано відповідно з першим, другим та третім первинними входами операндів, третій та четвертий входи другої логічної схеми формування результату - відповідно з першим та другим первинними входами операндів.

Текст

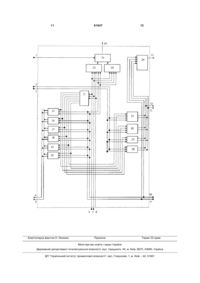

Комірка суматора за змінним модулем, що містить від першого до третього первинні входи операндів, первинний вихід результату, логічну схему формування сигналу SUB, первинні входи та первинні виходи перенесення в старші розряди, первинні входи та первинні виходи перенесення в молодші розряди, яка відрізняється тим, що містить від першої до шостої схеми формування кодованих сигналів перенесення у старші розряди, селекторну схему активування схем формування кодованих сигналів перенесення, першу та другу логічні схеми формування результату, селекторну схему вибору результату, від першої до четвертої схеми формування кодованих сигналів перенесення у молодші розряди, первинний вхід сигналу SUB, первинний вихід сигналу SUB, при цьому другий та третій входи усіх логічних схем формування кодованих сигналів перенесення у старші розряди під'єднані до першого та другого первинних входів перенесення з молодших розрядів, третій вхід від першої до шостої схем формування кодованих сигналів перенесення у старші розряди під'єднані від першого до шостого виходу селекторної схеми активування схем формування кодованих сигналів перенесення, перші виходи кожної з шести логічних схем формування кодованих сигналів перенесення у старші розряди об'єднані за схемою "монтажне АБО" та під'єднані до першого виходу перенесення у старші розряди, другі виходи кожної з шести логічних схем формування кодованих сигналів перенесення у старші розряди об'єднані за схемою "монтажне АБО" та під'єднані до другого виходу перенесення у старші розряди, три входи селекторної схеми активування схем формування кодованих сигналів перенесення пі 2 (19) 1 3 Корисна модель належить до обчислювальної техніки і може бути використана у спеціалізованих обчислювальних пристроях для побудови швидкодіючих суматорів за змінним модулем, системах асиметричних криптографічних перетворень, системах цифрового підпису. Відомий комбінаційний двійковий суматор [1], що діє за принципом групового перенесення та складається з m-груп (m=1…n), при цьому кожна група містить вісім однорозрядних двійкових комбінаційних суматорів, вісім блоків формування розрядних сигналів генерації та транзиту перенесення, блок формування внутрішньогрупових перенесень, а також блок формування міжгрупового перенесення. Недоліком даного суматора є відсутність безпосередньої можливості додавання цілих чисел за модулем, який не є ступенем двійки. Найбільш близьким до запропонованої корисної моделі є суматор за змінним модулем [2], комірка якого містить логічну схему формування позики у старших розрядах, логічну схему формування перенесення при додаванні, логічну схему формування перенесення при відніманні, логічну схему формування вихідного сигналу "на один менше", логічну схему формування сигналу "дорівнює", логічну схему формування сигналу "більше", першу логічну схему додавання за модулем 2, логічну схему формування сигналу SUB, інвертор, першу схему логічного множення, другу схему логічного множення. Задачею даної корисної моделі є удосконалення комірки суматора за змінним модулем шляхом внесення змін до її структури з метою зменшення кількості первинних входів та виходів, та забезпеченням можливості будь-якого допустимого кодування сигналів перенесення, що має спрощувати реалізацію комірки при орієнтації на сучасні засоби технології програмованих логічних схем та прискорювати процес обчислення цільової функції. На кресленні зображено функціональну схему комірки суматора за змінним модулем. Комірка суматора за змінним модулем містить першу логічну схему 15 формування кодованих сигналів перенесення у старші розряди суматора, другу логічну схему 16 формування кодованих сигналів перенесення у старші розряди суматора, третю логічну схему 17 формування кодованих сигналів перенесення у старші розряди суматора, четверту логічну схему 18 формування кодованих сигналів перенесення у старші розряди суматора, п'яту логічну схему 19 формування кодованих сигналів перенесення у старші розряди суматора, шосту логічну схему 20 формування кодованих сигналів перенесення у старші розряди суматора, селекторну схему 21 активування схем формування кодованих сигналів перенесення, першу логічну схему формування результату 22, другу логічну схему формування результату 23, селекторну схему 24 вибору результату, першу логічну схему 25 формування кодованих сигналів перенесення у молодші розряди суматора, другу логічну схему 26 формування кодованих сигналів перенесення у 61647 4 молодші розряди суматора, третю логічну схему 27 формування кодованих сигналів перенесення у молодші розряди суматора, четверту логічну схему 28 формування кодованих сигналів перенесення у молодші розряди суматора, логічну схему 29 формування сигналу SUB для і-1 комірки, де і поточна комірка. Комірка також містить первинні бокові входи перенесення з молодших розрядів 9 та 10, перший та другий первинні бокові входи перенесення зі старших розрядів 2 та 3, перший та другий первинні бокові виходи перенесення до старших розрядів 4 та 5, перший та другий первинні бокові виходи перенесення до молодших розрядів 11 та 12, первинний вхід 1 сигналу SUB, первинний вихід 13 сигналу SUB, первинні входи операндів 6,7, 8, первинний вихід результату 14. При цьому другий та третій входи логічних схем формування кодованих сигналів перенесення у старші розряди 15,16,17,18,19,20 під'єднані до першого та другого первинних входів перенесення з молодших розрядів 10 та 9, третій вхід усіх шести схем під'єднаний кожен до окремого виходу селекторної схеми активування схем формування кодованих сигналів перенесення, перші виходи кожної з шести логічних схем формування кодованих сигналів перенесення у старші розряди об'єднані за схемою "монтажне АБО" та під'єднані до першого первинного виходу перенесення у старші розряди 4. Другі виходи кожної з шести логічних схем формування кодованих сигналів перенесення у старші розряди об'єднані за схемою "монтажне АБО" та під'єднані до другого первинного виходу перенесення у старші розряди 5. Перший, другий та третій входи селекторної схеми 21 активування схем формування кодованих сигналів з'єднані з первинними входами 6,7 та 8, відповідно. Перші виходи логічних схем 25, 26, 27, 28 формування кодованих сигналів перенесення у молодші розряди суматора об'єднані за допомогою схеми "монтажне АБО" та під'єднані до первинного виходу 12 та третього входу логічної схеми 29 формування сигналу SUB. Другі виходи логічних схем 25, 26, 27, 28 формування кодованих сигналів перенесення у молодші розряди суматора об'єднані за допомогою схеми "монтажне АБО" та під'єднані до первинного виходу 11 та четвертого входу логічної схеми 29 формування сигналу SUB. Перший та другий (активуючі) входи логічної схеми 25 формування кодованих сигналів перенесення у молодші розряди суматора з'єднані з першим та п'ятим виходами схеми 21, відповідно, третій вхід з'єднаний з первинним входом 2, четвертий з первинним входом 3. Перший та другий (активуючі) входи логічної схеми 26 формування кодованих сигналів перенесення у молодші розряди суматора з'єднані з другим та шостим виходами схеми 21, відповідно, третій вхід з'єднаний з первинним входом 2, четвертий з первинним входом 3. Перший (активуючий) вхід логічної схеми 27 формування кодованих сигналів у молодші розряди суматора з'єднаний з третім виходом селекторної схеми 21 активування схем формування кодованих сигналів, другий вхід з'єднаний з пер 5 винним входом 2, третій з первинним входом 3. Перший (активуючий) вхід логічної схеми 28 формування кодованих сигналів у молодші розряди суматора з'єднаний з четвертим виходом селекторної схеми 21 активування схем формування кодованих сигналів, другий вхід з'єднаний з первинним входом 2, третій - з первинним входом 3. Перший, другий, третій, четвертий та п'ятий входи першої схеми формування результату 22, підключені до первинних входів 6,7, 8,9 та 10, відповідно. Перший, другий, третій та четвертий входи другої схеми формування результату 23 підключені до первинних входів 6, 7, 9 та 10. Вихід першої схеми формування результату 22 підключений до другого входу селекторної схеми вибору результату 24. Вихід другої схеми формування результату 23 підключений до другого входу селекторної схеми вибору результату 24. Перший вхід селекторної схеми 24 з'єднаний з первинним входом 1, вихід з'єднаний з первинним виходом основної функції 14. Перший та другий входи логічної схеми 29 під'єднані до первинних входів 9 та 10, єдиний вихід цієї схеми з'єднаний з первинним виходом 13. Запропонована корисна модель працює наступним чином. На первинні входи комірки 6,7 та 8 надходять відповідно значення розрядів хі, уi,pi з однаковою вагою двійкових чисел X,Y, Р, (і=0,1…n-і, n - розрядність суматора). На вхід 1 надходить сигнал SUB ознаки віднімання при обчисленні значення Z. На виході 14 комірки формується значення zi, розряду з тією самою вагою числа Z, де Z=(X+Y), якщо X+Y

ДивитисяДодаткова інформація

Назва патенту англійськоюVariable modulo adder cell

Автори англійськоюTarasenko Volodymyr Petrovych, Teslenko Oleksandr Kyrylovych, Rohovenko Andrii Ivanovych

Назва патенту російськоюЯчейка сумматора по переменному модулю

Автори російськоюТарасенко Владимир Петрович, Тесленко Александр Кирилович, Роговенко Андрей Иванович

МПК / Мітки

МПК: G06F 7/00

Мітки: змінним, модулем, комірка, суматора

Код посилання

<a href="https://ua.patents.su/6-61647-komirka-sumatora-za-zminnim-modulem.html" target="_blank" rel="follow" title="База патентів України">Комірка суматора за змінним модулем</a>

Попередній патент: Спосіб неінвазивних досліджень функціонального стану організму “оксітерм”

Випадковий патент: Спосіб визначення присутності напруги постійного струму