Пристрій для формування адрес процесора швидкого перетворення фур’е

Номер патенту: 82804

Опубліковано: 12.08.2013

Автори: Івашко Андрій Володимирович, Лунін Денис Олександрович

Формула / Реферат

Пристрій для формування адрес процесора швидкого перетворення Фур’є (ШПФ), що містить синхронізатор, реверсивний лічильник, лічильник шару і групу мультиплексорів, при цьому виходи синхронізатора з'єднані з тактовими входами реверсивного лічильника, виходи якого з'єднані з сигнальними входами групи мультиплексорів, у свою чергу старший розряд виходу реверсивного лічильника з'єднаний з тактовим входом лічильника шару, виходи якого з'єднані з входами, що управляють, групи мультиплексорів, який відрізняється тим, що виходи реверсивного лічильника підключені до сигнальних входів мультиплексорів в наступному порядку: нульовий розряд виходу реверсивного лічильника паралельно підключений до (N-1 - і) сигнального входу і-мультиплексора, де і міняється від 0 до (N - 1) (N - розмірність ШПФ), перший розряд виходу реверсивного лічильника паралельно підключений до нульового сигнального входу нульового мультиплексора, а так само до (N - і) сигнального входу і-мультиплексора, де і міняється від 1 до (N - 1), аналогічно з циклічним зсувом на 1 підключаються наступні (N - 3) розряду виходу реверсивного лічильника, (N - 1) розряд виходу реверсивного лічильника паралельно підключений до (N - 2 - і) сигнального входу і-мультиплексора, де і міняється від 0 до (N - 2), а так само до (N - 1) сигнального входу (N - 1)-мультиплексора і до входу (+1) лічильника шару, а синхронізатор містить дворозрядний лічильник, елемент 3-І і елемент 2-І, на вхід дворозрядного лічильника подаються тактові імпульси, інверсний нульовий розряд і прямий перший розряд виходу дворозрядного лічильника підключені до елемента 3-І, прямий вихід елемента 3-І є виходом синхронізатора (-1), інверсний вихід елемента 3-І сполучений з першим входом елемента 2-І, а на другий вхід елемента 2-І підключений вхід, на який подаються тактові імпульси, вихід елемента 2-І є виходом синхронізатора (+1), а виходи синхронізатора підключаються до входів реверсивного лічильника.

Текст

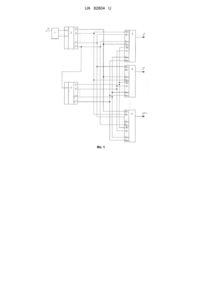

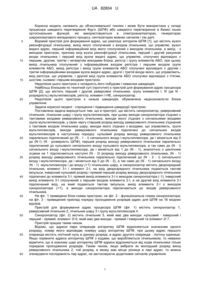

Реферат: UA 82804 U UA 82804 U 5 10 15 20 25 30 35 40 45 50 55 60 Корисна модель належить до обчислювальної техніки і може бути використана у складі процесора швидкого перетворення Фур’є (ШПФ) або швидкого перетворення в базисі інших ортогональних функцій, які використовуються в спектроаналізаторах, генераторах широкосмугового випадкового процесу, синтезаторах мовних сигналів і так далі. Відомий пристрій для формування адрес, що реалізує алгоритм ШПФ [1], що містить вузол реконфігурації лічильника, вихід якого сполучений з входом лічильника, що управляє, вузол видачі адрес, перший інформаційний вхід якого сполучений з виходом лічильника, а вихід - з виходом пристрою, причому вхід вузла реконфігурації лічильника, перший і другий рахункові входи лічильника і перший вхід вузла видачі адрес, що управляє, сполучені відповідно з першим, другим, третім і четвертим виходами блока, регістр і групу елементів АБО, при цьому вихід лічильника сполучений з інформаційним входом регістра і першим входом групи елементів АБО, вихід регістра і вихід групи елементів АБО сполучені відповідно з другим і третім інформаційними входами вузла видачі адрес, другої і третій входи якого, що управляють, вхід регістра, що управляє, і другий вхід групи елементів АБО сполучені відповідно з п'ятим, шостим, сьомим і першим входами пристрою. Недоліком цього пристрою є складність його побудови і невисока швидкодія. Найбільш близьким по технічній суті (прототип) є пристрій для формування адрес процесора ШПФ [2], що містить перший і другий реверсивні лічильники, групу елементів І, N (де N розрядність) мультиплексорів, регістр, елемент І-НЕ, синхронізатор. Недоліком цього пристрою є низька швидкодія, обумовлена недосконалістю блока управління. Задача корисної моделі - спрощення і підвищення швидкодії пристрою. Поставлена задача вирішується тим, що в пристрої, що містить синхронізатор, реверсивний лічильник, лічильник шару і групу мультиплексорів, при цьому виходи синхронізатора з'єднані з тактовими входами реверсивного лічильника, виходи якого з'єднані з сигнальними входами групи мультиплексорів, у свою чергу старший розряд виходу реверсивного лічильника з'єднаний з тактовим входом лічильника шару, виходи якого з'єднані з входами, що управляють, групи мультиплексорів, виходи реверсивного лічильника підключені до сигнальних входів мультиплексорів в наступному порядку: нульовий розряд виходу реверсивного лічильника паралельно підключений до (N - 1 - і) сигнального входу і-мультиплексора, де і міняється від 0 до (N-1) (N - розмірність ШПФ), перший розряд виходу реверсивного лічильника паралельно підключений до нульового сигнального входу нульового мультиплексора, а так само до (N - і) сигнального входу і-мультиплексора, де і міняється від 1 до (N - 1), аналогічно з циклічним зсувом на 1 підключаються наступні (N - 3) розряду виходу реверсивного лічильника, (N - 1) розряд виходу реверсивного лічильника паралельно підключений до (N - 2 - і) сигнального входу і-мультиплексора, де і міняється від 0 до (N - 2), а так само до (N - 1) сигнального входу (N - 1) -мультиплексора і до входу (+1) лічильника шару, а синхронізатор містить дворозрядний лічильник, елемент 3-І і елемент 2-І, на вхід дворозрядного лічильника подаються тактові імпульси, інверсний нульовий розряд і прямий перший розряд виходу дворозрядного лічильника підключені до елемента 3-І, прямий вихід елемента 3-І є виходом синхронізатора (-1), інверсний вихід елемента 3-І сполучений з першим входом елемента 2-І, а на другий вхід елемента 2-І підключений вхід, на який подаються тактові імпульси, вихід елемента 2-І є виходом синхронізатора (+1), а виходи синхронізатора підключаються до входів реверсивного лічильника. На фiг. 1 приведена блок-схема пристрою; на фіг. 2 - функціональна схема синхронізатора; на фіг. 3 - приведений приклад порядку проходження розрядів адрес для ШПФ на 16 вхідних відліків. Пристрій для формування адрес процесора ШПФ (фіг. 1) містить синхронізатор 1, реверсивний лічильник 2, лічильник шару 3 і групу мультиплексорів 4. Синхронізатор (фіг. 2) містить лічильник 5, який має два виходи: нульовий - інверсний і перший - прямий, елемент 3І 6; який має два виходи - прямий і інверсний та елемент 2I 7. Пристрій працює таким чином. Відомо, що адреси пари операндів алгоритму ШПФ відрізняються значенням одного розряду, номер якого відповідає номеру шару алгоритму ШПФ, при цьому адрес першого операнда містить логічний нуль в даному розряді, а адрес другого операнда - логічну одиницю. Якщо порівняти адреси алгоритму ШПФ з кодами, що виробляються лічильником, то неважко відмітити, що в кожному шарі алгоритму ШПФ адреси відрізняються від кодів лічильника тільки порядком проходження розрядів. Таким чином, якщо вибрати як молодший розряд вихід реверсивного лічильника 2, той розряд, в якому має місце різниця в парі адрес, то можна згенерувати послідовність пар адрес, не застосовуючи додаткових сигналів управління. 1 UA 82804 U 5 10 15 20 25 30 35 40 45 50 55 Розглянемо приклад комутації вихідних розрядів реверсивного лічильника 2 для 16-ти вхідних відліків (фіг. 3). Для знаходження ШПФ від 16-ти відліків необхідно 4 етапи (шари). У кожному з цих шарів обчислюється 8 елементарних "метеликів". У свою чергу для обчислення кожного елементарного "метелика" необхідно згенерувати дві адреси операнда. Таким чином, при виконанні першого шару перетворення, необхідно комутувати виходи реверсивного лічильника 2 таким чином: нульовий розряд реверсивного лічильника 2 комутується на третій вихід пристрою, перший розряд - на нульовий вихід, другий розряд - на перший вихід і третій розряд на другий вихід. У другому шарі всі розряди зрушуються циклічно по напряму зменшення номера виходу. У наступних шарах процес комутації повторюється відповідно до приведеної таблиці (фіг. 3). Для забезпечення роботи схеми з оперативним запам'ятовувальним пристроєм (ОЗП) слід дублювати пари адрес, що генеруються. Це необхідно для того, щоб на першому етапі генерації пари адрес проводилося прочитування з пам'яті пари операндів, які надходять на арифметичний пристрій. Після обробки в арифметичному пристрої ця пара операндів повинна бути поміщена в ОЗП по тих же адресах, тому необхідно повторно згенерувати пару адрес для запису в ОЗП. Це досягається тим, що тактові імпульси подаються на синхронізатор 1, який формує дві послідовності імпульсів, що подаються на входи реверсивного лічильника 2. На першому етапі від синхронізатора 1 подається пара імпульсів на вхід інкремент (+1) реверсивного лічильника 2, далі необхідно подати один імпульс на вхід декремент (-1) і один на вхід інкремент (+1) реверсивного лічильника 2, що забезпечує послідовне прочитування з ОЗП пари операндів, а далі запис пари операндів в ОЗП. Для подачі на адресні входи групи мультиплексорів 4 значення номера шару служить лічильник шару 3, на тактовий вхід якого подається старший розряд виходу реверсивного лічильника 2. Тактовий вхід лічильника шару 3 спрацьовує по низькому рівню сигналу, що забезпечує перемикання сигнальних входів групи мультиплексорів 4 тільки тоді, коли відбудеться переповнювання реверсивного лічильника 2 і він скинеться в нуль. Таким чином, запропонована корисна модель (пристрій для формування адрес процесора швидкого перетворення Фур’є) дозволяє зменшити кількість устаткування за рахунок спрощення схеми синхронізатора 1 і зміни комутації виходів реверсивного лічильника 2 при збереженні всіх функціональних і технічних можливостей пристрою. Джерела інформації: 1. Авторське свідоцтво СРСР № 548863, кл. G06F15/332, 1976 2. Авторське свідоцтво СРСР № 999062, кл. G06F15/332, 1983 ФОРМУЛА КОРИСНОЇ МОДЕЛІ Пристрій для формування адрес процесора швидкого перетворення Фур’є (ШПФ), що містить синхронізатор, реверсивний лічильник, лічильник шару і групу мультиплексорів, при цьому виходи синхронізатора з'єднані з тактовими входами реверсивного лічильника, виходи якого з'єднані з сигнальними входами групи мультиплексорів, у свою чергу старший розряд виходу реверсивного лічильника з'єднаний з тактовим входом лічильника шару, виходи якого з'єднані з входами, що управляють, групи мультиплексорів, який відрізняється тим, що виходи реверсивного лічильника підключені до сигнальних входів мультиплексорів в наступному порядку: нульовий розряд виходу реверсивного лічильника паралельно підключений до (N-1 - і) сигнального входу і-мультиплексора, де і міняється від 0 до (N - 1) (N - розмірність ШПФ), перший розряд виходу реверсивного лічильника паралельно підключений до нульового сигнального входу нульового мультиплексора, а так само до (N - і) сигнального входу імультиплексора, де і міняється від 1 до (N - 1), аналогічно з циклічним зсувом на 1 підключаються наступні (N - 3) розряду виходу реверсивного лічильника, (N - 1) розряд виходу реверсивного лічильника паралельно підключений до (N - 2 - і) сигнального входу імультиплексора, де і міняється від 0 до (N - 2), а так само до (N - 1) сигнального входу (N - 1)мультиплексора і до входу (+1) лічильника шару, а синхронізатор містить дворозрядний лічильник, елемент 3-І і елемент 2-І, на вхід дворозрядного лічильника подаються тактові імпульси, інверсний нульовий розряд і прямий перший розряд виходу дворозрядного лічильника підключені до елемента 3-І, прямий вихід елемента 3-І є виходом синхронізатора (-1), інверсний вихід елемента 3-І сполучений з першим входом елемента 2-І, а на другий вхід елемента 2-І підключений вхід, на який подаються тактові імпульси, вихід елемента 2-І є виходом синхронізатора (+1), а виходи синхронізатора підключаються до входів реверсивного лічильника. 2 UA 82804 U 3 UA 82804 U Комп’ютерна верстка В. Мацело Державна служба інтелектуальної власності України, вул. Урицького, 45, м. Київ, МСП, 03680, Україна ДП “Український інститут промислової власності”, вул. Глазунова, 1, м. Київ – 42, 01601 4

ДивитисяДодаткова інформація

Назва патенту англійськоюDevice for address generation of fast fourier transform processor

Автори англійськоюIvashko Andrii Volodymyrovych, Lunin Denys Oleksandrovych

Назва патенту російськоюУстройство для формирования адресов процессора быстрого преобразования фурье

Автори російськоюИвашко Андрей Владимирович, Лунин Денис Александрович

МПК / Мітки

МПК: G06F 17/14

Мітки: пристрій, формування, фур'е, процесора, адрес, перетворення, швидкого

Код посилання

<a href="https://ua.patents.su/6-82804-pristrijj-dlya-formuvannya-adres-procesora-shvidkogo-peretvorennya-fure.html" target="_blank" rel="follow" title="База патентів України">Пристрій для формування адрес процесора швидкого перетворення фур’е</a>

Попередній патент: Поїлка-годівниця для бджіл міленіна м.і

Наступний патент: Пристрій для подачі технологічної рідини в зону шліфування

Випадковий патент: Ймовірнісно-детермінований спосіб кодування цифрової інформації жердєва-пампухи