Спосіб відбраковки потенційно ненадійних і нестабільних інтегральних мікросхем

Номер патенту: 1056

Опубліковано: 30.12.1993

Автори: Усатенко Василь Григорович, Сердюк Гай Борисович, Сазонов Сергій Миколайович

Формула / Реферат

1. Способ отбраковки потенциально ненадежных и нестабильных интегральных микросхем, заключающийся в том, что выбирают пары выводов контролируемых интегральных микросхем, между которыми содержатся р-n-переходы, подают на выбранные лары выводов линейно возрастающее ступенчатое напряжение и регистрируют на заданном участке вольт-амперной характеристики величину информативного параметра, по которому проводят отбраковку дефектных микросхем, отличающийся тем, что в качестве выбираемых пар выводов используют пару выводов микросхемы, предназначенную для подключения источников питания, на которую дополнительно подают двухчастотное тестовое напряжение близких частот, причем остальные выводы микросхемы соединяют согласно ее типовой схеме включения при возможной подаче на них только статических сигналов, фиксируют по методу разностной частоты одновременно две зависимости вторых производных вольт-амперной и вольт-купонной характеристик от напряжения в цепи питания, изменяющегося с постоянным шагом от нулевого до номинального значения, которые принимают в качестве совокупности информативных параметров, а отбраковку потенциально ненадежных и нестабильных микросхем производят при сравнении полученных зависимостей с эталонными кривыми вторых производных вольт-амперной и вольт-кулонной характеристик.

2. Способ по п.1, отличающийся тем, что исследуемую микросхему бракуют при выходе ее вторых производных вольт-амперной и/или вольт-купонной характеристик хотя бы при одном значении аргумента за интервалы допуска, определяемые по формуле:

где - интервалы допуска для кривых вторых производных вольт-ампер ной и вольт-купонной характеристик соответственно, определяемые для каждой значения аргумента Ui:

- оценки математических ожиданий и средне-квадратических отклонений значений вторых производных вольт-амперных и вольт-купонных характеристик исправных и удовлетворяющих техническим условиям микросхем, определяемые для каждого значения аргумента Ui; К - количество значений аргумента, для которых измеряют значения вторых производных вольт-амперных и вольт-купонных характеристик, n - коэффициент пропорциональности, выбираемый с учетом допустимой вероятности ложной забраковки и/или допустимой вероятности необнаруженного скрытого дефекта.

Текст

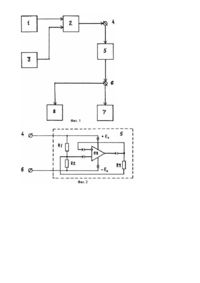

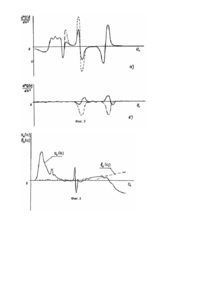

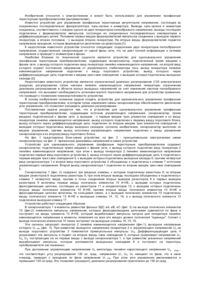

Изобретение относится к области технической диагностики и может быть использовано для отбраковки потенциально ненадежных и нестабильных интегральных микросхем (ИМС) со скрытыми дефектами как в процессе их производства на завершающих те хнологических операциях, так и на входном контроле при их применении в составе радиоэлектронной аппаратуры. Известен способ отбраковки КМОП интегральных схем по уровням надежности [1], который заключается в том. что на интегральную микросхему подают номинальное напряжение питания и входные сигналы и измеряют у все х микросхем, входящих в контролируемую партию, величину активного сопротивления, включенного в цепь питания интегральной схемы, при которой прекращается функционирование (так называемое критическое сопротивление Rкр), Затем определяют значение Rкрm, соответствующее максимуму распределения критических сопротивлений в партии интегральных микросхем, и отбраковывают микросхемы по отличию индивидуального значения Rкр от значения Rкрm на величину, превышающую, среднеквадратическое отклонение. Способ имеет следующие недостатки: - поскольку отбраковка микросхем производится при измерении Rкр вблизи номинального напряжения питания при высоком энергопотреблении схемы, а скрытые дефекты приводят, как правило, к незначительным изменениям энергопотребления и оказывают относительно слабое влияние на прекращение функционирования микросхемы при понижении питания и, следовательно, они не могут быть выявлены, то способ характеризуется низкой чувстви тельностью к скрытым дефектам; - вследствие низкой чувствительности способа к скрытым дефектам и применения для отбраковки только одного информативного параметра, он обладает относительно невысокой достоверностью отбраковки микросхем со скрытыми дефектами; - поскольку способ основан на контроле порога работоспособности микросхемы по напряжению, а к изменениям температуры более чувстви телен ток, то способ не чувстви телен к скрытым дефектам, которые связаны с изменением температуры. Наиболее близким по технической сущности к заявляемому является способ отбраковки интегральных схем [2], заключающийся в том, что на выбранные пары выводов контролируемых микросхем, между которыми содержатся р-n-переходы, подают линейно возрастающее напряжение и регистрируют заданный участок вольтамперной характеристики (ВАХ) с определением информативного параметра. В качестве информативного параметра используют величину тока утечки, по которому проводят отбраковку дефектных микросхем. Способ имеет следующие недостатки; - поскольку методом вольтамперометрии, применяемым в способе, не выявляются малые изменения тока при измерении ВАХ контролируемых цепей, то он обладает низкой чувстви тельностью к скрытым дефектам, слабо влияющим на форму ВАХ; - требование для контроля отдельных выводов микросхемы, к которым подключены только р-n-переходы, приводит к низкой достоверности отбраковки при контроле тех микросхем, в которых значительное число р-nпереходов не соединено непосредственно с внешними выводами и в которых невозможно отключить резисторные делители напряжения для исключения их влияния на информативный параметр. В основу изобретения поставлена задача усовершенствования способа отбраковки потенциально ненадежных и нестабильных интегральных микросхем, благодаря которому путем изменения диагностической информации и математического обеспечения повысилась бы чувствительность к скрытым дефектам исследуемой микросхемы и за счет этого повысилась бы достоверность отбраковки. Поставленная задача решается тем, что в способе, заключающемся в том, что выбирают пары выводов контролируемых микросхем, между которыми содержатся р-n-переходы, подают на выбранные пары выводов линейно возрастающее ступенчатое напряжение и регистрируют на заданном участке ВАХ величину информативного параметра, по которому проводят отбраковку интегральных схем с дефектами, согласно изобретению, в качестве выбираемых пар выводов используют пару выводов микросхемы, предназначенную для подключения источников питания, на которую дополнительно подают двухчастотное тестовое напряжение близких частот, причем остальные выводы микросхемы соединяют согласно ее типовой схеме включения при возможной подаче на них только статических сигналов, фиксируют по методу разностной частоты одновременно две зависимости вторых производных ВАХ и вольт-купонной (ВКХ) характеристик от напряжения в цепи питания, изменяющегося с постоянным шагом от нуля до номинального значения, которые принимают в качестве совокупности информативных параметров, а отбраковку дефектных микросхем производят при сравнении полученных зависимостей с эталонными кривыми вторых производных ВАХ и ВКХ, характерными для микросхем, для которых последующие испытания подтверждают их надежность и стабильность функционирования. Дополнительно в способе осуществляют забраковку исследуемой микросхемы при выходе ее вторых производных ВАХ и/или ВКХ хотя бы при одном значении аргумента за интервалы допуска: где Da2 (Ui ), Db2 (Ui ) - интервалы допуска для кривых вторых производных ВАХ и ВКХ соответственно, ˆ ˆ определяемые для каждого значения аргумента Ui; m[a 2U (Ui )] , s[a 2U (Ui )] , m[b 2U (Ui )] , s[b 2U (Ui )] -оценки ˆ ˆ математических ожиданий и среднеквадратических отклонений значений вторых производных ВАХ a 2U (Ui ) и ВКХ b 2U (Ui ) исправных и удовлетворяющих техническим условиям микросхем. определяемые для каждого значения аргумента Ui; К - количество значений аргумента, для которых измеряют значения вторых производных ВАХ и ВКХ; n - коэффициент пропорциональности, выбираемый с учетом допустимой вероятности ложной забраковки и/или допустимой вероятности необнаруженного скрытого дефекта. На фиг. 1 приведена структурная схема устройства, реализующего заявляемый способ. Способ заключается в следующем. На пару выводов микросхемы, предназначенную для подключения источников питания, при использовании типовой схемы включения для остальных выводов микросхемы подают линейно возрастающее ступенчатое напряжение и двухчасто тное напряжение близких частот. При изменении линейно возрастающего ступенчатого напряжения от нулевого до номинального значений происходит переход отдельных приборных структур микросхем из режима отсечки к активному режиму и, возможно, к режиму насыщения. При этом совокупность приборных стр уктур, осуществляющая такой переход при близких значениях питающего напряжения, будет порождать возникновение изгиба на ВАХ цепи питания. Этому изгибу на зависимости второй производной ВАХ от подаваемого ступенчатого напряжения будут соответство вать один или не сколько одиночных или групповых выбросов. Различные приборные структуры по отношению к величине питающего напряжения будут отличаться индивидуальными значениями напряжений, при которых осуществляются указанные переходы. Вследствие этого зависимость второй производной ВАХ цепи питания от питающего напряжения будет представлять собой зафиксированную с достаточной точностью и разрешающей способностью характеристику постепенного вхождения всей совокупности приборных структур микросхемы в рабочий режим, реализуемый при номинальном напряжении питания. Аналогично зависимость второй производной ВКХ цепи питания микросхемы от подаваемого ступенчатого напряжения характеризует процесс подключений локальных емкостей микросхемы и процессы накопления зарядов как в отдельных приборных структурах микросхемы, так и в ее физических средах, являющихся общими для группы приборных стр уктур. Скрытые дефекты в приборных структура х микросхемы, снижающие ее надежность и стабильность, приводят к изменению свойств отдельных элементов микросхемы, не изменяя в течение некоторого времени вид ее технического состояния. Однако такие дефекты или связанные с ними процессы дефектообразования будут отражаться в изменении параметров и признаков вторых производных ВАХ и ВКХ цепи питания микросхемы. Подача на цепь питания двухчастотного тестового напряжения близких частот достаточно малой амплитуды приводит к тому, что вследствие нелинейности ее ВАХ и ВКХ в токе цепи питания будут кроме постоянной составляющей и гармоник на основных частотах тестового напряжения присутствовать комбинационные гармоники на высших и разностных частотах, параметры которых функционально связаны с параметрами нелинейности ВАХ и ВКХ. По методу разностной частоты фиксируют зависимости комплексных параметров комбинационной гармоники тока на первой разностной частоте от напряжения питания, изменяющегося с постоянным шагом от нуля до номинального значения, и по ним определяют зависимости вторых производных ВАХ и ВКХ от напряжения в цепи питания микросхемы. Полученные характеристики принимают в качестве совокупности информативных параметров, по которым производят отбраковку дефектных микросхем. Отбраковка потенциально ненадежных и нестабильных микросхем осуществляется путем сравнения полученных зависимостей с эталонными кривыми вторых производных ВАХ и ВКХ. Эти кривые могут быть получены при регистрации рассматриваемых характеристик для выборки исправных микросхем и осуществлении выбора в качестве эталонных характеристик тех микросхем, которые при проведении последующи х испытаний на надежность проявили себя как надежные и стабильные. В качестве испытаний на надежность может быть использована, например, электротермотренировка. При сравнении характеристик вторых производных исследуемой микросхемы с эталонными кривыми, микросхема признается потенциально ненадежной и/или нестабильной в том случае, если эти характеристики содержат существенно отличные признаки (параметры), по сравнению с эталонными кривыми. В качестве одного из критериев отбраковки может использоваться факт выхода вторых производных ВАХ и/или ВКХ хотя бы при одном значении аргумента за интервалы допуска, определяемые по характеристикам выборки исправных и удо влетворяющи х те хническим условиям микросхем с помощью выражений (1) и (2). В этом случае получать информацию о надежности и стабильности микросхем обучающей выборки с помощью испытаний на надежность не требуется. Это обусловлено тем, что при этом параметры фиксируемых зависимостей нескольких потенциально ненадежных микросхем, возможно присутствующи х в обучающей выборке, будут иметь характер выбросов случайных процессов, образуемых соответствующими параметрами характеристик надежных и стабильных микросхем в обучающей выборке. Указанные выбросы практически не ˆ ˆ будут оказывать влияние на статистические оценки m[a 2U (Ui )] m[b 2U (Ui )] s[a 2U (Ui )] ˆ s[b 2U (Ui )] и, ˆ , , , следовательно, на интервалы допуска, определяемые с помощью выражений (1) и (2). Таким образом, при построении решающего правила указанным путем проведение испытаний на надежность микросхем обучающей выборки с целью выбора эталонных характеристик не требуется. Устройство, реализующее способ отбраковки потенциально ненадежных и нестабильных интегральных микросхем (фиг. 1), содержит источник 1 линейно возрастающего ступенчатого напряжения, выход которого соединен с первым входом линейного сумматора 2, ко второму входу которого подключен выход источника 3 тест-сигнала, а к выходу, через клемму 4 подключен первый вывод шины питания контролируемой интегральной микросхемы 5, второй вывод шины питания которой через клемму 6 подключен к датчику тока 7 и блоку регистрации 8. Способ осуществляется следующим образом. После подключения испытываемой микросхемы в схему для отбраковки через клеммы 4 и 6 в блоке 1 источника линейно возрастающего ступенчатого напряжения устанавливают предел изменения ступенчатого напряжения, соответствующего номинальному напряжению питания испытываемой микросхемы, а в блоке 3 источника тест-сигнала устанавливают параметры тестового воздействия. Затем, после запуска блоков 1 и 3, происходит суммирование напряжений сумматором 2 и подача суммы напряжений через клемму 4 на испытываемую микросхему 5. Через клемму 6 с датчика тока 7 происходит фиксация по методу разностной частоты зависимостей вторых производных ВАХ и ВКХ от напряжения в цепи питания испытываемой микросхемы в блоке 8 регистрации. В памяти блока 8 регистрации хранятся эталонные кривые вторых производных ВАХ и ВКХ, с которыми сравниваются полученные зависимости. Отбраковывают те микросхемы, кривые вторых производных ВАХ и ВКХ которых выходят за пределы интервала допуска, определяемого согласно формулам (1) и (2), на любом участке изменения линейно возрастающего ступенчатого напряжения. Пример схемы подключения интегральной микросхемы операционного усилителя к реализующему способ устройству приведен на фиг. 2. В приведенной схеме в качестве сопротивлений R1, R2 и R3 используются прецизионные резисторы, номиналы которых выбираются исходя из условий: где RH - допустимое нагрузочное сопротивление; Iвх - входной ток операционного усилителя; Іном , Е ном - номинальный ток и номинальное напряжение питания микросхемы операционного усилителя. Все перечисленные параметры приводятся в паспортных данных на микросхему. На фиг. 3 показан характер зависимостей вторых производных ВАХ (а) и ВКХ (б) для годной микросхемы типа К1417УД6А (сплошная линия) и типичные отклонения от этих зависимостей для изделий со скрытыми дефектами (пунктирная и штрихпунктирная линии). Микропроцессорная БИС серии К1810ВМ86 имеет вывод N40 для подключения источника питания +5В и два вывода N1 и N20 для подключения к шине земли. При этом общие выводы N1 и N20 конструктивно соединены с различными частями БИС и при использовании микропроцессора по назначению соединяются внешней цепью между собой. Однако при использовании заявляє" мого способа для отбраковки потенциально ненадежных и нестабильных БИС вторые производные ВАХ и ВКХ могут раздельно фиксироваться по выводам 1-40 и 20-40. При этом остальные выводы БИС находятся в отключенном состоянии. Примеры типичных характеристик вторых производных ВАХ и ВКХ надежных и стабильных микросхем, зафиксированных по выводам 1-40 и 20-40, приведены на фиг. 4 и фи г. 5 соотве тственно. Примеры аналогичных характеристик для потенциально ненадежных БИС приведены на фиг. 6 и фиг. 7. Эффективность заявляемого способа была оценена с использованием обучающей выборки БИС указанной серии объемом 150 шт. С этой целью были зафиксированы характеристики вторых производных ВАХ и ВКХ эти х БИС по выводам 1-40 и 20-40 и определены интервалы допуска в соответствии с выражениями (1) и (2). После этого в отдельную группу были выделены микросхемы, характеристики которых вы ходят за интервалы допуска. После измерений характеристик вторых производных ВАХ и ВКХ цепей питания БИС вся обучающая выборка подвергалась испытаниям на надежность с использованием электротермот-ренировки (ЭТП в течение 168 часов. При этом 38 из 150 микросхем после проведения ЭТТ были забракованы, что составило около 25% от всего объема выборки. Из 38-ми забракованных БИС 23 микросхемы (то есть 60%) принадлежали к выделенной группе микросхем, забракованных с помощью заявляемого способа. На фиг. 8 приведен пример выхода характеристики второй производной ВАХ цепи питания между выводами 1-40 за интервалы допуска на участке изменения питающего напряжения от 3 до 5 В. Таким образом, предлагаемый способ обладает по сравнению с прототипом большей чувствительностью к скрытым дефектам, поскольку, во-первых, в качестве первичной диагностической информации используют параметры и признаки не только ВАХ, но и ВКХ некоторой совокупности р-n-переходов исследуемой микросхемы. Во-вторых, использование вместо ВАХ ее второй производной повышает чувстви тельность способа к скрытым дефектам, поскольку они приводят к отклонениям ВАХ, которые практически не различимы непосредственно на фиксируемых инструментально ВАХ, и проявляются в достаточно большой степени в параметрах и признаках вторых производных ВАХ. В-третьих, предлагаемый способ позволяет обнаруживать скрытые дефекты в приборных структурах, непосредственно не имеющих специальных выводов, за счет выбора в качестве контролируемых пар выводов микросхемы ее цепи питания, к которой эти приборные структуры обязательно подключены. При этом повышается достоверность отбраковки, поскольку дополнительно выявляются микросхемы, потенциальная ненадежность и нестабильность которых обусловлена скрытыми дефектами, проявляющимися в параметрах и признаках фиксируемых по предлагаемому способу характеристик и не фиксируемых с помощью способа-прототипа. Дополнительно расширяется область применения способа эа счет возможности отбраковки потенциально ненадежных и нестабильных микросхем практически любых типов, изготовленных с использованием различных технологий, поскольку их цепи питания охватывают практически все приборные структуры, а дефекты в приборных структурах будут отражаться в параметрах и признаках фиксируемых в предлагаемом способе за счет регистрации одновременно вторых производных как ВАХ, так и ВКХ. Применение способа в процессе производства интегральных микросхем для отбраковки потенциально ненадежных и нестабильных чипов, находящихся не пластине, позволяет сократить затраты труда, энергии и материалов, необходимые для приварки выводов, корпусирования таких чипов и проведения ускоренных испытаний на надежность, например, с использованием электротермотренировки. Применение способа на входном контроле при применении микросхем в аппаратуре позволяет устранять потенциально ненадежные и нестабильные микросхемы, повышая надежность радиоэлектронной аппаратуры.

ДивитисяДодаткова інформація

Назва патенту англійськоюMethod for screening potentially not reliable and non-stable integral micro-circuits

Автори англійськоюUsatenko Vasyl Hryhorovych, Serdiuk Hai Borysovych, Sazonov Serhii Mykolaiovych

Назва патенту російськоюСпособ отбраковки потенциально ненадежных и нестабильных интегральных микросхем

Автори російськоюУсатенко Василий Григорьевич, Сердюк Гай Борисович, Сазонов Сергей Николаевич

МПК / Мітки

Мітки: спосіб, інтегральних, відбраковки, мікросхем, потенційно, нестабільних, ненадійних

Код посилання

<a href="https://ua.patents.su/7-1056-sposib-vidbrakovki-potencijjno-nenadijjnikh-i-nestabilnikh-integralnikh-mikroskhem.html" target="_blank" rel="follow" title="База патентів України">Спосіб відбраковки потенційно ненадійних і нестабільних інтегральних мікросхем</a>

Попередній патент: Дозатор сипких матеріалів

Наступний патент: Пристрій для здрібнювання матеріалів

Випадковий патент: Спосіб заряджання шпурів та свердловин аміачно-селітровими вибуховими речовинами