Перетворювач двійкового коду в однополярні оборотні коди і навпаки

Номер патенту: 107544

Опубліковано: 12.01.2015

Автори: Лукашенко Валентина Максимівна, Лукашенко Андрій Германович, Лукашенко Володимир Андрійович, Зубко Ігор Анатолійович, Лукашенко Дмитро Андрійович

Формула / Реферат

Перетворювач двійкового коду в однополярні оборотні коди і навпаки містить регістр входу, виконаний на тригерах з інформаційними та лічильними входами, інформаційні входи регістру входу з'єднані з входами перетворювача, а виходи з'єднані з відповідними входами першої комбінаційної схеми адреси, виходи блока вентилів з'єднані з відповідними входами ПЗП, виходи якого з'єднані через блок елементів АБО з відповідними лічильними входами регістру входу, керуючий вхід регістру входу з'єднаний з прямим виходом керуючого тригеру, а інверсний вихід керуючого тригера з'єднаний з керуючим входом ПЗП, перша комбінаційна схема адреси містить дозволяючий вхід, вхід керуючого тригера з'єднаний з першим керуючим входом перетворювача, керуючі входи блока вентилів з'єднані з відповідними виходами керуючого пристрою, вхід якого з'єднаний з керуючим входом перетворювача, вхід "скид" перетворювача з'єднаний з входами "скид" регістру входу, керуючого тригера та керуючого пристрою, крім того, прямий вихід тригера з'єднаний з входом інвертора, вихід якого підключений до входу диференціюючого ланцюга, вихід якого підключений до керуючого входу блока МДП - ключів, інформаційні входи якого з'єднані з відповідними виходами регістру входу, інформаційні виходи блока МДП-ключів з'єднані з інформаційними входами регістру входу і є "входом/виходом" перетворювача, який відрізняється тим, що додатково введено перший елемент "І", перший вхід якого підключено до інверсного виходу керуючого тригера, а другий вхід з'єднаний з додатково введеним другим керуючим входом перетворювача, вихід введеного першого елемента "І" підключено до дозволяючого входу першої комбінаційної схеми адреси, додатково введено другий елемент "І", перший вхід якого підключено до інверсного виходу керуючого тригера, а другий вхід з'єднаний з додатково введеним третім керуючим входом перетворювача, вихід другого елемента "І" підключено до дозволяючого входу додатково введеної другої комбінаційної схеми адреси, входи якої з'єднані з відповідними виходами регістру входу, а виходи підключені до відповідних входів додатково введеного блока елементів АБО, відповідні входи якого з'єднані з відповідними виходами першої комбінаційної схеми адреси, а виходи додатково введеного блока елементів АБО з'єднані з відповідними входами блока вентилів.

Текст

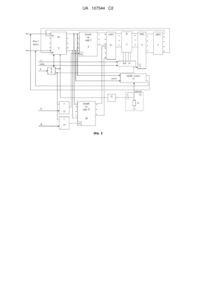

Реферат: Винахід належить до галузі обчислювальної техніки. Перетворювач двійкового коду в однополярні оборотні коди і навпаки містить регістр входу, першу комбінаційну схему адреси, блок вентилів, ПЗП, блок елементів АБО, керуючий тригер, керуючим вхід ПЗП, дозволяючий вхід першої комбінаційної схеми адреси, перший керуючий вхід перетворювача, вхід "скид", інвертор, диференціюючий ланцюг, блок МДП-ключів, з відповідними зв'язками, в перетворювач додатково введено перший елемент "І", перший вхід якого з'єднаний з інверсним виходом керуючого тригера, а другий вхід з'єднаний з додатково введеним другим керуючим входом перетворювача, вихід введеного першого елемента "І" підключено до дозволяючого входу першої комбінаційної схеми адреси, додатково введено другий елемент "І", перший вхід якого з'єднаний з інверсним виходом керуючого тригера, а другий вхід з'єднаний з додатково введеним третім керуючим входом перетворювача, вихід введеного другого елемента "І" підключено до додатково введеного дозволяючого входу додатково введеної другої комбінаційної схеми адреси, входи якої з'єднані з відповідними виходами регістру входу, а виходи підключені до відповідних входів додатково введеного блока елементів АБО, відповідні входи якого також з'єднані з виходами першої комбінаційної схеми адреси, а виходи додатково введеного блока елементів АБО з'єднаний з відповідними входами блока вентилів. Технічним результатом, що досягається, є розширення функціональних можливостей перетворювача. UA 107544 C2 (12) UA 107544 C2 UA 107544 C2 5 10 15 20 25 30 35 40 45 50 55 60 Винахід належить до обчислювальної техніки і призначається для використання в інформаційних обчислювальних системах, в дискретних перетворювачах координат, у системах з функціональними перетворювачами дискретної інформації. Відомий перетворювач двійкового коду, який містить регістр входу, ПЗП, блок елементів АБО, керуючий тригер, вхід "скид", комбінаційну схему адреси, блок вентилів, керуючий пристрій. [1]. Недоліком даного перетворювача є низька надійність та вузькі функціональні можливості. Найбільш близьким по технічній суті та схемному рішенню до запропонованого є перетворювач двійкового коду в однополярні оборотні коди [2], який містить регістр входу, виконаний на тригерах з інформаційними та лічильними входами, інформаційні входи регістру входу з'єднані з входами перетворювача, а виходи з'єднані з відповідними входами першої комбінаційної схеми адреси, виходи блока вентилів з'єднані з відповідними входами ПЗП, виходи якого з'єднані через блок елементів АБО з відповідними лічильними входами регістру входу, керуючий вхід регістру входу з'єднаний з прямим виходом керуючого тригера, а інверсний вихід керуючого тригера з'єднаний з керуючим входом ПЗП, перша комбінаційна схема адреси містить дозволяючий вхід, вхід керуючого тригера з'єднаний з першим керуючим входом перетворювача, керуючі входи блока вентилів з'єднані з відповідними виходами керуючого пристрою, вхід якого з'єднаний з керуючим входом перетворювача, вхід "скид" перетворювача з'єднаний з входами "скид" регістру входу, керуючого тригера та керуючого пристрою, крім того, прямий вихід тригера з'єднаний з входом інвертора, вихід якого підключений до входу диференціюючого ланцюга, вихід якого підключений до керуючого входу блока МДП-ключів, інформаційні входи якого з'єднані з відповідними виходами регістру входу, інформаційні виходи блока МДП-ключів з'єднані з інформаційними входами регістру входу і є "входом/виходом" перетворювача. Недоліком даного перетворювача є вузькі функціональні можливості. Задача винаходу-розширення функціональних можливостей перетворювача. Зазначена задача досягається тим, що в основу винаходу перетворювача двійкового коду в однополярні оборотні коди і навпаки поставлено задачу розширення функціональних можливостей шляхом схемотехнічного рішення. Поставлена задача вирішується тим, що додатково введено перший елемент "І", перший вхід якого підключено до інверсного виходу керуючого тригера, а другий вхід з'єднаний з додатково введеним другим керуючим входом перетворювача, вихід введеного першого елемента "І" підключено до дозволяючого входу першої комбінаційної схеми адреси, додатково введено другий елемент "І", перший вхід якого підключено до інверсного виходу керуючого тригера, а другий вхід з'єднаний з додатково введеним третім керуючим входом перетворювача, вихід введеного другого елемента "І" підключено до додатково введеного дозволяючоговходу додатково введеної другої комбінаційної схеми адреси, входи якої з'єднані з відповідними виходами регістру входу, а виходи підключені до відповідних входів додатково введеного блока елементів АБО, відповідні входи якого з'єднані з відповідними виходами першої комбінаційної схеми адреси, а виходи додатково введеного блока елементів АБО з'єднані з відповідними входами блока вентилів, забезпечено додаткову можливість перетворення вхідного однополярного оборотного коду в двійковий код, завдяки запропонованому рішенню для всіх ознак, які вказані в частині формули, що відрізняється, і виявляють в процесі взаємодії характерні їм відомі властивості, що дають кожен із них окремо відомий позитивний ефект. Отже, забезпечується надпідсумковий позитивний ефект, зумовлений сукупністю вказаних ознак, що задовольняє критерію "суттєві відмінності". На кресленні зображена структурна схема перетворювача двійкового коду в однополярні оборотні коди і навпаки. Перетворювач двійкового коду в однополярні оборотні коди і навпаки містить регістр входу 1, виконаний на тригерах з інформаційними та лічильними входами, інформаційні входи регістру входу 1 з'єднані з входами перетворювача, а виходи з'єднані з відповідними входами першої комбінаційної схеми адреси 2, виходи блока вентилів 3 з'єднані з відповідними входами ПЗП 4, виходи якого з'єднані через блок елементів АБО 5 з відповідними лічильними входами регістру входу 1, керуючий вхід регістру входу 1 з'єднаний з прямим виходом керуючого тригера 6, а інверсний вихід керуючого тригера 6 з'єднаний з керуючим входом 7 ПЗП 4, перша комбінаційна схема адреси 2 містить дозволяючий вхід 8, вхід керуючого тригера 6 з'єднаний з першим керуючим входом 9 перетворювача, керуючі входи блока вентилів 3 з'єднані з відповідними виходами керуючого пристрою 10, вхід якого з'єднаний з керуючим входом 11 перетворювача, вхід "скид" перетворювача з'єднаний з входами "скид" регістру входу 1, 1 UA 107544 C2 5 10 15 20 керуючого тригера 6 та керуючого пристрою 10, крім того, прямий вихід тригера 6 з'єднаний з входом інвертора 12, вихід якого підключений до входу диференціюючого ланцюга 13, вихід якого підключений до керуючого входу блока МДП - ключів 14, інформаційні входи якого з'єднані з відповідними виходами регістру входу 1, інформаційні виходи блока МДП-ключів 14 з'єднані з інформаційними входами регістру входу 1 і є "входом/виходом" перетворювача, в нього додатково введено перший елемент "І" 15, перший вхід якого підключено до інверсного виходу керуючого тригера 6, а другий вхід з'єднаний з додатково введеним другим керуючим входом 16 перетворювача, вихід введеного першого елемента "І" 15 підключено до дозволяючого входу 8 першої комбінаційної схеми адреси 2, додатково введено другий елемент "І" 17, перший вхід якого підключено до інверсного виходу керуючого тригера 6, а другий вхід з'єднаний з додатково введеним третім керуючим входом 18 перетворювача, вихід введеного другого елемента "І" 17 підключено до додатково введеного дозволяючого входу 19 додатково введеної другої комбінаційної схеми адреси 20, входи якої з'єднані з відповідними виходами регістру входу 1, а виходи підключені до відповідних входів додатково введеного блока елементів АБО 21, відповідні входи якого з'єднані з відповідними виходами першої комбінаційної схеми адреси 2, а виходи додатково введеного блока елементів АБО 21 з'єднані з відповідними входами блока вентилів 3. При проектуванні перетворювачів двійкового коду в однополярні оборотні коди і навпаки, на ряду з традиційними етапами розробки включаються наступні: - заздалегідь складається таблиця двійкових кодових комбінацій Ai та відповідних однополярних оборотних кодів Ві; - значення коригуючих констант А; для відповідних кодових послідовностей визначаються за формулою Δi=Ai Ві, (1) 25 З формули (1) видно, що завдяки властивості операції додавання по mod 2 вихідна кодова послідовність Ві визначається Ві = А Δi, 30 а зворотна вхідна кодова послідовність відповідно Ai = Δi Ві. 35 45 50 (3) Аналіз формул (1), (2), (3) показує, що для прямого та зворотного перетворення використовується одна і та ж константа Δi. Наприклад, коли Δi визначається за формулою (1) Bi 1011011100 010010 40 (2) A i 1001111101 010110 i 0010100001 000100 тоді Вi=10011111010101100010100001000100=1011011100010010 Аі=00101000010001001011011100010010=1001111101010110 Отже відтворення Ai або Ві здійснюється за допомогою одного об'єму коригуючих констант. Завдяки використанню одних і тих же значень коригуючих констант зменшується об'єм пам'яті не менш ніж в 2 рази, при цьому функціональні можливості перетворювача розширені в 2 рази. У випадку коли двійковий код А та однополярний оборотний код В мають різну кількість розрядів, рекомендується двійковий код та однополярний оборотний код перетворювача представляти однаковою розрядністю, для цього дописуються нулі у кодову послідовність наступним чином: - до коми в старші розряди; - після коми в молодші розряди. При подальшому зменшенні об'єму пам'яті пропонується: 1) коди розбивати на відповідні тетради; 2) коригуючі константи представляти чотирирозрядними кодами, які є результатами додавання по mod 2 відповідних тетрад для обох зазначених Ai та Ві кодових послідовностей. 2 UA 107544 C2 5 Наприклад, 16 розрядна вхідна двійкова кодова послідовність, яка має вигляд: А-0001100001001110 перетворюється у відповідні вихідні n - розрядні кодові послідовності однополярних оборотних кодів Ві, які мають вигляд В3-110; В5-11101; В7-1110010; В11-11100010010; В13-111100110101 (однополярні коди Баркера). Згідно зазначених вище рекомендацій відповідні кодові послідовності, які представляються однаковою розрядністю та розбиті на тетради, мають наступний вигляд А - 0001100001001110 - 0000_0000_0000_0110; - 0000_0000_0000_1110; - 0000_0000_01110010; - 0000_0111_0001_0010; - 000111110011_0101. В3-0000000000000110; В5-0000000000001110; В7-0000000001110010; В11-0000011100010010; В13-0001111100110101; 10 Для кожної тетради в таблиці 1 наведені значення коригуючих констант, що визначалися за формулою (1). Таблиця 1 Значення тетрад коригуючих кодових констант для відповідних тетрад кодових послідовностей A i та Ві Тетради код Δi константи для В3 код Δiконстанти для в5 коду Δi константи для в7 код Δi константи для В11 код Δi константи для В13 код A1 0001 Δ1_3 0001 код А2 1000 Δ2_3 1000 код А3 0100 Δ3_3 0100 код А4 1110 Δ4_3 1000 Δ1_5 0001 Δ2_5 1000 Δ3_5 0101 Δ4_5 0011 Δ1_7 0001 Δ2_7 1000 Δ3_7 0011 Δ4_7 1100 Δ1_11 0001 Δ1_13 0000 Δ2_11 1111 Δ2_13 0111 Δ3_11 0101 Δ3_13 0111 Δ4_11 1100 Δ4_13 1011 де і=1 - старша тетрада; і=2, і=3 середні тетради, і=4 - молодша тетрада. 15 20 25 30 Перетворювач двійкового коду в однополярні оборотні коди і навпаки працює у двох режимах: або перетворення двійкового коду в однополярний оборотний код A i → Ві, або перетворення однополярного оборотного коду в двійковий код Ві → Ai. Процес в режимі перетворення двійкового коду в однополярні оборотні коди A i → Ві здійснюється наступним чином. Перед перетворенням вхідного двійкового коду, що надходить на входи перетворювача, імпульсом, що приходить на вхід "скид" перетворювача встановлюються в нульовий стан регістр входу 1, тригер 6, керуючий пристрій 10. Імпульс запуску 9 надходить на лічильний вхід тригера 6 і на виході регістру входу 1 встановлюється вхідна кодова послідовність інформації. При цьому сигнал з інверсного виходу тригера 6 надходить на перший вхід першого елемента "І" 15, на другий вхід якого поступає сигнал з керуючого входу 16, в результаті їх одночасного надходження на виході першого елемента "І" 15 з'являється сигнал, який надходить на дозволяючий вхід 8 першої комбінаційної схеми адреси 2, при цьому сигнал інверсного виходу тригера 6 надходить на дозволяючий вхід 7 ПЗП 4. При надходженні керуючого імпульсу 11 на вхід керуючого пристрою 10, на відповідному виході якого з'являється імпульс, який дозволяє відповідному імпульсу з виходу першої комбінаційної схеми адреси 2 пройти через блок елементів АБО 21 та блок вентилів 3 і зчитати із ПЗП 4 коди значень відповідних коригуючих констант, які через блок елементів АБО 5 надходять на відповідні лічильні входи регістру входу 1. Під дією одиниць коду коригуючої константи відбувається перекидання станів тригерів 3 UA 107544 C2 5 10 15 20 25 30 35 40 45 регістру входу 1 в інший стан, тобто відбувається сумування по mod 2 вхідного двійкового коду та відповідного коду коригуючої константи і на виході регістру входу 1 з'являється відповідний однополярний оборотний код, який надходить на інформаційні входи блока МДП-ключів 14, однополярний оборотний код з'явиться на виході блока МДП-ключів 14 після надходження керуючого сигналу a(t+Δt) з прямого виходу керуючого тригера 6 через інвертор 12 і диференціюючий вузол 13, результат перетворення з'являється на виході перетворювача завдяки з'єднанню "вхід/вихід" з виходами блока МДП-ключів 14. Процес в режимі перетворення однополярного оборотного коду в двійковий код В і → Ai відрізняється тим, що: Після обнулення тригерів перетворювача, імпульс запуску 9 надходить на лічильний вхід тригера 6 й на виході регістру входу 1 встановлюється вхідна кодова послідовність інформації. При цьому сигнал з інверсного виходу тригера 6 надходить на перший вхід другого елемента "І" 17, на другий вхід якого поступає сигнал з керуючого входу 18, в результаті їх одночасного надходження на виході другого елемента "І" 17 з'являється сигнал, який надходить на дозволяючий вхід 19 другої комбінаційної схеми адреси 20, при цьому сигнал інверсного виходу тригера 6 надходить на дозволяючий вхід 7 ПЗП 4. При надходженні керуючого імпульсу 11 на вхід керуючого пристрою 10, на відповідному виході якого з'являється імпульс, який дозволяє відповідному імпульсу з виходу другої комбінаційної схеми адреси 20 пройти через блок елементів АБО 21 та блок вентилів 3 і зчитати із ПЗП 4 коди значень відповідних коригуючих констант, які через блок елементів АБО 5 надходять на відповідні лічильні входи регістру входу 1. Під дією одиниць коду коригуючої константи відбувається перекидання станів тригерів регістру входу 1 в інший стан, тобто відбувається сумування по mod 2 вхідного однополярного оборотного коду та відповідного коду коригуючої константи і на виході регістру входу 1 з'являється відповідний двійковий код, який надходить на інформаційні входи блока МДП-ключів 14, двійковий код з'явиться на виході блока МДП-ключів 14 після надходження керуючого сигналу a(t+Δt) з прямого виходу керуючого тригера 6 через інвертор 12 і диференціюючий вузол 13, результат перетворення з'являється на виході перетворювача завдяки з'єднанню "вхід/вихід" з виходами блока МДП-ключів 14. Отже перевагою перетворювача двійкового коду в однополярні оборотні коди і навпаки в порівнянні з прототипом є розширення функціональних можливостей в 2 рази. При цьому, зменшується об'єм пам'яті не менш ніж в 2 рази, завдяки використанню одних і тих же значень коригуючих констант, що сприяє збільшенню проценту виходу придатних кристалів з пластини і, як наслідок, зменшується собівартість. Крім того, при розподіленні кодів на тетради, що перетворюються, з'являється можливість варіювати об'ємом пам'яті завдяки тому, що кожний загальний стовпчик тетради (див. табл. 1) 4 має об'єм (2 -1)·4 біт, тому за рахунок використання одного або декількох таких стовпців одночасно з'являється можливість варіювати об'ємом пам'яті, що залежить від вимог до швидкості перетворення. Джерела інформації: 1. Патент № 44833 Перетворювач двійкового коду в однополярні оборотні коди, МПК G 06 F 5/00 Лукашенко В.М. та інші. 2. Пат. 72952 Україна, МПК (2012.01) G 06 F 5/00. Перетворювач двійкового коду в однополярні оборотні коди /А.Г. Лукашенко, В.М. Лукашенко, К.С. Рудаков, Д.А. Лукашенко, О.С. Вербицький, С.А. Міценко, В.А. Лукашенко; заявник та власник Черкас, держ. технол. ун-т. № u201113847; заявл. 24.11.2011; опубл. 10.09.2012, Бюл. № 17. ФОРМУЛА ВИНАХОДУ 50 55 60 Перетворювач двійкового коду в однополярні оборотні коди і навпаки містить регістр входу, виконаний на тригерах з інформаційними та лічильними входами, інформаційні входи регістру входу з'єднані з входами перетворювача, а виходи з'єднані з відповідними входами першої комбінаційної схеми адреси, виходи блока вентилів з'єднані з відповідними входами ПЗП, виходи якого з'єднані через блок елементів АБО з відповідними лічильними входами регістру входу, керуючий вхід регістру входу з'єднаний з прямим виходом керуючого тригеру, а інверсний вихід керуючого тригера з'єднаний з керуючим входом ПЗП, перша комбінаційна схема адреси містить дозволяючий вхід, вхід керуючого тригера з'єднаний з першим керуючим входом перетворювача, керуючі входи блока вентилів з'єднані з відповідними виходами керуючого пристрою, вхід якого з'єднаний з керуючим входом перетворювача, вхід "скид" перетворювача з'єднаний з входами "скид" регістру входу, керуючого тригера та керуючого пристрою, крім того, прямий вихід тригера з'єднаний з входом інвертора, вихід якого 4 UA 107544 C2 5 10 15 підключений до входу диференціюючого ланцюга, вихід якого підключений до керуючого входу блока МДП-ключів, інформаційні входи якого з'єднані з відповідними виходами регістру входу, інформаційні виходи блока МДП-ключів з'єднані з інформаційними входами регістру входу і є "входом/виходом" перетворювача, який відрізняється тим, що додатково введено перший елемент "І", перший вхід якого підключено до інверсного виходу керуючого тригера, а другий вхід з'єднаний з додатково введеним другим керуючим входом перетворювача, вихід введеного першого елемента "І" підключено до дозволяючого входу першої комбінаційної схеми адреси, додатково введено другий елемент "І", перший вхід якого підключено до інверсного виходу керуючого тригера, а другий вхід з'єднаний з додатково введеним третім керуючим входом перетворювача, вихід другого елемента "І" підключено до дозволяючого входу додатково введеної другої комбінаційної схеми адреси, входи якої з'єднані з відповідними виходами регістру входу, а виходи підключені до відповідних входів додатково введеного блока елементів АБО, відповідні входи якого з'єднані з відповідними виходами першої комбінаційної схеми адреси, а виходи додатково введеного блока елементів АБО з'єднані з відповідними входами блока вентилів. Комп’ютерна верстка А. Крижанівський Державна служба інтелектуальної власності України, вул. Урицького, 45, м. Київ, МСП, 03680, Україна ДП “Український інститут промислової власності”, вул. Глазунова, 1, м. Київ – 42, 01601 5

ДивитисяДодаткова інформація

Автори англійськоюLukashenko Andrii Hermanovych, Lukashenko Valentyna Maksymivna, Zubko Ihor Anatoliiovych, Lukashenko Dmytro Andriiovych, Lukashenko Volodymyr Andriiovych

Автори російськоюЛукашенко Андрей Германович, Лукашенко Валентина Максимовна, Зубко Игорь Анатольевич, Лукашенко Дмитрий Андреевич, Лукашенко Владимир Андреевич

МПК / Мітки

МПК: H03M 5/00, H03M 7/00, G06F 5/00

Мітки: оборотні, перетворювач, коду, двійкового, коді, однополярні, навпаки

Код посилання

<a href="https://ua.patents.su/7-107544-peretvoryuvach-dvijjkovogo-kodu-v-odnopolyarni-oborotni-kodi-i-navpaki.html" target="_blank" rel="follow" title="База патентів України">Перетворювач двійкового коду в однополярні оборотні коди і навпаки</a>

Попередній патент: Пристрій термостатування п’єзорезонансних коливальних систем напівпровідниковими термостатуючими елементами

Наступний патент: Система та спосіб для визначення положення й перекосу вантажозахватного пристрою крана

Випадковий патент: Спосіб одержання засобу,що має антитоксичну і радіопротекторну активність