Багатофункціональний таблично-логічний співпроцесор

Номер патенту: 111459

Опубліковано: 25.04.2016

Автори: Лукашенко Андрій Германович, Лукашенко Валентина Максимівна, Лукашенко Дмитро Андрійович, Лукашенко Володимир Андрійович, Зубко Ігор Анатолійович

Формула / Реферат

Багатофункціональний таблично-логічний співпроцесор, що містить вхідний регістр, виконаний на тригерах з лічильними та інформаційними входами, дешифратор коду Грея, інформаційні входи якого підключені до розрядних виходів вхідного регістра, а вхід керування з'єднаний з виходом першого елемента "І", керуючий вхід якого з'єднаний з інверсним виходом керуючого тригера, прямий вихід якого підключений до керуючого входу вхідного регістра, вхід керуючого тригера є першим керуючим входом співпроцесора, а вхід скидання підключений до входу скидання співпроцесора, виходи дешифратора коду Грея через групу елементів "АБО" підключені до відповідних входів шифратора корегуючих констант, виходи якого з'єднані з лічильними входами вхідного регістра, розрядні виходи якого підключені до інформаційних входів дешифратора двійкового коду, виходи якого підключені до відповідних входів групи елементів "АБО", керуючий вхід дешифратора двійкового коду з'єднаний з виходом другого елемента "І", керуючий вхід якого з'єднаний з інверсним виходом керуючого тригера, інформаційний вхід першого елемента "І" є другим керуючим входом для коду Грея, інформаційний вхід другого елемента "І" є третім керуючим входом для двійкових кодів, крім того, прямий вихід тригера з'єднаний з входом інвертора, вихід якого підключений до входу диференціюючого ланцюга, вихід якого підключений до керуючого входу блока МДП-ключів, інформаційні входи якого з'єднані з відповідними виходами вхідного регістра, інформаційні виходи блока МДП-ключів з'єднані з інформаційними входами вхідного регістру і є "входом/виходом" співпроцесора, дешифратор однополярного коду Баркера, до інформаційних входів якого підключені розрядні виходи вхідного регістра, а виходи дешифратора однополярного коду Баркера підключені до відповідних входів групи елементів "АБО", керуючий вхід дешифратора однополярного коду Баркера з'єднаний з виходом третього елемента "І", керуючий вхід, який з'єднаний з інверсним виходом керуючого тригера, інформаційний вхід третього елемента "І" є четвертим керуючим входом для однополярного коду Баркера, який відрізняється тим, що додатково введені дешифратор значень синуса, четвертий керуючий елемент "І", при цьому дешифратор значень синуса інформаційними входами з'єднаний з відповідними розрядними виходами вхідного регістра, а виходи дешифратора значень синуса підключені до відповідних входів групи елементів "АБО", керуючий вхід дешифратора значень синуса з'єднаний з виходом четвертого елемента "І", перший вхід якого є керуючим входом, що з'єднаний з інверсним виходом керуючого тригера, другий вхід четвертого елемента "І" підключений до інформаційного входу і є п'ятим керуючим входом для функції sin(x) багатофункціонального таблично-логічного співпроцесора.

Текст

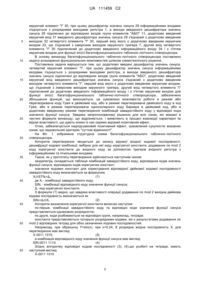

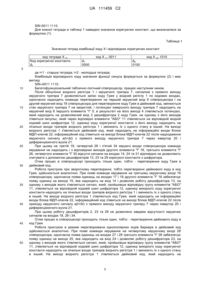

Реферат: Винахід належить до обчислювальної техніки. Багатофункціональний таблично-логічний співпроцесор містить вхідний регістр, виконаний на тригерах з лічильними та інформаційними входами, дешифратор коду Грея, перший елемент "1", керуючий тригер, групу елементів "АБО", шифратор корегуючих констант, дешифратор двійкового коду, другий елемент "І" третій елемент "І", інвертор, диференціюючий ланцюг, блок МДП-ключів, з відповідними зв'язками, додатково введено дешифратор значень синуса, до інформаційних входів якого підключені розрядні виходи регістра, а виходи введеного дешифратор значень синуса підключені до відповідних входів групи елементів "АБО", керуючий вхід дешифратор значень синуса з'єднаний з виходом четвертого елемента "І", керуючий вхід, який з'єднаний з інверсним виходом керуючого тригера, інформаційний вхід четвертого елемента "І" є п'ятим керуючим входом для багатофункціонального таблично-логічного співпроцесора. Технічним результатом, що досягається даним винаходом, є розширення функціональних можливостей співпроцесора. UA 111459 C2 (12) UA 111459 C2 UA 111459 C2 5 10 15 20 25 30 35 40 45 50 55 60 Винахід належить до обчислювальної техніки і призначений для використання в інформаційних обчислювальних системах. Відомий таблично-логічний перетворювач кодів, який містить регістр входу, блок елементів "АБО", керуючий тригер, вхід "скид", диференціюючий ланцюг, блок МДП-ключів [1]. Недоліком цього перетворювача є вузькі функціональні можливості. Найбільш близьким до пропонованого по технічній суті є таблично-логічний перетворювач кодів [2], що містить вхідний регістр, виконаний на тригерах з лічильними та інформаційними входами, дешифратор коду Грея, інформаційні входи якого підключені до розрядних виходів вхідного регістра, а вхід керування з'єднаний з виходом першого елемента "І", керуючий вхід якого з'єднаний з інверсним виходом керуючого тригера, прямий вихід якого підключений до керуючого входу вхідного регістра, вхід керуючого тригера є першим керуючим входом перетворювача, а вхід скидання підключений до входу скидання перетворювача, виходи дешифратора коду Грея через групу елементів "АБО" підключені до відповідних входів шифратора корегуючих констант, виходи якого з'єднані з лічильними входами вхідного регістра, розрядні виходи якого підключені до інформаційних входів дешифратора двійкового коду, виходи якого підключені до відповідних входів групи елементів "АБО", керуючий вхід дешифратора з'єднаний з виходом другого елемента "І", керуючий вхід якого з'єднаний з інверсним виходом керуючого тригера, інформаційний вхід першого елемента "І" є другим керуючим входом перетворювача для коду Грея, інформаційний вхід другого елемента "І" є третім керуючим входом для перетворювача двійкових кодів, крім того, прямий вихід тригера з'єднаний з входом інвертора, вихід якого підключений до входу диференціюючого ланцюга, вихід якого підключений до керуючого входу блока МДП-ключів, інформаційні входи якого з'єднані з відповідними виходами вхідного регістра, інформаційні виходи блока МДП-ключів з'єднані з інформаційними входами вхідного регістру і є "входом/виходом" перетворювача кодів, дешифратор однополярного коду Баркера, до інформаційних входів якого підключені розрядні виходи регістра, а виходи дешифратора однополярного коду Баркера підключені до відповідних входів групи елементів "АБО", керуючий вхід дешифратора однополярного коду Баркера з'єднаний з виходом третього елемента "І", керуючий вхід, який з'єднаний з інверсним виходом керуючого тригера, інформаційний вхід третього елемента "І" є четвертим керуючим входом для таблично-логічного перетворювача кодів. Недоліком даного перетворювача є відсутність математичної операції відтворення функції sin(x), що обмежує область використання. Мета винаходу - розширення функціональних можливостей багатофункціонального таблично-логічного співпроцесора. Зазначена мета досягається тим, що у багатофункціональний таблично-логічний співпроцесор, що містить вхідний регістр 1, виконаний на тригерах з лічильними та інформаційними входами, дешифратор 2 коду Грея, інформаційні входи якого підключені до розрядних виходів вхідного регістра 1, а вхід керування 3 з'єднаний з виходом 4 першого елемента "І" 5, керуючий вхід 6 якого з'єднаний з інверсним виходом керуючого тригера 7, прямий вихід 8 якого підключений до керуючого входу вхідного регістра 1, вхід 9 керуючого тригера 7 є першим керуючим входом співпроцесора, а вхід скидання 10 підключений до входу скидання співпроцесора, виходи дешифратора 2 коду Грея через групу елементів "АБО" 11 підключені до відповідних входів шифратора корегуючих констант 12, виходи якого з'єднані з лічильними входами вхідного регістра 1, розрядні виходи якого підключені до інформаційних входів дешифратора двійкового коду 13, виходи якого підключені до відповідних входів групи елементів "АБО" 11, керуючий вхід 14 цього дешифратора 13 з'єднаний з виходом 15 другого елемента "І" 16, керуючий вхід 17 якого з'єднаний з інверсним виходом керуючого тригера 7, інформаційний вхід 18 першого елемента "І" 5 є другим керуючим входом для коду Грея, інформаційний вхід 19 другого елемента "І" 16 є третім керуючим входом для двійкових кодів, крім того, прямий вихід тригера 7 з'єднаний з входом інвертора 20, вихід якого підключений до входу диференціюючого ланцюга 21, вихід якого підключений до керуючого входу блока МДПключів 22, інформаційні входи якого з'єднані з відповідними виходами вхідного регістра 1, інформаційні виходи блока МДП-ключів 22 з'єднані з інформаційними входами вхідного регістру 1 і є "входом/виходом" співпроцесора, дешифратор однополярного коду Баркера 23, до інформаційних входів якого підключені розрядні виходи регістра 1, а виходи дешифратора однополярного коду Баркера 23 підключені до відповідних входів групи елементів "АБО" 11, керуючий вхід 24 дешифратора однополярного коду Баркера 23 з'єднаний з виходом 25 третього елемента "І" 26, керуючий вхід 27, який з'єднаний з інверсним виходом керуючого тригера 7, інформаційний вхід 28 третього елемента "І" 26 є четвертим керуючим входом для однополярного коду Баркера, додатково введені дешифратор значень синуса 29, четвертий 1 UA 111459 C2 5 10 15 20 25 30 35 40 45 50 55 керуючий елемент "І" 30, при цьому дешифратор значень синуса 29 інформаційними входами з'єднується з розрядними виходами регістра 1, а виходи введеного дешифратора значень синуса 29 підключені до відповідних входів групи елементів "АБО" 11, додатково введений керуючий вхід 31 введеного дешифратора значень синуса 29 з'єднаний з додатково введеним виходом 32 четвертого елемента "І" 30, перший вхід якого є додатково введеним керуючим входом 33, що з'єднаний з інверсним виходом керуючого тригера 7, другий вхід четвертого елемента "І" 30 підключений до додатково введеного інформаційного входу 34 і є п'ятим керуючим входом для функції sin(x) багатофункціонального таблично-логічного співпроцесора. В основу винаходу багатофункціонального таблично-логічного співпроцесора поставлено задачу розширення функціональних можливостей шляхом схемотехнічного рішення. Поставлена задача вирішується тим, що додатково введені дешифратор значень синуса, четвертий керуючий елемент "І", при цьому дешифратор значень синуса інформаційними входами з'єднується з розрядними виходами регістра, а виходи введеного дешифратора значень синуса підключені до відповідних входів групи елементів "АБО", додатково введений керуючий вхід введеного дешифратора значень синуса з'єднаний з додатково введеним виходом четвертого елемента "І", перший вхід якого є додатково введеним керуючим входом, що з'єднаний з інверсним виходом керуючого тригера, другий вхід четвертого елемента "І" підключений до додатково введеного інформаційного входу і є п'ятим керуючим входом для функції sin(x) багатофункціонального таблично-логічного співпроцесора, забезпечено збільшення функцій, що виконуються, це зумовлено можливістю роботи в режимі або перетворювача коду Грея в двійковий код, або в режимі перетворювача двійкового коду в код Грея, або в режимі перетворювача однополярного коду Баркера в двійковий код, або в додатково введеному режимі перетворення комбінацій завадостійкого коду у відповідні коди значення функції синуса. Завдяки запропонованому рішенню для всіх ознак, які вказані в частині формули винаходу, що відрізняється, і виявляють в процесі взаємодії характерні їм відомі властивості, що дають кожен із них окремо відомий позитивний ефект. Отже, забезпечується надпідсумковий позитивний ефект, зумовлений сукупністю вказаних ознак, що задовольняє критерію "суттєві відмінності". На Фіг. 1 зображена структурна схема багатофункціонального таблично-логічного співпроцесора. Алгоритм перетворення зводиться до запису відомої вхідної кодової послідовності, дешифрації кодової комбінації, вибірки для неї коду корегуючої константи, додавання по mod 2 коду корегуючої константи до вхідного коду за допомогою тригерів вхідного регістра з інформаційними та лічильними входами. Також, як у прототипу перетворення здійснюється наступним чином: заздалегідь складається таблиця комбінацій завадостійкого коду, відповідних кодів значень функції синуса, відповідних кодів корегуючих констант; значення кодових констант для коректування відповідної двійкової кодової послідовності завадостійкого коду визначаються за формулою (1) XiSTNi=Δі, де Хі - комбінації завадостійкого коду; SINi - комбінації відповідного коду значення функції синуса; Δі -код корегуючої константи. З формули (1) видно, що завдяки властивості операції додавання по mod 2 вихідна двійкова кодова послідовність визначається як (2) SINi=ΔіХі. Алгоритм визначення корегуючої константи включає наступне: по-перше, комбінації завадостійкого коду та відповідні коди значення функції синуса представляється однаковою розрядністю; по друге, коди розбиваються на відповідні групи, наприклад, тетради; константи представляються чотирьох розрядними кодами, які є результатами додавання по mod 2 відповідних тетрад для обох зазначених кодових послідовностей. Наприклад, при обрахунку Y=sin(x), при х=0.24, 8 розрядна вхідна послідовність Х і для перетворення має вигляд: Х-0011 1010, (3) а комбінація відповідного коду значення функції синуса має вигляд: SIN-0011 1110. (4) Згідно алгоритму відповідні кодові послідовності (3), (4),що розбиті на тетради, мають наступний вигляд Х-0011 1010 2 UA 111459 C2 SIN-0011 1110. Для кожної тетради в таблиці 1 наведені значення корегуючих констант, що визначалися за формулою (1). Таблиця 1 Значення тетрад комбінації коду X і відповідних коригуючих констант код тетради Х (і) Код коригуючої константи Δі код Х (1) 0011 Δ1 0000 код X (2) 1010 Δ2 0100 5 10 15 20 25 30 35 40 45 50 де і=1 - старша тетрада; і=2 - молодша тетрада; Комбінація відповідного коду значення функції синуса формується за формулою (2) і має вигляд SIN=0011 1110. Багатофункціональний таблично-логічний співпроцесор, працює наступним чином. Після обнуління вхідного регістра 1 і керуючого тригера 7, сигналом з прямого виходу керуючого тригера 7 дозволяється запис коду Грея у вхідний регістр 1 по кодових входах, одночасно надходять команди перетворення на перший керуючий вхід 9 співпроцесора і на другий керуючий вхід 18 співпроцесора для перетворення коду Грея в двійковий код, змінюється стан керуючого тригера 7 на зворотній, і потенціал інверсного виходу тригера 7 надходить на керуючий вхід 6 першого елемента "І" 5, в результаті на його виході 4 з'являється потенціал, який надходить на дозволяючий вхід 3 дешифратора 2 коду Грея, на одному з його виходів з'явиться імпульс, який через відповідні елементи "АБО" 11 з'являється на відповідній вхідній кодовій шині шифратора 12, одиниці коду корегуючої константи з його виходу надходять на лічильні входи тригерів вхідного регістра 1 і змінюють їх з одного стану в інший. На виході вхідного регістра 1 з'являється двійковий код, який надходить на інформаційні входи блока МДП-ключів 22, інформаційний код з'явиться на виході блока МДП-ключів 22 після надходження керуючого сигналу a(t+Δt) з прямого виходу керуючого тригера 7 через інвертор 20 і диференціюючого вузла 21. При цьому на третій 19, четвертий 28 і п'ятий 34 керуючі входи співпроцесора команда керування не надходить і з відповідних виходів другого елемента "І" 16, третього елемента "І" 26, четвертого елемента "І" 30 відсутні сигнали на входах 14, 24 та 31 відповідно не дозволяють зчитувати з допомогою дешифраторів 13, 23 та 29 корегуючі константи з шифратора. Отже процес в співпроцесорі проходить тільки один, тобто - перетворення коду Грея в двійковий код. Робота пристрою при зворотному перетворенні, тобто перетворенні двійкового коду в код Грея, здійснюється аналогічно. При появі команди керування на третьому керуючому вході 19 співпроцесора, одночасна поява одиниць на входах 17 і 19 другого елемента "І" 16 забезпечує появу одиниці на виході 15, яка надходить на вхід 14 і дозволяє роботу дешифратора 13, на одному з виходів якого з'являється сигнал, який, пройшовши відповідну групу елементів "АБО" 11, з'являється на відповідній кодовій шині шифратора 12, одиниці вихідного коду корегуючої константи надходять на лічильні входи тригерів вхідного регістра 1 і змінюють їх з одного стану в інший. На виході вхідного регістра 1 з'являється код Грея, який надходить на інформаційні входи блока МДП-ключів 22, інформаційний код з'явиться на виході блока МДП-ключів 22 після приходу керуючого сигналу a(t+At) з прямого виходу керуючого тригеру 7 через інвертор 20 і диференціюючого вузла 21. При цьому роботу дешифраторів 2, 23 та 29 не дозволено завдяки відсутності керуючих сигналів на входах 18, 28 і 34. Отже процес в співпроцесорі проходить тільки один, тобто - перетворення двійкового коду в код Грея. Робота пристрою в режимі перетворювача однополярних кодів Баркера в двійковий код здійснюється аналогічно. При появі команди керування на четвертому керуючому вході 28 співпроцесора, одночасна поява одиниць на входах 27 і 28 третього елемента "І" 26 забезпечує появу одиниці на виході 25, яка надходить на вхід 24 і дозволяє роботу дешифратора 23, на одному з виходів якого з'являється сигнал, який, пройшовши відповідну групу елементів "АБО" 11, з'являється на відповідній кодовій шині шифратора 12, одиниці вихідного коду корегуючої константи надходять на лічильні входи тригерів вхідного регістра 1 і змінюють їх з одного стану в інший. На виході вхідного регістра 1 з'являється двійковий код, який надходить на 3 UA 111459 C2 5 10 15 20 25 30 35 інформаційні входи блока МДП-ключів 22, інформаційний код з'явиться на виході блока МДПключів 22 після приходу керуючого сигналу a(t+Δt) з прямого виходу керуючого тригеру 7 через інвертор 20 і диференціюючого вузла 21. При цьому роботу дешифраторів 2, 13 та 29 не дозволено завдяки відсутності керуючих сигналів на входах 18, 19 і 34. Отже процес в співпроцесорі проходить тільки один, тобто - перетворення однополярного коду Баркера в двійковий код. Робота пристрою в режимі перетворення комбінацій завадостійкого коду у відповідні коди значення функції синуса здійснюється аналогічно. При появі команди керування на п'ятому керуючому вході 34 співпроцесора, одночасна поява одиниць на входах 33 і 34 четвертого елемента "І" 30 забезпечує появу одиниці на виході 32, яка надходить на вхід 31 і дозволяє роботу дешифратора 29, на одному з виходів якого з'являється сигнал, який, пройшовши відповідну групу елементів "АБО" 11, з'являється на відповідній кодовій шині шифратора 12, одиниці вихідного коду корегуючої константи надходять на лічильні входи тригерів вхідного регістра 1 і змінюють їх з одного стану в інший. На виході вхідного регістра 1 з'являється двійковий код, який надходить на інформаційні входи блока МДП-ключів 22, інформаційний код з'явиться на виході блока МДП-ключів 22 після приходу керуючого сигналу a(t+Δt) з прямого виходу керуючого тригеру 7 через інвертор 20 і диференціюючого вузла 21. При цьому роботу дешифраторів 2, 13 та 23 не дозволено завдяки відсутності керуючих сигналів на входах 18, 19 і 28. Отже процес в співпроцесорі проходить тільки один, тобто - перетворення комбінацій коду X у відповідні коди значення функції синуса. Отже, запропонований багатофункціональний таблично-логічний співпроцесор має розширені функціональні можливості і має додаткову функцію на відміну від прототипу, тобто він має можливість роботи в режимі або перетворювача коду Грея в двійковий код, або в режимі перетворювача двійкового коду в код Грея, або в режимі перетворювача однополярного коду Баркера в двійковий код, або в режимі перетворення комбінацій завадостійкого коду у відповідні коди значення функції синуса. Джерела інформації: 1. Пат. 40178, Україна, МПК G06F 5/00. Перетворювач коду Грея в двійковий код і навпаки/ Лукашенко В.М., Корпань Я.В., Лукашенко А.Г., Рудаков К.С., Лукашенко В.А., Юпин Р.Є.; заявник Черкаський державний технологічний університет. - № u200813020; заявл. 10.11.08; опубл. 25.03.09, Бюл. № 6. 2. Пат. 89784 U Україна, МПК (2014.01) G06F 5/00. Таблично-логічний перетворювач кодів/ В.М. Лукашенко, І.А. Зубко, А.Г. Лукашенко, В.А. Лукашенко, М.В. Чичужко, Д.А. Лукашенко; заявник та власник В.М. Лукашенко. - № u201315042; заявл. 23.12.2013; опубл. 25.04.2014, Бюл. № 8. (Прототип). ФОРМУЛА ВИНАХОДУ 40 45 50 55 60 Багатофункціональний таблично-логічний співпроцесор, що містить вхідний регістр, виконаний на тригерах з лічильними та інформаційними входами, дешифратор коду Грея, інформаційні входи якого підключені до розрядних виходів вхідного регістра, а вхід керування з'єднаний з виходом першого елемента "І", керуючий вхід якого з'єднаний з інверсним виходом керуючого тригера, прямий вихід якого підключений до керуючого входу вхідного регістра, вхід керуючого тригера є першим керуючим входом співпроцесора, а вхід скидання підключений до входу скидання співпроцесора, виходи дешифратора коду Грея через групу елементів "АБО" підключені до відповідних входів шифратора корегуючих констант, виходи якого з'єднані з лічильними входами вхідного регістра, розрядні виходи якого підключені до інформаційних входів дешифратора двійкового коду, виходи якого підключені до відповідних входів групи елементів "АБО", керуючий вхід дешифратора двійкового коду з'єднаний з виходом другого елемента "І", керуючий вхід якого з'єднаний з інверсним виходом керуючого тригера, інформаційний вхід першого елемента "І" є другим керуючим входом для коду Грея, інформаційний вхід другого елемента "І" є третім керуючим входом для двійкових кодів, крім того, прямий вихід тригера з'єднаний з входом інвертора, вихід якого підключений до входу диференціюючого ланцюга, вихід якого підключений до керуючого входу блока МДП-ключів, інформаційні входи якого з'єднані з відповідними виходами вхідного регістра, інформаційні виходи блока МДП-ключів з'єднані з інформаційними входами вхідного регістру і є "входом/виходом" співпроцесора, дешифратор однополярного коду Баркера, до інформаційних входів якого підключені розрядні виходи вхідного регістра, а виходи дешифратора 4 UA 111459 C2 5 10 однополярного коду Баркера підключені до відповідних входів групи елементів "АБО", керуючий вхід дешифратора однополярного коду Баркера з'єднаний з виходом третього елемента "І", керуючий вхід, який з'єднаний з інверсним виходом керуючого тригера, інформаційний вхід третього елемента "І" є четвертим керуючим входом для однополярного коду Баркера, який відрізняється тим, що додатково введені дешифратор значень синуса, четвертий керуючий елемент "І", при цьому дешифратор значень синуса інформаційними входами з'єднаний з відповідними розрядними виходами вхідного регістра, а виходи дешифратора значень синуса підключені до відповідних входів групи елементів "АБО", керуючий вхід дешифратора значень синуса з'єднаний з виходом четвертого елемента "І", перший вхід якого є керуючим входом, що з'єднаний з інверсним виходом керуючого тригера, другий вхід четвертого елемента "І" підключений до інформаційного входу і є п'ятим керуючим входом для функції sin(x) багатофункціонального таблично-логічного співпроцесора. Комп’ютерна верстка Л. Литвиненко Державна служба інтелектуальної власності України, вул. Василя Липківського, 45, м. Київ, МСП, 03680, Україна ДП “Український інститут інтелектуальної власності”, вул. Глазунова, 1, м. Київ – 42, 01601 5

ДивитисяДодаткова інформація

Назва патенту англійськоюMulti-functional table-logic coprocessor

Автори англійськоюLukashenko Volodymyr Andriiovych, Lukashenko Andrii Germanovych, Zubko Ihor Antoliiovych, Lukashenko Dmytro Andriiovych, Lukashenko Valentyna Maksymivna

Назва патенту російськоюМногофункциональный таблично- логический сопроцессор

Автори російськоюЛукашенко Владимир Андреевич, Лукашенко Андрей Германович, Зубко Игорь Анатольевич, Лукашенко Дмитрий Андреевич, Лукашенко Валентина Максимовна

МПК / Мітки

МПК: G06F 9/00, G06F 5/00, H03K 19/00, G06F 7/00

Мітки: співпроцесор, багатофункціональний, таблично-логічний

Код посилання

<a href="https://ua.patents.su/7-111459-bagatofunkcionalnijj-tablichno-logichnijj-spivprocesor.html" target="_blank" rel="follow" title="База патентів України">Багатофункціональний таблично-логічний співпроцесор</a>

Попередній патент: Спосіб комплексного лікування хворих на генералізований пародонтит ii-iii ступеня

Наступний патент: Спосіб запобігання спробі здійснення несанкціонованого доступу до вантажу тентованого транспортного засобу та пристрій для його здійснення

Випадковий патент: Спосіб схрещування сафлору красильного