Система обробки сигналів цифрової антенної решітки

Номер патенту: 119000

Опубліковано: 11.09.2017

Автори: Шраєв Дмитро Валентинович, Волощук Ігор Вікторович, Солощев Олег Миколайович, Корольов Микола Олексійович, Слюсар Вадим Іванович, Шацман Леонід Георгієвич, Нікітін Микола Михайлович

Формула / Реферат

1. Система обробки сигналів цифрової антенної решітки, до складу якої входять багатоканальні цифрові модулі (БЦМ), синхронізатор, процесорний модуль, причому тактові виходи синхронізатора підключені до тактових входів БЦМ, яка відрізняється тим, що виходи БЦМ підключені до входів процесорного модуля за допомогою інтерфейсів Ethernet (10, 40 або 100 Гбіт/с).

2. Система обробки сигналів цифрової антенної решітки за п. 1, яка відрізняється тим, що виходи БЦМ підключені до входів процесорного модуля за допомогою інтерфейсів Ethernet (10, 40 або 100 Гбіт/с) через додатково введений Ethernet-комутатор, один з Ethernet-виходів якого підключений до додатково введеного Ethemet-входу синхронізатора.

3. Система обробки сигналів цифрової антенної решітки за будь-яким з пп. 1, 2, яка відрізняється тим, що для розведення інтерфейсів Ethernet (10, 40 або 100 Гбіт/с) та тактових сигналів синхронізатора застосовують додатково введену об'єднавчу (крос) плату.

4. Система обробки сигналів цифрової антенної решітки за будь-яким з пп. 1-3, яка відрізняється тим, що першу частину багатоканальних цифрових модулів використовують для прийому сигналів, а другу - для формування аналогових сигналів на передачу.

Текст

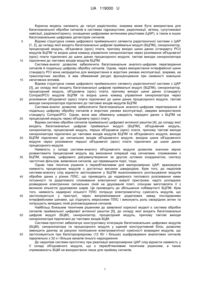

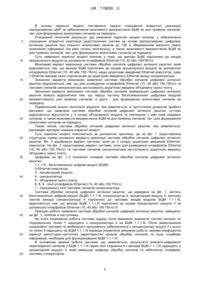

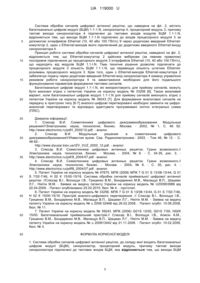

Реферат: Система обробки сигналів цифрової антенної решітки, до складу якої входять багатоканальні цифрові модулі (БЦМ), синхронізатор, процесорний модуль, причому тактові виходи синхронізатора підключені до тактових входів БЦМ. Виходи БЦМ підключені до входів процесорного модуля за допомогою інтерфейсів Ethernet (10, 40 або 100 Гбіт/с). UA 119000 U (12) UA 119000 U UA 119000 U 5 10 15 20 25 30 35 40 45 50 55 Корисна модель належить до галузі радіотехніки, зокрема може бути використана для багатоканальної обробки сигналів в системах гідроакустики, радіолокації, зв'язку, супутникової навігації, радіомоніторингу, оснащених цифровими антенними решітками (ЦАР), а також в інших багатоканальних цифрових детекторах сигналів. Відома структурна схема цифрового приймального сегмента радіотехнічної системи з ЦАР [1, 2], до складу якої входять багатоканальні цифрові приймальні модулі (БЦПМ), синхронізатор, процесорний модуль, об'єднавча (крос) плата, причому вихідні шини даних (стандарту РСІ) модулів БЦПМ та вхідна шина команд управління синхронізатора через рознімання об'єднавчої (крос) плати підключені до шини даних процесорного модуля, тактові виходи синхронізатора підключені до тактових входів модулів БЦПМ. Система-аналог дозволяє забезпечити багатоканальне аналого-цифрове перетворення сигналів й подальшу цифрову обробку сигналів. Однак, через використання інтерфейсної шини стандарту РСІ вона непридатна для використання в жорстких умовах експлуатації, зокрема, на транспортних засобах, й має обмежений ресурс функціонування при наявності зовнішніх негативних впливів. Відома структурна схема цифрового приймального сегменту радіотехнічної системи з ЦАР [3], до складу якої входять багатоканальні цифрові приймальні модулі (БЦПМ), синхронізатор, процесорний модуль, об'єднавча (крос) плата, причому вихідні шини даних (стандарту CompactPCI) модулів БЦПМ та вхідна шина команд управління синхронізатора через рознімання об'єднавчої (крос) плати підключені до шини даних процесорного модуля, тактові виходи синхронізатора підключені до тактових входів модулів БЦПМ. Система-аналог дозволяє забезпечити багатоканальне аналого-цифрове перетворення й подальшу цифрову обробку сигналів в жорстких умовах експлуатації, завдяки використанню стандарту CompactPCI. Однак, вона має обмежену швидкість передачі даних з БЦПМ на процесорний модуль через об'єднавчу (крос) плату. Відома система обробки сигналів приймальної цифрової антенної решітки [4], до складу якої входять багатоканальні цифрові приймальні модулі (БЦПМ), об'єднавчий модуль, синхронізатор, процесорний модуль, перша об'єднавча (крос) плата, причому тактові виходи синхронізатора підключені до тактових входів модулів БЦПМ та об'єднавчого модуля, виходи БЦПМ підключені до сигнальних входів об'єднавчого модуля, вихідна шина об'єднавчого модуля через рознімання першої об'єднавчої (крос) плати підключені до шини даних процесорного модуля. Наявність у складі системи-аналогу об'єднавчого модуля дозволяє значною мірою розвантажити процесорний модуль від виконання операцій над сигналами, отриманими з БЦПМ, зокрема, цифрового діаграмоутворення за другою кутовою координатою, синтезу частотних фільтрів, виявлення сигналів, що перевищили поріг, тощо. Однак таке технічне рішення є переобтяжливим для малорозмірних ЦАР, враховуючи наявність процесорних модулів з достатньо високою швидкодією. Крім того, до недоліків системи-аналогу слід віднести застосування у БЦПМ ешелонованого розташування модулів обробки даних у різних ПЛІС, що призводить до надмірного теплового розсіювання ними потужності та додаткового споживання електричної енергії пристроєм, надто ускладнює розведення електричних сигнальних ліній на друкованій платі, спонукає виготовляти її з великою кількістю друкованих шарів. Це призводить до збільшення собівартості БЦПМ. Крім того, наявність надмірної кількості ПЛІС погіршує електромагнітну сумісність модулів, що застосовуються у пристрої, через випромінювання додаткових завад послідовними інтерфейсними шинами, що з'єднують мікросхеми ПЛІС і виконують роль своєрідних антен та погіршують імпеданс ліній розповсюдження сигналів. Найбільш близьким технічним рішенням до заявленої корисної моделі є система обробки сигналів приймальної цифрової антенної решітки [5], до складу якої входять багатоканальні цифрові модулі (БЦМ), синхронізатор, процесорний модуль, причому тактові виходи синхронізатора підключені до тактових входів БЦМ. Система-прототип забезпечує конструктивну інтеграцію багатоканальних цифрових модулів (БЦМ), синхронізатора та процесорного модуля у єдиний конструктивний блок, дозволяє зменшити джитер за рахунок поліпшення електромагнітної сумісності всередині модулів, що застосовуються при багаторозрядному (12 біт і більше) оцифровуванні аналогових сигналів паралельно з 32-х і більше каналів їхнього надходження. До недоліків системи-прототипу при реалізації малорозмірних ЦАР слід віднести наявність у її складі об'єднавчого модуля, що є переобтяжливим технічним рішенням, а також спрямованість БЦМ на використання лише для прийому сигналів. 1 UA 119000 U 5 10 15 20 25 30 35 40 45 50 55 60 В основу корисної моделі поставлена задача спрощення апаратної реалізації малорозмірних ЦАР та забезпечення можливості використання БЦМ як для прийому сигналів, так і для формування аналогових сигналів на передачу. Очікуваний технічний результат від заявленої корисної моделі полягає у забезпеченні спрощення апаратної реалізації радіотехнічних систем на основі малорозмірних цифрових антенних решіток при кількості аналогових каналів до 128 зі збереженням високого темпу оновлення інформації (на рівні сотень мілісекунд), а також можливості використання БЦМ як для прийому сигналів, так і для формування аналогових сигналів на передачу. Суть заявленої корисної моделі полягає у тому, що виходи БЦМ підключені до входів процесорного модуля за допомогою інтерфейсів Ethernet (10, 40 або 100Гбіт/с). Можливий варіант виконання системи обробки сигналів цифрової антенної решітки, який відрізняється тим, що виходи БЦМ підключені до входів процесорного модуля за допомогою інтерфейсів Ethernet (10, 40 або 100 Гбіт/с) через додатково введений Ethernet-комутатор, один з Ethernet-виходів якого підключений до додатково введеного Ethernet-входу синхронізатора. Зазначені варіанти виконання заявленої системи обробки сигналів цифрової антенної решітки відрізняються тим, що для розведення інтерфейсів Ethernet (10, 40 або 100 Гбіт/с) та тактових сигналів синхронізатора застосовують додатково введену об'єднавчу (крос) плату. Зазначені варіанти виконання системи обробки сигналів приймальної цифрової антенної решітки можуть відрізнятися тим, що першу частину багатоканальних цифрових модулів використовують для прийому сигналів, а другу - для формування аналогових сигналів на передачу. Порівняльний аналіз технічного рішення, яке заявляється, із прототипом дозволяє зробити висновок, що заявлена система обробки сигналів цифрової антенної решітки суттєво відрізняється відсутністю у її складі об'єднавчого модуля та пов'язаних з ним ліній передачі сигналів, а також можливістю використання БЦМ як для прийому сигналів, так і для формування аналогових сигналів на передачу. Таким чином, система обробки сигналів цифрової антенної решітки, яка заявляється, відповідає критерію новизни корисної моделі. Суть корисної моделі пояснюється за допомогою креслень, де на фіг. 1 представлена структурна схема основного варіанту реалізації системи обробки сигналів цифрової антенної решітки. Фіг. 2 відображує варіант системи, коли до її складу додатково введений Ethernetкомутатор. На фіг. 3 представлено варіант системи, коли для розведення інтерфейсів Ethernet (10, 40 або 100 Гбіт/с) та тактових сигналів синхронізатора застосовують додатково введену об'єднавчу (крос) плату. Цифрами на фіг. 1-3 позначені складові системи обробки сигналів цифрової антенної решітки: 1.1-1.N - багатоканальні цифрові модулі (БЦМ); 2-Ethernet-комутатор; 3 - процесорний модуль; 4 - синхронізатор; 5 - об'єднавча (крос) плата; 6, 8, 9 - лінії інтерфейсів Ethernet (10, 40 або 100 Гбіт/с). 7 - з'єднувальні лінії тактових сигналів синхронізатора. Система обробки сигналів цифрової антенної решітки, що наведена на фіг. 1, містить багатоканальні цифрові модулі (БЦМ) 1.1-1.N, синхронізатор 4, процесорний модуль 3, причому тактові виходи синхронізатора 4 підключені до тактових входів модулів БЦМ 1.1-1.N, відрізняється тим, що виходи БЦМ 1.1-1.N підключені до входів процесорного модуля 3 за допомогою інтерфейсів Ethernet (10, 40 або 100 Гбіт/с) 9. Принцип роботи заявленої системи обробки сигналів цифрової антенної решітки, наведеної на фіг. 1, полягає в наступному. На етапі ініціювання роботи системи одразу після вмикання живлення тактові сигнали по з'єднувальних лініях 7 надходять з синхронізатора 4 на БЦМ 1.1-1.N. Після завантаження операційної системи та необхідного програмного забезпечення у процесорному модулі 3 з нього по лініях 9 надходять на БЦМ 1.1-1.N команди управління режимом роботи, масиви коефіцієнтів корекції амплітудно-частотниххарактеристик каналів обробки сигналів та інша службова інформація, необхідна для функціонування БЦМ 1.1-1.N. В основному режимі роботи системи, що заявляється, результати аналого-цифрового перетворення сигналів у БЦМ 1.1-1.N через лінії з'єднання 9 з виходів БЦМ 1.1-1.N надходять у процесорний модуль 3, який завершує цифрову обробку сигналів та забезпечує інтерфейс системи з оператором. 2 UA 119000 U 5 10 15 20 25 30 35 40 45 50 55 Система обробки сигналів цифрової антенної решітки, що наведена на фіг. 2, містить багатоканальні цифрові модулі (БЦМ) 1.1-1.N, синхронізатор 4, процесорний модуль 3, причому тактові виходи синхронізатора 4 підключені до тактових входів модулів БЦМ 1.1-1.N, відрізняється тим, що виходи БЦМ 1.1-1.N підключені до входів процесорного модуля 3 за допомогою інтерфейсів Ethernet (10, 40 або 100 Гбіт/с) 9 через додатково введений Ethernetкомутатор 2, один з Ethernet-виходів якого підключений до додатково введеного Ethernet-входу синхронізатора 4. Принцип роботи системи обробки сигналів цифрової антенної решітки, наведеної на фіг. 2, відрізняється тим, що Ethernet-комутатор 2 здійснює вибіркове (за певним правилом) послідовне підключення до процесорного модуля 3 інтерфейсів Ethernet (10, 40 або 100 Гбіт/с), що надходять від модулів БЦМ 1.1-I.N. Таке технічне рішення дозволяє підключати до процесорного модуля 3 кількість БЦМ 1.1-1.N, що перевищує кількість штатних Ethernetрознімань процесорного модуля 3. Крім того, один з Ethernet-виходів Ethernet-комутатора 2 забезпечує подачу через додатково введений Ethernet-вхід синхронізатора 4 команд управління режимом роботи синхронізатора 4 та завантаження необхідних для його подальшого функціонування параметрів формування тактових сигналів. Багатоканальні цифрові модулі 1.1-1.N, які використовують для прийому сигналів, можуть бути виконані згідно з патентом України на корисну модель № 33256 [6]. Також можливий варіант, коли багатоканальні цифрові модулі 1.1-1.N для прийому сигналів виконують згідно з патентом України на корисну модель № 39243 [7]. Для формування аналогових сигналів на передачу в пристроях типу [6-7] аналого-цифрові перетворювачі необхідно замінити на цифроаналогові перетворювачі та відповідно адаптувати програмовані логічні інтегральні схеми (ПЛІС). Джерела інформації: 1. Слюсар В.И. Схемотехника цифрового диаграммообразования. Модульные решенияУ/Электроника: наука, технология, бизнес. -Москва. - 2002, № 1, С. 46 52. http://www.electronics.ru/pdf/l_2002/12.pdf. - аналог. 2. Слюсар В.И. Модульные решения в схемотехнике цифрового диаграммообразованияУ/Известия вузов. Сер. Радиоэлектроника.- 2003. - Том 46, № 12. - С. 48-62.http://www.slyusar.kiev.ua/IZV_VUZ_2003_12.pdf. - аналог. 3. Слюсар В.И. Схемотехника цифровых антенных решеток. Грани возможного.// Электроника: наука, технология, бизнес. - Москва. - 2004, № 8. - С. 34-35, рис. 3. http://www.electronics.ru/pdf/8_2004/07.pdf. -аналог. 4. Слюсар В.И. Схемотехника цифровых антенных решеток. Грани возможного.// Электроника: наука, технология, бизнес. - Москва. - 2004, № 8. - С. 35, рис. 4. http://www.electronics.ru/pdff8_2004/07.pdf. -аналог. 5. Патент України на корисну модель № 47675. МПК (2009) МПК 7 G 01 S 13/08-13/44, G 01 S 7/02-7/46, Н 02 К 15/00-15/16. Система обробки сигналів приймальної цифрової антенної решітки. //Слюсар В.І., Волощук І.В., Гриценко В.М., Бондаренко М.В., Малащук В.П., Шацман Л.Г., Нікітін М.М. - Заявка на видачу патенту України на корисну модель № U200903986 від 22.04.2009. - Патент опубліковано 25.02.2010, бюл. № 4. - прототип. 6. Патент України на корисну модель № 33256. МПК 7 G 01 S 13/08-13/44, G 01 S 7/02-7/46, Н 02 К 15/00-15/16. Пристрій аналого-цифрового перетворення. // Слюсар В.І., Волощук І.В., Гриценко В.М., Бондаренко М.В., Малащук В.П., Шацман Л.Г., Нікітін М.М. - Заявка на видачу патенту України на корисну модель № u 2008 02466 від 26.02.2008. - Патент опубл. 10.06.2008, бюл. № 11. 7. Патент України на корисну модель № 39243. МПК (2006) G01S 13/00, G01S 7/00, H02K 15/00. Багатоканальний приймальний пристрій.// Слюсар В.І., Волощук І.В., Алесін A.M., Гриценко В.М., Бондаренко М.В., Малащук В.П., Шацман Л.Г., Нікітін М.М. - Заявка на видачу патенту України на корисну модель № u 200813442 від 21.11.2008. - Патент опубл. 10.02.2009, бюл. № 3. ФОРМУЛА КОРИСНОЇ МОДЕЛІ 1. Система обробки сигналів цифрової антенної решітки, до складу якої входять багатоканальні цифрові модулі (БЦМ), синхронізатор, процесорний модуль, причому тактові виходи синхронізатора підключені до тактових входів БЦМ, яка відрізняється тим, що виходи БЦМ 3 UA 119000 U 5 10 підключені до входів процесорного модуля за допомогою інтерфейсів Ethernet (10, 40 або 100 Гбіт/с). 2. Система обробки сигналів цифрової антенної решітки за п. 1, яка відрізняється тим, що виходи БЦМ підключені до входів процесорного модуля за допомогою інтерфейсів Ethernet (10, 40 або 100 Гбіт/с) через додатково введений Ethernet-комутатор, один з Ethernet-виходів якого підключений до додатково введеного Ethemet-входу синхронізатора. 3. Система обробки сигналів цифрової антенної решітки за будь-яким з пп. 1, 2, яка відрізняється тим, що для розведення інтерфейсів Ethernet (10, 40 або 100 Гбіт/с) та тактових сигналів синхронізатора застосовують додатково введену об'єднавчу (крос) плату. 4. Система обробки сигналів цифрової антенної решітки за будь-яким з пп. 1-3, яка відрізняється тим, що першу частину багатоканальних цифрових модулів використовують для прийому сигналів, а другу - для формування аналогових сигналів на передачу. 4 UA 119000 U Комп’ютерна верстка М. Мацело Міністерство економічного розвитку і торгівлі України, вул. М. Грушевського, 12/2, м. Київ, 01008, Україна ДП “Український інститут інтелектуальної власності”, вул. Глазунова, 1, м. Київ – 42, 01601 5

ДивитисяДодаткова інформація

МПК / Мітки

МПК: G01S 13/00, G01S 7/00

Мітки: сигналів, решітки, обробки, цифрової, система, антенної

Код посилання

<a href="https://ua.patents.su/7-119000-sistema-obrobki-signaliv-cifrovo-antenno-reshitki.html" target="_blank" rel="follow" title="База патентів України">Система обробки сигналів цифрової антенної решітки</a>

Попередній патент: Спосіб лікування пацієнтів з акне середнього та тяжкого ступеня тяжкості

Наступний патент: Тара з гофрованого картону для транспортування та зберігання цвяхів

Випадковий патент: Монорейкова транспортна система