Швидкодіючий помножувач

Номер патенту: 47521

Опубліковано: 15.07.2002

Формула / Реферат

Швидкодіючий помножувач, що має m (m = 16n2, n = 2 t, t = 1, 2, . . .) елементів І, який відрізняється тим, що в нього введені: блок суматорів сум першого рангу, блок суматорів сум другого рангу, блок суматорів результуючих, блок суматорів переносів першого рангу, блок суматорів переносів другого рангу, блок суматорів переносів третього рангу, перша та друга шини, при цьому виходи елементів І об'єднані в групи по 4n та виходи кожної групи з'єднані з відповідними 4n входами блока суматорів сум першого рангу, перша група виходів розрядів сум S якого з'єднана з відповідними розрядами входу блока суматорів сум другого рангу, друга група виходів розрядів переносів Р1 блока суматорів сум першого рангу з'єднана з відповідними розрядами першого входу блока суматорів переносів другого рангу, третя група виходів розрядів переносів Р2 блока суматорів сум першого рангу з'єднана з відповідними розрядами входу блока суматорів переносів першого рангу, перша група виходів розрядів сум S та друга група виходів розрядів переносів Р якого з'єднані відповідно з відповідними розрядами другого та третього входів блока суматорів переносів другого рангу, перша група виходів розрядів сум S та друга група виходів розрядів переносів Р якого з'єднані відповідно з відповідними розрядами першого та другого входів блока суматорів переносів третього рангу, перша група виходів розрядів сум S та друга група виходів розрядів переносів Р якого з'єднані відповідно з відповідними розрядами третього та четвертого входів блока суматорів результуючих, перша група виходів розрядів сум S та друга група виходів розрядів переносів Р блока суматорів сум другого рангу з'єднані відповідно з відповідними розрядами першого та другого входів блока суматорів результуючих, вхід пристрою через виходи першої шини з'єднаний відповідно з першими входами, а через виходи другої шини – відповідно з другими входами елементів І, розряди виходу пристрою з’єднані з відповідними розрядами виходу блока суматорів результуючих.

Текст

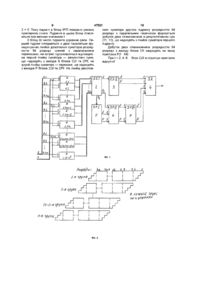

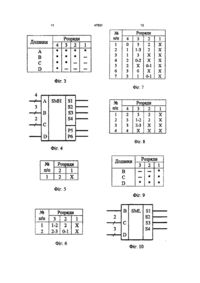

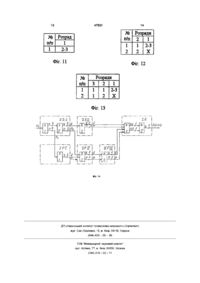

Швидкодіючий помножувач, що має m (m = 16n2, n = 2\ t = 1, 2, ) елементів І, який відрізняється тим, що в нього введені блок суматорів сум першого рангу, блок суматорів сум другого рангу, блок суматорів результуючих, блок суматорів переносів першого рангу, блок суматорів переносів другого рангу, блок суматорів переносів третього рангу, перша та друга шини, при цьому виходи елементів І об'єднані в групи по 4п та виходи кожної групи з'єднані з ВІДПОВІДНИМИ 4П входами блока суматорів сум першого рангу, перша група виходів розрядів сум S якого з'єднана з ВІДПОВІДНИМИ розрядами входу блока суматорів сум другого рангу, друга група виходів розрядів переносів Рі блока суматорів сум першого рангу з'єднана з ВІДПОВІДНИМИ розрядами першого входу блока суматорів переносів другого рангу, третя група виходів розрядів переносів P-z блока суматорів сум першого рангу з'єднана з ВІДПОВІДНИМИ розрядами входу блока суматорів переносів першого рангу, перша група виходів розрядів сум S та друга група виходів розрядів переносів Р якого з'єднані ВІДПОВІДНО з ВІДПОВІДНИМИ розрядами дру гого та третього входів блока суматорів переносів другого рангу, перша група виходів розрядів сум S та друга група виходів розрядів переносів Р якого з'єднані ВІДПОВІДНО з ВІДПОВІДНИМИ розрядами першого та другого входів блока суматорів переносів третього рангу, перша група виходів розрядів сум S та друга група виходів розрядів переносів Р якого з'єднані ВІДПОВІДНО З ВІДПОВІДНИМИ розрядами третього та четвертого входів блока суматорів результуючих, перша група виходів розрядів сум S та друга група виходів розрядів переносів Р блока суматорів сум другого рангу з'єднані ВІДПОВІДНО З ВІДПОВІДНИМИ розрядами першого та другого входів блока суматорів результуючих, вхід пристрою через виходи першої шини з'єднаний ВІДПОВІДНО З першими входами, а через виходи другої шини ВІДПОВІДНО з другими входами елементів І, розряди виходу пристрою з'єднані з ВІДПОВІДНИМИ розрядами виходу блока суматорів результуючих О ю Запропонований винахід відноситься до області обчислювальної техніки та може бути використаним в цифрових пристроях та системах цифрової обробки сигналів Відомий пристрій для перемноження (а с СССР № 1206773, кл G06F 7152, БИ № 3, 1986 г), що вміщує регістр множного та регістр множника, комутатор, накопичуючий суматор, вузол керування комутатором, інформаційні входи розрядів першої, другої та третьої груп комутатора з'єднані з прямими виходами ВІДПОВІДНИХ розрядів регістра множного, прямими виходами розрядів регістра множного із зсувом на один розряд вліво та з інверсними виходами ВІДПОВІДНИХ розрядів регістра множника, виходи комутатора приєднані до входів розрядів накопичуючого суматора, перший, другий та третій керуючі входи комутатора з єднані ВІДПОВІДНО з першим, другим та третім виходами вузла керування комутатором, виходи двох молодших розрядів накопичуючого суматора з'єднані з входами ВІДПОВІДНО двох старших розрядів регістра множника, виходи двох молодших розрядів котрого та вихід знакового розряда накопичуючого суматора з'єднані з входами вузла керування комутатором, третій вихід якого приєднано до входу переносу накопичуючого суматора, вузол визначення знаку операції, що вміщує елемент І та елемент АБО, а накопичуючий суматор вміщує регістр та комбінований суматор, виходи розрядів котрого з'єднані із зсувом на два розряди вправо з входами розрядів регістра накопичуючого суматора, вихід знакового розряду якого є виходом знакового 47521 розряду накопичую чого суматора та приєднаний до першого входу елемента І вузла визначення знаку операцій, перша група входів комбінаційного суматора є входом розрядів накопичуючого суматора, друга група входів комбінаційного суматора з'єднана з виходами розрядів накопичуючого суматора, другий та третій входи елемента І вузла визначення знака операції з'єднані з виходами молодших розрядів регістра множника, а вихід приєднано до першого входу елемента АБО вузла визначення знака операції, другий вхід котрого з'єднаний з третім виходом вузла керування комутатором, вихід елемента АБО вузла визначення знака операції приєднано до входу знакового розряду регістра накопичуючого суматораг вхід переносу комбінаційного суматора є входом переносу накопичуючого суматора, виходи розрядів регістра ~ множника з'єднані зсувом на два розряди вправо з входами розрядів регістра множника Перемноження чисел за допомогою цього пристрою виконується програмно-апаратним способом в декілька тактів і, отже, у цього пристрою низька швидкодія Найбільш близьким за технічною суттю та досягаемому результату до пропонуємого винаходу є пристрій для перемноження двійкових чисел (а с СССР № 1156066, кл G06F 7/52, БИ №18,1985 г), що містить m (m = 16n2, n = 2f, t = 1, 2, ) тривходових суматорів, m елементів затримки та m елементів І, при цьому перші входи елементів І з'єднані з входом множного пристрою, другий вхід і-го елемента І з'єднаний з входом і-го розряду множника пристрою ВІДПОВІДНО (І = 1, 2, , m), a виходи елементів і з'єднані з першими входами ВІДПОВІДНИХ тривходових суматорів, другі входи котрих, крім останнього тривходового суматора, з'єднані з виходами ВІДПОВІДНИХ елементів затримки, вхід і-го елемента затримки, крім останнього, з'єднано з виходом суми (і + 1)-го тривходового суматора, вхід m-ro елемента затримки з'єднано з виходом порозрядного переносу m-ro тривходового суматора, вихід суми першого тривходового суматора з'єднано з виходом пристрою, вхід логічного нуля пристрою з'єднано з третім входом першого тривходового суматора, вихід порозрядного переносу j-ro тривходового суматора Q = 1, 2, , m - 1) з'єднано з третім входом Q + 1)-го тривходового суматора, вихід m-го елемента затримки з'єднаний з другим входом m-ro тривходового суматора Недоліком прототипу є застосування в його схемі лише однорозрядних тривходових суматорів з послідовним переносом із розряду в розряд, що приводить до низької швидкодії В основу винаходу поставлено задачу створення такого швидкодіючого помножувача, в якому шляхом введення нових елементів та взаємозв'язків зменшується число рангів, що приводить до підвищення швидкодії Поставлена задача розв'язується тим, що в пристрій, що має m (m = 16n2, n = 2f, t = 1, 2, ) елементів І, ВІДПОВІДНО до винаходу введені блок суматорів сум першого рангу, блок суматорів сум другого рангу, блок суматорів результуючих, блок суматорів переносів першого рангу, блок суматорів переносів другого рангу, блок суматорів переносів третього рангу, перша та друга шини, при цьому виходи елементів І об'єднані в групи по 4п та виходи кожної групи з'єднані з ВІДПОВІДНИМИ 4П входами блока суматорів сум першого рангу, перша група виходів розрядів сум S котрого з'єднана з ВІДПОВІДНИМИ розрядами входу блока суматорів сум другого рангу, друга група виходів розрядів переносів Рі блока суматорів сум першого рангу з'єднана з ВІДПОВІДНИМИ розрядами першого входу блока суматорів переносів другого рангу, третя група виходів розрядів переносів P-z блока суматорів сум першого рангу з'єднана з ВІДПОВІДНИМИ розрядами входу блока суматорів переносів першого рангу, перша група виходів розрядів сум S та друга група виходів розрядів переносів Р котрого з'єднані ВІДПОВІДНО з ВІДПОВІДНИМИ розрядами дру гого та третього входів блока суматорів переносів другого рангу, перша група виходів розрядів сум S та друга група виходів розрядів переносів Р котрого з'єднані ВІДПОВІДНО з ВІДПОВІДНИМИ розрядами першого та другого входів блока суматорів переносів третього рангу, перша група виходів розрядів сум S та друга група виходів розрядів переносів Р котрого з'єднані ВІДПОВІДНО З ВІДПОВІДНИМИ розрядами третього та четвертого входів блока суматорів результуючих, перша група виходів розрядів сум S та друга група виходів розрядів переносів Р блока суматорів сум другого рангу з'єднані ВІДПОВІДНО з ВІДПОВІДНИМИ розрядами першого та другого входів блока суматорів результуючих, вхід пристрою крізь виходи першої шини з'єднаний ВІДПОВІДНО з першими входами, а крізь виходи другої шини — ВІДПОВІДНО з другими входами елементів І, розряди виходу пристрою з'єднані з ВІДПОВІДНИМИ розрядами виходу блока суматорів результуючих В даному пристрої на основі введених нових елементів та взаємозв'язків в усіх блоках, крім останнього блока суматорів результуючих, виконується нарізне підсумовування значень сум та одержаних при підсумовуванні переносів на базі швидкодіючих три і чотирисловних чотирихрозрядних суматорів, що приводить до скорочення рангів та підвищення швидкодії Суть винаходу пояснюється наступними фігурами фіг 1 — структурна схема швидкодіючого помножувача, фіг 2 — розбиття паралелограму часткових добутків, фіг 3 — трикутня підматриця для суматора SMH, фіг 4 — функціональне позначення суматора SMH, фіг 5 —таблиця переносу РЗ суматора SMH, фіг 6 —таблиця переносу Р4 суматора SMH, фіг 7 —таблиця переносу Р5 суматора SMH, фіг 8 —таблиця переносу Р6 суматора SMH, фіг 9 — трикутня підматриця для суматора SML, фіг 10 — функціональне позначення суматора SML, фіг 11 —таблиця переносу Р2 суматора SML, фіг 12 —таблиця переносу РЗ суматора SML, фіг 13 —таблиця переносу Р4 суматора SML, фіг 14 — структура швидкодіючого помножувача 32x32 47521 Схема пристрою, що заявляється, приведена на фіг 1 Тут позначено 1,1, 1,2, , 1,16n 2 — [ елементи І (n = 2 , t = 1, 2, ), 2 — блок суматорів сум першого рангу SEN, 3 — блок суматорів сум другого рангу SSI, 4 — блок суматорів результуючих SR, 5 — блок суматорів переносів першого рангу ЕРІ, 6 — блок суматорів переносів другого рангу SSPII, 7 — блок суматорів переносів третього рангу SPIN, 8 — перша шина 4п-розрядного множного А, 9 — друга шина 4п-розрядного множника В Перелічені компоненти схеми з'єднані наступним чином Виходи елементів 1 1 1 — 1 16п 2 об'єднані в групи по 4п та виходи кожної групи з'єднані з ВІДПОВІДНИМИ 4п входами блока 2, перша група виходів розрядів сум S котрого з'єднана з ВІДПОВІДНИМИ розрядами входу блока 3, друга група виходів розрядів переносів Рі блока 2 з'єднана з ВІДПОВІДНИМИ розрядами першого входу блока б, третя група виходів розрядів переносів Рг блока 2 з'єднана з ВІДПОВІДНИМИ розрядами входу блока 5, перша група виходів розрядів сум S та друга група виходів розрядів переносів Р котрого з'єднані ВІДПОВІДНО з ВІДПОВІДНИМИ розрядами другого та третього входів блока 6, перша група виходів розрядів сум S та друга група виходів розрядів переносів Р котрого з'єднані ВІДПОВІДНО з ВІДПОВІДНИМИ розрядами першого та другого входів блока 7, перша група виходів розрядів сум S та друга група виходів розрядів переносів Р котрого з'єднані ВІДПОВІДНО З ВІДПОВІДНИМИ розрядами третього та четвертого входів блока 4, перша група виходів розрядів сум S та друга група виходів розрядів переносів Р блока 3 з'єднані ВІДПОВІДНО з ВІДПОВІДНИМИ розрядами першого та другого входів блока 4, вхід пристрою крізь виходи першої шини 8 з'єднаний ВІДПОВІДНО З першими входами, а крізь виходи другої шини 9 — ВІДПОВІДНО з другими входами елементів 1 І, розряди виходу пристрою з'єднані з ВІДПОВІДНИМИ розрядами виходу блока 4 Працює пристрій наступним чином Значення і-х (і = 1-4/7 ) розрядів множного А надходять на ВІДПОВІДНІ першй входи (і + 4n(j - 1))х елементів 1 І, де j - номер групи елементів 1 І 0 = 1.4/7 ) (при кожному фіксованому значенні j значення і змінюється від 1 до 4п), а значення j-x розрядів множника В надходять на другі входи усіх елементів 1 І J-I групи Таким чином, на виходах елементів 1 І формуються часткові добутки розрядністю 4п так, що кожна j-та група із 4п елементів 1 і формує j-й частковий добуток Часткові добутки створюють матрицю у вигляді паралелограма На фіг 2 приведено розбиття цієї матриці на п груп по 4 доданки (часткові добутки) Крім того, кожна група розбивається на блоки (тетради) по 4 розряди, крім лівих (старших) блоків При цьому молодші (праві) та старші (ЛІВІ) тетради в групі створюють трикутні (верхню та нижню ВІДПОВІДНО) підматриці, а останні тетради — квадратні підматриці часткових добутків В блоці 2 значення виходів J-I групи елементів 1 І надходять на ВІДПОВІДНІ ВХОДИ розрядів g-і під групи (д = 1 - 4 ) k-і групи ВХОДІВ (к = 1- и ) так, що j = д + 4(к - 1) (при кожному фіксованому значенні k значення д змінюється ВІД 1 до 4) Значення д-х часткових добутків k-оі групи надходять далі на входи складових k-і ЛІНІЙКИ суматорів 1-го підрангу блока 2, при цьому для k-і ЛІНІЙКИ суматорів кожен даний g-й доданок за допомогою відповідної комутації зсувається вліво на один розряд відносно попереднього (д - 1)-го доданку Кожна тетрада в групі обробляється у ВІДПОВІДНІЙ ЛІНІЙЦІ суматорів окремим чотирирозрядним суматором, кожен із котрих видає на свої виходи сигнали значень часткових сум S та переносів Р Всі квадратні підматриці обробляються суматорами, що Уявляють собою спрощений варіант (відсутні ВХІДНІ переноси) пристрою для підсумовування М чисел (див а с СССР № 1545216, кл G06F 7/52, БИ № 7, 1990 г ) Трикутні підматриці обробляються спеціалізованими суматорами SMH та SML ВІДПОВІДНО для молодшої та старшої тетрад На фіг 3, , фіг 8 приведені підматриця, функціональне зображення та таблиці значень розрядних індексів функцій переносів у ВІДПОВІДНИЙ розряд для спеціалізованого суматора SMH, на фіг 9, ,фіг 13 приведені підматриця, функціональне зображення та таблиці значень розрядних індексів функцій переносів у ВІДПОВІДНИЙ розряд для спеціалізованого суматора SML незалежно від значення п Таблиці значень розрядних індексів функцій переносів описують (аналогічно як і у пристрої для підсумовування М чисел) схеми паралельних переносів всередині груп розрядів даних суматорів у термінах симетричних булевих функцій Число паралельно функціонуючих ЛІНІЙОК суматорів k в 1-му підранзі блока 2 дорівнює k = п Загальне число підранпв е в цьому блоці визначар ється як ф = 1 4 ]log4n[ Число паралельно функціонуючих ЛІНІЙОК суматорів в кожному наступному підранзі в 4 рази менше, ніж в попередньому підранзі Дані послідовно проходять із ВІДПОВІДНИМ зсувом між собою через всі підранги та доданки на всіх лінійках суматорів обробляються потетрадно При цьому переноси, що виникають на всіх підрангах при підсумовуванні чисел, з частковими сумами не додаються При t = 1, 8, 5, на першу групу виходів розрядів сум S блока 2 надходять дві результуючі суми розрядністю (4n + 2 ( t + 1 ) розрядів кожна, зсунуті одна відносно другої на 2 ( t + 1 ) розрядів При t = 2, 4, 6, на вихід S цього блока надходить одна результуюча сума розрядністю 8п Переноси, що створюються в блоці 2 при підсумовуванні чисел на кожній ЛІНІЙЦІ суматорів підранпв з 1-го до (ер 1)-й надходять на третю групу виходів розрядів переносів Рг, а переноси, що виникають на суматорах останнього, ср-го підрангу цього блока, надходять на його другу групу виходів розрядів переносів Рі Усі переноси підсумовуються окремо від часткових сум у блоках 5 та 6 Переноси, що формуються на лінійках суматорів 1-го підрангу блока 2 з розрядністю часткових сум, які формуються на цих суматорах, надходять на ВІДПОВІДНІ ЛІНІЙКИ суматорів 1-го підрангу блока 5 Переноси, що формуються на лінійках 47521 суматорів 2-го підрангу блока 2 з розрядністю часткових сум, що формуються на цих суматорах, надходять на ВІДПОВІДНІ ЛІНІЙКИ суматорів 2-го під рангу блока 5 і т д Переноси, що формуються на лінійках суматорів (ер -1)-го підрангу блока 2 з розрядністю часткових сум, що формуються на цих суматорах, надходять на ВІДПОВІДНІ суматори останнього, ц-го, підрангу блока 5 Таким чином, загальне число підранпв ц в блоці 5 дорівнює ц, = Ф - 1 Число паралельно функціонуючих ЛІНІЙОК суматорів kj в 1-му підранзі цього блока дорівнює к' = п/4, а число паралельно функціонуючих ЛІНІЙОК суматорів в кожному наступному підранзі в 4 рази менше, ніж в попередньому підранзі Дані послідовно проходять через ВІДПОВІДНІ підранги і на всіх лінійках суматорів обробляються потетрадно При цьому переноси, що виникають на суматорах даного підрангу, підсумовуються окремо від часткових сум на суматорах наступного підрангу Результуючі суми переносів з двох ЛІНІЙОК суматорів при t = 1, 3, 5, або результовні суми переносів з однієї ЛІНІЙКИ суматорів при t = 2, 4, 6, останнього підрангу блока 5 надходять на першу групу виходів розрядів сум S цього блока, а переноси, що виникають на суматорах останнього підрангу, надходять на другу групу виходів розрядів переносів Р цього ж блока У випадку, коли з виходу S блока 2 надходять дві суми, вони підсумовуються на ЛІНІЙЦІ суматорів лише на одному підранзі блока 3 та обробляються потетрадно Виникаючі при цьому на суматорах блока 3 переноси надходять на другу групу виходів розрядів переносів Р цього блока та підсумовуються окремо від часткових сум в блоці 4, Результуюча сума розрядністю 8п з виходів суматорів блока 3 надходить на першу групу виходів розрядів сум S цього блока У випадку, коли з виходу S блока 2 надходить одна сума, вона передається на вихід S блока 3 без зміни При цьому переноси в блоці 3 не формуються та на вихід Р цього блока видаються ЛОГІЧНІ нулі Всі переноси та суми переносів, що надходять на входи блока 6, підсумовуються в ньому на Л І НІЙЦІ суматорів єдиного підрангу При цьому доданки на ЛІНІЙЦІ суматорів обробляються потетрадно і переноси, що виникають на суматорах, надходять на другу групу виходів розрядів переносів Р та підсумовуються окремо від часткових сум в блоці 7 Результуюча сума переносів надходить на першу групу виходів розрядів сум S блока 6 Всі переноси та суми переносів, що надходять на входи блока 7, обробляються в ньому на лінійках суматорів потетрадно При t = 1, 3, 5, число підранпв X, в блоці дорівнює X = ер - 2 При t = 2, 4, 6, X=ф- З Кожен підранг має одну лінійку суматорів і дані послідовно проходять через ВІДПОВІДНІ підранги, При цьому переноси, що виникають на суматорах даного підрангу, підсумовуються окремо від часткових сум на ЛІНІЙЦІ суматорів наступного підрангу, Переноси, що виникають на суматорах останнього підрангу, надходять на другу групу виходів розрядів переносів Р Результуюча сума переносів надходить на першу групу виходів розрядів сум S цього блока У блоці 4 число підранпв дорівнює двом Пер 8 ший підранг складається із двох паралельно функціонуючих ЛІНІЙОК двословних суматорів розрядністю 8п кожен з паралельними переносами, на котрих підсумовуються ВІДПОВІДНО на першій Л І НІЙЦІ суматора — результуюча суми, що надходять з виходів S блоків 3 та 7, на другій ЛІНІЙЦІ суматора — переноси, що надходять з виходів Р блоків 3 та 7 На ЛІНІЙЦІ двословного суматора другого підрангу розрядністю 8п з паралельним переносом формується добуток двох СПІВМНОЖНИКІВ із результуюча сум, що надходять з ЛІНІЙОК суматорів першого підрангу Добуток двох СПІВМНОЖНИКІВ розрядністю 8п з виходу блока 4 надходить на вихід пристрою Таким чином, підвищення швидкодії в пристрої досягається за рахунок одночасного підсумовування до чотирьох доданків, а також за рахунок того, що переноси, які одержуються при додаванні даних, не підсумовуються з частковими сумами на всіх підрангах пристрою за винятком підранпв, що входять до блоку 4 Як приклад розглянемо структуру швидкодіючого помножувача 32x32 (t = 3, п = 8) (фіг 14) На вхід блока ЕЕІ надходять 32 часткових добутки (елементи 1 І на фіг 14 не показані) Число підранпв ф в блоці ЕЕІ дорівнює ф = 1+ ]Іод48[ = 2 Число паралельно функціонуючих ЛІНІЙОК суматорів k в 1-му підранзі цього блока дорівнює k = 8, в другому підранзі — в 4 рази менше, тобто 2 ЛІНІЙКИ суматорів Доданки на всіх лінійках суматорів обробляються потетрадно Переноси (П) з кожної ЛІНІЙКИ суматорів 1-го підрангу надходять до блока ЕРІ, а переноси з кожної ЛІНІЙКИ суматорів 2-го підрангу - в блок ЕРИ Загальне число підранпв u в блоці ЕРІ дорівнює JL = 2 - 1 = 1 Число паралельно функціонуюL чих ЛІНІЙОК суматорів к' в цьому підранзі дорівнює к' = 8 4 = 2 Дані на ГЬсіх лінійках суматорів обробляються потетрадно ВІДМІТИМО особливість блока ЕРІ при t = 3 Він має лише один підранг, на котрому підсумовуються лише переноси При цьому на лінійках суматорів виникають одні часткові суми (£), Переноси відсутні, і ось чому При підсумовуванні чисел за допомогою пристрою для підсумовування М чисел на виході данного пристрою формуються значення чотирирозрядних часткових сум S та дворозрядних переносів в старші розряди Р, Отже, максимальне значення переносів може дорівнювати (11)2 або (3)ю При підсумовуванні на пристрої для підсумовування М чисел, із котрих складаються ЛІНІЙКИ суматорів підрангу блока ЕРІ, чотирьох максимальних значень переносів, на виході цього пристрою формується значення часткової суми, яка дорівнює (1100)2 або (12)ю при цьому умови для виникнення переносів відсутні і вони дорівнюють нулю (Але при підсумовуванні сум переносів виникають як часткові суми, так і переноси ) В результаті цього вихід Р блока ЕРІ на фіг 14 показано умовно пунктирною ЛІНІЄЮ Блоки SEN та ЕРИ мають по одному підрангу, кожен із котрих складається із однієї ЛІНІЙКИ суматорів Доданки на цих лінійках суматорів обробляються потетрадно та переноси, що виникають на суматорах, додаються окремо від часткових сум в блоці ER Число підранпв X, в блоці SPIN дорівнює Х-1 47521 2 = 0 Тому підранг в блоці ІРІП показано умовно пунктирною ЛІНІЄЮ Підранги в цьому блоці з'являються при великих значеннях! В блоці Ш число підранпв дорівнює двом Перший підранг складається із двох паралельно функціонуючих ЛІНІЙОК двослоених суматорів розрядністю 54 розряди кожний з паралельними переносами, на котрих підсумовуються ВІДПОВІДНО на першій ЛІНІЙЦІ суматора — результовні суми, що надходять з виходів S блоків SEN та ЕРИ, на другій ЛІНІЙЦІ суматора — переноси, ще надходять 3 виходів Р блоків SEN та ЕРИ 10 ногс суматора другого підрангу розрядністю 64 розряди з паралельним переносом формується добуток двох СПІВМНОЖНИКІВ із результативних сум (11, 12), що надходять з ЛІНІЙОК суматорів першого підрангу Добуток двох СПІВМНОЖНИКІВ розрядністю 64 розряди з виходу блока SR надходить на вихід пристрою F(1 64) При t = 2, 4, 6, блок SEN в структурі пристрою відсутній На ЛІНІЙЦІ ДВОСЛОВ р ц э. г р з Фіг І г, 2 р 11 Доданки А В С D 47521 4 * * * * Розряди 3 2 • * * * * _ — 1 * — — — 12 п/п 1 2 3 4 5 6 7 Розряди 3 2 3 2 1-3 2 3 X 0-2 X X 04 0 X 1 0-1 4 0 І 1 2 2 3 3 Фіг. З 1 X X X X X X X Фіг. 7 4 SMH З 2 SI S2 S3 S4 С P5 P6 D п/п 1 2 3 4 Розряди 3 2 3 2 1-2 2 2-3 X X X 4 2 3 3 4 І X X X X Фіг. 8 Фіг. 4 п/п 1 Розряди 2 1 2 X Доданки В С D Розряди 3 2 1 * * * * * Фіг. 5 Фіг. 9 № п/п 1 2 Розряди 3 2 1 1-2 2 X 2-3 0-1 X ФІГ. 6 Фіг. 10 13 47521 Розряд п/п I I 2-3 1 4 Розряди п/п 2 1 1 1 2-3 2 X 2 Фіг. II Фіг. 12 № п/п 1 2 Розряди 2 3 1 1 1 2-3 1 2 X Фіг. 13 Фіг І4 ДП «Український інститут промислової власності» (Укрпатент) вул Сім'ї Хохлових, 15, м Київ, 04119, Україна ( 0 4 4 ) 4 5 6 - 2 0 - 90 ТОВ "Міжнародний науковий комітет" вул Артема, 77, м Київ, 04050, Україна (044)216-32-71

ДивитисяДодаткова інформація

Назва патенту англійськоюQuick multiplier

Автори англійськоюPaulin Oleh Mykolaiovych, Synehub Mykola Ivanovych

Назва патенту російськоюБыстродействующий умножитель

Автори російськоюПаулин Олег Николаевич, Синегуб Николай Иванович

МПК / Мітки

Мітки: швидкодіючий, помножувач

Код посилання

<a href="https://ua.patents.su/7-47521-shvidkodiyuchijj-pomnozhuvach.html" target="_blank" rel="follow" title="База патентів України">Швидкодіючий помножувач</a>

Попередній патент: Спосіб визначення якості дерев хвойних порід

Наступний патент: Засіб “глутакам” для лікування серцево-судинних захворювань