Пристрій для множення n-розрядних чисел

Формула / Реферат

Пристрій для множення n-розрядних чисел, що містить n-розрядні регістри множеного й множника, комутатори груп та розрядів множеного й множника, керуючі входи яких підключені відповідно до першого й другого керуючих входів та пристрою, а виходи комутаторів груп підключені відповідно до входів блока перемножування к-розрядних чисел (к-розрядність груп множеного й множника), причому виходи регістрів множеного й множника, які згруповані по к розрядів, підключені до інформаційних входів комутаторів груп та розрядів множеного й множника відповідно, комутатор часткових добутків, інформаційні входи якого підключені до виходів блока перемножування к-розрядних чисел, а його керуючі входи підключені до першого й другого керуючих входів пристрою, виходи комутатора часткових добутків підключені до входів накопичуючого суматора, блок перемножування к-розрядних чисел містить буферні регістри та матрицю елементів І, вузли, що диференціюють, елементи І, АБО й затримки, причому входи першого й другого буферних регістрів підключені відповідно до входів множеного й множника блока перемножування к-розрядних чисел відповідно, вихід і-го розряду другого буферного регістра (і=1,.., к) підключений до перших входів елементів І і-го рядка матриці, прямий вихід і-го розряду першого буферного регістра з'єднаний з першим входом і-го елемента І, другий вхід якого підключений до тактового входу пристрою, а вихід - до других входів елементів І і-го стовпця матриці, що перебувають у парних рядках та до входу скидання і-го розряду першого буферного регістра, інверсний вихід якого через і-ий вузол диференціювання підключений до других входів елементів І і-го стовпця матриці, що перебувають у непарних її рядках, виходи елементів І j-oї діагоналі матриці (j-1,...,2к-1) з'єднані з входами j-гo елемента АБО, причому виходи перших двох елементів І кожної l-ої діагоналі матриці (l=2,..., 2к-2) підключені до входів 1-го елемента АБО безпосередньо, а виходи інших елементів І l-ої діагоналі матриці з'єднані із входами 1-го елемента АБО через елементи затримки, виходи елементів АБО є виходами блока перемножування к-розрядних чисел, який відрізняється тим, що з метою підвищення надійності в нього додатково введено третій керуючий вхід пристрою, який з'єднаний з керуючим входом введеного блока МДП-ключів, інформаційні входи блока МДП-ключів з'єднані з відповідними виходами накопичуючого суматора, а відповідні виходи МДП-ключів з'єднані з відповідними входами регістрів множеного і множника , які є входом/виходом пристрою.

Текст

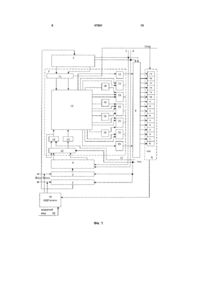

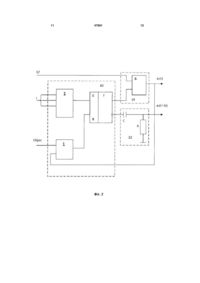

Пристрій для множення n-розрядних чисел, що містить n-розрядні регістри множеного й множника, комутатори груп та розрядів множеного й множника, керуючі входи яких підключені відповідно до першого й другого керуючих входів та пристрою, а виходи комутаторів груп підключені відповідно до входів блока перемножування крозрядних чисел (к-розрядність груп множеного й множника), причому виходи регістрів множеного й множника, які згруповані по к розрядів, підключені до інформаційних входів комутаторів груп та розрядів множеного й множника відповідно, комутатор часткових добутків, інформаційні входи якого підключені до виходів блока перемножування крозрядних чисел, а його керуючі входи підключені до першого й другого керуючих входів пристрою, виходи комутатора часткових добутків підключені до входів накопичуючого суматора, блок перемножування к-розрядних чисел містить буферні регістри та матрицю елементів І, вузли, що диференціюють, елементи І, АБО й затримки, причому входи першого й другого буферних регістрів підключені відповідно до входів множеного й множника блока перемножування к-розрядних чисел від U 2 47901 1 3 входи регістру з'єднані з відповідними тактовими виходами [1]. Недоліком цього обладнання є мала швидкодія та надійність. Найбільш близьким по технічній сутності до запропонованого є пристрій [2] для множення nрозрядних чисел, що містить n-розрядні регістри множеного 1 й множника 2, комутатори 3 та 4 відповідних груп розрядів множеного й множника, керуючі входи яких підключені відповідно до першого й другого керуючих входів 5 та 6 пристрою, а виходи підключені відповідно до входів блоку 7 перемножування к-розрядних чисел (к-розрядність груп множеного 1 й множника 2), причому виходи регістрів множеного й множника, які згруповані по к розрядів, підключені до інформаційних входів комутаторів груп 3 та 4 розрядів множеного й множника відповідно, комутатор часткових добутків 8, інформаційні входи якого підключені до виходів блоку перемножування к-розрядних чисел 7, а його керуючі входи, підключені до першого 5 й другого 6 керуючих входів пристрою, а виходи підключені до входів накопичуючого суматора 9, блок перемножування к-розрядних чисел 7 містить буферні регістри 10 та 11, матрицю 12 елементів І, вузли 13, що диференціюють, елементи І 14, АБО 15 й затримки 16, причому входи першого 10 й другого 11 буферних регістрів підключені відповідно до входів множеного 1 й множника 2 блоку перемножування к-розрядних чисел 7 відповідно, вихід і-го розряду другого буферного регістру 11 (і=1,.., к) підключений до перших входів елементів І і-го рядка матриці 12, прямий вихід і-го розряду першого буферного регістру 10 з'єднаний з першим входом і-го елемента І 14, другий вхід якого підключений до тактового входу 17 пристрою, а вихід - до других входів елементів 1 і-го стовпця матриці 12, що перебувають у парних рядках та до входу скидання і-го розряду першого буферного регістру 10, інверсний вихід якого через і-ий вузол диференціювання 13 підключений до других входів елементів 1 і-го стовпця матриці 12, що перебувають у непарних її рядках, виходи елементів І joї діагоналі матриці 12 (j-1, ..., 2к-1) з'єднані з входами j-гo елемента АБО 15, причому виходи перших двох елементів І кожної l-ої діагоналі матриці 12 (l=2,..., 2к-2) підключені до входів І-го елемента АБО 15 безпосередньо, а виходи інших елементів І l-ої діагоналі матриці 12 з'єднані із входами l-го елемента АБО 15 через елементи затримки 16, виходи елементів АБО 15 є виходами блоку 7 перемножування до к-розрядних чисел. Виходи накопичувального суматору є виходи пристрою. Розподілення в просторі IС на підложці кристалу входів та виходів приводить до зниження надійності пристрою. Наприклад, при обробці операнд і в множеного й множника з розрядністю по n=32 біт необхідно розташовувати на підложці кристалу 64 контакти для вхідних операндів та 64 контакти для вихідних операндів (для результату множення з розрядпістю n=64 біт). Всього потрібно 128 зовнішніх контактних площадок. IС. Отже, недоліком цього пристрою є низька надійність через більшу кількість зовнішніх контактів 47901 4 IС для входів та виходів. Мета корисної моделі підвищення надійності. Зазначена мета досягається тим, що у пристрій для множення n-розрядних чисел, що містить n-розрядні регістри множеного 1 й множника 2, комутатори груп 3 та 4 розрядів множеного 1 й множника 2, керуючі входи яких підключені відповідно до першого й другого керуючих входів 5 та 6 пристрою, а виходи комутаторів груп 3 та 4 підключені відповідно до входів блоку перемножування к-розрядних чисел 7 (к-розрядність груп множеного 1 й множника 2), причому виходи регістрів множеного 1 й множника 2, які згруповані по к розрядів, підключені до інформаційних входів комутаторів груп 3 та 4 розрядів множеного й множника відповідно, комутатор 8 часткових добутків, інформаційні входи якого підключені до виходів блоку перемножування к-розрядних чисел 7, а його керуючі входи, підключені до першого 5 й другого 6 керуючих входів пристрою, а виходи комутатора часткових добутків 8 підключені до входів накопичуючого суматора 9, блок перемножування крозрядних чисел 7 містить буферні регістри 10 та 11, матрицю 12 елементів І, вузли 13, що диференціюють, елементи І 14, АБО 15 й затримки 16, причому входи першого 10 й другого 11 буферних регістрів підключені відповідно до входів множеного 1 й множника 2 блоку перемножування крозрядних чисел 7 відповідно, вихід і-го розряду другого буферного регістру 11 (і=1,.., к) підключений до перших входів елементів І і-го рядка матриці 12, прямий вихід і-го розряду першого буферного регістру 10 з'єднаний з першим входом і-го елемента І 14, другий вхід якого підключений до тактового входу 17 пристрою, а вихід - до других входів елементів І і-го стовпця матриці 12, що перебувають у парних рядках та до входу скидання іго розряду першого буферного регістру 10, інверсний вихід якого через і-ий вузол диференціювання 13 підключений до других входів елементів І і-го стовпця матриці 12, що перебувають у непарних її рядках, виходи елементів І j-ої діагоналі матриці 12 (j-1,...,2к-1) з'єднані з входами j-гo елемента АБО 15, причому виходи перших двох елементів І кожної 1-ої діагоналі матриці 12 (1=2,..., 2к-2) підключені до входів l-го елемента АБО 15 безпосередньо, а виходи інших елементів І l-ої діагоналі матриці 12 з'єднані із входами l-го елемента АБО 15 через елементи затримки 16, виходи елементів АБО 15 є виходами блоку перемножування до крозрядних чисел 7, додатково введено третій керуючий вхід 18 пристрою, який з'єднаний з керуючим входом введеного блоку МДП-ключів 19, інформаційні входи блоку МДП-ключів 19 з'єднані з відповідними виходами накопичуючого суматора 9, а відповідні виходи МДП-ключів 19 з'єднані з відповідними входами регістрів множеного 1 і множника 2, які є входом/виходом пристрою. В основу корисної моделі поставлено задачу підвищення надійності, шляхом запропонування схемотехнічного рішення у вигляді додатково введеного керуючого входу 18 пристрою, який з'єднаний з керуючим входом блоку МДП-ключів 19, керуючий вхід МДП-ключів 19 з'єднаний з відповідним третім керуючим входом пристрою, 5 інформаційні входи блоку МДП-ключів 19 з'єднані з відповідними виходами накопичуючого суматора 9, а відповідні виходи МДП-ключів 19 з'єднані з відповідними входами регістрів множеного 1 і множника 2, які є входом/виходом пристрою. Причому результат множення з виходу накопичуючого суматору 9, що має 2n розрядів, тобто -2n точність результату має похибку , розподіляється наступним чином. Виходи суматору 9, на яких знаходяться старші розряди результату множення, з'єднані з відповідними n входами регістра множеного 1, а останні n розрядів суматору 9 - з відповідними входами регістра множника 2. У випадку коли достатня точність результату з -n похибкою (це широко використовується в спеціалізованих сопроцесорах), останні n розрядів суматору 9 по відповідним входам регістра множника 2 не з'єднаються. Отже забезпечується надпідсумковий позитивний ефект, зумовлений сукупністю вказаних ознак. На Фіг.1 показана функціональна схема обладнання для множення n-розрядних чисел; на Фіг.2 - принципова схема формування одиничного імпульсу a(t) і затриманого на a (t+ t); на Фіг.3 - матриця добутків двох 8-розрядних чисел. Надійність пристроїв, які створюються у вигляді інтегральних мікросхем, підвищується тому, що інтенсивність відмов , контактних вузлів всередині схеми на три, ..., чотири порядки менші в порівнянні з формуванням зовнішніх контактних вузлів. Відомо, що основними причинами відмови приладів при зборці кристалів в корпус та установці на друковану плату є недостатня механічна міцність контактів, мала адгезія виводів до контактної площадки і останньої до підложи, деградації контактного опору через взаємну дифузію металів з утворенням інтерметалевих фаз і пустот, або прихованого технологічного дефекту. Під контактним вузлом приймається система: струмоведуча площина металізації - термокомпресія - провідник – контактний вивід корпусу – міжз'єднання до струмоведучої площадки друкованої плати. Припустимо, інтенсивність відмов кожного контактного вузла при операціях: - термокомпресія провідника до металізованої площадки дорівнює -6 1=10 , - термокомпресія провідника до контакту площини корпусу дорівнює -6 2=10 , - контакт виводів корпусу IС до друкованої плати дорівнює -6 3=10 . Тоді загальна інтенсивність відмови одного контактного вузла дорівнює -6 -6 -6 -6 з= 1+ 2+ 3=10 +10 +10 =3 10 . Наприклад, у пристроях при паралельній обробці інформаційних операндів з розрядністю 32 загальна інтенсивність відмов зовнішніх контактних вузлів для множника, множеного та суматору 47901 6 -2n при отриманні результату з похибкою дорівнює (32+32+64) з=128 3 10-6=384 10-6. Тоді середній час безвідмовної роботи Тр пристрою дорівнює Тр=(1/ 1). Припустимо, що для пристроїв з числом контактних вузлів 32 інтенсивність відмови пристрою прототипу дорівнює з пр=384 10-6, а для пристрою з розробленою новою схемотехнікою число контактних вузлів зменшується в 2 рази, тоді з вин=(384/2) 10-6, тобто за рахунок зменшення кількості контактних вузлів інтенсивність відмови пристроюкорисної моделі зменшується в 2 рази. Причому, порівняння проводиться при ідентичних умовах формування елементів конструкції, технології виготовлення перетворювачів і мають однакову інтенсивність відмови. Це забезпечує збільшення середнього часу безвідмовної роботи пристрою для множення nрозрядних чисел, відповідно в 2 рази. Дійсно Тр вин/Тр пp=(1/ і)вин/(1/ і)пp, де Тр пр - середній час безвідмовної роботи пристрою-прототипу; Тр вин - середній час безвідмовної роботи пристрою для множення n-розрядних чисел з розробленою новою схемотехнічною реалізацією. Тоді для наведеного прикладу середній час безвідмовної роботи збільшується в 2 рази, тобто Твин/Тпр=384 10-6/[(384/2) 10-6]=2. Таким чином, зменшення кількості контактних вузлів в 2 рази при збереженні паралельної обробки операндів високої точності збільшує середній час безвідмовної роботи в 2 рази. Розглянемо роботу пристрою для співмножників N1, N2. У двійковій позиційній системі числення число представляється у вигляді многочлена k n 1 ak 2k , N k 0 де n - число розрядів; an 1 - значення відповідних розрядів числа і рівних 1 або 0. Отже, добуток двох сум можна представити як перемножування n/k частин співмножників по к розрядів в кожній. Тоді алгоритм зводиться до послідовного підсумовування складових добутків малорозрядних частин співмножників. На Фіг.3 представлені доданки добутків двійкових чисел N1 і N2, заданих 8-розрядними кодами і розбитих на дві частини по чотири розряди в кожній, тобто числа N1=а7а6а5а4а3а2а1а0 ((Представлені першою і другою частинами відповідно [а7а6а5а4] та [а3а2a1a0], а N2- b7b6b5b4b3b2b1b0 аналогічно [b7b6b5b4] та [b3b2b1b0] Добуток N1·N2 може бути здійснено послідовно за чотири мікрокоманди для результату з подвійною точністю. Нехай N1=10110011, N2=10110110, тобто а7=1, а6=0, a5=1, а4=1, а3=0, а2=0, а1=1, 7 47901 b7=1, b6=0, b5=1, b4=1, b3=0, b2=1, b1=1, b0=0, тоді їх частини мають вигляд: (Іа=а7а6а5а4=1011, ІІа=а3а2а1ао=0011) - частини множеного; (Іb=b7b6b5b4=1011, ІІb=b3b2b1b0=01100) - частини множника. Пристрій працює наступним чином. Після обнуління регістрів 1 і 2 співмножників, буферних регістрів 10 і 11 і накопичуючого суматора 9 записуються числа N1 і N2 у регістри 1 і 2 відповідно. По приходу керуючих сигналів f1 і f2 по першому 5 і другому 6 керуючих входах у комутаторах 3 і 4 груп формуються мікрокоманди по структурним формулам [2] F f1 f 2 f1 f2 ; F f1 f2 f1 f2 ; F f1 f 2 f1 f2 ; (1) F f1 f2 f1 f2 . Під дією мікрокоманд (1) у буферні регістри 10 і 11 відповідно записуються Іаi або Iiаi та Іbi або IIbi частини кодів співмножників. Одиниці bi надходять на перши входи елементів І і-го рядка матриці 12. Одиниці ai по приходу тактового імпульсу 17 пройдуть через елементи 14 і надійдуть на другі входи І і-го стовпця матриці 12, що перебувають у парних рядках та на вхід скидання і-го розряду буферного регістру 10, при цьому при перемиканні тригера на його інверсному виході з'являється імпульс, який пройшовши і-ий вузол 13 диференціювання надійде на другі входи елементів І і-го стовпця матриці 12, що перебувають у непарних її рядках, на вихо 8 дах елементів І j-ої діагоналі матриці 12 (j=1,..., 2к1) з'явиться імпульс, який для перших двох елементів І кожної l-ої діагоналі матриці 12 (l=2,...,2к-2) пройде на входи l-го елемента АБО 15 безпосередньо, а імпульси на виходах інших елементів І l-ої діагоналі матриці 12 пройдуть на входи l-го елемента АБО 15 через елементи затримки 16. Вихідні імпульси елементів АБО 15 надходять на інформаційні входи комутатора 8 часткових добутків, у якому по керуючих сигналах f1 і f2 відповідно до структурних формул: Y1 f1 f2 ; Y2 f1 f2 f1 f2 ; (2) Y3 f1 f2 формуються мікрокоманди (2), які пропускають імпульси результату часткових перемножувань у відповідні розряди накопичуючого суматора 9. Після виконання всіх мікрокоманд у накопичуючому суматорі 9 установлюється результат перемножування всіх частин співмножників. По третьому керуючому входу 18 пристрою надходить імпульс, під дією якого відкриваються МДП-ключі 19 і результат перемножування з'являється на входах/виходах пристрою. Література: 1. Патент США №3670956, кл. 235/164, опубл. 1972. 2. А.С. №813417, МПК G06F7/52, опубл. 15.03.81. Бюл. №10 (прототип). 9 47901 10 11 47901 12 13 Комп’ютерна верстка О. Рябко 47901 Підписне 14 Тираж 26 прим. Міністерство освіти і науки України Державний департамент інтелектуальної власності, вул. Урицького, 45, м. Київ, МСП, 03680, Україна ДП “Український інститут промислової власності”, вул. Глазунова, 1, м. Київ – 42, 01601

ДивитисяДодаткова інформація

Назва патенту англійськоюDevice for multiplication of n-didgit numbers

Автори англійськоюLukashenko Andrii Hermanovych

Назва патенту російськоюУстройство для умножения n-разрядных чисел

Автори російськоюЛукашенко Андрей Германович

МПК / Мітки

МПК: G06F 7/52

Мітки: n-розрядних, пристрій, чисел, множення

Код посилання

<a href="https://ua.patents.su/7-47901-pristrijj-dlya-mnozhennya-n-rozryadnikh-chisel.html" target="_blank" rel="follow" title="База патентів України">Пристрій для множення n-розрядних чисел</a>

Попередній патент: Cпociб oдepжaння bitamih d3-е білкового комплексу

Наступний патент: Грейферні ваги

Випадковий патент: Спосіб дистанційного виміру анізотропії інтенсивності температурних пульсацій атмосфери за допомогою акустичного зондування