Схемний пристрій, виконаний на електронних компонентах

Формула / Реферат

1. Схемний пристрій з кількома електронними компонентами (2, 3, 4, 5), робочий стан яких може бути переведений у стан стирання за допомогою заданого керуючого сигналу або сигналу даних (6, 7, 8, 9), поданого на відповідні компоненти схеми (2, 3, 4, 5), у якому дані, записані до компонентів схеми (2, 3, 4, 5), приймають значення логічного нуля, причому для послідовного у часі запуску всіх компонентів схеми (2, 3, 4, 5) передбачена автоматично функціонуюча незалежно від зовнішніх тактових імпульсів після запуску схема запуску (25) з кількома послідовно підключеними відпираючими каскадами (26, 27, 28, 29) відповідно до кількості компонентів (2, 3, 4, 5), кожний відпираючий каскад (26, 27, 28, 29) можна запускати або активізувати за допомогою відпираючого сигналу (42, 43, 44, 45), що генерується одним з розташованих безпосередньо перед ним відпираючим каскадом (26, 27, 28, 29) для видачі керуючого сигналу на відповідний компонент схеми, і відпираючий каскад (26, 27, 28, 29) після здійснення запуску відповідних компонентів схеми (2, 3, 4, 5), у свою чергу, видає відпираючий сигнал (42, 43, 44, 45) для запуску або активізації відпираючого каскаду (26, 27, 28, 29), розташованого безпосередньо після нього, який відрізняється тим, що:

- компоненти схеми включають у себе, по-перше, регістр (2) та/або елементи схеми (3) і, по-друге, елементи пам'яті (4, 5);

- регістрам (2) або елементам схеми (3) підпорядкована перша схема запуску (25) із відпираючими каскадами (26, 27), а елементам пам'яті (4, 5) підпорядкована підключена послідовно до першої схеми запуску (25) друга схема запуску (25а) з відпираючими каскадами (28, 29);

- для стирання вмісту елементів пам'яті (4, 5) передбачена шина даних (20), на яку подається сигнал даних для запису до елементів пам'яті (4, 5), причому після активізації другої схеми запуску (25а) за допомогою попереднього відпираючого каскаду (27) першої схеми запуску (25) до елементів пам'яті (4, 5) записується значення логічного нуля, подане на шину даних, і, таким чином, елементи пам'яті (4, 5) переводяться у стан стирання.

2. Схемний пристрій за п. 1, який відрізняється тим, що кожному компоненту схеми (2, 3, 4, 5) підпорядкований відповідний відпираючий каскад (26, 27, 28, 29) обох схем запуску (25, 25а).

3. Схемний пристрій за пп. 1 або 2, який відрізняється тим, що передбачена адресна шина (18) для адресації компонента схеми (2, 3, 4, 5).

Текст

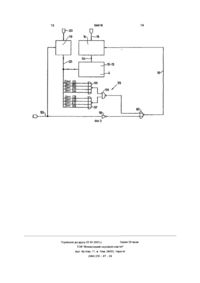

1 Схемний пристрій з кількома електронними компонентами (2, 3, 4, 5), робочий стан яких може бути переведений у стан стирання за допомогою заданого керуючого сигналу або сигналу даних (6, 7, 8, 9), поданого на ВІДПОВІДНІ компоненти схеми (2, 3, 4, 5), у якому дані, записані до компонентів схеми (2, 3, 4, 5), приймають значення логічного нуля, причому для послідовного у часі запуску всіх компонентів схеми (2, 3, 4, 5) передбачена автоматично функціонуюча незалежно від ЗОВНІШНІХ тактових імпульсів після запуску схема запуску (25) з кількома послідовно підключеними відпираючими каскадами (26, 27, 28, 29) ВІДПОВІДНО до КІЛЬКОСТІ компонентів (2, 3, 4, 5), кожний відпираючий каскад (26, 27, 28, 29) можна запускати або активізувати за допомогою відпираючого сигналу (42, 43, 44, 45), що генерується одним з розташованих безпосередньо перед ним відпираючим каскадом (26, 27, 28, 29) для видачі керуючого сигналу на ВІДПОВІДНИЙ ком понент схеми, і відпираючий каскад (26, 27, 28, 29) після здійснення запуску ВІДПОВІДНИХ компонентів схеми (2, 3, 4, 5), у свою чергу, видає відпираючий сигнал (42, 43, 44, 45) для запуску або активізації відпираючого каскаду (26, 27, 28, 29), розташованого безпосередньо після нього, який відрізняється тим, що - компоненти схеми включають у себе, по-перше, регістр (2) та/або елементи схеми (3) і, по-друге, елементи пам'яті (4, 5), - регістрам (2) або елементам схеми (3) підпорядкована перша схема запуску (25) із відпираючими каскадами (26, 27), а елементам пам'яті (4, 5) підпорядкована підключена послідовно до першої схеми запуску (25) друга схема запуску (25а) з відпираючими каскадами (28, 29), - для стирання вмісту елементів пам'яті (4, 5) передбачена шина даних (20), на яку подається сигнал даних для запису до елементів пам'яті (4, 5), причому після активізації другої схеми запуску (25а) за допомогою попереднього відпираючого каскаду (27) першої схеми запуску (25) до елементів пам'яті (4, 5) записується значення логічного нуля, подане на шину даних, і, таким чином, елементи пам'яті (4, 5) переводяться у стан стирання 2 Схемний пристрій за п 1, який відрізняється тим, що кожному компоненту схеми (2, 3, 4, 5) підпорядкований 00 ВІДПОВІДНИЙ відпираючий каскад (26, 27, 28, 29) обох схем запуску (25, 25а) 3 Схемний пристрій за пп 1 або 2, який відрізняється тим, що передбачена адресна шина (18) для адресації компонента схеми (2, 3, 4, 5) Винахід стосується схемного пристрою з кількома електронними компонентами, робочий стан яких за допомогою заданого керуючого сигналу, стиранні даних, записаних в окремих регістрах, або повний вміст напівпровідникового пристрою що подається до ВІДПОВІДНИХ компонентів схеми, або іншого компонента схеми Зокрема, у разі користування чіп-картками, для захисту від несанкціонованого зчитування конфіденційних даних може виникнути потреба у забезпеченні активно функціонуючих заходів захисту для запобігання зчитуванню секретних даних, наприклад, під час спроби можна змінювати на стан установлення на нуль або стирання, причому дані, записані до компонентів схеми, замінюються значенням логічного нуля З різних підстав може виникнути необхідність у О пам'яті, інтегрованого у мікропроцесорному ЧІПІ, ю 54418 несанкціонованого доступу, здійснюваного хакерами (комп'ютерними зломниками), також і у тому разі, коли подача тактових сигналів на мікропроцесор відключена У разі вмикання мікропроцесора в усіх регістрах зазвичай записується певне значення, замість якого у процесі обробки даних записуються різні дані, причому ці дані, у залежності від обставин, можуть містити також конфіденційну або персональну інформацію Для попереднього запису до регістрів певного заданого значення у них зазвичай передбачається окремий вхід для скидання Цей вхід для скидання з'єднаний, наприклад, з транзисторним ключем, який змінює значення, що має бути записаним до регістру, на певний потенціал Для напівпровідникового пристрою пам'яті з довільною вибіркою, що має велику КІЛЬКІСТЬ комірок пам'яті, у разі наявності окремих входів для скидання для кожної комірки пам'яті значно зросла б потрібна площа Крім того, такий ПІДХІД вимагає великої потужності запускаючого пристрою для скидання даних, записаних у пристрої пам'яті, оскільки, наприклад, треба одночасно керувати 256 х 8 транзисторами Така структура схеми суперечить, крім бажання досягти високого ступеню інтеграції інтегральних схем напівпровідникового пристрою пам'яті, також якомога простішій структурі схем керування, що дозволяла б економити електроенергію Крім того, як захід активного захисту проти несанкціонованого доступу до конфіденційних даних, можна було б за допомогою мікропроцесора адресувати усі ПОСЛІДОВНІ комірки пристрою пам'яті, яких стосувалась спроба несанкціонованого доступу, і потім замість наявних даних записувати до кожної комірки пам'яті, якої стосувався запит, значення логічного нуля Проте, таке рішення не є вдалим в усіх випадках для запобігання недозволеного доступу до даних, оскільки можна припинити подачу тактових імпульсів, мікропроцесор не функціонує і не може приймати завдання для виконання З опису до патенту США US-A-4 928266 відома схема запуску з ланцюгом з N елементів затримки, керування першим з яких здійснюється за допомогою внутрішнього сигналу скидання RESET, а також певної КІЛЬКОСТІ N запускаючих пристроїв для скидання, керування кожним з яких здійснюється через елемент затримки Мета керування із зміщенням за фазою полягає у зменшенні ПІКІВ струму, що звичайно зумовлені видачею сигналу скидання В Європатенті ЕР-А-0 574 094 описаний ланцюг із схем "Flash-clear", що спрацьовують послідовно одна за одною із затримкою у часі, причому перша активізується за допомогою сигналу пуску, що генерується пусковою схемою У тексті опису до патенту далі наведений спрощений варіант схеми "Flash-clear" з кільцевим генератором з функцією утримування коливань для генерування тактових імпульсів, що застосовуються для визначення часу стирання, із лічильником для рахування КІЛЬКОСТІ тактових імпульсів, що видаються кільцевим генератором, а також т-біт-лічильником для рахування КІЛЬКОСТІ груп комірок пам'яті У описі до патенту WO-A-82 022 74 А показаний пристрій для автоматичного стирання даних, записаних до банків даних, із спеціальним вимика чем, аварійним вимикачем , що після запуску на першому етапі керує процесом стирання усієї інформації у банку даних, а на другому етапі - стиранням усіх інформацій щодо програм у банку даних Цей спеціальний схемний пристрій служить, насамперед, для того, щоб стирати записи у банку даних від несанкціонованого доступу або саботажу без їхнього фізичного знищення Схемний пристрій має бістабільний мультивібратор, що спрацьовує у разі натискання аварійної кнопки, вихідний сигнал якого може активізувати керовані тактовими імпульсами системи адресними генераторами, тобто генеруються всі адреси, що можуть мати місце у ВІДПОВІДНИХ пристроях для запису даних Адресні генератори функціонують паралельно У патенті Німеччини DE-A-41 35 767 описаний пристрій для забезпечення захисту даних від несанкціонованого доступу у блоці керування автоматів, операції яких оплачуються монетами У разі спроби відкрити кожух, що захищає блок керування, цей процес розпізнається за допомогою сенсорів Сенсори, що реєструють механічний або ХІМІЧНИЙ злом, а також зміну температури навколишнього середовища і робочої напруги, зв'язані із сенсорною схемою, що має автономний блок електроживлення За допомогою схеми стирання у разі спроби злому блока керування стираються дані, що зберігаються у ВІДПОВІДНИХ конструктивних вузлах Метою винаходу була розробка схемного пристрою зазначеного на початку опису типу, за допомогою якого також незалежно від ЗОВНІШНІХ тактових імпульсів можна активізувати процес автоматичного скидання даних, записаних в обраних компонентах схеми до значення логічного нуля, причому немає потреби у додатковій площі або суттєвому збільшенню схемотехнічних витрат для реалізації схемного пристрою Це завдання вирішується завдяки схемному пристрою згідно з п 1 формули винаходу За винаходом, передбачається, зокрема - компоненти схеми включають у себе, поперше, регістр та/або елементи схеми, і, по-друге, елементи пам'яті, - регістрам або елементам схеми підпорядкована перша схема запуску із відпираючими каскадами, а елементам пам'яті підпорядкована підключена послідовно до першої схеми запуску друга схема запуску з відпираючими каскадами, - для стирання вмісту елементів пам'яті передбачена шина даних, на яку подається сигнал даних для запису до елементів пам'яті, причому після активізації другої схеми запуску за допомогою попереднього відпираючого каскаду першої схеми запуску до елементів пам'яті записується значення логічного нуля, подане на шину даних, і, таким чином, елементи пам'яті переводяться у стан стирання При цьому в основу винаходу було покладено перевірену досвідом ідею, що полягає у використанні для стирання даних, записаних до окремих компонентів схеми, наприклад регістрів або комірок пам'яті напівпровідникових пристроїв пам'яті, автоматично активізованої схеми запуску, принцип дії якої аналогічний принципу дії відомого механічного "ланцюга доміно" За винаходом, після одно 54418 6 ті, який, таким чином, потребує досить великої потужності запускаючого пристрою шини даних, для того, щоб одночасно перевести усі комірки пам'яті на рівень логічного нуля, схемний пристрій згідно з винаходом має ту перевагу, що шина даних має забезпечувати значно меншу потужність запускаючого пристрою, оскільки компоненти схеми або комірки пам'яті опитуються не одночасно, а послідовно один за одним У наступному варіанті втілення винаходу з особливо простою схемотехнічною реалізацією схеми запуску може бути передбачено, що відпираючий сигнал, що видається останнім відпираючим каскадом, знову повертається по контуру зворотного зв'язку на вхід першого відпираючого каскаду другої схеми запуску В особливо переважному варіанті реалізації винаходу передбачено, що компоненти схеми є комірками пам'яті регістра та/або програмованого напівпровідникового пристрою пам'яті При цьому перевага полягає у тому, що відпираючі каскади, підпорядковані коміркам пам'яті регістру, включені перед відпираючими каскадами, підпорядкованими коміркам пам'яті програмованого напівпровідникового пристрою пам'яті Таким чином, після запуску схеми запуску за допомогою сигналу дозволу спочатку відпираються регістри, а після них комірки пам'яті напівпровідникового пристрою пам'яті При цьому регістри підтримують потужність сигнали у ВІДПОВІДНОСТІ до бажаної КІЛЬКОСТІ комзапускаючого пристрою шини даних Перевага понентів схеми, які слід запустити такої ПОСЛІДОВНОСТІ відпираючих каскадів полягає у тому, що у разі запуску комірок пам'яті динамічноУ переважному варіанті реалізації винаходу го напівпровідникового пристрою пам'яті з довільможе бути передбачено, щоб кожний компонент ною вибіркою (RAM) лише за допомогою додаткосхеми був ВІДПОВІДНО підпорядкований одному вих схемотехнічних витрат можна розпізнати, коли відпираючому каскаду схеми запуску будуть повністю опитані окремі відпираючі каскади У переважному варіанті виконання схемного схеми запуску, тому завдяки залежності адресації пристрою згідно з винаходом передбачена адрескомірок пам'яті або групи комірок пам'яті від попена шина для адресації компоненту схеми, а також редньої відповідної адреси не можна однозначно шина даних надає сигнал даних у розпорядження прийняти рішення щодо того, яка з груп фактично для запису даних до одного з компонентів схеми запускається "першою" чи "останньою" Після відпирання компонента схеми за допомогою підпорядкованого відпираючого каскаду схеми Іншою перевагою схемного пристрою згідно з запуску, здійснюється, наприклад, запис поданого винаходом за аналогією з механічним "ланцюгом на шину даних значення логічного нуля до комподоміно" Є те, що для послідовного у часі запуску нента схеми, так що таким чином дані, записані до окремих відпираючих каскадів потрібен ВІДПОВІДНО компоненту схеми, стираються В особливо перелише інвертор відпираючого каскаду, і, крім того, важному варіанті реалізації винаходу на всі лінії кожний попередній відпираючий каскад запускає шини даних, наприклад, подане значення логічноабо керує ВІДПОВІДНО наступним відпираючим касго нуля, за допомогою схеми запуску окремі комкадом поненти схеми, з'єднані з шиною даних, відпираУ особливо переважному варіанті реалізації ються послідовно один за одним у часі, причому винаходу передбачено, що запуск схеми запуску реакцією на відпирання є послідовний у часі запис відбувається автоматично шляхом подання сигназначення логічного нуля через шину даних до лу дозволу на перший відпираючий каскад При окремих компонентів схеми У порівнянні з відоцьому перевага полягає у включенні перед схемою мими на сьогодні заходами, що відповідають сузапуску, що підпорядкована схемі керування для часному рівню технічного розвитку, які полягають у керування одним або кількома компонентами схетому, що для кожного компонента схеми або кожми, сенсорної схеми, передбаченої у схемному ної комірки пам'яті для подачі досить великого пристрої, що реєструє відхилення від дозволеного сигналу скидання є необхідним транзистор скирежиму роботи схеми керування або компоненту дання, що потребує великої площі для розташусхеми, причому реакцією цієї сенсорної схеми на вання, перевага схемного пристрою згідно з винавідхилення від дозволеного режиму є генерація ходом полягає у значно меншій потрібній площі У сигналу дозволу, що передається на перший відпорівнянні з іншим відомим заходом, що відповіпираючий каскад для автоматичної активізації дає сучасному технічному рівню, у якому адресний схеми запуску У спрощеному щодо схемотехніки декодер оснащений додатковою схемою, що заваріанті реалізації винаходу може бути при цьому безпечує одночасне відпирання всіх комірок пам'япередбачено, щоб сенсорна схема була підпорядкратного запуску схема запуску працює окремо і повністю незалежно від ЗОВНІШНІХ тактових імпульсів схеми керування, наприклад, мікроконтролера, який можна зупинити у разі недозволеного доступу, так що, у певному розумінні, існує можливість вільного зчитування конфіденційних даних, записаних, наприклад, у особливо ризикованому статичному напівпровідниковому пристрої пам'яті Після реєстрації ВІДПОВІДНОГО сигналу пуску, що надходить, наприклад, після виявлення неприпустимого відхилення від дозволеного робочого режиму схеми керування або компонента схеми, видається сигнал дозволу, який, певним чином, запускає електричний "ланцюг доміно", тобто схему запуску Реакцією на сигнал дозволу є те, що через перший відпираючий каскад, керування яким здійснюється за допомогою відпираючого сигналу, запускається перший з багатьох потрібних компонентів схемного пристрою, записані дані до якого слід стерти, наприклад, накопичувач або регістр мікроконтролера, у розумінні установлення на нуль або стирання, і потім послідовно у часі після запуску першого відпираючого каскаду, видається наступний відпираючий сигнал, який запускає наступний відпираючий каскад, наприклад, для активізації адресного декодера і наступного стирання даних, записаних до групи адресованих комірок пам'яті статичного напівпровідникового пристрою пам'яті Після ЦЬОГО надходять наступні відпираючі 54418 кована генератору тактових імпульсів та/або схемі електроживлення схеми керування або компоненту схеми, і реєструвала відхилення напруги електроживлення від робочого діапазону напруги та/або тактової частоти від робочого діапазону частоти тактових імпульсів, і у разі наявності відхилення від робочого діапазону напруги та/або частоти тактових імпульсів генерувала сигнал дозволу, передаючи його на перший відпираючий каскад для забезпечення автоматичного спрацьовування або активізації схеми запуску При цьому сенсорна схема може включати у себе детектор напруги, що реєструє моменти, коли напруга електроживлення не досягає або перевищує ВІДПОВІДНО задані нижнє або верхнє граничне значення робочого діапазону З іншого боку, сенсорна схема може включати в себе також детектор частоти, що реєструє моменти, коли частота тактового імпульсу не досягає або перевищує ВІДПОВІДНІ задані нижнє або верхнє граничне значення робочого діапазону частоти тактових імпульсів Таким чином, можна, наприклад, у разі надто високого або надто низького значення робочої напруги або частоти тактових імпульсів, розпізнавати спробу недозволеного доступу до конфіденційних даних і використовувати це для автоматичного запуску схеми запуску Для забезпечення за будь-яких обставин достатньої потужності запускаючого пристрою шини даних для того, щоб послідовно здійснювати перезапис даних у керованих компонентах схеми, за допомогою регулювання можна припинити процес послідовного відпирання компонентів схеми, що опитуються, у разі надто малої потужності запускаючого пристрою шини даних Тому перевага переважного варіанту втілення винаходу полягає у наявності схеми регулювання, підпорядкованої схемі запуску, яка у разі збою шини даних або запускаючого пристрою знову активізує схему запуску Лише після досягнення стабільного стану продовжується процес послідовного установлення на нуль всіх компонентів схеми, тобто припиняється, а потім знову активізується робота схеми запуску При цьому у разі простої схемотехнічної реалізації винаходу може бути передбачено, щоб схема регулювання знімала сигнали даних з шини даних і реєструвала відхилення від нульового значення для короткочасного відключення і повторної автоматичної активізації схеми запуску У особливо переважному варіанті втілення винаходу передбачено, що принаймні один з компонентів схеми представляє собою побудований на напівпровідниковій основі напівпровідниковий пристрій пам'яті з довільною вибіркою, що має багато комірок пам'яті, які за допомогою схеми адресації можна адресувати для довільно частого повторення процесу запису та зчитування даних, що подані на схему введення або виведення даних, і відпираючий каскад схеми запуску, підпорядкований напівпровідниковому пристрою пам'яті, безпосередньо впливає на схему адресації для адресації принаймні однієї з комірок пам'яті, причому здійснюється керування схемою введення або виведення даних для видачі значення логічного нуля на адресовану комірку пам'яті При цьому щонайменше частина компонентів схеми може бути підпорядкована групі комірок пам'яті напів 8 провідникового пристрою памяті, які за допомогою схеми запуску автоматично послідовно адресуються для установлення на значення логічного нуля Завдяки наявній схемі декодування звичайного напівпровідникового пристрою пам'яті з довільною вибіркою дуже просто здійснюється послідовна адресація комірок пам'яті за допомогою відпираючих каскадів схеми запуску згідно з винаходом В існуючих напівпровідникових пристроях пам'яті з довільною вибіркою завдяки наявності схемного пристрою за винаходом немає необхідності у інтегруванні додаткових логічних елементів, із складною у залежності від обставин схемотехнікою Для запуску або установлення на нуль комірок пам'яті напівпровідникового пристрою пам'яті з довільною вибіркою вистачає однієї спільної для всіх комірок пам'яті схеми запуску з ВІДПОВІДНОЮ КІЛЬКІСТЮ відпираючих каскадів Лише після того, як була адресована перша група комірок пам'яті, тобто ВІДПОВІДНІ числові шини комірок пам'яті знаходяться в активному стані, здійснюється адресація наступної групи комірок пам'яті напівпровідникового пристрою пам'яті з довільною вибіркою Внаслідок цього гарантується також обмеження ємнісного навантаження шини даних Якщо, навпаки, всі регістри та комірки пам'яті напівпровідникового пристрою пам'яті відкриваються одночасно, шина даних повинна мати значно вищу потужність запускаючого пристрою, для того, щоб у найнесприятливішому стані існувала можливість швидкого перекидання всіх комірок пам'яті напівпровідникового пристрою пам'яті В особливо переважному варіанті реалізації схемного пристрою за винаходом це стосується напівпровідникового чіпа, розташованого всередині корпусу електронної чіп-картки, причому цей чіп крім напівпровідникового пристрою пам'яті з довільною вибіркою охоплює також ІНШІ функціональні вузли, зокрема постійний напівпровідниковий пристрій пам'яті та/або напівпровідниковий пристрій пам'яті з електричним стиранням Інші ознаки, переваги та ДОЦІЛЬНІ рішення винаходу пояснюються на прикладі реалізації за допомогою креслень На кресленнях показано На фіг 1 схема схемного пристрою зі схемою запуску згідно з прикладом реалізації винаходу, та на фіг 2 - схема регулювання, підпорядкована схемі запуску за фіг 1 Показаний на фіг 1 та 2 приклад реалізації винаходу схемного пристрою 1 має кілька електронних компонентів 2, 3, 4 та 5, робочим станом яких можна керувати за допомогою заданого керуючого сигналу 6, 7, 8 та 9, що подається на ВІДПОВІДНІ компоненти схеми 2 5 для переведення їх у стан встановлення на нуль або стирання, причому замість даних, записаних до ВІДПОВІДНИХ компонентів схеми 2 5, записується значення логічного нуля Компонент схеми 4 охоплює напівпровідниковий пристрій пам'яті з довільною вибіркою (статичний RAM), побудований на напівпровідниковій основі, з першою групою комірок пам'яті 10 та 11 Компонент схеми 5 охоплює напівпровідниковий пристрій пам'яті з довільною вибіркою (статичний RAM), побудований на аналогічній напівпровідниковій основі з іншою групою комірок пам'яті 12 та 13 Комірки пам'яті 10 13 можна адресувати за допомогою схеми адресації 14 у формі відомого адресного декодера, керування яким можна здійснювати за допомогою адресних шин 15 (адресний біт нуль), 16 (адресний біт одиниця) та інших адресних шин 17 (адресні біти від двох до п) адресної шини 18, для довільно частого повторення процесу запису та зчитування 8-біт-даних схеми введення або виведення даних, поданих на шину даних 20, з 8 ЛІНІЯМИ даних від DB [0] до DB [7], як це є зрозумілим для спеціаліста, і тому тут немає потреби пояснювати це детально Компонент схеми 2 представляє собою, наприклад, регістр для періодичного запам'ятовування даних, компонент схеми 3 представляє собою, наприклад, накопичувач, що також служить для періодичного запам'ятовування даних, причому регістр 2 та накопичувач 3 підпорядковані також інтегрованому на напівпровідниковій основі мікропроцесору (схемі керування), причому цей мікропроцесор для наочності не показаний більш детально на фіг 1 та 2 Адресне кодування комірок пам'яті 10 13 здійснюється за допомогою 8 селективних числових шин 21, 21', 22, 22', 23, 23', 24, 24', що мають ВІДПОВІДНИЙ електричний зв'язок з адресним декодером 14 Крім показаних на фіг 1 компонентів схеми 2 5, можуть бути передбачені будь-які ІНШІ компоненти, керування якими також можна здійснювати за допомогою керуючого сигналу для переведення у стан установлення на нуль або стирання, причому замість існуючих даних записується значення логічного нуля За винаходом, для запуску процесу установлення на нуль (скидання) даних, записаних до всіх компонентів схеми, із записом до них значення логічного нуля передбачена схема запуску 25 з певною КІЛЬКІСТЮ послідовно підключених відпираючих каскадів 26, 27, 28, 29 ВІДПОВІДНО ДО КІЛЬ КОСТІ компонентів схеми, якими потрібно керувати, яка активізується автоматично Кожний відпираючий каскад охоплює вентильну схему, що складається з транзисторного ключа ЗО, 31, 32, 33 та запускаючого пристрою 38, 39, 40, 41, що запускає керуючий сигнал на входи для керування 34, 35, 36, 37 транзисторних ключів ЗО 33, причому на вхід цього запускаючого пристрою подається ВІДПОВІДНО сигнал пуску 42, 43, 44, 45 Якщо граничне значення сигналу запускаючого пристрою дорівнює ЛОГІЧНІЙ "одиниці", відкривається ВІДПОВІДНО керований транзисторний ключ ЗО 33, в той час, коли при рівні логічного "нуля" ВІДПОВІДНИЙ транзисторний ключ запирається Крім того, кожний відпираючий каскад 26 29 має перемикач дозволу 47, 48, 49, 50, що відпирається за допомогою відпираючого сигналу 53, поданого на ЛІНІЮ сигналу дозволу 52, як тільки сигнал дозволу досягне рівня логічної "одиниці", І, навпаки, запирається при рівні сигналу дозволу 53, що дорівнює логічному "нулю" Для активізації схеми запуску 25, тобто послідовного у часі запуску для скидання даних, записаних до всіх компонентів схеми 2 5, до значення логічного "нуля", сигнал дозволу встановлюється на рівень логічної "одиниці" При виставлянні сигналу дозволу 53 на рівень логічного "нуля" схема запуску 25 деактивується Схема запуску 25 за прикладом реалізації винаходу працює як описано нижче Для активізації 54418 10 схеми запуску 25 видається сигнал дозволу 53, тобто рівень сигналу дозволу 53 переводиться з логічного "нуля" на логічну "одиницю" і відкривається транзисторний ключ ЗО першого відпираючого каскаду 26 для запуску компонента схеми 2 За допомогою виданого транзисторним ключем ЗО відпираючого сигналу 6 спрацьовує регістр 4 і запускає процес скидання або стирання даних до значення логічного нуля Після цього на ЛІНІЮ 54 видається сигнал запускаючого пристрою 43, за допомогою якого активізується другий відпираючий каскад 27 схеми запуску 25, і стираються дані, записані у компоненті пристрою 43, за допомогою якого активізується другий відпираючий каскад 27 схеми запуску 25, і стираються дані, записані у компоненті схеми 3, до якої звертається другий відпираючий каскад 27 Другий відпираючий каскад 27 після цього видає сигнал запускаючого пристрою 46а на ЛІНІЮ 46 через логічну схему (елемент) "НЕ І" 62 та інвертор 63, що тепер відпирає всі відпираючі каскади 28 та 29 другої схеми запуску 25а для груп елементів пам'яті Завдяки такому типу запуску елементів пам'яті 10 13 через адресний декодер 14 завжди залишається активною одна комірка пам'яті 10 13 Для пояснення принципу функціонування складової частини схеми 25а далі уявимо, що спочатку адресний декодер опитує групу елементів пам'яті 4 Отже, до активних комірок пам'яті 12 та 13 записуються ЛОГІЧНІ значення з шини 20, подані на лінії даних від DB [0] до DB [7] При цьому вміст комірок пам'яті 12 та 13 автоматично замінюється нульовими значеннями, поданими на шину даних 20, що відповідає стиранню вмісту комірок пам'яті Після ЦЬОГО через ЛІНІЮ 51 до задавального пристрою 41 наступного відпираючого каскаду 29 подається наступний сигнал запускаючого пристрою 45, що відкриває транзисторний ключ 33 відпираючого каскаду 29 для видачі керуючого сигналу 9 Керуючий сигнал 9, у свою чергу, служить для запуску комірок пам'яті 12 та 13 компонента схеми 5, причому замість даних, що зберігаються у комірках пам'яті 12 та 13, записується нульове значення, подане на шину даних 20 Таким чином автоматично здійснюється послідовне адресування за групами всіх комірок пам'яті RAM 10, 11, 12, 13 компонентів схеми 4 та 5, і у них записується значення логічного "нуля", подане на шину даних 20 Послідовна у часі адресація комірок пам'яті 10 13 може здійснюватись дуже просто завдяки ієрархічно структурованій схемі декодера пристрою пам'яті RAM за допомогою схеми запуску 25а згідно з винаходом, так що передбачаються лише деякі додаткові ЛОГІЧНІ схеми, які можна реалізувати за допомогою простої схемотехніки Лише після того, як була здійснена адресація групи комірок пам'яті 10 та 11, тобто ВІДПОВІДНІ ЧИСЛОВІ ШИНИ знаходяться в активному стані, здійснюється адресація наступної групи комірок пам'яті 12 та 13 пристрою пам'яті RAM Таким чином забезпечується обмеження ємнісного навантаження на шину даних 20 Якщо, навпаки, всі комірки пам'яті 10 13 пристрою пам'яті RAM будуть відкриті одночасно, шина даних 20 повинна мати значно вищу потужність запускаючого пристрою, для того, щоб у 11 54418 найнесприятливому випадку можна було б швидко записати замість даних в усіх комірках пам'яті пристрою пам'яті RAM значення логічного "нуля" Безпосередньо після процесу стирання, що спричиняє запуск, на шину даних 20 подається певне значення, наприклад, на всі лінії даних шини даних подається значення логічного "нуля" 12 на вхід якого подається сигнал дозволу 53, і вентиль "НЕ АБО" 60, входи якого з'єднані з виходом інвертора 59 та виходом елемента "НЕ І" 58, а вихід якого за допомогою лінії 61 зв'язаний з адресним декодером 14 Цифрою 64, у свою чергу, позначені лінії, на які подані відпираючі сигнали для регістрів 2 та 3, а також селективні числові шини для комірок пам'яті пристрою пам'яті RAM 10 13 Після активізації схеми запуску 25, тобто коли сигнал дозволу 53 має рівень логічної "одиниці", всі лінії шини даних 20 переводяться на рівень логічного "нуля" Якщо у зв'язку з певними обставинами необхідна потужність запускаючого пристрою шини даних 20 виявиться недостатньою для того, щоб послідовно перекидати комірки пам'яті 10 13 пристрою пам'яті RAM, за допомогою схеми регулювання 55 припиняється процес відпирання або установлення на нуль комірок пам'яті у разі надто низької потужності запускаючого пристрою шини даних, і процес послідовної адресації продовжується лише тоді, коли рівень шини даних знову приймає стабільне значення логічного "нуля" На виході елемента "НЕ І" 58, таким чином, видається значення логічної "одиниці", якщо тільки одна ЛІНІЯ шини даних 20 приймає значення логічної "одиниці" При цьому на виході вентиля "НЕ АБО" 60 генерується сигнал із рівнем логічного "нуля" і через ЛІНІЮ 61 короткочасно відключає схему запуску 25, поки на шину даних 20 знову не буде подане значення логічного "нуля" Таким чином, через певний час схема запуску 25 знову автоматично починає працювати, причому сигнал дозволу 53, поданий на вхід інвертора 59 та на вхід схеми введення або виведення даних 19, ще має значення логічної "одиниці" Сигнал запускаючого пристрою, що видається останнім відпираючим каскадом 29, розташованим на КІНЦІ схеми запуску 25, знову подається на вхід відпираючого каскаду 26 На фіг 2 показані деталі схеми регулювання 55, підпорядкованої схемі запуску 25а, яка у разі збою керує новою активізацією схеми запуску 25, у тому разі, коли - наприклад, якщо час спрацьовування встановлений надто коротким - потужність запускаючого пристрою шини даних 20 виявляється недостатньою для того, щоб перевести регістр або комірку пам'яті пристрою пам'яті RAM на значення логічного "нуля", так що схема, що керує шиною даних, не має достатньої потужності запускаючого пристрою, тобто, незважаючи на те, що запуск компонентів схеми за допомогою запускаючого пристрою триває, на шині даних записуються "невірні", тобто такі, що відрізняються від нуля, значення Схема регулювання 55 у цьому разі слідкує за тим, щоб сигнал дозволу 53 для запуску схеми запуску 25 ще раз короткочасно мав рівень логічного "нуля", після чого переводився на рівень логічної "одиниці", І "ланцюг доміно" знову запускався у визначений момент Передбачена для цього схема регулювання 55 охоплює вентилі "НЕ АБО" 56, 57, входи яких з'єднані з ЛІНІЯМИ ШИНИ даних 20, елемент "НЕ І" 58, входи якого з'єднані з виходами вентилів "НЕ АБО" 56 та 57, інвертор 59, ШД17] \ Фіг.1 13 14 54418 Фіг.2 Підписано до друку 03 04 2003 р Тираж 39 прим ТОВ "Міжнародний науковий комітет" вул Артема, 77, м Київ, 04050, Україна (044)236-47-24

ДивитисяДодаткова інформація

Назва патенту англійськоюCircuit arrangement with a number of electronic circuit components

Назва патенту російськоюКомпоновка схемы, содержащей несколько электронных элементов

МПК / Мітки

МПК: G11C 11/407, G11C 7/00

Мітки: електронних, схемний, виконаний, компонентах, пристрій

Код посилання

<a href="https://ua.patents.su/7-54418-skhemnijj-pristrijj-vikonanijj-na-elektronnikh-komponentakh.html" target="_blank" rel="follow" title="База патентів України">Схемний пристрій, виконаний на електронних компонентах</a>

Попередній патент: 3-заміщені похідні піридо[4′,3′:4,5]тієно[2,3-d]піримідину

Наступний патент: Спосіб виготовлення корпусу ковша з вгнутим перерізом

Випадковий патент: Дерев`яна двотаврова клеєна балка