Цифровий оптоелектронний спецпроцесор

Номер патенту: 63651

Опубліковано: 10.10.2011

Автори: Заболотна Наталія Іванівна, Дроненко Олена Василівна, Шолота Владислав Васильович, Мусійчук Ірина Вікторівна

Формула / Реферат

Цифровий оптоелектронний спецпроцесор, що містить арифметико-логічний пристрій, який відрізняється тим, що в нього ввведено другий арифметико-логічний пристрій, тривходовий матричний комутатор, двовходовий матричний комутатор, п'ятивходовий матричний комутатор, семивходовий матричний комутатор, два групових матричних комутатори, чотири матричні регістри, матричний суматор за модулем два, паралельну матричну схему порівняння, затвор, блок просторового зсуву, комбінаційну схему та блок формування ознак, причому перші входи пристрою оптично з'єднані з інформаційними входами першого матричного регістра, а його другі входи оптично з'єднані з інформаційними входами четвертого матричного регістра, треті входи пристрою оптично з'єднані з інформаційними входами другого матричного регістра, а його четверті входи оптично з'єднані з інформаційними входами третього матричного регістра, виходи першого матричного регістра оптично з'єднані з відповідними входами першої групи другого групового матричного комутатора та з відповідними входами другої групи входів першого групового матричного комутатора, перший вихід першого регістра оптично з'єднаний з другим входом тривходового матричного комутатора та з третім входом блока формування ознак, а останній вихід першого регістра оптично з'єднаний з другим входом двовходового матричного комутатора, виходи четвертого регістра оптично з'єднуються з відповідними входами другої групи входів другого групового матричного комутатора, а також з відповідними входами третьої групи входів комбінаційної схеми, причому перший вихід четвертого регістра оптично з'єднаний з першим входом тривходового матричного комутатора та з четвертим входом блока формування ознак, а його останній вихід з першим входом двовходового матричного комутатора, вихід тривходового матричного комутатора оптично з'єднаний з другим входом першого арифметико-логічного пристрою, а вихід двовходового матричного комутатора оптично з'єднаний з першим входом першого арифметико-логічного пристрою, виходи першого арифметико-логічного пристрою є першими виходами пристрою, а також його перший вихід оптично з'єднаний з першим входом блока просторового зсуву, з другим входом блока формування ознак та з входом матричного суматора за модулем два, другий вихід першого арифметико-логічного пристрою оптично з'єднаний з першим входом блока формування ознак, виходи першого арифметико-логічного пристрою з другого по останній оптично з'єднані з відповідними входами першої групи входів першого групового матричного комутатора, виходи першого групового матричного комутатора оптично з'єднані з входами затвора та з першою групою входів комбінаційної схеми, виходи другого групового матричного комутатора оптично з'єднані з відповідними входами блока просторового зсуву, виходи затвора також оптично з'єднані з входами блока просторового зсуву, виходи якого оптично з'єднані з відповідними входами другої групи входів комбінаційної схеми, а виходи першої групи виходів комбінаційної схеми оптично з'єднані з входами першого арифметико-логічного пристрою з другого по останній відповідно, виходи другої групи виходів комбінаційної схеми оптично з'єднані з відповідними входами першого матричного регістра відповідно з другого по останній, виходи третьої групи виходів комбінаційної схеми оптично з'єднані з входами четвертого матричного регістра відповідно з другого по останній, перший вихід другого матричного регістра оптично з'єднаний з другим входом п'ятивходового матричного комутатора, а його останній вихід оптично з'єднаний з шостим входом семивходового матричного комутатора, перший інверсний вихід третього матричного регістра оптично з'єднаний з третім входом п'ятивходового матричного комутатора, останній вихід третього матричного регістра оптично з'єднаний з п'ятим входом семивходового матричного комутатора, вихід п'ятивходового матричного комутатора оптично з'єднаний з другим входом другого арифметико-логічного пристрою, вихід семивходового матричного комутатора оптично з'єднаний з першим входом другого арифметико-логічного пристрою, виходи другого арифметико-логічного пристрою є виходами пристрою, причому перший вихід арифметико-логічного пристрою оптично з'єднаний з п'ятим входом блока формування ознак, виходи другого арифметико-логічного пристрою оптично з'єднані з відповідними входами матричної схеми порівняння, перший вихід матричної схеми порівняння оптично з'єднаний з шостим входом комбінаційної схеми та восьмим входом блока формування ознак, перший вихід блока формування ознак оптично з'єднаний з п'ятим входом п'ятивходового матричного комутатора та першим входом семивходового матричного комутатора, другий вихід блока формування ознак оптично з'єднаний з дев'ятим входом комбінаційної схеми та третім входом семивходового матричного комутатора, третій вихід блока формування ознак оптично з'єднаний з десятим входом комбінаційної схеми та другим входом семивходового матричного та входом матричного суматора за модулем два, вихід якого оптично з'єднаний з третім входом тривходового матричного комутатора, четвертий вихід блока формування ознак оптично з'єднаний з одинадцятим входом комбінаційної схеми та третім входом другого групового матричного комутатора, п'ятий вихід блока формування ознак оптично з'єднаний з четвертим входом комбінаційної схеми та четвертим входом семивходового матричного комутатора, шостий вихід блока формування ознак оптично з'єднаний з п'ятим входом комбінаційної схеми, сьомий вихід блока формування ознак оптично з'єднаний з шостим входом комбінаційної схеми, з сьомим входом семивходового матричного комутатора та четвертим входом п'ятивходового матричного комутатора, восьмий вихід блока формування ознак оптично з'єднаний з сьомим входом комбінаційної схеми та першим входом п'ятивходового матричного комутатора.

Текст

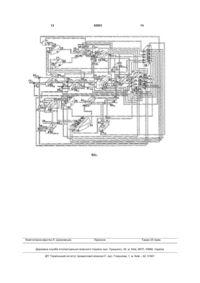

Цифровий оптоелектронний спецпроцесор, що містить арифметико-логічний пристрій, який відрізняється тим, що в нього введено другий арифметико-логічний пристрій, тривходовий матричний комутатор, двовходовий матричний комутатор, п'ятивходовий матричний комутатор, семивходовий матричний комутатор, два групових матричних комутатори, чотири матричні регістри, матричний суматор за модулем два, паралельну матричну схему порівняння, затвор, блок просторового зсуву, комбінаційну схему та блок формування ознак, причому перші входи пристрою оптично з'єднані з інформаційними входами першого матричного регістра, а його другі входи оптично з'єднані з інформаційними входами четвертого матричного регістра, треті входи пристрою оптично з'єднані з інформаційними входами другого матричного регістра, а його четверті входи оптично з'єднані з інформаційними входами третього матричного регістра, виходи першого матричного регістра оптично з'єднані з відповідними входами першої групи другого групового матричного комутатора та з відповідними входами другої групи входів першого групового матричного комутатора, перший вихід першого регістра оптично з'єднаний з другим входом тривходового матричного комутатора та з третім входом блока формування ознак, а останній вихід першого регістра оптично з'єднаний з другим входом двовходового матричного комутатора, виходи четвертого регістра оптично з'єднуються з відповідними входами другої групи входів другого групового матричного комутатора, а також з відповідними входами третьої групи входів комбінаційної схеми, причому перший вихід четвертого регістра оптично з'єднаний з першим входом тривходового матричного комутатора та з четвертим входом блока формування ознак, а його останній вихід з першим входом двовходового матричного комутатора, вихід тривходового мат 2 (19) 1 3 63651 4 логічного пристрою, виходи другого арифметикологічного пристрою є виходами пристрою, причому перший вихід арифметико-логічного пристрою оптично з'єднаний з п'ятим входом блока формування ознак, виходи другого арифметико-логічного пристрою оптично з'єднані з відповідними входами матричної схеми порівняння, перший вихід матричної схеми порівняння оптично з'єднаний з шостим входом комбінаційної схеми та восьмим входом блока формування ознак, перший вихід блока формування ознак оптично з'єднаний з п'ятим входом п'ятивходового матричного комутатора та першим входом семивходового матричного комутатора, другий вихід блока формування ознак оптично з'єднаний з дев'ятим входом комбінаційної схеми та третім входом семивходового матричного комутатора, третій вихід блока формування ознак оптично з'єднаний з десятим входом комбінаційної схеми та другим входом семивходового матрично го та входом матричного суматора за модулем два, вихід якого оптично з'єднаний з третім входом тривходового матричного комутатора, четвертий вихід блока формування ознак оптично з'єднаний з одинадцятим входом комбінаційної схеми та третім входом другого групового матричного комутатора, п'ятий вихід блока формування ознак оптично з'єднаний з четвертим входом комбінаційної схеми та четвертим входом семивходового матричного комутатора, шостий вихід блока формування ознак оптично з'єднаний з п'ятим входом комбінаційної схеми, сьомий вихід блока формування ознак оптично з'єднаний з шостим входом комбінаційної схеми, з сьомим входом семивходового матричного комутатора та четвертим входом п'ятивходового матричного комутатора, восьмий вихід блока формування ознак оптично з'єднаний з сьомим входом комбінаційної схеми та першим входом п'ятивходового матричного комутатора. Корисна модель відноситься до обчислювальної техніки і може бути використаний для паралельної арифметико-логічної обробки багаторівневих зображень за просторово-неперервними розрядними зрізами. Відомо цифровий оптоелектронний процесор для обробки зображень в просторово-неперервній формі [Очин Е.Ф. Принципы организации цифрового оптоэлектронного процессора для обработки изображений в пространственно-непрерывной форме. - Электронное моделирование. - 1984. № 3. - С. 16-19], що містить голографічний оперативний запам'ятовувальний пристрій, регістр зсуву, просторово-логічний пристрій та накопичувальний регістр, причому оптичний вихід голографічного оптичного запам'ятовувального пристрою через регістр зсуву з'єднаний з оптичним входом просторово-логічного пристрою, оптичний вихід якого через накопичувальний регістр підключений до оптичних входів голографічного оперативного запам'ятовувального пристрою і просторовологічного пристрою, крім того входи управління пристрою підключені відповідно до адресних входів і входів управління записом і зчитуванням голографічного оперативного запам'ятовувального пристрою, до входів управління зсувом по координатах х, у регістра зсуву і до входів управління мікроопераціями просторово-логічного пристрою. Недоліком відомого процесора є обмежені функціональні можливості, оскільки просторовологічний пристрій процесора виконує лише функціонально повний набір логічних операцій над дворівневими зображеннями. Відомо цифровий оптоелектронний процесор багаторівневих зображень за просторовонеперервними розрядними зрізами [Денисов В.М. и др. Структура цифрового оптоэлектронного процессора многоуровневых изображений по пространственно-непрерывным разрядным срезам // Электронное моделирование.-1984. - № 6. - С. 99101, рис. 1], що містить лазер, два запам'ятовува льні пристрої, пристрій управління, два модулятора, чотири дефлектора і операційний автомат, що містить два дефлектора, суматор та аналоговоцифровий перетворювач, причому лазер оптично через перший модулятор з'єднаний через перший і другий дефлектори з входами першого і другого запам'ятовувальних пристроїв відповідно, а через другий модулятор - з аналогово-цифровим перетворювачем, перший і другий виходи якого з'єднані оптично через третій і четвертий дефлектори з входами першого і другого запам'ятовувальних пристроїв, виходи яких оптично з'єднані через п'ятий і шостий дефлектори відповідно з входами суматора, вихід якого оптично підключений до входу аналогово-цифрового перетворювача, перший, другий, третій, четвертий і п'ятий входи пристрою управління електрично підключені до входів управління двох модуляторів, першого і другого дефлекторів, п'ятого і шостого дефлекторів, третього і четвертого дефлекторів і аналогоцифрового перетворювача відповідно. Недоліком відомого процесора є обмежені функціональні можливості, оскільки пристрій виконує операції підсумовування без урахування знака. Найбільш близьким за технічною суттю є цифровий оптоелектронний процесор багаторівневих зображень [Патент України № 23431А, МКІ G06F15/66,G06E 1/04. Опубл. 02.06.98, Бюл. № 4.] що містить два запам'ятовувальні пристрої, пристрій керування, суматор, логічний блок, перший і другий елементи пам'яті картинного типу, причому запам'ятовувальний пристрій і суматор є пристроями картинного типу, виходи першого і другого запам'ятовувальних пристроїв з'єднані оптично з першим і другим входами логічного блока, третій, четвертий, п'ятий і шостий входи якого з'єднані оптично з прямими та інверсними входами першого і другого елемента пам'яті відповідно, а перший, другий, третій і четвертий виходи оптично підключені до входу першого доданка і входу переносу суматора, інформаційного виходу пристрою та 5 інформаційного входу другого елемента пам'яті відповідно, вхід другого доданка суматора оптично з'єднаний з оптично з'єднаний з виходом другого запам'ятовувального пристрою, а вихід суми і вихід переносу суматора оптично підключені до входу другого запам'ятовувального пристрою і сьомого входу логічного блока відповідно, інформаційний вхід пристрою і вхід матриці знаків операндів пристрою з'єднані оптично з входами першого запам'ятовувального пристрою і першого елемента пам'яті відповідно, а вихід результуючої матриці знаків пристрою підключений оптично до прямого виходу другого елемента пам'яті, перший і другий виходи пристрою керування підключені до управляючих входів першого елемента пам'яті, третій та четвертий виходи - до управляючих входів логічного блока, п'ятий та шостий виходи - до управляючих входів другого елемента пам'яті, сьомий та восьмий виходи - до управляючих входів першого та другого запам'ятовувальних пристроїв відповідно, в подальшому цифровий оптоелектронний процесор багаторівневих зображень названо арифметико-логічним пристроєм. Недоліком відомого пристрою є обмежені функціональні можливості, оскільки процесор виконує операцію паралельного додавання лише знакозмінних цілочисельних матриць. В основу корисної моделі поставлено задачу створення цифрового оптоелектронного спецпроцесора, в якому за рахунок введення нових елементів та зв'язків досягається можливість виконання операції паралельного додавання матриць, елементи яких подані у формі з плаваючою комою, що приводить до розширення діапазону вхідних чисел, збільшення точності пристрою і за рахунок цього розширення функціональних можливостей та області застосування цифрового оптоелектронного спецпроцесора. Поставлена задача вирішується тим, що в цифровий оптоелектронний спецпроцесор, що містить арифметико-логічний пристрій згідно винаходу введено другий арифметико-логічний пристрій, тривходовий матричний комутатор, двовходовий матричний комутатор, п'ятивходовий матричний комутатор, семивходовий матричний комутатор, два групових матричних комутатора, чотири матричні регістри, матричний суматор за модулем два, паралельну матричну схему порівняння, затвор, блок просторового зсуву, комбінаційну схему та блок формування ознак, причому перші входи пристрою оптично з'єднані з інформаційними входами першого матричного регістра, другі входи пристрою оптично з'єднані з інформаційними входами четвертого матричного регістра, треті входи пристрою оптично з'єднані з інформаційними входами другого матричного регістра, а четверті входи пристрою оптично з'єднані з інформаційними входами третього матричного регістра, виходи першого матричного регістра оптично з'єднані з відповідними входами першої групи другого групового матричного комутатора та з відповідними входами другої групи входів першого групового матричного комутатора, перший вихід першого регістра оптично з'єднаний з другим входом тривходового матричного комутатора та з третім вхо 63651 6 дом блока формування ознак, а останній вихід першого регістра оптично з'єднаний з другим входом двовходового матричного комутатора, виходи четвертого регістра оптично з'єднуються з відповідними входами другої групи входів другого групового матричного комутатора, а також з відповідними входами третьої групи входів комбінаційної схеми, причому перший вихід четвертого регістра оптично з'єднаний з першим входом тривходового матричного комутатора та з четвертим входом блока формування ознак, а його останній вихід з першим входом двовходового матричного комутатора, вихід тривходового матричного комутатора оптично з'єднаний з другим входом першого арифметико-логічного пристрою, а вихід двовходового матричного комутатора оптично з'єднаний першим входом першого арифметико-логічного пристрою, виходи першого арифметико-логічного пристрою є першими виходами пристрою, а також його перший вихід оптично з'єднаний з першим входом блока просторового зсуву, з другим входом блока формування ознак та з входом матричного суматора за модулем два, другий вихід першого арифметико-логічного пристрою оптично з'єднаний з першим входом блока формування ознак, виходи першого арифметико-логічного пристрою з другого по останній оптично з'єднані з відповідними входами першої групи входів першого групового матричного комутатора, виходи першого групового матричного комутатора оптично з'єднані з входами затвора та з першою групою входів комбінаційної схеми, виходи другого групового матричного комутатора оптично з'єднані з відповідними входами блока просторового зсуву, виходи затвора також оптично з'єднані з входами блока просторового зсуву, виходи якого оптично з'єднані з відповідними входами другої групи входів комбінаційної схеми, а виходи першої групи виходів комбінаційної схеми оптично з'єднані з входами першого арифметико-логічного пристрою з другого по останній відповідно, виходи другої групи виходів комбінаційної схеми оптично з'єднані з відповідними входами першого матричного регістра відповідно з другого по останній, виходи третьої групи виходів комбінаційної схеми оптично з'єднані з входами четвертого матричного регістра відповідно з другого по останній, перший вихід другого матричного регістра оптично з'єднаний з другим входом п'ятивходового матричного комутатора, а його останній вихід оптично з'єднаний з шостим входом семивходового матричного комутатора, перший інверсний вихід третього матричного регістра оптично з'єднаний з третім входом п'ятивходового матричного комутатора, останній вихід третього матричного регістра оптично з'єднаний з п'ятим входом семивходового матричного комутатора, вихід п'ятивходового матричного комутатора оптично з'єднаний з другим входом другого арифметикологічного пристрою, вихід семивходового матричного комутатора оптично з'єднаний з першим входом другого арифметико-логічного пристрою, виходи другого арифметико-логічного пристрою є виходами пристрою, причому перший вихід арифметико-логічного пристрою оптично з'єднаний з п'ятим входом блока формування ознак, виходи 7 другого арифметико-логічного пристрою оптично з'єднані з відповідними входами матричної схеми порівняння, перший вихід матричної схеми порівняння оптично з'єднаний з шостим входом комбінаційної схеми та восьмим входом блока формування ознак, перший вихід блока формування ознак оптично з'єднаний з п'ятим входом п'ятивходового матричного комутатора та першим входом семивходового матричного комутатора, другий вихід блока формування ознак оптично з'єднаний з дев'ятим входом комбінаційної схеми та третім входом семивходового матричного комутатора, третій вихід блока формування ознак оптично з'єднаний з десятим входом комбінаційної схеми та другим входом семивходового матричного та входом матричного суматора за модулем два, вихід якого оптично з'єднаний з третім входом три входового матричного комутатора, четвертий вихід блока формування ознак оптично з'єднаний з одинадцятим входом комбінаційної схеми та третім входом другого групового матричного комутатора, п'ятий вихід блока формування ознак оптично з'єднаний з четвертим входом комбінаційної схеми та четвертим входом семивходового матричного комутатора, шостий вихід блока формування ознак оптично з'єднаний з п'ятим входом комбінаційної схеми, сьомий вихід блока формування ознак оптично з'єднаний з шостим входом комбінаційної схеми, з сьомим входом семивходового матричного комутатора та четвертим входом п'ятивходового матричного комутатора, восьмий вихід блока формування ознак оптично з'єднаний з сьомим входом комбінаційної схеми та першим входом п'ятивходового матричного комутатора. На кресленні представлено структурну схему цифрового оптоелектронного спецпроцесора. Цифровий оптоелектронний спецпроцесор містить арифметико-логічний пристрій (АЛП) 11. Крім того пристрій містить арифметико-логічний пристрій (АЛП) 9, тривходовий матричний комутатор (МК-3) 5, двовходовий матричний комутатор (МК-2) 6, п'ятивходовий матричний комутатор (МК5) 7, семивходовий матричний комутатор (МК-7) 10, два групових матричних комутатора (ГМК) 12, 13, чотири матричних регістри (Рг) 2, 3, 4, 8, матричний суматор за модулем два 1, паралельну матричну схему порівняння (МСП) 14, затвор (Зт) 15, блок просторового зсуву (БЗС) 16, комбінаційну схему (КС) 17 та блок формування ознак (БФО) 18. Причому, цифровий оптоелектронний спецпроцесор містить входи 19(0)…19(М), 20(0)…20(М), 19(М+1)…19(М+Р+1), 20(М+1)…20(М+Р+1) пристрою, які є відповідно входами розрядних зрізів мантис першого та другого операндів та порядків першого та другого операндів відповідно, та виходи 47(0)…47(М), 48(0)…48(Р) пристрою, що є виходами розрядних зрізів мантиси та порядку результату додавання відповідно. Входи 19(0)…19(М) пристрою оптично з'єднані з інформаційними входами Рг 2, входи 20(0)…20(М) пристрою оптично з'єднані з інформаційними входами Рг 8, входи 19(М+1)…19(М+Р+1) пристрою оптично з'єднані з інформаційними входами Рг 3, входи 20(М+1)…20(М+Р+1) пристрою оптично з'єднані з інформаційними входами Рг 4. Виходи 29(1)…29(М) Рг 63651 8 2 оптично з'єднані з входами 511(0)…511(М-1) ГМК 13 та з входами 492(0)…492(М-1) ГМК 12, вихід 29(0) Рг 2 оптично з'єднаний з входом 23 МК-3 5 та з входом 61 БФО 18, вихід 29(М) оптично з'єднаний з входом 27 МК-2 6. Виходи 30(1)…30(М) Рг 8 оптично з'єднані з входами 512(0)…512(М-1) ГМК 13, а також з входами 573(0)…573(М-1) КС 17, вихід 30(0) Рг 8 оптично з'єднаний з входом 22 МК-3 5 та входом 62 БФО 18, а вихід 30(М) з входом 26 МК-2 6. Вихід 25 МК-3 5 оптично з'єднаний з входом 45(0) АЛП 9, а вихід 28 МК-2 6 оптично з'єднаний з входом 45 АЛП 9. Вихід 47(0) АЛП 9 оптично з'єднаний з входом 56 БЗС 16 та з входом 60 БФО 18, вихід 47(1) АЛП 9 оптично з'єднаний з входом 59 БФО 18 та з входом матричного суматора за модулем два 1, виходи 47(1)…47(М) АЛП 9 оптично з'єднані з відповідними входами 491(0)…491(М-1) ГМК 12. Виходи 50(0)…50(М-1) ГМК 12 оптично з'єднані з входами Зт 20 та з входами 571(0)…571(М-1) КС 17. Виходи 52(0)…52(М-1) ГМК 13 оптично з'єднані з входами 56(0)…56(М-1) БЗС 16, виходи 55(0)…55(М-1) Зт 15 оптично з'єднані з входами 56(0)…56(М-1) БЗС 16. Виходи БЗС 16 оптично з'єднані з входами 572(0)…572(М-1) КС 17. Виходи 581(0)…581(М-1) КС 17 оптично з'єднані з входами 45(1)…45(М) АЛП 9, виходи 582(0)…582(М-1)… КС 17 оптично з'єднані з входами 19(1)…19(М) Рг 2, виходи 583(0)…583(М-1) КС 17 оптично з'єднані з входами 20(1)…20(М) Рг 8. Вихід 29(М+1) Рг 3 оптично з'єднаний з входом 32 МК-5 7, вихід 29(М+Р+1) Рг 3 оптично з'єднаний з входом 42 МК-7 10. Вихід 30(М+1) Рг 4 оптично з'єднаний з входом 33 МК-5 7, вихід 30(М+Р+1) оптично з'єднаний з входом 41 МК-7 10. Вихід 36 МК-5 7 оптично з'єднаний з входом 46(0) АЛП 11, вихід 44 МК-7 10 оптично з'єднаний з входом 46 АЛП 11. Виходи 48(0)…48(Р) АЛП 11 є виходами пристрою, також вихід 48(0) оптично з'єднаний з входом 63 БФО 18, виходи 48(0)…48(Р) АЛП 11 оптично з'єднані з відповідними входами 53(0)…53(Р) МСП 14. Вихід 54(0) МСП 14 оптично з'єднаний з входом 77 КС 17 та входом 72 БФО 18. Вихід 64 БФО 18 оптично з'єднаний з входом 35 МК-5 7 та входом 37 МК-810, Вихід 65 БФО 18 оптично з'єднаний з входами 78 КС 17 і входом 39 МК-7 10. Вихід 66 БФО 18 оптично з'єднаний з входом матричного суматора за модулем два 1, вихід 21 якого оптично з'єднаний з входом 24 МК-3 5, з входом 79 КС 17 та входом 38 МК-7 10. Вихід 67 БФО 18 оптично з'єднаний з входом 80 КС 17 та входом 513 ГМК 13. Вихід 68 БФО 18 оптично з'єднаний з входом 73 КС 17 та входом 40 МК-7 10. Вихід 69 БФО 18 оптично з'єднаний з входом 74 КС 17. Вихід 70 БФО 18 оптично з'єднаний з входом 75 КС 17, входом 43 МК-7 10 і входом 34 МК-5 7. Вихід 71 БФО 18 оптично з'єднаний з входом 76 КС 17, входом 5Ц ГМК 13 та входом 31 МК-5 7. Цифровий оптоелектронний спецпроцесор працює наступним чином. Оскільки додавати числа з різними порядками не можна, то спочатку треба прирівняти порядки доданків: менший порядок збільшити до більшого, а мантису числа, над яким виконується перетворення, зсунути вправо на відповідну кількість розрядів. Для цього необхідно відняти порядки операндів, що можна реалізувати як додавання, 9 попередньо змінивши знак порядку другого операнда на протилежний. Це виконується наступним чином. На інформаційні входи 19(М+2)…19(М+Р+1) Рг 3 і 20(М+2)…20(М+Р+1) Рг 4 паралельно поступають розрядні зрізи (РЗ) порядків першого та другого операндів і записуються у відповідних регістрах зсуву. Одночасно з цим на знакові входи 19(М+1) Рг 3 І 20(М+1) Рг 4 поступають знакові РЗ порядків першого та другого операндів. Після цього зі знакового виходу 29(М+1) Рг 3 і інверсного знакового виходу 29(М+1) Рг 4 на входи 32 і 33 МК-5 7 надходять знакові РЗ порядків першого та другого операндів відповідно, з виходу 36 якого на знаковий вхід 46(0) АЛП 11 поступає знаковий РЗ порядку першого операнда. Одночасно з цим, з виходу 29(М+Р+1) Рг 3 на вхід 42 МК-7 10 поступають чергові РЗ порядку першого операнда починаючи з молодшого, які з виходу 44 МК-7 10 поступають на інформаційний вхід 46 АЛП 11. В наступний момент часу з виходу 36 МК-5 7 на знаковий вхід 46(0) АЛП 11 поступає знаковий РЗ порядку другого операнда. Одночасно з цим, з виходу 30(М+Р+1) Рг 4 на вхід 41 МК-7 10 поступають чергові РЗ порядку другого операнда починаючи з молодшого, які з виходу 44 МК-7 10 поступають на інформаційний вхід 46 АЛП 11, де відбувається безпосереднє віднімання порядків операндів. Результат віднімання формується в доповняльному коді на виходах 48(0))…48(Р) АЛП 11, з яких він поступає на входи 53(0)…53(Р) МСП 14, на виході 54(0) якого формується ознака рівності порядків операндів, яка надходить на вхід 77 КС 17, а також на вхід 72 БФО 18, на виході 68 якого утворюється ознака нерівності порядків операндів, що надходить з виходу 68 БФО 18 на вхід 73 КС 17, а також на вхід 40 МК-7 10. Крім того знаковий РЗ результату віднімання порядків операндів поступає з виходу 48(0) АЛП 11 на вхід 63 БФО 18, на виході 67 якого формується ознака переваги порядку першого операнда, а на виході 71 БФО 18 формується ознака переваги порядку другого операнда. Одночасно з записом порядків операндів в Рг 3 і Рг 4 на інформаційні входи 19(1)… 19(М) Рг 2 і 20(1)…20(М) Рг 8 паралельно поступають РЗ мантис першого та другого операндів і записуються у відповідних паралельних регістрах. Одночасно з цим на знакові входи 19(0) Рг 2 і 20(0) Рг 8 поступають знакові РЗ порядків першого та другого операндів. Далі інформаційні РЗ першого та другого операндів з виходів 29(1)…29(М) Рг 2 і 30(1)…30(М) Рг 8 поступають відповідно на входи 511(0)…511(М-1) та 512(0)…512(М-1) ГМК 13, на виходах 521(0)…521(М-1) якого формуються РЗ з елементів мантис операндів, які будуть зсунуті, відповідно до ознаки переваги першого операнда, що надходить на вхід 51 3 ГМК 13 з виходу 67 БФО 18 та ознаки переваги другого операнда, яка поступає на вхід 5Ц ГМК 13 з виходу 71 БФО 18. Ці РЗ поступають на входи 56(0)…56(М-1) БЗС 16, на виходах якого формуються вже зсунуті вправо РЗ елементів мантис відповідних операндів, що поступають на входи 572(0)…572(М-1) КС 17, на входи 573(0)…573(М-1) якого з виходів 30(1)…30(М) Рг 8 поступають РЗ мантис другого операнда, а з виходів 29(1)…29(М) Рг 2 РЗ мантис першого операнда поступають на входи 63651 10 49(0)…49(М-1) ГМК 12, з виходів 50(0)…50(М-1) якого поступають на входи 571(0)…571(М-1) КС 17. Відповідно до ознаки рівності порядків операндів, що надходить на вхід 77 КС 17 з виходу 54(0) МСП 14, ознаки нерівності порядків операндів, що надходить на вхід 73 КС 17 з виходу 68 БФО 18, ознаки переваги порядку першого операнда, що надходить на вхід 80 КС 17 з виходу 67 БФО 18, та ознаки переваги порядку другого операнда, що надходить на вхід 76 КС 17 з виходу 71 БФО 18, на виходах 582(0)…582(М-1) КС 17 з'являються РЗ мантиси першого операнда, елементи якого зсунуті вправо на один розряд, де це необхідно за даних ознак, а на виходах 583(0)…583(М-1) КС 17 РЗ мантиси другого операнда, елементи якого сформовані аналогічним чином. З виходів 582(0)…582(М-1) КС 17 новоутворені РЗ мантиси першого операнда поступають на входи 19(1)…19)(M) Рг 2, а з виходів 583(0)…583(М-1) КС 17 новоутворені РЗ мантиси першого операнда поступають на входи 20(1)…201(М) Рг 8, де зберігаються до наступного етапу. Разом із зсувом мантис операндів, зменшуємо різницю порядків операндів на одиницю. Для цього на вхід 40 МК-7 10 з виходу 68 БФО 18 поступає ознака нерівності порядків операндів, що з виходу 44 МК-7 10 поступає на вхід 46 АЛП 11 та відповідно зсувається в ньому до молодшого РЗ за Р тактів, після чого з виходу 44 МК-7 10 на знаковий вхід 46 АЛП 11 подається знаковий РЗ різниці порядків. Після цього на виходах 48(0)…48(Р) АЛП 11 формується нова різниця порядків операндів. Таким чином, вся вищеописана процедура повторюється, поки всі елементи ознаки рівності порядків не стануть одиницями, тоді з виходу 64 БФО 18 на вхід 37 МК-7 10 та на вхід 35 МК-5 7 подається знаковий РЗ різниці порядків, що надійшов на вхід 63 БФО 18 зі знакового виходу 48(0) АЛП 11 та був збережений у БФО 18. Відповідно до цього знакового РЗ різниці порядків на виході 44 МК-7 10, починаючи з молодшого, формуються чергові інформаційні РЗ загального порядку двох операндів, які складаються з елементів порядку першого або другого операндів, що мають більше значення, та подаються на вхід 46 АЛП 11. Аналогічним чином відповідно до знакового РЗ різниці порядків на знаковий вхід 46(0) АЛП 11 з виходу 36 МК-5 7 подається знаковий РЗ загального порядку двох операндів, що складається відповідно з більших значень елементів першого та другого операндів. Так завершується перший етап додавання, тобто вирівнювання порядків: збільшено менші елементи порядку операндів до більшого значення та записано в АЛП 11, а їх мантиси зсунуто на відповідну кількість розрядів та перезаписано в Рг 2 та Рг 8. Другий етап додавання полягає в безпосередньому додаванню мантис операндів. Для цього зі знакового виходу 29(0) Рг 2 на вхід 23 МК-3 5 надходить знаковий РЗ мантиси першого операнда, на вхід 22 якого зі знакового виходу 30(0) Рг 8 надходить знаковий РЗ мантиси другого операнда. З виходу 25 МК-3 5 знаковий РЗ першого операнда поступає на знаковий вхід 45(0) АЛП 9. Одночасно з цим, на вхід 27 МК-2 6 з інформаційного виходу 11 29(М) Рг 2 поступають чергові РЗ мантиси першого операнда починаючи з молодшого, які з виходу 28 МК-2 6 поступають на інформаційний вхід 45 АЛП 9. В наступний момент часу з виходу 25 МК-3 5 на знаковий вхід 45(0) АЛП 9 поступає знаковий РЗ мантиси другого операнда. Одночасно з цим, з виходу 30(М) Рг 8 на вхід 26 МК-2 6 поступають чергові РЗ мантиси другого операнда починаючи з молодшого, які з виходу 28 МК-2 6 поступають на інформаційний вхід 45 АЛП 9, де відбувається безпосереднє додавання мантис операндів. Результат додавання формується в доповняльному коді на виходах 47(0)…47(Р) АЛП 9. Оскільки при додаванні може виникнути переповнення розрядної сітки, тобто денормалізація ліворуч, зі знакового виходу 47(0) АЛП 9 на вхід 60 БФО 18 поступає знаковий РЗ суми мантис операндів, на входи 59 та 62 якого поступають зі знакових виходів 29 (0) Рг 2 та ЗСЦ Рг 8 знакові РЗ першого та другого операндів відповідно. Відповідно до цих РЗ на виході 66 БФО 18 формується пряма ознака денормалізації ліворуч, а на виході 69 БФО 18 - інверсна ознака денормалізації ліворуч. Для корегування РЗ суми мантис операндів, з виходу 66 БФО 18 на перший вхід матричного суматора за модулем два подається пряма ознака денормалізації ліворуч, на другий вхід якого зі знакового виходу 47 (0) АЛП 9 подається знаковий РЗ сформованої суми мантис операндів. З виходу 21 матричного суматора за модулем два скорегований знаковий РЗ суми мантис операндів поступає на вхід 24 МК-3 5, з виходу 25 якого знову поступає на знаковий вхід 45(0) АЛП 9. Одночасно з записом скорегованого знакового РЗ суми мантис операндів в АЛП 9, з Його виходів 47(1)…47(М) на входи 491(0)…491(М-1) ГМК 12 поступають інформаційні РЗ суми мантис операндів, з виходів 50(0)…50(М-1) якого вони поступають на входи 571(0)…571(М-1) КС 17, а також на входи Зт 15, з виходів 55(0)…55(М-1) якого поступають на входи 56(0)…56(М-1) БЗС 16, на вхід 56 якого зі знакового виходу 47(0) АЛП 9 поступає знаковий РЗ суми мантис операндів. В БЗС 16 вони відповідно зсуваються на 1 РЗ вправо, а зсунуті РЗ суми мантис операндів з виходів БЗС 16 поступають на входи 572(0)…572(М-1) КС 17. Відповідно до прямої та інверсної ознак денормалізації ліворуч, що поступають на входи 79 та 74 КС 17 з виходів 66 та 69 БФО 18 відповідно, на виходах 581(0)…581(М-1) КС 17 формуються РЗ суми мантис операндів, що складається з елементів попередньо отриманої суми мантис операндів та елементів, зсунутих на 1 РЗ вправо. З виходів 581(0)…581(М-1) КС 17 вони подаються на входи 45(1)…45(М) АЛП 9, де перетворюються з доповняльного в прямий код, що формується на виходах 47(0)…47(М) АЛП 9. 63651 12 Оскільки ми зсуваємо вправо елементи мантис операндів, то необхідно порядки відповідних елементів операндів збільшити на одиницю. Для цього з виходу 66 БФО 18 на вхід 38 МК-7 10 подається пряма ознака денормалізації ліворуч, яка з виходу 44 МК-7 10 поступає на вхід 46 АЛП 11, де зсувається до наймолодшого розряду та додається до записаного там загального порядку операндів. Одночасно з цим з виходу 47(1) АЛП 9 старший РЗ отриманої в прямому коді суми мантис операндів поступає на вхід 59 БФО 18, на виході 65 якого формується пряма ознака денормалізації праворуч, а на виході 70 БФО 18 - інверсна ознака денормалізації праворуч. Для нормалізації елементів суми мантис операндів з виходів 47(1)…47(М) АЛП 9 на входи 491(0)…491(М-1) ГМК 12 поступають інформаційні РЗ суми мантис операндів, з виходів 50(0)…50(М-1) якого вони поступають на входи 571(0)…571(М-1) КС 17, а також на входи Зт 15, з виходів 55(0)…55(М-1) якого поступають на входи 56(0)…56(М-1) БЗС 16, на вхід 56 якого зі знакового виходу 47(0) АЛП 9 поступає знаковий РЗ суми мантис операндів. В БЗС 16 вони відповідно зсуваються на 1 РЗ вліво, а зсунуті РЗ суми мантис операндів з виходів БЗС 16 поступають на входи 572(0)…572(М-1) КС 17. Відповідно до прямої та інверсної ознак денормалізації праворуч, що поступають на входи 78 та 75 КС 17 з виходів 65 та 70 БФО 18 відповідно, на виходах 581(0)…581(М-1) КС 17 формуються РЗ суми мантис операндів, що складається з елементів попередньо отриманої суми мантис операндів та елементів, зсунутих на 1 РЗ вліво. З виходів 581(0)…581(М-1) КС 17 вони подаються на входи 45(1)…45(М) АЛП 9. Оскільки ми зсуваємо вліво елементи мантис операндів, то необхідно порядки відповідних елементів операндів зменшити на одиницю. Для цього з виходу 70 БФО 18 на вхід 34 МК-5 7 подається інверсна ознака денормалізації праворуч, яка з виходу 36 МК-5 7 поступає на знаковий вхід 46(0) АЛП 11. Крім того, інверсна ознака денормалізації праворуч з виходу 70 БФО 18 подається на вхід 43 МК-7 10, з виходу 44 якого подається на вхід 46 АЛП 11, де зсувається до наймолодшого розряду. Таким чином в АЛП 11 відбувається зменшення відповідних елементів порядків на одиницю. Процедура повторюється до тих пір, поки не буде нормалізовано всі елементи мантиси суми, або поки не переберемо всі РЗ. Таким чином, на виходах пристрою ми отримаємо результат додавання, у вигляді набору РЗ порядку суми, сформованого в прямому коді на виходах 48(0)…48(Р) АЛП 11 та набору РЗ мантиси суми, сформованого в прямому коді на виходах 47(0)…47(М) АЛП 9. 13 Комп’ютерна верстка Л. Ціхановська 63651 Підписне 14 Тираж 23 прим. Державна служба інтелектуальної власності України, вул. Урицького, 45, м. Київ, МСП, 03680, Україна ДП “Український інститут промислової власності”, вул. Глазунова, 1, м. Київ – 42, 01601

ДивитисяДодаткова інформація

Назва патенту англійськоюDigital optoelectronic special-purpose processor

Автори англійськоюZabolotna Nataliia Ivanivna, Sholota Vladyslav Vasyliovych, Musiichuk Iryna Viktorivna, Dronenko Olena Vasylivna

Назва патенту російськоюЦифровой оптоэлектронный спецпроцессор

Автори російськоюЗаболотная Наталия Ивановна, Шолота Владислав Васильевич, Мусийчук Ирина Викторовна, Дроненко Елена Васильевна

МПК / Мітки

МПК: G06F 15/00

Мітки: спецпроцесор, цифровий, оптоелектронний

Код посилання

<a href="https://ua.patents.su/7-63651-cifrovijj-optoelektronnijj-specprocesor.html" target="_blank" rel="follow" title="База патентів України">Цифровий оптоелектронний спецпроцесор</a>

Попередній патент: Система вентиляції та рекуперації тепла житлових та промислових будівель

Наступний патент: Сенсор магнітної індукції

Випадковий патент: Застосування мезопрогестинів j 867, j 1042 або j 912 для жіночої контрацепції, фармацевтична композиція та набір (варіанти)