Цифро-аналоговий перетворювач

Номер патенту: 24660

Опубліковано: 04.08.1998

Автори: Биков Валентин Іванович, Лукашенко Валентина Максимівна, Лукашенко Андрій Германович

Формула / Реферат

Цифроаналоговый преобразователь, содержащий операционный усилитель, резисторную матрицу типа R-2R, резистор обратной связи, шины питания, шину общего потенциала, шину опорного напряжения, n-разрядные ячейки, причем каждая разрядная ячейка содержит входную разрядную шину, защитный диод, первый и второй МДП-ключи, транзистор сброса, управляющий транзистор, причем выход защитного диода подключен к шине общего потенциала, каждый из выходов резисторной матрицы через соответствующий первый МДП-ключ подключены к инвертирующему входу операционного усилителя и выходу резистора обратной связи, вход которого подключен к выходу операционного усилителя, выход которого является выходом устройства, затвор первого МДП-ключа соединен с соответствующим стоком управляющего транзистора, а исток первого МДП-ключа соединен с истоком второго МДП-ключа и с соответствующим выходом резисторной матрицы, сток второго МДП-ключа подключен к неинвертирующему входу операционного усилителя и шине общего потенциала, а его затвор соединен со стоком транзистора сброса, шина опорного напряжения соединена с входом резисторной матрицы, n-разрядные входы устройства являются входами цифроаналогового преобразователя, общая шина резисторной матрицы соединена с шиной общего потенциала, отличающийся тем, что в него введены генератор тактовых импульсов, фазовый селектор, четыре преобразователя уровней напряжения, шина синхронизации, а в каждую ячейку введены разрешающий транзистор, второй защитный диод, транзистор предварительной установки, два МДП-варактора, второй транзистор управления, второй транзистор сброса, причем исток разрешающего транзистора подключен к соответствующему входу устройства, затвор разрешающего транзистора соединен с входом первого защитного диода и подключен к выходу соответствующего преобразователя уровня, сток разрушающего транзистора подключен к затворам первого МДП-варактора, первого управляющего транзистора и стоку второго транзистора сброса, истоки последних, а также сток и исток, первого МДП-варактора подключены к выходу соответствующего преобразователя уровня напряжений, затвор второго транзистора-сброса соединен с истоком первого транзистора сброса, с входом второго защитного диода и подключены к выходу соответствующего преобразователя уровня напряжений, сток и исток второго МДП-варактора подключены к затвору второго МДП-ключа и стоку второго управляющего транзистора, исток последнего соединен с истоком и затвором транзистора предварительной установки и подключен к выходной шине соответствующего преобразователя уровня напряжений, затворы второго МДП-варактора, второго управляющего транзистора подключены к стоку транзистора предварительной установки, выход генератора тактовых импульсов подключен к шине синхронизации и к входу фазового селектора, выходы которого соединены с соответствующими входами преобразователей уровня напряжений, шина общего потенциала устройства соединена с выходами вторых защитных диодов и подключена к соответствующим шинам генератора тактовых импульсов, фазового селектора, четырех преобразователей уровней напряжений, шины питания устройства подключены к соответствующим шинам питания генератора тактовых импульсов, фазового селектора, четырех преобразователей уровня напряжений.

Текст

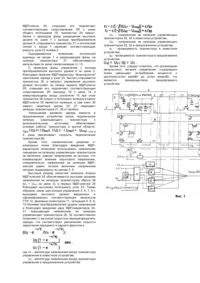

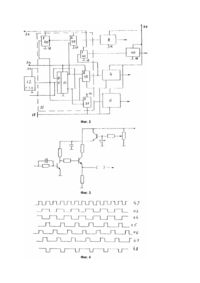

Изобретение относится к вычислительной технике и может быть использовано в системах управления при обработке информации для преобразования цифровой кодовой последовательности в аналоговый сигнал. Построение систем управления, использующих ЦАП с малой потребляемой мощностью и высоким быстродействием является проблемой. Известен ЦАП (Аналоговые и цифровые интегральные схемы. Справ. пособие / Под ред. С.Б. Якубовскбго. - М.: Радио и связь, 1979. С.263), содержащий резисторную матрицу 301НС1 типа R-2R, операционный усилитель 240УД1, стабилизатор напряжения 240ЕН1, шина питания, шины общего потенциала, три аналоговых ключа 240КН-3, причем входы аналоговых ключей являются входами n-разрядной информации преобразования, а выходы подключены к входам резисторной матрицы, выходы которой соединены с входами операционного усилителя (ОУ), выход стабилизатора напряжения подключен к соответствующим шинам питания аналоговых ключей, а его общая шина подключена к шине общего потенциала, вход стабилизатора напряжения подключен к соответствующим шинам напряжения, выход ОУ через Roc подключен к информационному входу ОУ, выход которого является выходом преобразователя. Недостатком этого преобразователя является большая потребляемая мощность. Кроме того, известен ЦАП серии 572ПА (Алексенко А.Г. и др. Применение прецизионных аналоговых микросхем. - М.: Радио и связь, 1985. - Справ. Т.II. - МЭП СССР, микросхемы интегральные п/п аналоговые. - НИИ, 1976) являющейся прототипом и содержащий операционный усилитель, резисторную матрицу типа R-2R, резистор обратной связи, шину питания, шину общего потенциала, шину опорного напряжения, nразрядные ячейки, причем каждая разрядная ячейка содержит входную разрядную шину, защитный диод, первый и второй МДП-ключи, транзистор сброса, управляющий транзистор, причем выход защитного диода подключен к шине общего потенциала, каждый из выходов резисторной матрицы через соответствующий первый МДП-ключ подключен к инвертирующему входу операционного усилителя и выходу резистора обратной связи, вход которого подключен к выходу ОУ, выход которого является выходом устройства, затворы первых МДП-ключей соединены с соответствующими стоками управляющих транзисторов, а каждый исток первого МДП-ключа соединен с истоком второго МДП-ключа и с соответствующим выходом резисторной матрицы, стоки вторых МДП-ключей подключены к неинвертирующему входу операционного усилителя, а их затворы соединены с соответствующим стоком транзистора сброса, исток которого подключен к шине общего потенциале, к которой подключен неинвертирующий вход ОУ, шина опорного напряжения соединена с входом резисторной матрицы; n-разрядные входы преобразователя являются входами преобразователя, общая шина резисторной матрицы соединена с шиной общего потенциала. Однако указанный ЦАП при малой потребляемой мощности имеет малое быстродействие порядка 1 - 5мкс. Это вызвано малым амплитудным значением напряжения управления на затворах транзисторов. Целью изобретения является повышение быстродействия. Поставленная цель достигается тем, что в известном цифроаналоговом преобразователе, содержащем операционный усилитель, резисторную матрицу типа R-2R, резистор обратной связи, шины питания, шину общего потенциала, шину опорного напряжения, nразрядные ячейки, причем каждая разрядная ячейка содержит входную разрядную шину, защитный диод, первый и второй МДП-ключи, транзистор сброса, управляющий транзистор, причем выход защитного диода подключен к шине общего потенциала, каждый из выходов резисторной матрицы через соответствующий первый МДП-ключ подключены к инвертирующему входу операционного усилителя и выходу резистора обратной связи, вход которого подключен к выходу операционного усилителя, выход которого является выходом устройства; затвор первого МДП-ключа соединен с соответствующим стоком управляющего транзистора, а исток первого МДП-ключа соединен с истоком второго МДП-ключа и с соответствующим выходом резисторной матрицы, сток второго МДП-ключа подключен к неинвертирующему входу операционного усилителя и шине общего потенциала, а его затвор соединен со стоком транзистора сброса, шина опорного напряжения соединена с входом резисторной матрицы, n-разрядные входы устройства являются входами цифроаналогового преобразователя, общая шина резисторной матрицы соединена с шиной общего потенциала, введены генератор тактовых импульсов, фазовый селектор, четыре преобразователя уровней напряжения, шина синхронизации, а в каждую разрядную ячейку введены разрешающей транзистор, второй защитный диод, транзистор предварительной установки, два МДП-варактора, второй транзистор управления, второй транзистор сброса, причем исток разрешающего транзистора подключен к соответствующему входу устройства, затвор разрешающего транзистора соединен с входом первого защитного диода и подключен к выходу соответствующего преобразователя уровня, сток разрешающего транзистора подключен к затворам первого МДП-варактора, первого управляющего транзистора и стоку второго транзистора сброса, истоки последних и сток, исток первого МДП-варактора подключены к выходу соответствующего преобразователя уровня напряжений, затвор второго транзистора сброса соединен с истоком первого транзистора сброса, с входом второго защитного диода и подключены к выходу соответствующего преобразователя уровня напряжений, сток и исток второго МДП-варактора подключены к затвору второго МДП-ключа и стоку второго управляющего транзистора, исток последнего соединен с истоком и затвором транзистора предварительной установки и подключен к выходной шине соответствующего преобразователя уровня напряжений, затворы второго МДП-варактора, второго управляющего транзистора подключены к стоку транзистора предварительной установки, выход генератора тактовых импульсов подключен к шине синхронизации и к входу фазового селектора, выходы которого соединены с соответствующими входами преобразователей уровня напряжений, шина общего потенциала устройства соединена с выходами вторых защитных диодов и подключена к соответствующим шинам генератора тактовых импульсов, фазового селектора, четырех преобразователей уровней напряжений, шины питания устройства подключены к соответствующим шинам питания генератора тактовых импульсов, фазового селектора, четырех преобразователей уровня напряжений. В предлагаемом решении все признаки, указанные в отличительной части формулы изобретения, проявляют в процессе взаимодействия присущие им известные свойства, дающие каждый в отдельности известный положительный эффект. При этом обеспечивается сверхсуммарный технический эффект обусловленный совокупностью указанных признаков, заключающихся в том, что связь входов управления транзисторов разрешения, транзисторов сброса, транзисторов предварительной установки, МДП-варакторов, управляющих транзисторов, управления питанием, с выходами высокого уровня, сформированных ГТИ и выделенных фазовым селектором, импульсов управления, преобразователей уровня напряжений позволяете высокой скоростью перераспределить заряды, что способствует увеличению быстродействия за счет уменьшения времени переключения. Таким образом, предлагаемое решение удовлетворяет критерию "существенные отличия". На фиг.1 приведена структурная схема предлагаемого ЦАП; на фиг.2 - принципиальная схема фазового селектора и его связь с ГТИ и преобразователями уровней напряжений; на фиг.3 - принципиальная схема преобразователя уровня напряжения; на фиг.4 - временные диаграммы, поясняющие работу устройства. На фиг.1 n-входов ЦАП 1 соединены с соответствующими входами n-разрядной ячейки 2, первые управляющие входы 3, которых соединены с выходом первого преобразователя уровня 4, вторые управляющие 28 подключены к затвору второго транзистора сброса 26 и к шине общего потенциала 18 к ней подключены выходы защитных диодов 22, 27; шины питания 34, 35 подключены к соответствующим шинам питания ГТИ 12, фазового селектора 11 и преобразователей уровня напряжений (4, 6, 8, 10). Фазовый селектор 11 (фиг.2) содержит Дтриггер 36, вход "C" которого подключен к выходу ГТИ 12, вход "Д" соединен с инверсным выходом триггера 36 и вторым входом элемента И 37, первый вход которого подключен к "C" входу триггера 36 и второму входу элемента И 38, первый вход которого подключен к прямому выходу триггера 36 и второму входу элемента И 39, первый вход которого соединен с выходом элемента НЕ 40, вход которого подключен к входу "C" триггера 36. выход И 38 подключен к входу элемента НЕ 41, выход которого подключен к входу преобразователя уровня 10, выход которого соединен с шиной управления 9, выход И 39 подключен к входу преобразователя 8, выход которого соединен с шиной управления 7, выход элемента И 38 соединен с входом преобразователя уровня 4, выход которого подключен к шине управления 3, выход элемента И 37 подключен к входу преобразователя 6, выход которого соединен с шиной управления 5, шины общего потенциала элементов 36, 37, 38, 39, 40, 41 подключены к шине общего потенциала 18 фазового селектора 11, его шина питания 34 подключена к шине питания элементов 36, 37, 38, 39, 40, 41, шина питания высокого уровня 35 подключена к соответствующим шинам питания преобразователя уровня напряжения (4, 6, 8, 10). ГТИ 12 является стандартным; ОУ 15 является стандартным. Преобразователи уровней 4, 6, 8, 10 идентичны (фиг.3) и выполнены по схеме 141. На фиг.4: 42 - временная диаграмма на выходе ГТИ 12; 43 - временная диаграмма на выходе выходе Д-триггера 36; 44 - временная диаграмма на выходе Q выходе Д-триггера 36; 45 - временная диаграмма на выходе элемента И 38; 46 - временная диаграмма на выходе элемента И 37; 47 - временная диаграмма на выходе элемента И 39; 48 - временная диаграмма на выходе элемента И 41. Как известно [2] ЦАП с ОУ образует обычный инвертирующий усилитель, у которого входное напряжение равно Vоп, а выходное напряжение Uвых = UопRос/Rм и зависит от сопротивления матрицы R-2R между точками Uоп и инвертирующим входом ОУ. В свою очередь сопротивление Rм зависит от того, подключены резисторы к шине общего потенциала или к инвертирующему входу усилителя. Это подключение осуществляется через соответствующие МДП-ключи, состояние которых (открыт или закрыт) зависит от поданного на их затворы напряжения, которые в свою очередь зависит от цифрового n-разрядного слова на входу ЦАП. Известно, что время переключения МОПтранзистора определяется скоростью нарастания переднего и заднего фронтов импульса соответственно где U1 - амплитуда напряжения входа управления на МДП-ключах; - постоянная времени; c - выходная емкость; b - коэффициент усиления; Uз - напряжение на затворе транзистора; Uпор - пороговое напряжение транзистора. Работает устройство следующим образом. Перед началом преобразования производят обнуление емкостных узлов 23 в ячейке 2 и емкости узла связи истоков МДП-ключей 29, 30, для этого по шинам 5, 9 подаются импульсы сброса, выработанные ГТИ 12 и выделенные фазовым селектором 11, высокий уровень которых обеспечивается преобразователем уровня 6, 10. Обнуление емкости узла 23 осуществляется через открытый транзистор 26 на нулевой потенциал шины 3, транзистор 33 и второй МДП-варактор способствуют подачи напряжения высокого уровня через открытый транзистор 32 на затвор второго МДП-ключа 30, открывая его подключает соответствующие сопротивления 2R к шине общего потенциала 18, транзистор 28 закрыт. Затем с приходом фазы разрешения высокого уровня по шине 7 с выхода преобразователя уровня 8, открывается транзистор 21 и логический сигнал с входа 1 заряжает соответствующую емкость узла 23 ячейки 2. Одновременное появление логической единицы на входе 1 и разрешающей фазы на затворе транзистора 21 обеспечивается импульсами по шине синхронизации Uт 13. С приходом фазы управления с выхода преобразователя высокого уровня 4 по шине 3, благодаря первому МДП-варактору "форсируется" накопление заряда в узле 23, быстро открывается транзистор 25 и импульс управления высокого уровня поступает на затвор первого МДП-ключа 29, открывая его подключает соответствующее сопротивление 2R матрицы 19 к шине 14 и инвертирующему входу усилителя 15 при этом транзистор 28 открыт и потенциал затвора второго МДП-ключа 30 является нулевым, а сам ключ 30 закрыт, защитные диоды 22, 27 защищают затворы транзисторов 21, 26 от пробоя. Уменьшение времени заряда емкости в предложенном устройстве путем подключения затвора разрешающего транзистора к дополнительному источнику, обеспечивает условия работы транзистора в крутой области. При что в 4 раза увеличивает скорость переключения транзистора [6]. Кроме того, схематическое решение nразрядных ячеек благодаря введению МДПваракторов позволило использовать напряжение смещения на затворах управляющих транзисторов на величину, равную напряжению на истоках, что компенсирует влияние порогового напряжения, следовательно, напряжение на затворах МДПключей равно полной величине напряжения питания подводимого по шинам 3, 9. Быстрый разряд емкостей затворов вторых МДП-ключей 30 обеспечивается высоким уровнем напряжения на затворах транзисторов сброса 28 (Uз = Uпит на шине 3), а первых МДП-ключей 29 благодаря высокому потенциалу узла 23. Таким образом, связь шин входов управления 3, 5, 7, 9 с выходами высокого уровня введенных и сформированных соответствующих импульсов ГТИ 12, фазовым селектором 11, четырьмя 4, 6, 8, 10 блоками преобразователей уровня напряжений и благодаря введению двух МДП-варакторов 24, 31 повышающих напряжение на затворах управляющих транзисторов 25, 32 соответственно позволяют с высокой скоростью перераспределить заряды, что соответствует увеличению скорости нарастания переднего и заднего фронтов в где U1 - амплитуда напряжения входе транзистора управления в известном устройстве, U2 - амплитуда напряжения входа транзистора управления в предложенном устройстве. Uз1 - напряжение на затворах управляющих транзисторов 25, 32 в известном устройстве, Uз2 - напряжение на затворах управляющих транзисторов 25, 32 в предложенном устройстве, q1 - проводимость транзистора в известном устройстве, q2 - проводимость транзистора в предлагаемом устройстве, Кроме того, следует отметить, что организация импульсного питания управления n-разрядных ячеек уменьшает потребление мощности с десятков-сотен милиВт до сотен микроВт, что является преимуществом предлагаемого устройства.

ДивитисяДодаткова інформація

Автори англійськоюLukashenko Valentyna Maksymivna, Bykov Valentyn Ivanovych, Lukashenko Andrii Hermanovych

Автори російськоюЛукашенко Валентина Максимовна, Быков Валентин Иванович, Лукашенко Андрей Германович

МПК / Мітки

МПК: G06J 3/00, G06G 7/26, H03M 1/12

Мітки: цифро-аналоговий, перетворювач

Код посилання

<a href="https://ua.patents.su/4-24660-cifro-analogovijj-peretvoryuvach.html" target="_blank" rel="follow" title="База патентів України">Цифро-аналоговий перетворювач</a>

Попередній патент: Спосіб охолодження ствола пістолета-кулемета

Наступний патент: Спосіб лікування виразкової хвороби

Випадковий патент: Спосіб виготовлення розсільного сиру