Двотактний симетричний підсилювач струму

Номер патенту: 117383

Опубліковано: 26.06.2017

Автори: Азаров Олексій Дмитрович, Богомолов Сергій Віталійович, Гарнага Володимир Анатолійович, Гринько Олексій Олексійович

Формула / Реферат

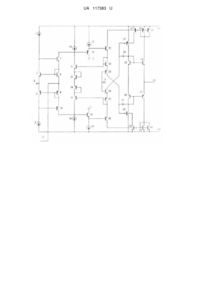

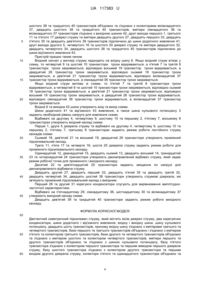

Двотактний симетричний підсилювач струму, який містить вісім джерел струму, два корегуючих конденсатори, шини додатного і від'ємного живлення, вхідну і вихідну шини, шину нульового потенціалу, двадцять шість транзисторів, причому вхідну шину з'єднано з емітерами третього та четвертого транзисторів, бази першого та третього транзисторів об'єднано і з'єднано з емітером п'ятого та колектором третього транзисторів, бази другого та четвертого транзисторів об'єднано та з'єднано з емітером шостого та колектором четвертого транзисторів, емітери першого та другого транзисторів об'єднано та з'єднано з шиною нульового потенціалу, базу п'ятого транзистора з'єднано з колектором першого транзистора та першим виводом першого джерела струму, базу шостого транзистора з'єднано з колектором другого транзистора та першим входом другого джерела струму, колектори п'ятого та одинадцятого транзистора об'єднано та з'єднано з базою сьомого транзистора та першим виводом третього джерела струму, колектори шостого та дванадцятого транзистора об'єднано та з'єднано з базою восьмого транзистора та першим входом четвертого джерела струму, емітер одинадцятого транзистора об'єднано з емітером дванадцятого транзистора, емітер сьомого транзистора з'єднано з базою дев'ятого транзистора та першим виводом п'ятого джерела струму, емітер восьмого транзистора з'єднано з базою двадцятого транзистора та першим виводом шостого джерела струму, колектори сьомого та восьмого транзисторів з'єднані з шиною нульового потенціалу, емітери десятого та тринадцятого транзисторів об'єднано і з'єднано з базою одинадцятого транзистора, емітер чотирнадцятого з'єднано з колектором та базою дев'ятнадцятого транзистора та базою дванадцятого транзистора, бази тринадцятого та чотирнадцятого транзисторів об'єднано та з'єднано з шиною нульового потенціалу, емітер дев'ятого транзистора з'єднано з колектором та базою десятого транзистора, емітери двадцятого та дев'ятнадцятого транзисторів об'єднано між собою, колектор дев'ятого транзистора з'єднано з базами двадцять першого та двадцять п'ятого транзисторів, колектор двадцятого транзистора з'єднано з базами двадцять четвертого та двадцять шостого транзисторів, колектор тринадцятого транзистора з'єднано з базою двадцять третього транзистора та з другим корегуючим конденсатором, колектор чотирнадцятого транзистора з'єднано з базою двадцять другого транзистора та першим корегуючим конденсатором, колектор двадцять другого транзистора з'єднано з колектором та базою п'ятнадцятого транзистора, колектор двадцять третього транзистора з'єднано з колектором та базою шістнадцятого транзистора, колектор двадцять четвертого транзистора з'єднано з базою двадцять третього транзистора, колектор двадцять першого транзистора з'єднано з базою двадцять другого транзистора, бази п'ятнадцятого та сімнадцятого транзисторів об'єднано між собою, бази шістнадцятого та вісімнадцятого транзисторів об'єднано між собою, бази двадцять першого та двадцять п'ятого транзисторів об'єднано та з'єднано з колектором двадцять п'ятого та колектором сімнадцятого транзисторів та першим виводом сьомого джерела струму, бази двадцять четвертого та двадцять шостого транзисторні об'єднано та з'єднано з колектором двадцять шостого та колектором вісімнадцятого транзисторів та першим виводом восьмого джерела струму, емітери сімнадцятого та вісімнадцятого транзисторів з'єднано з вихідною шиною та вхідною шиною, другі виходи першого, третього, п'ятого та сьомого джерел струму та емітери двадцять другого, двадцять першого та двадцять п'ятого транзисторів підключено до шини додатного живлення, другі виходи другого, четвертого, шостого та восьмого джерел струму та емітери двадцятого, двадцять четвертого та двадцять шостого транзисторів підключено до шини від'ємного живлення, який відрізняється тим, що у нього введено чотири транзистори, причому емітер одинадцятого транзистора з'єднано з базою та колектором двадцять сьомого транзистора, емітер дванадцятого транзистора з'єднано з базою та колектором двадцять восьмого транзистора, емітер двадцять сьомого транзистора з'єднано з емітером двадцять восьмого транзистора, бази десятого та одинадцятого транзисторів об'єднано та з'єднано з емітером дев'ятого та колектором десятого транзисторів, бази дванадцятого та дев'ятнадцятого транзисторів об'єднано та з'єднано з колектором дев'ятнадцятого та емітером двадцятого транзисторів, емітер десятого транзистора з'єднано з емітером тринадцятого транзистора, емітер дев'ятнадцятого транзистора з'єднано з емітером чотирнадцятого транзистора, колектор дев'ятого транзистора з'єднано з базами двадцять першого, двадцять п'ятого та двадцять дев'ятого транзисторів, колектор двадцятого транзистора з'єднано з базами двадцять четвертого, двадцять шостого та тридцятого транзисторів, бази двадцять першого, двадцять п'ятого та двадцять дев'ятого транзисторів об'єднано та з'єднано з колекторами двадцять п'ятого, сімнадцятого та двадцять дев'ятого транзисторів, бази двадцять четвертого, двадцять шостого та тридцятого транзисторів об'єднано та з'єднано з колекторами вісімнадцятого, двадцять шостого та тридцятого транзисторів, емітери двадцять дев'ятого та тридцятого транзисторів підключено до шини додатного і від'ємного живлення відповідно.

Текст

Реферат: Двотактний симетричний підсилювач струму містить вісім джерел струму, два корегуючих конденсатори, шини додатного і від'ємного живлення, вхідну і вихідну шини, шину нульового потенціалу, двадцять шість транзисторів. Відбивачі на другому, четвертому, шостому та першому, п'ятому, восьмому транзисторах утворюють вхідний канал схеми. Перше, друге джерела струму та відбивачі на другому, четвертому, шостому та першому, п'ятому, третьому транзисторах задають режим роботи постійного струму каскадів схеми. Сьомий, дев'ятий та восьмий, двадцятий транзистори утворюють проміжний підсилювальний каскад. Третє, п'яте та четверте, шосте джерела струму задають режим роботи для проміжного підсилювального каскаду. Одинадцятий, дванадцятий, двадцять сьомий, двадцять восьмий, тринадцятий та чотирнадцятий транзистори утворюють двонаправлений відбивач струму, який задає режим робочої точки для проміжного і вихідного каскаду. Десятий та дев'ятнадцятий транзистори задають зміщення по напрузі для двонаправленого відбивача струму. Двадцять другий, двадцять перший, двадцять п'ятий та двадцять третій, двадцять четвертий, двадцять шостий транзистори утворюють струмові дзеркала, які зв'язують проміжний підсилювальний каскад з вихідним. Перший та другий корегуючі конденсатори слугують для вирівнювання амплітудночастотної характеристики. Відбивачі на п'ятнадцятому, сімнадцятому, шістнадцятому та вісімнадцятому утворюють вихідний каскад схеми. Двадцять дев'ятий та тридцятий транзистори задають режим роботи вихідного каскаду. UA 117383 U (12) UA 117383 U UA 117383 U 5 10 15 20 25 30 35 40 45 50 55 60 Корисна модель належить до імпульсної техніки і може бути використана в аналоговоцифрових перетворювачах і цифрових вимірювальних приладах. Відомо двотактний симетричний підсилювач струму (Патент України № 69736 Н03К 5/24, G05B 1/01, 2011), який містить перше та друге джерело струму, шини додатного і від'ємного живлення, вхідну і вихідну шини, шину нульового потенціалу, вісімнадцять транзисторів, причому вхідну шину з'єднано з емітерами третього і четвертого транзисторів, емітери першого і другого транзисторів об'єднано та з'єднано з шиною нульового потенціалу, колектори третього і четвертого транзисторів з'єднано з базами п'ятого і шостого транзисторів та з колекторами сьомого та восьмого транзисторів відповідно, бази третього і четвертого транзисторів з'єднано з базами та колекторами першого і другого транзисторів відповідно, а також з першими виводами першого і другого джерел струму, другі виводи першого і другого джерел струму з'єднано з шинами додатного і від'ємного живлення відповідно, бази сьомого та восьмого транзисторів з'єднано з колекторами та базами дев'ятого та десятого транзисторів відповідно, а також з колекторами одинадцятого та дванадцятого транзисторів, а також з базами п'ятнадцятого та шістнадцятого транзисторів відповідно, емітери одинадцятого та дванадцятого транзисторів об'єднано між собою, бази одинадцятого та дванадцятого транзисторів з'єднано з емітерами тринадцятого та чотирнадцятого транзисторів, а також з колекторами п'ятого та шостого транзисторів відповідно, бази тринадцятого та чотирнадцятого транзисторів з'єднано з шиною нульового потенціалу, емітери п'ятнадцятого та шістнадцятого транзисторів з'єднано з колекторами чотирнадцятого та тринадцятого транзисторів відповідно, колектори сімнадцятого та вісімнадцятого транзисторів з'єднано з вихідною шиною, бази сімнадцятого та вісімнадцятого транзисторів з'єднано з базами п'ятого та шостого транзисторів відповідно, емітери сьомого, дев'ятого, п'ятого та сімнадцятого транзисторів, а також колектор п'ятнадцятого транзистора підключено до шини додатного живлення, емітери восьмого, десятого, шостого та вісімнадцятого транзисторів, а також колектор шістнадцятого транзистора підключено до шини від'ємного живлення. Недоліком пристрою є недостатньо високий коефіцієнт підсилення, що призводить до збільшення похибок при роботі схеми. За найближчий аналог вибрано двотактний симетричний підсилювач струму (Патент України № 107581 Н03К 5/24, G05B 1/01, опубл. 10.06.2016, Бюл. № 11), який містить вісім джерел струму, два корегуючих конденсатори, шини додатного і від'ємного живлення, вхідну і вихідну шини, шину нульового потенціалу, двадцять шість транзисторів, причому вхідну шину з'єднано з емітерами третього та четвертого транзисторів, бази першого та третього транзисторів об'єднано і з'єднано з емітером п'ятого та колектором третього транзисторів, бази другого та четвертого транзисторів об'єднано та з'єднано з емітером шостого та колектором четвертого транзисторів, емітери першого та другого транзисторів об'єднано та з'єднано з шиною нульового потенціалу, базу п'ятого транзистора з'єднано з колектором першого транзистора та першим виводом першого джерела струму, базу шостого транзистора з'єднано з колектором другого транзистора та першим входом другого джерела струму, колектори п'ятого та одинадцятого транзистора об'єднано та з'єднано з базою сьомого транзистора та першим виводом третього джерела струму, колектори шостого та дванадцятого транзистора об'єднано та з'єднано з базою восьмого транзистора та першим входом четвертого джерела струму, емітер одинадцятого транзистора об'єднано з емітером дванадцятого транзистора, емітер сьомого транзистора з'єднано з базою дев'ятого транзистора та першим виводом п'ятого джерела струму, емітер восьмого транзистора з'єднано з базою двадцятого транзистора та першим виводом шостого джерела струму, колектори сьомого та восьмого транзисторів з'єднані з шиною нульового потенціалу, емітери десятого та тринадцятого транзисторів об'єднано і з'єднано з базою одинадцятого транзистора, емітер чотирнадцятого з'єднано з колектором та базою дев'ятнадцятого транзистора та базою дванадцятого транзистора, бази тринадцятого та чотирнадцятого транзисторів об'єднано та з'єднано з шиною нульового потенціалу, емітер дев'ятого транзистора з'єднано з колектором та базою десятого транзистора, емітери двадцятого та дев'ятнадцятого транзисторів об'єднано між собою, колектор дев'ятого транзистора з'єднано з базами двадцять першого та двадцять п'ятого транзисторів, колектор двадцятого транзистора з'єднано з базами двадцять четвертого та двадцять шостого транзисторів, колектор тринадцятого транзистора з'єднано з базою двадцять третього транзистора та з другим корегуючим конденсатором, колектор чотирнадцятого транзистора з'єднано з базою двадцять другого транзистора та першим корегуючим конденсатором, колектор двадцять другого транзистора з'єднано з колектором та базою п'ятнадцятого транзистора, колектор двадцять третього транзистора з'єднано з колектором та базою шістнадцятого транзистора, колектор двадцять четвертого транзистора з'єднано з базою двадцять третього транзистора, колектор двадцять першого транзистора з'єднано з базою 1 UA 117383 U 5 10 15 20 25 30 35 40 45 50 55 60 двадцять другого транзистора, бази п'ятнадцятого та сімнадцятого транзисторів об'єднано між собою, бази шістнадцятого та вісімнадцятого транзисторів об'єднано між собою, бази двадцять першого та двадцять п'ятого транзисторів об'єднано та з'єднано з колектором двадцять п'ятого та колектором сімнадцятого транзисторів та першим виводом сьомого джерела струму, бази двадцять четвертого та двадцять шостого транзисторів об'єднано та з'єднано з колектором двадцять шостого та колектором вісімнадцятого транзисторів та першим виводом восьмого джерела струму, емітери сімнадцятого та вісімнадцятого транзисторів з'єднано з вихідною шиною та вхідною шиною, другі виходи першого, третього, п'ятого та сьомого джерел струму та емітери двадцять другого, двадцять першого та двадцять п'ятого транзисторів підключено до шини додатного живлення, другі виходи другого, четвертого, шостого та восьмого джерел струму та емітери двадцятого, двадцять четвертого та двадцять шостого транзисторів підключено до шини від'ємного живлення. Недоліком найближчого аналога є недостатньо високий коефіцієнт підсилення, що призводить до збільшення похибок при роботі схеми. В основу корисної моделі поставлено задачу створення двотактного симетричного підсилювача струму, в якому за рахунок введення нових елементів та зв'язків між ними підвищується точність роботи завдяки збільшенню коефіцієнта підсилення по струму, це розширює галузь використання корисної моделі у різноманітних пристроях імпульсної та обчислювальної техніки, автоматики тощо. Поставлена задача вирішується тим, що у двотактний симетричний підсилювач струму, який містить вісім джерел струму, два корегуючих конденсатори, шини додатного і від'ємного живлення, вхідну і вихідну шини, шину нульового потенціалу, двадцять шість транзисторів, причому вхідну шину з'єднано з емітерами третього та четвертого транзисторів, бази першого та третього транзисторів об'єднано і з'єднано з емітером п'ятого та колектором третього транзисторів, бази другого та четвертого транзисторів об'єднано та з'єднано з емітером шостого та колектором четвертого транзисторів, емітери першого та другого транзисторів об'єднано та з'єднано з шиною нульового потенціалу, базу п'ятого транзистора з'єднано з колектором першого транзистора та першим виводом першого джерела струму, базу шостого транзистора з'єднано з колектором другого транзистора та першим входом другого джерела струму, колектори п'ятого та одинадцятого транзистора об'єднано та з'єднано з базою сьомого транзистора та першим виводом третього джерела струму, колектори шостого та дванадцятого транзистора об'єднано та з'єднано з базою восьмого транзистора та першим входом четвертого джерела струму, емітер одинадцятого транзистора об'єднано з емітером дванадцятого транзистора, емітер сьомого транзистора з'єднано з базою дев'ятого транзистора та першим виводом п'ятого джерела струму, емітер восьмого транзистора з'єднано з базою двадцятого транзистора та першим виводом шостого джерела струму, колектори сьомого та восьмого транзисторів з'єднані з шиною нульового потенціалу, емітери десятого та тринадцятого транзисторів об'єднано і з'єднано з базою одинадцятого транзистора, емітер чотирнадцятого з'єднано з колектором та базою дев'ятнадцятого транзистора та базою дванадцятого транзистора, бази тринадцятого та чотирнадцятого транзисторів об'єднано та з'єднано з шиною нульового потенціалу, емітер дев'ятого транзистора з'єднано з колектором та базою десятого транзистора, емітери двадцятого та дев'ятнадцятого транзисторів об'єднано між собою, колектор дев'ятого транзистора з'єднано з базами двадцять першого та двадцять п'ятого транзисторів, колектор двадцятого транзистора з'єднано з базами двадцять четвертого та двадцять шостого транзисторів, колектор тринадцятого транзистора з'єднано з базою двадцять третього транзистора та з другим корегуючим конденсатором, колектор чотирнадцятого транзистора з'єднано з базою двадцять другого транзистора та першим корегуючим конденсатором, колектор двадцять другого транзистора з'єднано з колектором та базою п'ятнадцятого транзистора, колектор двадцять третього транзистора з'єднано з колектором та базою шістнадцятого транзистора, колектор двадцять четвертого транзистора з'єднано з базою двадцять третього транзистора, колектор двадцять першого транзистора з'єднано з базою двадцять другого транзистора, бази п'ятнадцятого та сімнадцятого транзисторів об'єднано між собою, бази шістнадцятого та вісімнадцятого транзисторів об'єднано між собою, бази двадцять першого та двадцять п'ятого транзисторів об'єднано та з'єднано з колектором двадцять п'ятого та колектором сімнадцятого транзисторів та першим виводом сьомого джерела струму, бази двадцять четвертого та двадцять шостого транзисторів об'єднано та з'єднано з колектором двадцять шостого та колектором вісімнадцятого транзисторів та першим виводом восьмого джерела струму, емітери сімнадцятого та вісімнадцятого транзисторів з'єднано з вихідною шиною та вхідною шиною, другі виходи першого, третього, п'ятого та сьомого джерел струму та емітери двадцять другого, двадцять першого та двадцять п'ятого транзисторів підключено до 2 UA 117383 U 5 10 15 20 25 30 35 40 45 50 55 60 шини додатного живлення, другі виходи другого, четвертого, шостого та восьмого джерел струму та емітери двадцятого, двадцять четвертого та двадцять шостого транзисторів підключено до шини від'ємного живлення, введено чотири транзистори, причому емітер одинадцятого транзистора з'єднано з базою та колектором двадцять сьомого транзистора, емітер дванадцятого транзистора з'єднано з базою та колектором двадцять восьмого транзистора, емітер двадцять сьомого транзистора з'єднано з емітером двадцять восьмого транзистора, бази десятого та одинадцятого транзисторів об'єднано та з'єднано з емітером дев'ятого та колектором десятого транзисторів, бази дванадцятого та дев'ятнадцятого транзисторів об'єднано та з'єднано з колектором дев'ятнадцятого та емітером двадцятого транзисторів, емітер десятого транзистора з'єднано з емітером тринадцятого транзистора, емітер дев'ятнадцятого транзистора з'єднано з емітером чотирнадцятого транзистора, колектор дев'ятого транзистора з'єднано з базами двадцять першого, двадцять п'ятого та двадцять дев'ятого транзисторів, колектор двадцятого транзистора з'єднано з базами двадцять четвертого, двадцять шостого та тридцятого транзисторів, бази двадцять першого, двадцять п'ятого та двадцять дев'ятого транзисторів об'єднано та з'єднано з колекторами двадцять п'ятого, сімнадцятого та двадцять дев'ятого транзисторів, бази двадцять четвертого, двадцять шостого та тридцятого транзисторів об'єднано та з'єднано з колекторами вісімнадцятого, двадцять шостого та тридцятого транзисторів, емітери двадцять дев'ятого та тридцятого транзисторів підключено до шини додатного і від'ємного живлення відповідно. На кресленні представлено принципову схему двотактного симетричного підсилювача струму. Пристрій містить вхідну шину 6, яку з'єднано з емітерами третього 8 та четвертого 9 транзисторів, бази першого 2 та третього 8 транзисторів об'єднано і з'єднано з емітером п'ятого 7 та колектором третього 8 транзисторів, бази другого 4 та четвертого 9 транзисторів об'єднано та з'єднано з емітером шостого 10 та колектором четвертого 9 транзисторів, емітери першого 2 та другого 4 транзисторів об'єднано та з'єднано з шиною нульового потенціалу 3, базу п'ятого 7 транзистора з'єднано з колектором першого 2 транзистора та першим виводом першого 1 джерела струму, базу шостого 10 транзистора з'єднано з колектором другого 4 транзистора та першим входом другого 5 джерела струму, колектори п'ятого 7 та одинадцятого 12 транзистора об'єднано та з'єднано з базою сьомого 18 транзистора та першим виводом третього 11 джерела струму, колектори шостого 10 та дванадцятого 15 транзистора об'єднано та з'єднано з базою восьмого 19 транзистора та першим входом четвертого 16 джерела струму, емітер одинадцятого 12 транзистора з'єднано з базою та колектором двадцять сьомого 13 транзистора, емітер дванадцятого 15 транзистора з'єднано з базою та колектором двадцять восьмого 14 транзистора, емітер двадцять сьомого 13 транзистора з'єднано з емітером двадцять восьмого 28 транзистора, емітер сьомого 18 транзистора з'єднано з базою дев'ятого 21 транзистора та першим виводом п'ятого 17 джерела струму, емітер восьмого 19 транзистора з'єднано з базою двадцятого 26 транзистора та першим виводом шостого 20 джерела струму, колектори сьомого 18 та восьмого 19 транзисторів з'єднані з шиною нульового потенціалу 3, бази десятого 22 та одинадцятого 12 транзисторів об'єднано та з'єднано з емітером дев'ятого 21 та колектором десятого 22 транзисторів, бази дванадцятого 15 та дев'ятнадцятого 25 транзисторів об'єднано та з'єднано з колектором дев'ятнадцятого 25 та емітером двадцятого 26 транзисторів, емітер десятого 22 транзистора з'єднано з емітером тринадцятого 23 транзистора, емітер дев'ятнадцятого 25 транзистора з'єднано з емітером чотирнадцятого 24 транзистора, бази тринадцятого 23 та чотирнадцятого 24 транзисторів об'єднано та з'єднано з шиною нульового потенціалу 3, колектор дев'ятого 21 транзистора з'єднано з базами двадцять першого 33, двадцять п'ятого 35 та двадцять дев'ятого 39 транзисторів, колектор двадцятого 26 транзистора з'єднано з базами двадцять четвертого 34, двадцять шостого 38 та тридцятого 40 транзисторів, колектор тринадцятого 23 транзистора з'єднано з базою двадцять третього 32 транзистора та з другим корегуючим конденсатором 31, колектор чотирнадцятого 24 транзистора з'єднано з базою двадцять другого 27 транзистора та першим корегуючим конденсатором 28, колектор двадцять другого 27 транзистора з'єднано з колектором та базою п'ятнадцятого 29 транзистора, колектор двадцять третього 32 транзистора з'єднано з колектором та базою шістнадцятого 30 транзистора, колектор двадцять четвертого 34 транзистора з'єднано з базою двадцять третього 32 транзистора, колектор двадцять першого 33 транзистора з'єднано з базою двадцять другого 27 транзистора, бази п'ятнадцятого 29 та сімнадцятого 36 транзисторів об'єднано між собою, бази шістнадцятого 30 та вісімнадцятого 37 транзисторів об'єднано між собою, бази двадцять першого 33, двадцять п'ятого 35 та двадцять дев'ятого 39 транзисторів об'єднано та з'єднано з колекторами двадцять п'ятого 35, сімнадцятого 36 та двадцять дев'ятого 39 транзисторів, бази двадцять четвертого 34, двадцять 3 UA 117383 U 5 10 15 20 25 30 35 40 45 шостого 38 та тридцятого 40 транзисторів об'єднано та з'єднано з колекторами вісімнадцятого 37, двадцять шостого 38 та тридцятого 40 транзисторів, емітери сімнадцятого 36 та вісімнадцятого 37 транзисторів з'єднано з вихідною шиною 42, другі виходи першого 1, третього 11 та п'ятого 17 джерел струму та емітери двадцять другого 27, двадцять першого 33, двадцять п'ятого 35 та двадцять дев'ятого 39 транзисторів підключено до шини додатного живлення 41, другі виходи другого 5, четвертого 16 та шостого 20 джерел струму та емітери двадцятого 32, двадцять четвертого 34, двадцять шостого 38 та тридцятого 40 транзисторів підключено до шини від'ємного живлення 43. Пристрій працює таким чином. Вхідний сигнал у вигляді струму надходить на вхідну шину 6. Якщо вхідний струм втікає у схему, то четвертий 9 та шостий 10 транзистори трохи відкриваються, а п'ятий 7 та третій 8 транзистори трохи закриваються, відповідно восьмий 19 транзистор трохи відкривається, а двадцятий 26 транзистор трохи закривається, відповідно сьомий 18 транзистор трохи закривається, а дев'ятий 21 транзистор трохи відкривається, відповідно вісімнадцятий 37 транзистор трохи відкривається, а сімнадцятий 36 транзистор трохи закривається. Якщо вхідний струм витікає зі схеми, то п'ятий 7 та третій 8 транзистори трохи відкриваються, а четвертий 9 та шостий 10 транзистори трохи закриваються, відповідно сьомий 18 транзистор трохи відкривається, а дев'ятий 21 транзистор трохи закривається, відповідно восьмий 19 транзистор трохи закривається, а двадцятий 26 транзистор трохи відкривається, відповідно сімнадцятий 36 транзистор трохи відкривається, а вісімнадцятий 37 транзистор трохи закривається. Вхідна 6 та вихідна 42 шини утворюють вхід та вихід схеми. Шини додатного 41 та від'ємного 43 живлення, а також шина нульового потенціалу 3 задають необхідний рівень напруги для живлення схеми. Відбивачі на другому 4, четвертому 9, шостому 10 та першому 2, п'ятому 7, восьмому 8 транзисторах утворюють вхідний каскад схеми. Перше 1, друге 5 джерела струму та відбивачі на другому 4, четвертому 9, шостому 10 та першому 2, п'ятому 7, третьому 8 транзисторах задають режим роботи постійного струму каскадів схеми. Сьомий 18, дев'ятий 21 та восьмий 19, двадцятий 26 транзистори утворюють проміжний підсилювальний каскад. Третє 11, п'яте 17 та четверте 16, шосте 20 джерела струму задають режим роботи для проміжного підсилювального каскаду. Одинадцятий 12, дванадцятий 15, двадцять сьомий 13, двадцять восьмий 14, тринадцятий 23 та чотирнадцятий 24 транзистори утворюють двонаправлений відбивач струму, який задає режим робочої точки для проміжного і вихідного каскаду. Десятий 22 та дев'ятнадцятий 25 транзистори задають зміщення по напрузі для двонаправленого відбивача струму. Двадцять другий 27, двадцять перший 33, двадцять п'ятий 35 та двадцять третій 32, двадцять четвертий 34, двадцять шостий 38 транзистори утворюють струмові дзеркала, які зв'язують проміжний підсилювальний каскад з вихідним. Перший 28 та другий 31 корегуючі конденсатори слугують для вирівнювання амплітудночастотної характеристики. Відбивачі на п'ятнадцятому 29, сімнадцятому 36, шістнадцятому 30 та вісімнадцятому 37 утворюють вихідний каскад схеми. Двадцять дев'ятий 39 та тридцятий 40 транзистори задають режим роботи вихідного каскаду. ФОРМУЛА КОРИСНОЇ МОДЕЛІ 50 55 60 Двотактний симетричний підсилювач струму, який містить вісім джерел струму, два корегуючих конденсатори, шини додатного і від'ємного живлення, вхідну і вихідну шини, шину нульового потенціалу, двадцять шість транзисторів, причому вхідну шину з'єднано з емітерами третього та четвертого транзисторів, бази першого та третього транзисторів об'єднано і з'єднано з емітером п'ятого та колектором третього транзисторів, бази другого та четвертого транзисторів об'єднано та з'єднано з емітером шостого та колектором четвертого транзисторів, емітери першого та другого транзисторів об'єднано та з'єднано з шиною нульового потенціалу, базу п'ятого транзистора з'єднано з колектором першого транзистора та першим виводом першого джерела струму, базу шостого транзистора з'єднано з колектором другого транзистора та першим входом другого джерела струму, колектори п'ятого та одинадцятого транзистора об'єднано та 4 UA 117383 U 5 10 15 20 25 30 35 40 45 50 з'єднано з базою сьомого транзистора та першим виводом третього джерела струму, колектори шостого та дванадцятого транзистора об'єднано та з'єднано з базою восьмого транзистора та першим входом четвертого джерела струму, емітер одинадцятого транзистора об'єднано з емітером дванадцятого транзистора, емітер сьомого транзистора з'єднано з базою дев'ятого транзистора та першим виводом п'ятого джерела струму, емітер восьмого транзистора з'єднано з базою двадцятого транзистора та першим виводом шостого джерела струму, колектори сьомого та восьмого транзисторів з'єднані з шиною нульового потенціалу, емітери десятого та тринадцятого транзисторів об'єднано і з'єднано з базою одинадцятого транзистора, емітер чотирнадцятого з'єднано з колектором та базою дев'ятнадцятого транзистора та базою дванадцятого транзистора, бази тринадцятого та чотирнадцятого транзисторів об'єднано та з'єднано з шиною нульового потенціалу, емітер дев'ятого транзистора з'єднано з колектором та базою десятого транзистора, емітери двадцятого та дев'ятнадцятого транзисторів об'єднано між собою, колектор дев'ятого транзистора з'єднано з базами двадцять першого та двадцять п'ятого транзисторів, колектор двадцятого транзистора з'єднано з базами двадцять четвертого та двадцять шостого транзисторів, колектор тринадцятого транзистора з'єднано з базою двадцять третього транзистора та з другим корегуючим конденсатором, колектор чотирнадцятого транзистора з'єднано з базою двадцять другого транзистора та першим корегуючим конденсатором, колектор двадцять другого транзистора з'єднано з колектором та базою п'ятнадцятого транзистора, колектор двадцять третього транзистора з'єднано з колектором та базою шістнадцятого транзистора, колектор двадцять четвертого транзистора з'єднано з базою двадцять третього транзистора, колектор двадцять першого транзистора з'єднано з базою двадцять другого транзистора, бази п'ятнадцятого та сімнадцятого транзисторів об'єднано між собою, бази шістнадцятого та вісімнадцятого транзисторів об'єднано між собою, бази двадцять першого та двадцять п'ятого транзисторів об'єднано та з'єднано з колектором двадцять п'ятого та колектором сімнадцятого транзисторів та першим виводом сьомого джерела струму, бази двадцять четвертого та двадцять шостого транзисторні об'єднано та з'єднано з колектором двадцять шостого та колектором вісімнадцятого транзисторів та першим виводом восьмого джерела струму, емітери сімнадцятого та вісімнадцятого транзисторів з'єднано з вихідною шиною та вхідною шиною, другі виходи першого, третього, п'ятого та сьомого джерел струму та емітери двадцять другого, двадцять першого та двадцять п'ятого транзисторів підключено до шини додатного живлення, другі виходи другого, четвертого, шостого та восьмого джерел струму та емітери двадцятого, двадцять четвертого та двадцять шостого транзисторів підключено до шини від'ємного живлення, який відрізняється тим, що у нього введено чотири транзистори, причому емітер одинадцятого транзистора з'єднано з базою та колектором двадцять сьомого транзистора, емітер дванадцятого транзистора з'єднано з базою та колектором двадцять восьмого транзистора, емітер двадцять сьомого транзистора з'єднано з емітером двадцять восьмого транзистора, бази десятого та одинадцятого транзисторів об'єднано та з'єднано з емітером дев'ятого та колектором десятого транзисторів, бази дванадцятого та дев'ятнадцятого транзисторів об'єднано та з'єднано з колектором дев'ятнадцятого та емітером двадцятого транзисторів, емітер десятого транзистора з'єднано з емітером тринадцятого транзистора, емітер дев'ятнадцятого транзистора з'єднано з емітером чотирнадцятого транзистора, колектор дев'ятого транзистора з'єднано з базами двадцять першого, двадцять п'ятого та двадцять дев'ятого транзисторів, колектор двадцятого транзистора з'єднано з базами двадцять четвертого, двадцять шостого та тридцятого транзисторів, бази двадцять першого, двадцять п'ятого та двадцять дев'ятого транзисторів об'єднано та з'єднано з колекторами двадцять п'ятого, сімнадцятого та двадцять дев'ятого транзисторів, бази двадцять четвертого, двадцять шостого та тридцятого транзисторів об'єднано та з'єднано з колекторами вісімнадцятого, двадцять шостого та тридцятого транзисторів, емітери двадцять дев'ятого та тридцятого транзисторів підключено до шини додатного і від'ємного живлення, відповідно. 5 UA 117383 U Комп’ютерна верстка А. Крулевський Міністерство економічного розвитку і торгівлі України, вул. М. Грушевського, 12/2, м. Київ, 01008, Україна ДП “Український інститут інтелектуальної власності”, вул. Глазунова, 1, м. Київ – 42, 01601 6

ДивитисяДодаткова інформація

МПК / Мітки

МПК: H03F 3/34, G05B 1/01, H03K 5/24

Мітки: струму, підсилювач, двотактний, симетричний

Код посилання

<a href="https://ua.patents.su/8-117383-dvotaktnijj-simetrichnijj-pidsilyuvach-strumu.html" target="_blank" rel="follow" title="База патентів України">Двотактний симетричний підсилювач струму</a>

Попередній патент: Спосіб приготування смузі “джерельна насолода”

Наступний патент: Пристрій для захисту від буксування колісних пар

Випадковий патент: Корпус апарата