Пристрій для з’єднання процесорів через спільну пам’ять у багатопроцесорній системі

Номер патенту: 1839

Опубліковано: 20.12.1994

Автори: Череп'яная Валентина Івановна, Єрзаков Євген Михайлович, Деніщенко Ігор Якович, Головін Віктор Іванович

Формула / Реферат

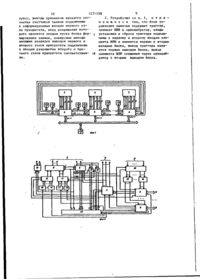

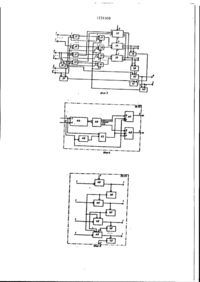

1. Устройство для сопряжения процессоров через общую память в многопроцессорной системе, содержащее с первого по третий мультиплексоры, демультиплексор, 2К + 1 регистров, где К — число подключаемых процессоров, два элемента задержки, блок формирования заявок и блок управления памятью, отличающееся тем, что, с целью повышения быстродействия, в него введены 2K + 1 блоков ввода-вывода, четвертый и пятый мультиплексоры, 2K + 1 счетчиков адреса записи, 2K + 1 счетчиков адреса считывания, первый и второй дешифраторы, входы-выходы сообщений блоков ввода-вывода являются входами-выходами шин обмена устройства, выходы сообщений блоков ввода-вывода подключены к информационным входам первого мультиплексора, выход которого является выходом сообщений, записываемых в общую память устройства, информационный вход демультиплексора является входом сообщений, считываемых из общей памяти устройства, выходы демультиплексора подключены к информационным входам регистров, выходы которых подключены к входам сообщений соответствующих блоков ввода-вывода, выходы квитирования которых подключены к входам заявок на запись блока формирования заявок и к счетным входам соответствующих счетчиков адреса записи, выходы которых подключены к информационным входам пятого мультиплексора, выход которого подключен к первому информационному входу третьего мультиплексора, выход которого является выходом группы разрядов адреса ячейки общей памяти устройства, выходы второго дешифратора подключены к входам сброса записанной заявки блока формирования заявок и к входам разрешения приема соответствующих блоков ввода-вывода, выходы первого дешифратора подключены к входам сброса считанной заявки блока формирования заявок и к счетным входам соответствующих счетчиков адреса считывания, выходы которых подключены к информационным входам четвертого мультиплексора, выход которого подключен ко второму информационному входу третьего мультиплексора, выходы адреса записываемой заявки блока формирования заявок подключены к входам управления первого и пятого мультиплексоров, выходы адреса считываемой заявки подключены к входам управления четвертого мультиплексора, к информационным входам первой группы второго мультиплексора и к входам разрешения передачи соответствующих блоков ввода-вывода, выход признака записи блока формирования заявок подключен к первым входам управления второго и третьего мультиплексоров, к первому входу блока управления памятью и через первый элемент задержки — к входу стробирования первого дешифратора, выход признака считывания блока формирования заявок подключен ко вторым входам управления второго и третьего мультиплексоров, к второму входу блока управления памятью и через второй элемент задержки — к входу стробирования второго дешифратора, первый и второй выходы блока управления памятью являются выходами режима и стробирования общей памяти устройства соответственно, выходы разрядов адреса выхода первого мультиплексора подключены к информационным входам второй группы второго мультиплексора, выходы которого подключены к входам первого и второго дешифраторов и являются выходами группы разрядов адреса секции общей памяти устройства, причем блок формирования заявок содержит три группы триггеров, группу счетчиков заявок, три узла приоритета, пять элементов ИЛИ и два триггера, входы установки триггеров первой группы являются входами заявок на запись блока формирования заявок, входы сброса триггеров третьей группы соединены с вычитающими входами соответствующих счетчиков заявок группы, с входами первого элемента ИЛИ и являются входами сброса считанной заявки блока формирования заявок, входы сброса триггеров первой группы соединены с входами сброса соответствующих триггеров второй группы, суммирующими входами соответствующих счетчиков заявок группы, с входами второго элемента ИЛИ и являются входами сброса записанной заявки блока формирования заявок выходы триггеров первой группы подключены к информационным входам соответствующих триггеров второй группы, выходы которых подключены к информационным входам второго узла приоритета, выходы которого подключены к входам четвертого элемента ИЛИ и являются выходами адреса записываемой заявки блока формирования заявок, выходы переложения счетчиков заявок группы подключены к информационным входам соответствующих триггеров третьей группы, выходы которых подключены к информационным входам третьего узла приоритета, выходы которого поразрядно объединены через МОНТАЖНОЕ ИЛИ с входами первого узла приоритета и подключены к входам третьего элемента ИЛИ и являются выходами адреса считываемой заявки блока формирования заявок, выходы первого и второго элементов ИЛИ подключены к входам установки первого и второго триггеров соответственно, входы сброса которых подключены к выходам третьего и четвертого элементов ИЛИ соответственно, выходы первого и второго триггеров являются выходами признаков считывания и записи блока формирования заявок и подключены к первому и второму входам пятого элемента ИЛИ, выход которого подключен к входам синхронизации триггеров второй и третьей групп, выходы признаков нулевого состояния счетчиков заявок подключены к информационным входам первого узла приоритета, выход разрешения которого является входом пуска блока формирования заявок, инверсные выходы младших разрядов выходов первого и второго узлов приоритета подключены к входам разрешения второго и третьего узлов приоритета соответственно.

2. Устройство по п. 1, отличающееся тем, что блок управления памятью содержит триггер, элемент ИЛИ и одновибратор, входы установки и сброса триггера подключены к первому и второму входам элемента ИЛИ и являются первым и вторым входами блока, выход триггера является первым выходом блока, выход элемента ИЛИ соединен через одновибратор со вторым выходом блока.

Текст

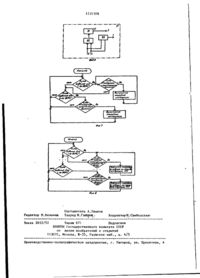

Изобретение позволяет реализовывать многопроцессорные системы с высоким быстродействием за счет ор ганизации асинхронного обращения процессоров через общую память. Конструкция предлагаемого устройства , ,содєржит 2К+! блоков ввода-вывода, где К определяется количеством подключаемых к устройству процессоров, пять мультиплексоров, демультиплексор, 2К+1 регистров, 2К+1 счетчиков адреса записи, 2К+1 счетчиков адреса считывания, дешифраторы сброса записанной и считанной заявки, блок управления памятью, блок формирования заявок и два элемента задержки. Работа устройства происходит в двух режимах записи и считывания заявок. 1 з.п. ф-лы. 8 ил, 1 табл. о 00 \ S і 1231508 2 Изобретение относится к вычисКаждый узел 33-35 приоритета лительной технике и может быть ис(фиг. 5) содержит группу элементов пользовано в автоматизированных сисИ 49 и группу элементов НЕ 50. темах управления для сопряжения проБлок 21 управления памятью цессоров. 5 (фиг. 6) содержит одновибратор 51, Целью изобретения является повыэлемент ИЛИ 52 и триггер 53. шение быстродействия. Вычислительная система (фиг. 1 ) , На фиг. \ приведен пример блокиспользующая предложенное устройстсхемы многопроцессорной системы с во, работает следующим обрадом^ использованием устройства для со10 С помощью магистрали системы в пряжения процессоров і на фиг, 2 оперативное запоминающее устройство функциональная схема устройства для (034)2 центрального МП 1 записывасопряжения процессоровJ на фиг. 3-6 ются содержание инструкции, которое функциональные схемы блока формированеобходимо выполнить, и исходные ния заявок, счетчика сообщений, уз- ' ( 5 данные, которые необходимы для выла приоритета и блока управления паполнения инструкции. Под управленимятью соответственно; на фиг. 7 и ем центрального МП с помощью устрой8 - примеры алгоритмов управления ства 4 для сопряжения производится местного и центрального процессоров перепись содержания инструкций и иссоответственно в составе многопро20 ходных данных к ним в ОЗУ 3 общего . цессорной системы. пользования, например, следующими Многопроцессорная система (фиг.1) сообщениями: содержит микропроцессоры (МП) 1,один из которых центральный, местные опе№№_МП Информация Код типа ративные запоминающие устройства 25 (5 бит) (8 бит) информации (ОЗУ) 2, общие ОЗУ 3, устройства 4 (3 бита); для сопряжения процессоров, через общую память. . Код типа информации определяет Устройство 4 для сопряжения проназначение информации согласно следуцессоров (фиг. 2) содержит с первого 30 ющей таблицы. 5 по (2К+1) 6 блоков ввода-вывода, где К определяется количеством под'Код типа Назначение информации ключаемых ^подключенных к уст- • информации ройству 4, с первого по третий муль, 000 Запрещена типлексоры 7-9, демультиплексор 10, 35 четвертый II и пятый 12 мультиплек001 Резервная соры, с первого ІЗ по (2К+1) І4 регистры, с первого 15 по (2К+1) 16 010 Данные (байт № 1 ) счетчики адреса записи, с первого 17 по (2К+1) 18 счетчики адреса счи40 011 тывания, дешифраторы 19 и 20 сброса • Данные (байт № 2) записанной и считанной заявки соответственно, блок 21 управления па100 Номер инструкции мятью, блок 22 формирования заявок, два элемента 23 и 24 задержки. Ї01 Программа инструкции» 45 (байт № 1) Блок 22 формирования заявок (фиг. 3) содержит первую, вторую и по третью группы триггеров, в которых Программа инструкции соответственно обозначены первый и (байт № 2) 2К+1 триггеры 25 и 26« 27 и 2 8 J 2 9 и' 50 111 30'; с первого по 2К+І счетчики 31 и Номер данного 32 заявок, три узла 33-35 приоритета^ пять элементов ИЛИ 36-40, два тригВ начале передается номер инструкгера 41 и 42. ции, программа выполнения инструкции, а потом номер данных и его значения Каждый счетчик 31 и 32 заявок 55 в виде байта № 1 и байта № 2. Обра(фиг. 4) содержит элемент ИЛИ 43, реверсивный счетчик 44, дешифратор щение центрального МП 1 к соответ45, элемент 46 задержки, два триггествующему устройству 4 происходит ра 47, 48. последовательно в порядке, опреде 4 З 1231 508 который поступает.на соответствующий ленном выполняемой инструкцией вход сброса записанной заявки блока Каждое устройство 4 может принимать 22 и сбрасывает заявку на запись сосообщения одновременно от 2К+1 местобщения в ОЗУ 3. ных ОЗУ 2 под управлением соответВ режиме Считывание при выполнествующих МП 1. Запись принятых сооб- нии заявки на считывание сообщения щений в соответствующие секции ОЗУ 3 из ОЗУ 3 по одному из выходов адреобщего пользования происходит послеса С

ДивитисяДодаткова інформація

Назва патенту англійськоюDevice for processor interface through common memory in multiprocessing system

Автори англійськоюYerzakov Yevhen Mykhailovych, Denischenko Ihor Yakovych, Holovin Viktor Ivanovych, Cherepiana Valentyna Ivanivna

Назва патенту російськоюУстройство для соединения процессоров через общую память в многопроцессорной системе

Автори російськоюЕрзаков евгений Михайлович, Денищенко Игорь Яковлевич, Головин Виктор Иванович, Черепьяная Валентина Ивановна

МПК / Мітки

МПК: G06F 15/16, G06F 15/167

Мітки: спільну, системі, пристрій, процесорів, з'єднання, пам'ять, багатопроцесорній

Код посилання

<a href="https://ua.patents.su/8-1839-pristrijj-dlya-zehdnannya-procesoriv-cherez-spilnu-pamyat-u-bagatoprocesornijj-sistemi.html" target="_blank" rel="follow" title="База патентів України">Пристрій для з’єднання процесорів через спільну пам’ять у багатопроцесорній системі</a>

Попередній патент: Спосіб хімічної очістки внутрішньої поверхні теплообмінників

Наступний патент: Розпилювач рідини

Випадковий патент: Роторно-поршнева машина