Контролер станції локальної мережі

Номер патенту: 2066

Опубліковано: 20.12.1994

Автори: Савчин Дмитро Васильович, Гавшин Ігор Дмитрович, Щербатюк Віктор Маркович

Формула / Реферат

Контроллер станции локальной сети, содержащий блок приема, блок передачи, процессор, блок памяти, блок постоянной памяти и блок сопряжения с абонентом, адресно-информационно-управляющий вход-выход процессора соединен с адресно-информационно-управляющим входом-выходом блока сопряжения с абонентом, адресно-информационно-управляющим входом-выходом блока постоянной памяти и адресно-информационно-управляющими входами-выходами блока приема и блока передачи, отличающийся тем, что, с целью повышения пропускной способности сети за счет уменьшения задержки на обработку информации в станции и уменьшения служебной информации в передаваемых пакетах, в него введен многоканальный коммутатор доступа к памяти, выход блока приема соединен с информационно-управляющими входами блока передачи и многоканального коммутатора доступа к памяти, первый информационно-управляющий вход-выход которого соединен с адресно-информационно-управляющим входом-выходом процессора, второй информационно-управляющий вход-выход многоканального коммутатора доступа к памяти соединен с информационно-управляющим входом-выходом блока передачи, третий информационно-управляющий вход-выход многоканального коммутатора доступа к памяти соединен с адресно-информационно-управляющим входом-выходом блока памяти, вход и выход блока сопряжения с абонентом являются входом и выходом контроллера для связи с абонентом, вход блока приема и выход блока передачи являются входом и выходом контроллера для подключения к физической среде передачи данных.

Текст

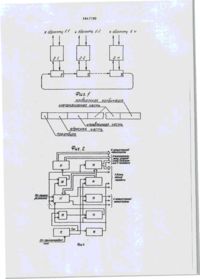

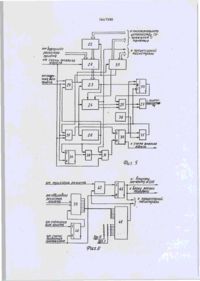

Изобретение относится к цифровым системам связи, в частности к локальным сетям передачи данных, и может быть использовано для обмена данными в локальных информационновычислительных и управляющих сетях. Цель изобретения - повышение пропускной способности сети за счет уменьшения задержек на обработку информации в станциях и уменьшения количества служебной информации в передаваемых пакетахв Контроллер станции локальной сети содержит профессор 6, блок 7 постоянной памяти, блок 9 сопряжения с абонентом и многоканальный коммутатор 10 доступа к памяти, блок 5 логики передачи, блок 4 логики приема и блок 8 памяти, В контроллере станции локальной сети блоки 4 и 5 для увеличения быстродействия используют прямой доступ к блоку 8 памяти. 6 ил. Каёсненту U СП СО К приемопередатчику Фт. 3 1647590 Изобретение относится к цифровым системам электросвязи, в частности к локальным сетям передачи данных, и может быть использовано для обмена данными в локальных информационновычислительных и управляющих сетях» Целью изобретения является повышение пропускной способности сети за счет уменьшения задержки на обработ- 10 ку информации в станции и уменьшения количества служебной информации в передаваемых пакетах. На фиг.1 представлена структура кольцевой локальной сети; на фиг.2 - І5 формат информационных кадров; на фнг.З - блок-схема контроллера станции локальной сети; на фиг,4 - структурная схема блока приема; на фиг.5 структурная схема блока передачи; 20 на фиг.6 - схема анализа адреса, вариант выполнения о Кольцевая локальная сеть содержит п абонентов I к п контроллеров 2 і(фиг.І), каждый из которых подключен 25 к физической среде передачи данных через приемопередатчик 3. Контроллер (фиг о 3) содержит блок 4 приема, блок 5 передачи» процессор 6, блок 7 постоянной памяти, блок 8 30 памяти, блок 9 сопряжения с абонентом и многоканальный коммутатор 10 доступа к памяти. Блок 4 приема (фиг.4) содержит декодер S2 линейного кода, счетчик 35 13 бит приема, сдвиговый регистр 14 приема, декодер і5 проверочного кода, буферный регистр 16 приема, схему 17 анализа адреса, схему 18 выделения промежутка, элементы И 19 40 и 20 и контролер ZX прямого доступа к памяти (КВДП). Блок 5 передачи (фнг,5) содержит буферный регистр 22 передачи, сдвиговый регистр 23 передачи, кодер 45 24 проверочного кода, мультиплексор 25, счетчик 26 бит передачи, кодер 27 линейного кода, мультиплексоры 28-31, триггер 32 режима, триггер 33 выдачи, триггер 34 завершения тран50 сляции, элементы И 35 и 36, контроллер 37 прямого доступа к памяти и генератор 38 синхрочастоты передачи. Обмен информацией между абонентами, подключенными к сети, происходит следующим образом. Информация от абонента, предназначенная рд передачи удаленному абоненту сети, буферизуется в блоке 8 памяти контроллера и разбивается на пакеты. В адресной части каждого пакета контроллер помещает адрес удаленного контроллера абонента, затем преобразует пакет в кадр (формат кадра показан на фиг.2) и передает его удаленному контроллеру-получателю. Продвигаясь по кольцевой магистрали, кадр, как,правило, проходит через несколько транзитных контроллеров (станций), кроме случаев, когда станция-получатель является соседней со станцией-отправителем по направлению передачи. Каждый контроллер анализирует адресную часть кадра и, таким образом, отличает транзитные кадры от кадров, адресо- • ( ванных емуо Кадр, адресованный данному контроллеру, принимается им в блок 8 памяти, из которого затем принятая информация поступает к абоненту. Транзитные кадры транслируются контроллером (станцией) к следующей станции сети с минимальной задержкой. В случае, если в момент прихода транзитного кадра станция передает собственный кадр, транзитный кадр буферизуется в блоке 8 памяти данной станции и передается ею в кольцевую магистраль сразу после завершения передачи своего кадра. Таким образом,, каждая станция в активном состоянии осуществляет следующие режимы: прием н/нлн передача, трансляция. В режиме приема обработка поступающих на вход контроллера (станции) кадров производится следующим образом,, -Кадры, переданные удаленными станциями, поступают на вход декодера 12, который выделяет из линейного кода биты данных, а по характеристическим моментам синхронизации, содержащимся в линейном коде,- сккхрочастоту приема f n M . Схема 18 выделения промежутка анализирует наличие синхроимпульсов fnM*f выдает сигнал "Промежуток" в течение тех временных интервалов» когда на вход станции неСхема 17 анализа адреса (фиг.6) 55 поступает линейный код. При обнаружесодержит буферный регистр 39 адреса, нии первого синхроимпульса приема триггер 40 анализа адреса, схему 41 схема 18 выделения промежутка снимасравнения, элемент УЧШ 42 и триггер ет сигнал "Промежуток", Этот момент 43 приема. 1647 590 идентифицируется станцией кпк момент цу триггера 43 Приема и переводит начала приема кадра.^При приеме кадра его в единичное состояние. Сигнал с синхроимпульсы г ПДЛ поступают нл первыхода триггера 43 приема разрешает вый вход первого элемента И 19, , прохождение ciiHxpoitMuyjihcoB приема на второй вход которого поступает байтов через второй элемент И 20 сигнал "Промежуток", запрещающий прона вход запросов контроллеров 21 хождение синхроимпульсов через элепрямого доступа к памяти. Последний, мент И 19. Из-за инерционности схемы обращаясь к блоку 8 памяти через 18 выделения промежутка сигнал "Про- Ю многоканальный коммутатор, перепвсымежуток" снимается с некоторой завает байты принимаемого пакета в блок держкой относительно первого выделен8 памяти. Поскольку разделителем межного синхроимпульса f П Д А (соответстду кадрами, передаваемыми по кольцевующего биту преамбулы), в резульвой магистрали, служит межкадровый тате чего этот синхроимпульс не про- 15 промежуток (интервал молчания), проходит через элемент И 19. Вследствие цедура приема пакета продолжается до этого бит преамбулы уничтожается, тех пор, пока из линии в блок 4 приетак как запись в сдвиговый регистр ма поступает линейный код» После 14 приема, декодер 15 проверочного приема последнего бита кадра схема кода и счет синхроимпульсов ї:пмсчет20 18 выделения промежутка выдает сигнал чиком 13 бит приема производится, "Промежуток", прекращается выдача имначиная со второго синхроимпульса, пульсов синхрочастоты приема г п л Д десоответствующего первому биту приникодером 12 линейного кода. Сигналом маемого пакета» "Промежуток" обнуляется счетчик 13 25 бит приема, а также сбрасываются Под каждый восьмой импульс fn;WHa триггер 40 анализа адреса и триггер выходе счетчика 13 бит приема появ43 приема в схеме 17 анализа адреса. ляется синхроимпульс приема байта, Передний фронт сигнала "Промежуток" означающий, что в сдвиговом регистре соответствует моменту окончания прие14 приема накоплен байт информации. Синхроимпульсом приема байта произ- 30 ма пакета (когда весь пакет принят водится перезапись накопленного бай~в блок 8 памяти станции, а на выходе та из сдвигового регистра 14 приема * декодера 15•проверочного кода устав буферный регистр 16 приема. По перновился результат анализа пакета на вому синхроимпульсу приема байта корректность). Этим фронтом осущесхема 17 анализа адреса анализирует ,, ствляется прерывание процессора 6, адресный байт пакета. При этом тригпо которому процессор 6 анализирует гером АО анализа адреса (фиг.6) выдекорректность принятого пакета (по ляется передний фронт первого синхросостоянию выхода декодера 15 проверочимпульса приема байта» Под этот фронт ного кода и его назначение (предназадресный байт из сдвигового регистра 40 наченный абоненту данной станции или 14 приема переписывается в буферный транзитный - по состоянию выхода схерегистр 39 адреса, с выходов которомы 41 сравнения). Блок 4 приема го поступает на вторую группу вхоготов к приему следующего кадра о » дов схемы 41 сравнения. На первой группе входов схемы 4 1 сравнения В каждой станции возможна конфликт45 присутствует значение собственного ная ситуация, когда на вход станции адреса станции, заданное с помощью приходит транзитный кадр, а станция перемычек между входами схемы 41 в этот момент передает свой кадр, сравнения и уровня логического нуля В этом случае транзитный кадр буфеи логической единицы. Если значение 50 ризуется в блоке 8 памяти станции и адресного байта сравнилось с заданпередается вслед за собственным кадным значением собственного адреса ром. При приеме транзитного кадра станции (контроллера), на выходе во время передачи своего кадра на высхемы 41 сравнения появляется сигнал ходе схемы 4І сравнения сигнал сравсравнения, служащий для перевода гг нения отсутствует, но триггер 43 станции в режим приема. При этом приема переведен в единичное состоясигнал с выхода схемы 41 сравнения ние сигналом с инверсного выхода через второй вход элемента ИЛИ 42 триггера 32 режима, поступающим на поступает на вход установки в единиход установки в единицу триггера 43 7 1647590 приема через первый вход элемента ИЛИ 42. Передачу собственного пакета стан-, ция может начать, если она не находится в режиме трансляции. Передачу ' инициирует процессор 6. Перед началом передачи он анализирует, находитг ся ли станция в режиме трансляции (по состоянию выхода схемы 48 выделе- ,« ния промежутка тл триггера 43 приема). Если в момент анализа схема J8 выделения промежутка выдает сигнал "Промежуток" или при отсутствии сигнала "Промежуток" триггер 43 приема нахо- ^ днтся в единичном состоянии (происходит прием кадра из кольцевой магистрали в блок 8 памяти станции), процессор 6 инициирует работу контроллера 37 прямого доступа к памяти, который обращается через многоканаль- 20 ный коммутатор 10 к блоку 8 памяти» считывает из блока 8 первый байт передаваемого пакета и выдает синхросигнал записи, по которому считанный 25 из блока 8 байт заносится в буферный регистр 22 передачи, а триггер 32 режима переводится в единичное состояние, соответствующее режиму передачи пакета. При этом через первый 30 элемент И 35 начинают проходить импульсы синхрочастоты передачи і:Пд от генератора 38, которые поступают на входы синхронизации сдвигового регистра 23 передачи, кодера 24 проверочного кода, счетчика 26 бит пере- 35 дачи, триггера 33 выдачи и кодера 27 линейного кода. Предварительно (передним фронтом сигнала с выхода триггера 32 режима) триггер 33 выдачи 40 устанавливается в исходное состояние, тем самым формируется однобитовая преамбула передаваемого кадра, необходимая для настройки декодера \2 линейного кода в станции-получателе 45 кадра. При поступлении первого импульса fniпреамбула выдается триггером 23 выдачи в кодер 27 и с его выхода в кольцевую магистраль. 8 через триггер 33 выдачи и первый мультиплексор 25 в кодер 27 линейного кода, который преобразует биты информации в линейный, например манчестерский, код и выдает его через приемопередатчик в кольцевую магистраль . Триггер 33 выдачи служит также для нормализации длительности битовых посылок. После записи последнего байта передаваемого пакета в буферный регистр 22 передачи, контроллер 37 прямого доступа к памяти выдает а кодер 24 проверочного кода сигнал, по которому кодер 24 проверочного кода переключает первый мультиплексор 25 и через его второй вход выдает в кодер 27 линейного кода проверочную комбинацию. Закончив выдачу проверочной комбинации, кодер 24 проверочного кода выдает процессору 6 прерывание, свидетельствующее о завершении передачи кодра, и сбрасывает триггер 32 режима. При этом запрещается прохождение импульсов синхрочастоты передачи f n . через первый элемент И 35, прекращается выдача в кольцевую магистраль линейного кода, что воспринимается другими станциями как промежуток. Если в блоке 8 станции имеются пакеты на передачу, процессор 6, получив прерывание, инициирует передачу следующего пакета, как это описано выше. Если за время передачи пакета в блоке 8 станции принят хотя бы один транзитный пакет, он передается в первую очередь, Если в блоке 8 станции нет пакетов на передачу, поступающие на ее вход транзитные кадры транслируются без буферизации в блок 8 О Байты транслируемого кадра, накапливаемые в сдвиговом регистре 14 .приема, как и при приеме, по синхроимпульсу приема байта переписываются в буферный регистр І6 приема, выходы которого в режиме трансляции через второй мультиплексор 28 подключены к Под первый импульс £„. (и далее 50 входам сдвигового регистра 23 перепод каждый восьмой) счетчиком 26 бит дачи. Первым синхроимпульсом приема передачи вырабатывается синхроимпульс байта триггер 32 режима в блоке 5 передачи байта, которым производится логики передачи устанавливается в запись байтов передаваемого пакета единичное состояние, и далее передача в сдвиговый регистр 23 передачи. 55 транслируемого кадра осуществляется Этот регистр выполняет параллельнотак же, как описано для режима перепоследовательное преобразование индачи за исключением того, что трансформации. Записываемые в него байты лируемый кадр не подвергается провервыдаются в последовательном виде 1647590 ке на корректность и кодированию кодером 24 проверочного кода в транслирующей станции. Он транслируется е без изменений в том виде, в котором был передан станцией-отправителем. Трансляция кадра заканчивается с помощью триггера 34 завершения трансляции, обеспечивающего передачу последнего байта транслируемого кадра, 10 после чего сбрасывается триггер 32 режима , * Для обмена информацией с абонентом в блок 8 станции выделены буфер- J5 нан зона приема и буферная зона передачи. При приеме из кольцевой магистрали информации» предназначенной абоненту, она накапливается в буферной зоне приема, из которой через 20 блок 9 сопряжения с абонентом передается к абоненту. Информация, подготовленная абонентом для передачи через локальную сеть, заносится в буферную зону передачи блока в памяти, 25 из которой передается в виде пакетов в кольцевую магистраль, .Схема 18 выделения промежутка представляет собой формирователь импуль- J0 сов длительностью, превышающей период тактовой частоты приема. За счет такого соотношения на выходе формирователя поддерживается низкий уровень до тех пор, пока на его вход поступа-35 ет тактовая частота приема. При наступлении межкадрового промежутка подача импульсов тактовой частоты приема на вход формирователя прекращается, при этом на его выходе уста- 40 навливается высокий уровень, соответствующий сигналу "Промежуток", При возобновлении тактовой частоты приема на выходе формирователя вновь устанавливается низкий уровень,* 45 10 Ф о р м у л а и з о б р е т е н и я Контроллер станции локальной сети, содержащий блок приема, блок передачи, процессор f блок памяти f блок постоянной памяти и блок сопряжения с абонентом, адресно-информационноуправляющий вход-выход процессора соединен с здресно-информационно-управляющим входом-выходом блока сопряжения с абонентом, адресно-информационно-управляющим входом-выходом блока постоянной памяти и адресно-ннформационно-управляющими входами-выходами блока приема и блока передачи, о т л и ч а ю щ и й с я тем, что, с целью повышения пропускной способности сети за счет уменьшения задержки на обработку информации в станции и уменьшения служебной информации в передаваемых пакетах» в него введен многоканальный коммутатор доступа к памяти, выход блока приема соединен с информационно-управляющими входами блока передачи и многоканального коммутатора доступа к памяти, первый информационно-управляющий вход-выход которого соединен с адресио-информационно-управляющим входом-выходом процессора, второй информационноуправляющий вход-выход многоканального коммутатора доступа к памяти с о е динен с информационно-управляющим входом-выходом блока передачи, третий информационно-управляющий вход-выход многоканального коммутатора доступа к памяти соединен с адресио-информационно—управляющим входом—выходом блока памяти, вход н выход блока сопряжения с абонентом являются входом и выходом контроллера для связи с абонентом, вход блока приема и выход блока передачи являются входом и выходом контроллера для подключения к физической среде передачи данньш. 1647590 к аЬоиентц Л к аЬо^еитц /.2 к абоненту 4 п 1 • 22 1 \ 5 J (Риг,/ ПРО he DO чная комбинация информационная пряжения с 1 21 ямЕу(рерио2о регистра приёма от схемы а адреса отсчетчика^ Sum приёма ,_у ' и процессорной магистрами 2$ 29 23 -if L 24 21 25 33 26 32 г 1 « f ^ анализа ' адреса .. w 5 ят второму , жменту и (20) к Елоку логши передачи ._ л к процессорной У магистрали от схепы Вшепеная Фиг.є 1647590 • • . ' Редактор Н.Гунько Составитель В.Бородин Техред М.Дидык Корректор Н.Ревская Зека» 1401 Тираж 418 Подписное ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35» Раушская наб,, д. 4/5 Производственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина, 101

ДивитисяДодаткова інформація

Назва патенту англійськоюController of station of local memory

Автори англійськоюScherbatiuk Viktor Markovych, Gavshyn Ihor Dmytrovych, Savchin Dmytro Vasyliovych

Назва патенту російськоюКонтроллер станции локальной сети

Автори російськоюЩербатюк Виктор Маркович, Гавшин Игорь Дмитриевич, Савчин Дмитрий Васильевич

МПК / Мітки

МПК: G06F 15/16

Мітки: мережі, станції, контролер, локальної

Код посилання

<a href="https://ua.patents.su/8-2066-kontroler-stanci-lokalno-merezhi.html" target="_blank" rel="follow" title="База патентів України">Контролер станції локальної мережі</a>

Попередній патент: Самохідний пристрій для транспортування та стикування труб

Наступний патент: Вимірювальний перетворювач струму

Випадковий патент: Спосіб бактерицидного впливу світлодіодного випромінювання апарату medolight red ha staphylococcus aureus