Пристрій для моделювання процесу передачі інформації

Номер патенту: 23270

Опубліковано: 19.05.1998

Автори: Козлов Олександр Леонідович, Корольова Любов Анатолійовна, Гришко Артур Віталійович

Формула / Реферат

Устройство для моделирования процесса передачи информации, содержащее формирователь команд, состоящий из генератора интервалов команд, генератор тактовых импульсов, суммирующего счетчика, блока памяти и элементов И и ИЛИ, первый и второй генераторы импульсов помех, первый формирователь импульсов, с первого по третий триггеры, реверсивный счетчик, вычитающий счетчик, первый дешифратор, первый элемент задержки, с первого по пятый элементы ИЛИ, с первого по одиннадцатый элементы И, причем вход запуска устройства соединен с первым входом первого элемента ИЛИ, второй вход которого связан выходом первого элемента И, выход первого элемента ИЛИ подан на инверсный единичный вход первого триггера, прямой выход которого соединен с вторым входом элемента И формирователя команд, первый вход которого связан с выходом генератора тактовых импульсов и с первым входом пятого элемента И устройства, в формирователе команд выход элемента И подан на суммирующий вход суммирующего счетчика, разрядные выходы которого соединены с информационными входами блока памяти, выходы которого связаны с соответствующими входами элемента ИЛИ и с соответствующими разрядными входами вычитающего счетчика устройства, разрядные выходы которого в устройстве поданы на соответствующие входы второго элемента ИЛИ, выход которого соединен с вторым входом пятого элемента И и с инверсным входом запуска первого формирователя импульсов, выход которого связан с первыми входами четвертого и шестого элементов И, выход пятого элемента И подан на вычитающий вход вычитающего счетчика, вход записи которого соединен с выходом пятого элемента ИЛИ, первый вход которого является выходом седьмого элемента И, первый вход которого соединен с выходом первого элемента задержки, первый установочный вход суммирующего счетчика формирователя команд объединен с четвертым входом третьего элемента ИЛИ устройства и с установочным входом реверсивного счетчика устройства, разрядные выходы которого поданы на соответствующие разрядные входы первого дешифратора, выходы которого связаны с соответствующими коммутирующими входами блока памяти формирователя команд, выход генератора интервалов команд в устройстве соединен с первыми входами третьих элементов И и ИЛИ, выход элемента ИЛИ формирователя команд в устройстве соединен с третьим входом десятого элемента И, первый вход которого объединен с первым входом одиннадцатого элемента И, выходы первого и второго генераторов импульсов помех соединенных соответственно с инверсным и с первым входами соответственно второго и восьмого элементов И, выходы которых поданы соответственно на инверсный нулевой и единичный входы соответственно второго и третьего триггеров, выход девятого элемента И связан с первым входом четвертого элемента ИЛИ, отличающееся тем, что оно дополнительно содержит с первого по четвертый суммирующие счетчики, второй дешифратор, регистр, блок сравнения кодов, формирователь интервалов запроса, с второго по четвертый формирователи импульсов и с второго по четвертый элементы задержки, причем установочный вход первого суммирующего счетчика объединен с первым входом первого элемента ИЛИ, выход которого соединен с четвертым входом третьего элемента ИЛИ и с инверсным входом запуска генератора интервалов команд, выход которого через третий элемент задержки связан с вторым установочным входом суммирующего счетчика формирователя команд, в устройстве выход третьего элемента ИЛИ соединен с прямым входом второго элемента И, инверсный вход которого связан с единичным входом второго триггера, прямой выход которого подан на вторые выходы третьего и шестого элементов И, инверсный выход второго триггера соединен с вторым входом четвертого элемента И, выход которого связан с вычитающим входом реверсивного счетчика и с входом сдвига блока памяти формирователя команд, вход записи которого в устройстве объединен с выходом третьего элемента И и с инверсным суммирующим входом реверсивного счетчика, разрядные выходы которого связаны с соответствующими разрядными входами регистра, выходы которого соединены с соответствующими входами первой группы блока сравнения кодов, выход которого соединен с вторым входом седьмого элемента И непосредственно и через четвертый элемент задержки с инверсным входом запуска третьего формирователя импульсов, выход которого связан с установочными входами третьего и четвертого суммирующих счетчиков и с вторым входом четвертого элемента ИЛИ, выход которого подан на инверсный вход запуска формирователя интервалов запроса, выход которого соединен с вторым входом восьмого элемента И и с инверсным входом запуска четвертого формирователя импульсов, выход которого связан с вторыми входами девятого, десятого и одиннадцатого элементов И и с инверсным нулевым входом третьего триггера, прямой выход которого подан на первый вход десятого элемента И, инверсный выход третьего триггера соединен с первым входом десятого элемента И, третий вход которого связан с инверсным входом одиннадцатого элемента И, выход которого соединен с суммирующим входом первого суммирующего счетчика непосредственно и через второй элемент задержки с прямым входом первого элемента И, инверсный вход которого связан с выходом переполнения первого суммирующего счетчика, выход десятого элемента И подан на вторые входы третьего и пятого элементов ИЛИ и на вход записи регистра, выход седьмого элемента И соединен с третьим входом третьего элемента ИЛИ, первый и четвертый входы которого связаны соответственно с суммирующими и установочными входами второго суммирующего счетчика, выход переполнения которого соединен с инверсным входом третьего элемента И, с третьими входами четвертого и шестого элементов И и с выходом запуска второго формирователя импульсов, выход которого подан на третий вход четвертого элемента ИЛИ, на запрещающий вход генератора интервалов команд формирователя команд и в устройстве на нулевой вход первого триггера, инверсный выход которого связан с третьим входом пятого элемента И, соответствующие выходы второй группы блока сравнения кодов соединены с разрядными выходами третьего суммирующего счетчика, инверсный суммирующий вход которого связан с входом первого элемента задержки и первым входом шестого элемента И, выход которого подан на суммирующий вход четвертого суммирующего счетчика, разрядные выходы которого поданы на соответствующие разрядные входы второго дешифратора, выходы которого соединены с соответствующими считывающими входами блока памяти формирователя команд, который состоит из параллельной группы n регистров, двух параллельных групп по n элементов И, параллельных групп (n-1) элементов ИЛИ, n элементов задержки, m элементов 2-nИ-ИЛИ из (n-1) параллельных групп по m элементов 2-2И-ИЛИ, причем входом записи блока памяти являются первые входы элементов И первой параллельной группы, выходы которых соединены с инверсными и первыми входами соответственно первых и вторых схем И всех элементов 2-2И-ИЛИ параллельных групп непосредственно и через соответствующие элементы задержки параллельной группы с входами записи соответствующих регистров параллельной группы, соответствующие коммутирующие входы блока памяти являются вторыми входами соответствующих элементов И первой параллельной группы, входом сдвига блока памяти являются первые входы элементов И второй параллельной группы, выходы которых поданы на сдвиговые входы соответствующих регистров параллельной группы, разрядные выходы которых связаны с первыми входами схем И, соответствующих номеру регистра параллельной группы, элементов 2-пИ-ИЛИ параллельной группы, соответствующих номеру разряда соответствующего регистра, разрядные выходы каждого последующего регистра параллельной группы поданы на прямые входы первых схем И соответствующих элементов 2-2И-ИЛИ каждого предшествующего регистра параллельной группы, информационные входы блока памяти являются соответствующими разрядными входами последнего регистра параллельной группы и вторыми входами вторых схем И соответствующих элементов 2-2И-ИЛИ в каждой из групп из m этих элементов 2-2И-ИЛИ, выходы которых связаны с соответствующими разрядными входами, кроме последнего, соответствующего регистра параллельной группы, первый из соответствующих считывающих входов блока памяти соединен с вторым входом первого элемента И второй параллельной группы и с первыми входами элементов ИЛИ параллельной группы, остальные из соответствующих считывающих входов блока памяти поданы на соответствующие входы соответствующего своего и всех последующих элементов ИЛИ параллельной группы, выходы которых связаны с вторыми входами соответствующих, кроме первого, элементов И второй параллельной группы, также соответствующие считывающие входы блока памяти являются вторыми входами соответствующих схем И каждого из элементов 2-пИ-ИЛИ параллельной группы, выходы которых являются выходами блока памяти.

Текст

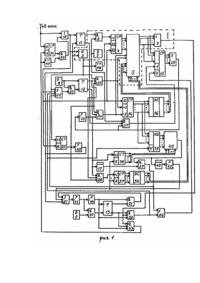

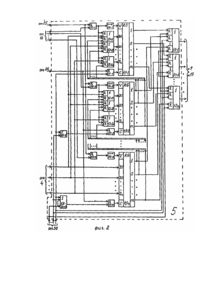

Изобретение относится к области вычислительной техники и может быть использовано, в частности, в специализированных средствах для моделирования процесса передачи информации. Известно устройство для моделирования процесса передачи информации, содержащее формирователь команд, состоящий из генератора интервалов команд, генератора тактовых импульсов, двухэлементов И, суммирующего и вычитающего счетчиков и элемента ИЛИ, генератор импульсов помех, триггер, три суммирующих счетчика, элемент задержки, двенадцать элементов И, четыре элемента ИЛИ, два регистра памяти, блок сумматоров по модулю два, два формирователя импульсов, элемент ИЛИ-НЕ, вход запуска устройства, выход не обнаруживаемых ошибок устройства, двенадцатый и шестой элементы И. Устройство позволяет исследовать процесс передачи информации в зависимости от уровня помех, действующих в прямом канале модели системы передачи информации с решающей обратной связью и мажоритарной обработкой на приемной стороне принимаемых повторов команд [1]. Недостатком этого устройства является то, что oho в модели системы передачи дискретной информации не обеспечивает учет влияния ошибок в обратном канале, искажающих сигналы запроса, а также это устройство не может моделировать передачу дискретной информации с адресным переспросом группы искаженных команд ввиду отсутствия в нем соответствующих запоминающих устройств. Известно также устройство для моделирования процесса передачи информации, содержащее формирователь команд, состоящий из генератора интервалов команд, генератора тактовых импульсов, элемента И, суммирующего счетчика, элемента ИЛИ, первого и второго блоков памяти, формирователь квитанции, состоящий из генератора тактовых импульсов, вычитающего счетчика трех элементов ИЛИ, трех элементов И, элемента задержки, два генератора импульсов помех, формирователь импульсов, четыре триггера, девять элементов И, пять элементов ИЛИ, реверсивный счетчик, элемент ИЛИ-НЕ, дешифратор, блок управления работой формирователя квитанций, состоящий из двух триггеров, двух элементов И, сумматора по модулю два, элементов НЕ и ИЛИ, В устройстве обеспечивается моделирование непрерывной передачи по прямому каналу на приемную сторону сигналов команд, имитируемых интервалами времени определенной длительности, с повторной передачей тех команд, квитанции на которые были приняты по обратному каналу с искажениями, возникающими из-за помех, действующих в прямом и обратном каналах [2]. К недостаткам данного устройства относится отсутствие возможности моделирования передачи дискретной информации в системе с разрешающей обратной связью, а также это устройство не может моделировать передачу дискретной информации с адресным переспросом группы искаженных команд ввиду отсутствия в нем соответствующих запоминающих устройств. Наиболее близким к предлагаемому техническим решением, выбранным в качестве прототипа, является устройство для моделирования процесса передачи информации, содержащее формирователь 1 команд, состоящих из генератора 2 интервалов команд, генератора 3 тактовых импульсов, двух элементов И 4 и 5, суммирующего 6 и вычитающего 7 счетчиков и элемента ИЛИ 8, формирователь 9 квитанций, состоящих из генератора 10 тактовых импульсов, трех элементов И 11-13, реверсивного счетчика 14, элемента ИЛИ 15, первый 16 и второй 17 генераторы импульсов помех, первый 18 формирователь импульсов, второй 19 и первый 20 триггеры, управляющий триггер 21, формирователь 22 интервалов запроса, суммирующий счетчик 23, шестой 24, первый 25, третий 26, второй 27, четвертый 28 и пятый 29 элементы И, первый 30 - четвертый 33 элементы ИЛИ, элемент задержки 34, третий 35 триггер, второй 36 формирователь импульсов, седьмой 37 - девятый 39 элементы И, пятый 40 элемент ИЛИ, вход 41 запуска устройства и выходы 42 и 43 установки режима работы устройства [3]. Работа данного устройства заключается в следующем. Допустим, что управляющий триггер 21 находится в нулевом состоянии, то есть модель функционирует в системе с ИОС. В этом случае элемент И 27 закрыт и через него сигналы не проходят. Все счетчики 6,7, 14 формирователи 1 команд и формирователя 9 квитанций находятся в нулевом состоянии. По сигналу, поступающему на вход 41 запуска, обнуляется суммирующий 23 счетчик и через ИЛИ 30 запускается генератор 2 интервалов команд, который формирует на своем выходе единичный сигнал, длительность которого соответствует длительности передаваемой команды по прямому каналу. Этим единичным сигналом открывается элемент И 4 формирователя 1 команд, закрывается элемент И 5 формирователя 1 команд и через элемент ИЛИ 8 открывается элемент И 11 формирователя 9 квитанций и элемент И 25, закрываются элементы И 12, 13 формирователя 9 квитанции. На суммирующие входы суммирующего 6 и реверсивного 14 счетчиков через соответствующие открытые элементы И 4 и 11 поступают тактовые импульсы от генератора 3 тактовых импульсов формирователя команд. Подсчитывая определенное число этих импульсов за интервал длительности команды, счетчики 6 и 14 косвенно фиксируют величину этого интервала. Сразу после окончания действия импульса команды закрывается элемент И 4, и на выходе элемента ИЛИ 8 формируется нулевой потенциал, который закрывает элемент И 11 и открывает элементы И 12, 13 формирователя 9 квитанции. Объединяя единичные сигналы с определенных выходов реверсивного счетчика 14, на входе элемента ИЛИ 15 формирователя 9 квитанций формируется единичный сигнал, который окончательно открывает элемент И 12 и через элемент И 13 открывает элемент И 26. Таким образом, устройство переходит в режим имитации передачи свертки (квитанции) команды по обратному каналу на передающую сторону. Тактовые импульсы с выхода генератора 10 через открытый элемент И 12 начинают поступать на вычитающий вход реверсивного счетчика 14 и уменьшают его состояние за среднее время Тг. По истечении времени Тг во время перепада единичного потенциала в нулевой на выходах элемента ИЛИ 15 и соответственно элемента И 13, на выходе формирователя 18 импульсов сформируется короткий по длительности импульс, который пойдет через открытый нулевым потенциалом с выхода элемента ИЛИ 32 элемент И 29 на его выход. Этот импульс на выходе элемента И 29 сигнализирует об окончании имитации передачи свертки (квитанции) команды на передающую сторону и является разрешением на передачу следующей команды. В устройстве этот импульс, во-первых,, увеличивает на единицу состояние суммирующего счетчика 23, что означает, что в системе с ИОС передана неискаженной первая команда и на нее получена неискаженная квитанция, во-вторых, проходя через элементы задержки 34, И 24, ИЛИ 30 на вход запуска генератора 2 интервалов команд, дает разрешение на формирование следующего импульса - команды, предварительно обнулив суммирующий счетчик 6. Если же во время передачи команды или квитанции на нее в прямом или обратном каналах соответственно действуют сигналы помех, формируемые соответственно генераторами 16, 17 импульсов помех, то эти сигналы через открытые соответственно элементы И 25,26 переведут в единое состояние триггеры 19 или 20 единичные сигналы с выходов которых через элемент ИЛИ 32 закроют элемент И 29 и откроют элемент И 28. В этом случае импульс, сформированный формирователем 18, пройдет через элементы И 28 и ИЛИ 33 на инверсный выход записи вычитающего счетчика 7 и перепишет в его число из счетчика 6, При этом на выходе элемента ИЛИ 8 опять формируется единичный потенциал и произойдет имитация повторной передачи команды, передача которой или квитанция на нее была искажена. Повторная передача этой команды будет происходить до тех пор, пока не будет промоделирована неискаженная передача этой команды и квитанции на нее. После имитации неискаженной передачи числа команд, которое определяется появлением единичного потенциала на выходе переполнения суммирующего счетчика 23, элемент И 24 запирается, и сигнал разрешения передачи очередной команды через него проходит, чем прекращается моделирование передачи информации в системе с информационной обратной связью. При установке триггера 21 в единичное состояние устройство переходит в режим моделирования передачи информации в системе с информационной решающей обратной связью. Отличие его в следующем. После неискаженного приема команды на приемной стороне следует передача квитанции на нее передающую сторону, как в системе с информационной обратной связью, и после неискаженного приема квитанции следует следующая команда. Если же произошло искажение команды, то приемная сторона передает вместо квитанции сигнал запроса повторной передачи команды, подвергающейся искажению. Причем, сам сигнал запроса может исказиться под действием помех в обратном канале. Поэтому его передача будет повторена до тех пор, пока передающая сторона не примет неискаженный сигнал запроса. Этот сигнал формируется во время перепада единичного потенциала в нулевой на выходе элемента ИЛИ 40. Сигнал запроса формируется, когда триггеры 19 и 21 находятся в единичном состоянии, то есть произошло искажение передачи команды. После окончания передачи команды искаженной команды перепад потенциала из единичного в нулевой проходит через элементы ИЛИ 8, Й 27 и ИЛИ 40 на вход формирователя 22 интервалов запроса, который и формирует сигналы запроса. Этот сигнал, предварительно обнулив реверсивный счетчик 14, обнуляет через элемент ИЛИ -31 триггер 19 своим срезом. После окончания действия сигнала запроса формирователь 36 импульсов сформирует короткий по длительности импульс, который" через открытый единичным потенциалом с инверсного выхода триггера 35 элемент И 39 и далее элемент ИЛИ 33 произведет запись в вычитающий счетчик 7 информацию, хранящуюся в суммирующем счетчике 6, чем производится начало повторной передачи искаженной команды. Далее функционирование устройства такое же, как в предыдущем случае. Если во время формирования сигнала запроса генератор 17 импульсов помех сформирует сигнал помехи в обратном канале, то этот сигнал через открытый сигналом запроса элемент 37 пройдет на вход триггера 35 и переведет его в единичное состояние. При этом элемент И 38 откроется и элемент И 39 закроется. После окончания действия сигнала запроса формирователь 36 сформирует импульс, который пройдет через элементы И 38 и ИЛИ 40 на вход формирователя 22, который опять вырабатывает сигнал запроса. Одновременно с этим своим срезом импульс с выхода формирователя 36 переведет триггер 35 в нулевое состояние. Так будет происходить до тех пор, пока триггер 35 будет переводиться сигналом помехи от генератора 17 в единичное состояние во время действия сигнала запроса. Однако в устройстве из-за отсутствия элементов, учитывающих длительность передаваемых команд в группах по прямому каналу, невозможно осуществить моделирование адресной повторной передачи искаженных команд. Таким образом, недостатком устройства-прототипа является недостаточные функциональные возможности, заключающиеся в невозможности этим устройством моделировать передачу дискретной информации с адресным переспросом группы искаженных команд. В основу изобретения поставлена задача создать такое устройство для моделирования процесса передачи информации, которое обладало бы расширенными функциональными возможностями за счет моделирования передачи дискретной информации с адресным переспросом группы искаженных команд. Технический результат, который может быть получен при осуществлении изобретения, заключается в получении опытным путем вероятностно-временных характеристик передачи информации в указанной модели системы связи при различных законах распределения интервалов команд и различных законов распределения вероятностей интервалов длительностей импульсов помех и интервалов времени между этими импульсами. Поставленная задача решается за счет того, что в устройство, содержащее формирователь 1 команд, состоящий из генератора 2 интервалов команд, генератора 3 тактовых импульсов, суммирующего счетчика 4, блока памяти 5 и элементов И 6 и ИЛИ 7, первый 8 и второй 9 генераторы импульсов помех, первый ТО формирователь импульсов, первый 11, второй 12, третий 13 триггеры, реверсивный счетчик 14, вычитающий счетчик 15, первый 16 дешифратор, первый 17 элемент задержки, первый 18, второй 19, третий 20, четвертый 21, пятый 22 элементы ИЛИ, первый 23, второй 24, третий 25, четвертый 26, пятый 27, шестой 28, седьмой 29, восьмой 30, девятый 31, десятый 32 и одиннадцатый 33 элементы И, причем вход запуска устройства соединен с первым входом первого 18 элемента ИЛИ, второй вход которого связан выходом первого 23 элемента И, выход первого 18 элемента ИЛИ подан на инверсный единичный вход первого 11 триггера, прямой выход которого соединен с вторым входом 6 элемента И формирователя команд, первый вход которого связан с выходом генератора 3 тактовых импульсов и с первым входом пятого 27 элемента И устройства, в формирователе команд выход элемента И 6 подан на суммирующий вход суммирующего счетчика 4, разрядные выходы которого соединены с информационными входами блока 5 памяти, выходы которого связаны с соответствующими входами элемента ИЛИ 7 и с соответствующими разрядными входами вычитающего счетчика 15 устройства, разрядные выходы которого в устройстве поданы на соответствующие входы второго 19 элемента ИЛИ, выход которого соединен с вторым входом пятого 27 элемента И и с инверсным входом запуска первого 10 формирователя импульсов, выход которого связан с первыми входами четвертого 26 и шестого 28 элементов И, выход пятого 27 элемента И подан на вычитающий вход вычитающего счетчика 15, вход записи которого соединен с выходом пятого 22 элемента ИЛИ, первый вход которого является выходом седьмого 29 элемента И, первый вход которого соединен с выходом первого элемента задержки 17, первый установочный вход суммирующего счетчика 4 формирователя команд объединен с четвертым входом третьего 20 элемента ИЛИ устройства и с установочным входом реверсивного счетчика 14 устройства, разрядные выходы которого поданы на соответствующие разрядные входы первого 16 дешифратора, выходы которого связаны с соответствующими коммутирующими входами блока памяти 5 формирователя команд, выход генератора 2 интервалов команд в устройстве соединен с первыми входами третьих элементов И 25 и ИЛИ 20, выход элемента ИЛИ 7 формирователя команд в устройстве соединен с третьим входом десятого 32 элемента И, первый вход которого объединен с первым входом одиннадцатого 33 элемента И, выходы первого 8 и второго 9 генераторов импульсов помех соединенных соответственно с инверсным и с первым входами соответственно второго 24 и восьмого 30 элементов И, выходы которых поданы соответственно на инверсный нулевой и единичный входы соответственно второго 12 и третьего 13 триггеров, выход девятого 31 элемента И связан с первым входом четвертого 21 элемента ИЛИ, дополнительно введены первый 34, второй 35, третий 36 и четвертый 37 суммирующие счетчики, второй 38 дешифратор, регистр 39, блок 40 сравнения кодов, формирователь 41 интервалов запроса, второй 42, третий 43, четвертый 44 формирователи импульсов и второй 45, третий 46, четвртый 37 элементы задержки, причем установочный вход первого 34 суммирующего счетчика объединен с первым входом первого 18 элемента ИЛИ, выход которого соединен с четвертым входом третьего 20 элемента ИЛИ и с инверсным входом запуска генератора 2 интервалов команд, выход которого через третий элемент 46 задержки связан с вторым установочным входом суммирующего счетчика 4 формирователя команд, в устройстве выход третьего 20 элемента ИЛИ соединен с прямым входом второго 24 элемента И, инверсный вход которого связан с единичным входом второго 12 триггера, прямой выход которого подан на вторые выходы третьего 25 и шестого 26 элементов И, инверсный выход второго 12 триггера соединен с вторым входом четвертого 26 элемента И, выход которого связан с вычитающим входом реверсивного счетчика 14 и с входом сдвига блока памяти 5 формирователя команд 1, вход записи которого в устройстве объединен с выходом третьего 25 элемента И и с инверсным суммирующим входом реверсивного счетчика 14, разрядные выходы которого связаны с соответствующими разрядными входами регистра 39, выходы которого соединены с соответствующими входами первой группы блока 40 сравнения кодов, выход которого соединен с вторым входом седьмого 29 элемента И непосредственно и через четвертый элемент 47 задержки с инверсным входом запуска третьего 43 формирователя импульсов, выход которого связан с установочными входами третьего 36 и четвертого 37 суммирующих счетчиков и с вторым входом четвертого 21 элемента ИЛИ, выход которого подан на инверсный вход запуска формирователя 41 интервалов запроса, выход которого соединен с вторым входом восьмого 30 элемента И и с инверсным входом запуска четвертого 44 формирователя импульсов, выход которого связан с вторыми входами девятого 31, десятого 32 и одиннадцатого 33 элементов И и с инверсным нулевым входом третьего 31 триггера, прямой выход которого подан на первый вход девятого 31 элемента И, инверсный выход третьего 31 триггера соединен с первым входом десятого 32 элемента И, третий вход которого связан с инверсным входом одиннадцатого 33 элемента И, выход которого соединен с суммирующим входом первого 34 суммирующего счетчика непосредственно и через второй элемент задержки с прямым входом первого 23 элемента И, инверсный вход которого связан с выходом переполнения первого 34 суммирующего счетчика, выход десятого 32 элемента И подан на вторые входы третьего 20 и пятого 22 элементов ИЛИ и на вход записи регистра 39, выход седьмого 2 элемента И соединен с третьим входом третьего 20 элемента ИЛИ, первый и четвертый входы которого связаны соответственно с суммирующим и установочным входами второго 35 суммирующего счетчика, выход переполнения которого соединен с инверсным входом третьего 25 элемента И, с третьими входами четвертого 26 и шестого 28 элементов И и с выходом запуска второго 42 формирователя импульсов, выход которого подан на третий вход четвертого 21 элемента ИЛИ, на запрещающий вход генератора 2 интервалов команд формирователя команд 1 и в устройстве на нулевой вход первого 11 триггера, инверсный выход которого связан с третьим входом пятого 27 элемента И, соответствующие выходы второй группы блока сравнения кодов 40 соединены-с разрядными выходами третьего суммирующего счетчика 36, инверсный суммирующий вход которого связан с входом первого элемента задержки 17 и первым входом шестого 28 элемента И, выход которого подан на суммирующий вход четвертого 37 суммирующего счетчика, разрядные выходы которого поданы на соответствующие разрядные входы второго 38 дешифратора, выходы которого соединены с соответствующими считывающими входами блока 5 памяти формирователя команд. Структурная схема предлагаемого устройства приведена на фиг. 1. Предлагаемое устройство содержит блок 5 памяти, который состоит из параллельной группы η регистров 49-1, 49-2.....49-n, двух параллельных групп по η элементов И 50-1, 50-2.....50-n и 51-1, 51-2.....51-n, из (n-1) параллельных групп по m элементов 2-2И-ИЛИ [52-11, 52-12..... 52-1 n], [52-21, 52-22..... 52-2n]..... [52-(n-1)1, 52(n-2).....52-{n-1)m], из параллельной группы т элементов 2-пИ-ИЛИ 53-1, 53-2..... 53-m, из параллельных групп n элементов задержки 54-1, 54-2, ..., 54-n и (n-1) элементов ИЛИ 55-1,55-2, ...,55-(п-1), причем входом записи блока 5 памяти являются первые входы элементов И 50-1, 50-2.....50-п первой параллельной группы, выходы которых соединены с инверсными и первыми входами соответственно первых и вторых схем И всех элементов 2-2И-ИЛИ [52-11, 52-12.....52-1 m], [52-21,52-22.....52-2m].....[52-(n-1)1, 52-(n-2)2.....52-(n-1)m] параллельных групп непосредственно и через соответствующие элементы задержки 54-1, 54-2, ..., 54-n параллельной группы с входами записи соответствующих регистров 49-1, 49-2.....49-n параллельной группы, соответствующие коммутирующие входы блока 5 памяти являются вторыми входами соответствующих элементов И 50-1, 50-2, ..., 50-n первой параллельной группы, выходом сдвига блока 5 памяти являются первые входы элементов И 51-1, 51-2, .... 51-n второй параллельной группы, выходы которых поданы на сдвиговые входы соответствующих регистров 49-1, 49-2,..., 49-n параллельной группы, разрядные выходы которых связаны с первыми входами схем И, соответствующих номеру регистра параллельной группы, элементов 2-nИ-ИЛИ 53-1. 53-2.....53-m параллельной группы, соответствующих номеру разряда соответствующего регистра, разрядные выходы каждого последующего регистра 49-2, 49-3.....49-n параллельной группы поданы на прямые входы первых схем И соответствующих элементов 2-2И-ИЛИ [52-11, 52-12, ..., 52-1 m], [52-21. 52-22.....52-2m].....[52-(n-1)1,52-{n-2)2......52-(-1)m] каждого предшествующего регистра 49-1, 49-2..... 49-(n-1) параллельной группы, информационные входы блока 5 памяти являются соответствующими разрядными входами последнего регистра 49-п параллельной группы и вторыми входами вторых схем И соответствующих элементов 2-2И-ИЛИ в каждой из групп из m этих элементов 2-2И-ИЛИ [5211, 52-12..... 52-1 m], [52-21, 52-22..... 52-2m]..... [52-{n-1)1,52-(n-2)2.....52-in-1)m], выходы которых связаны с соответствующими разрядными входами, кроме последнего 49-n, соответствующего регистра 49-1, 49-2, ..., 49-(n-1) параллельной группы, первый из соответствующих входов блока 5 памяти соединен с вторым входом первого элемента И 51-1 второй параллельной группы и с первыми входами элементов ИЛИ 55-1, 55-2, ..., 55(п-1) параллельной группы, остальные из соответствующих входов блока 5 памяти поданы на соответствующие входы соответствующего своего и всех последующих элементов ИЛИ 55-1, 55-2.....55-(n-1) параллельной группы, выходы которых связаны с вторыми входами соответствующих, кроме первого 5.1-1, элементов И 51-2,51-3.....51-n второй параллельной группы, также соответствующие считывающие входы блока 5 памяти являются вторыми входами соответствующих схем И каждого из элементов 2-nИ-ИЛИ 53-1, 53-2, .... 53-m параллельной группы, выходы которых являются выходами блока 5 памяти. Структурная схема блока памяти представлена на фиг. 2. Предлагаем положительную логику функционирования устройства. Генератор 2 интервалов команд вырабатывает короткие по длительности импульсы через интервалы времени, соответствующие длительностям передаваемых команд по прямому каналу, Первый из этих импульсов формируется по окончании действия сигнала, подаваемого на инверсный вход запуска генератора 2. С поступлением сигнала на запрещающий вход генератора 2 прекращается формирование импульсов окончания интервалов команд. Генератор 3 тактовых импульсов формирователя 1 команд вырабатывает периодическую последовательность импульсов периода следования Τ 1, который для повышения точности моделирования должен быть не более величины Та/100, где 1г - средняя длительность передаваемых команд. Разрядность суммирующего счетчика 4 формирователя 1 команд и вычитающего счетчика 15 устройства должна быть не менее величины log2. (Ζ/Τ1), где Ζ≥10Т2. Эти счетчики посредством импульсов от генератора 3 тактовых импульсов фиксируют и считывают длительности повторов команд. Первый 8 и второй 9 генераторы импульсов помех вырабатывают случайные импульсы с определенным законом распределения вероятностей интервалов длительностей самих импульсов и интервалов времени между соседними импульсами. Единичное состояние второго 12 или третьего 13 триггера соответствует ситуации, когда соответственно команда или сигнал запроса, передаваемые соответственно на приемную или передающую стороны, исказились соответственно в прямом или обратном канале под действием помех, вырабатываемых соответственно первым 8 или вторым 9 генератором импульсов помех. Первый 34 суммирующий счетчик подсчитывает количество групп команд, переданных и принятых на приемной стороне, то есть команд, объединенных в группы, на которые не был сформирован сигнал запроса повторной передачи приемной стороной. Второй 35 суммирующий счетчик подсчитывает число команд в одной группе. По достижении определенных чисел на выходах переполнения счетчиков 34 и 35 формируются высокие потенциалы. Блок 5 памяти рассчитан на хранение и выдачу η кодов длительностей команд одной группы, вследствие чего его основными звеньями являются η регистров 49-1, 49-2, .... 49-n разрядности m; предназначенных для хранения кодов длительностей тех команд из передаваемой группы, которые были искажены сигналами помех при передаче. Запись кодов осуществляется в тот из регистров 49-1, 49-2, ..., 49-n, у которого на входе соответствующий из элементов И 50-1, 50-2.....50-n открыт в момент записи единичным потенциалом от соответствующего выхода первого 16 дешифратора. В первые (n-1) регистров блока 5 на их разрядные входы коды длительностей искаженных команд подаются с разрядных выходов суммирующего счетчика 4 через элементы 2-2И-ИЛИ [52-11,52-12.....52-1 m], [52-21, 52-22.....52-2m].....[52-(n-1)1, 42-(n- 2)2.....52-(n-1)m], а в последний n-й регистр блока 5 информация подается непосредственно. Сдвиг информации из последующих регистров в предшествующие с меньшим на единицу номером осуществляется через эти же элементы 2-2ИИЛИ по сигналу сдвига, поступающему от четвертого 26 элемента И. Сдвиг информации происходит согласно разрешающих сигналов от второго 38 дешифратора, объединенных элементами ИЛИ 55-1, 55-2.....55-(n-1) по принципу "свой и все последующие", то есть если, например, у дешифратора 38 возбужден третий выход, то в блоке 5 памяти будут открыты элементы И 51-1, 51-2.....51-n, через которые пройдут сигналы сдвига на соответствующие сдвиговые входы регистров 49-3, 49-4, ..., 49-n. При этом произойдет сдвиг информации из последующего по номеру из перечисленных регистров в предшествующий кроме регистров 49-1 и 49-2, в которых останется информация, хранящаяся в них. Кроме этого, код длительности искаженной команды из соответствующего регистра подключается на выход блока 5 с помощью сборок 2-nИ-ИЛИ 53-1, 53-2.....53-m в соответствии с возбужденным выходом дешифратора 38. Для нормальной записи информации в регистры блока 5 и сдвига информации из регистра в регистр время задержки элементами 54-1, 54-2, .,., 54-n должно быть больше времени срабатывания элементов 2-2И-ИЛИ [52-11, 52-12..... 52-1m], [52-21, 52-22..... 522m].....[52-(n-1)1, 52-{n-2)2.....52-(n-1)m), но меньше длительности импульса, вырабатываемого первым 10 формирователем импульсов. Разрядность счетчиков 14, 35, 36 и 37 определяется числом команд, объединяемых в группы при передаче. Формирователь 41 интервалов запроса вырабатывает импульсы, длительность которых соответствует длительности передаваемых сигналов запроса по обратному каналу. Формирователи импульсов 10, 42, 43 и 44 формируют короткие по длительности импульсы. Срабатывание функциональных элементов, в основу которых положена тригерная ячейка, а именно: генератора 2 интервалов команд, счетчиков 4, 14, 15, 34, 35, 36 и 37, триггеров 11, 12 и 13, блока 5 памяти, регистра 39, а также формирователей 10, 41, 42, 43 и 44, или переход их в соответствующее состояние происходит по переднему фронту импульсов, передаваемых на прямые соответствующие входы этих элементов, и по задним срезам импульсов, подаваемых на соответствующие инверсные входы этих элементов. Время задержки второго 45 элемента задержки определяется временем срабатывания первого 34 суммирующего счетчика. Время срабатывания четвертого 47 и первого 17 элементов задержки определяется временем срабатывания соответственно третьего 36 и четвертого 37 суммирующих счетчиков и блоков 40 сравнения кодов. Задержка элемента задержки 46определяется временем записи информации из счетчика 4 в регистры блока 5 памяти. Блок 40 сравнения кодов вырабатывает нулевойпотенциал на своем выходе в случае равенства двоичных чисел, подаваемых на его соответствующие входы первой и второй группы. Работа предлагаемого устройства заключается в следующем. Предварительно предположим, что счетчики 15, 36 и 37, триггеры 11 и 13, регистр 39 и регистры блока 5 памяти находятся в нулевом состоянии. По сигналу, поступающему на вход 48 запуска устройства, обнуляется суммирующий счетчик 34 и через первый 18 элемент ИЛИ запускается генератор 2 интервалов команд, триггер 11 переводится в единичное состояние и обнуляются счетчики 4, 14 и 35. Единичным потенциалом с прямого выхода триггера 11 открывается элемент И 6, вследствие чего на суммирующий вход счетчика 4 поступают тактовые импульсы от генератора 3 тактовых импульсов. Подсчитывая определенное число этих импульсов за интервал длительности команды, то есть до момента выработки короткого по длительности импульса после запуска генератором 2 интервалов команд, счетчик 4 косвенно фиксирует величину этого интервала. По истечении интервала длительности команды на входе генератора 2 формируется короткий по длительности импульс, который сигнализирует об окончании имитации передачи неискаженной команды на передающую сторону. В устройстве этот импульс, во-первых, увеличивает на единицу состояния суммирующего счетчика 35 и, во-вторых, обнуляет счетчик 4 формирователя 1 команд. После имитации передачи определенного числа команд объединенных в группу, на выходе переполнения счетчика 35 формируется высокий потенциал, вследствие чего формирователь импульсов 42 выработает короткий по длительности импульс. Этот импульс обнуляет триггер 11 и запрещает функционирование генератора 2 интервалов команд, а также через элемент ИЛИ 21 запускает формирователь 41 интервалов запроса, на выходе которого вырабатывается единичный потенциал. По окончании сигнала запроса на выходе формирователя 44 импульсов вырабатывается короткий по длительности импульс, который, проходя через элемент И 33, увеличивает на единицу состояние счетчика 34, что означает прием приемной стороной одной группы неискаженных команд, а, проходя через элементы задержки 45, И 23 и ИЛИ 18, разрешает формирование следующей группы команд, запустив генератор 2, обнулив счетчик 4 и 35 и приведя в единичное состояние триггер 11. В случае, если во время имитации передачи группы команд действует сигналы помех от генератора 8 импульсов помех, устройство функционирует следующим образом. В момент действия сигнала помехи триггер 12 переводится в единичное состояние, вследствие чего открывается элемент И 25. В момент окончания интервала команды импульс от генератора 2 проходит через элемент И 25 и проходит запись кода числа длительности искаженной команды в первый регистр блока 5 памяти из счетчика 4, после чего счетчик 4 обнуляется, а состояние счетчика 14 увеличивается на единицу. Если в момент действия импульса окончания команды импульс помехи от генератора 8 не прекратит свое действие, то есть элемент И 24 будет закрыт, то триггер 12 останется в единичном состоянии, что будет означать искажение следующей команды. Если же сигнал помехи прекратится до окончания искаженной команды, то импульс от генератора 2 через элементы ИЛИ 20 и И 24 обнулит триггер 12. Так как счетчик 14 перейдет в следующее состояние, то у дешифратора 16 возбудится очередной выход, вследствие чего код длительности очередной искаженной команды запишется в следующий регистр блока 5 памяти (допустим, во второй 49-2). В случае, когда хотя бы в одном регистре блока 5 памяти хранится нулевой код, на выходе элемента ИЛИ 7 вырабатывается единичный потенциал, открывающий элемент И 32 и закрывающий элемент И 33. При этом после формирования сигнала запроса после имитации передачи группы команд импульс от формирователя 44 импульсов проходит через элементы И 32 и ИЛИ 22 на вход записи вычитающего счетчика 15, вследствие чего переписывается из блока 5 код его первого регистра 49-1, так как счетчик 37 находится в нулевом состоянии и у дешифратора 38 возбужден его первый выход, который подключает к выходам блока 5 разрядные ячейки его первого 49Ί регистра. Одновременно с этим регистр 39 перепишется код числа искаженных команд в группе из счетчика 14 и обнулится триггер 12, если в это время не действует сигнал помехи от генератора 8. Предположим теперь, что β процессе повторного считывания длительностей искаженных команд не будет происходить процесс их повторного искажения. В этом случае с записью информации в вычитающий счетчик 15 на выходе элемента ИЛИ 19 формируется единичный потенциал, открывающий элемент И 27, через который на вычитающий вход счетчика 15 начнут поступать тактовые импульсы от генератора 3. Через интервал длительности первой искаженной команды в переданной группе счетчик 15 обнулится, вследствие чего элемент И 27 закроется, а формирователь импульсов 10 выработает короткий по длительности импульс. Этот импульс пройдя через элемент И 26, произойдет сдвиг информации из поступающих регистров в предыдущие в блоке 5 памяти и уменьшает на единицу состояние счетчика 14, а непосредственно - увеличивает на единицу состояние счетчика 36, а, пройдя через элемент задержки 17, И 29 и ИЛИ 22, перепишет в счетчик 15 состояние опять первого 49-1 регистра блока 5 памяти. Это состояние будет уже соответствовать коду длительности второй искаженной команды в переданной группе. Так будет происходить, пока не будет проимитирована передача длительностей повторов всех искаженных команд. После того, как будет промоделирована неискаженная передача повторов всех искаженных команд в группе, счетчик 36 подсчитает число повторов команд, равное числу, хранящемуся регистре 39. В этом случае на выходе блока 40 сравнения кодов вырабатывается нулевой потенциал, вследствие чего на выходе формирователя импульсов 43 вырабатывается короткий по длительности импульс, который обнулит счетчик 36 и запустит формирователь 41. После формирования неискаженного сигнала запроса будет моделироваться передача следующей группы команд по приведенному выше алгоритму. Далее будет рассмотрен случай, когда во время моделирования повторной передачи искаженных команд опять произойдет искажение некоторых из них. Для примера, допустим, что при передаче группы команд пятеро из них было искажено. И при этом при повторной передаче вторая, третья и пятая искаженные команды опять подвергнутся повторному искажению. В этом случае при имитации повторной передачи второй искаженной команды закроется элемент И 26 и откроется элемент И 28, что повлечет за собой сдвига информации в регистрах блока 5 и счетчик 14 не уменьшит свое состояние; вместе с тем, у счетчика 14 останется четвертое состояние после неискаженной передачи первой искаженной команды. Наряду с этим, состояние счетчика 37 увеличится на единицу, у дешифратора 38 возбудится второй выход, вследствие чего к выходам блока 5 будут подключены ячейки памяти его второго 49-2 регистра, в котором будет теперь храниться код длительности третьей искаженной команды, а в первом 49-1 регистре блока 5 будет храниться код второй команды, при передаче повтора которой опять произошло ее искажение. Импульс от формирователя 10 вызовет имитацию повтора третьей искаженной команды по вышеприведенному алгоритму, после чего состояние cчетчика 37 увеличится еще на единицу и на выходе дешифратора 38 возбудится его третий выход. В этом случае к выходам блока 5 будет подключен код его третьего 49-3 регистра, соответствующий длительности четвертой искаженной команды. После искаженного повтора четвертой искаженной команды состояние счетчика 14 уменьшается на единицу, то есть будет соответствовать третьему состоянию, а в блоке 5 памяти информация из четвертого 49-4 регистра перепишется в третий 49-3, после чего информация из третьего 49-3 регистра блока 5 будет опять считана и будет произведен повтор пятой искаженной команды. После имитации передачи повтора пятой последней искаженной команды счетчик 14 будет находиться в третьем состоянии, регистр 39 - в пятом, счетчик 36 - в пятом и счетчик 37 - в третьем. В этом случае у дешифратора 38 возбудится четвертый выход, вследствие чего к выходам блока 5 будет подключен код его четвертого 49-4 регистра. После того, как счетчик 36 перейдет в пятое состояние импульсом от формирователя 10, коды регистра 39 и счетчика 36 сравняются и на выходе блока 40 сравнения кодов сформируется нулевой потенциал, который вызовет срабатывание формирователя импульсов 43. Импульс от формирователя 43 импульсов обнулит счетчики 36 и 37 и запустит формирователь 41. Так как счетчик 37 обнулится, то у дешифратора 38 опять возбудится первый выход, который скоммутирует на выходы блока 5 код, хранящийся в его первом 49-1 регистре, вследствие чего на выходе элемента ИЛИ 7 сформируется единичный потенциал, открывающий элемент И 32. После формирования сигнала запроса импульс от формирователя 44 пройдет через элемент И 32 и произведет запись в регистр 39 третьего состояния из счетчика 14, после чего будет повторен алгоритм моделирования повторной передачи команд, коды длительностей которые хранятся в регистрах блока 5 памяти. Имитация повторной передачи искаженных команд будет происходить по вышеприведенному алгоритму функционирования устройства до тех пор, пока не будет промоделирована их передача без искажения сигналами помех, то есть тогда, когда во всех регистрах блока 5 будут храниться нулевые коды. В этом случае на выходе элемента ИЛИ 7 сформируется нулевой потенциал, открывающий элемент И 33, вследствие чего после формирования сигнала запроса импульс от формирователя 44 пройдет через элемент И 33, чем вызовет формирование интервалов следующей группы команд. В случае, если во время формирования сигнала запроса второй 9 генератор импульсов помех сформирует сигнал помехи в обратном канале, то этот сигнал через открытый сигналом запроса восьмой 30 элемент И пройдет единичный вход второго 13 триггера и переведет его в единичное состояние. При этом элемент И 31 откроется, а элементы И 32 и 33 закроются. После окончания действия сигнала запроса формирователь 44 сформирует импульс, который пройдет через элементы И 31 и ИЛИ 21 на инверсный вход запуска формирователя 41, который опять выработает сигнал запроса. Вместе с этим своим задним фронтом импульс с выхода формирователя 44 переведет триггер 13 в нулевое состояние. Так будет проходить до тех пор, пока триггер 13 будет переводиться сигналом помехи от генератора 9 в единичное состояние во время действия сигнала запроса. После имитации неискаженной передачи числа групп команд, определяемым появлением единичного потенциала на выходе переполнения первого 34 суммирующего счетчика, элемент И 23 закроется и сигнал разрешения формирования интервалов очередной группы команд через него не пройдет, что приводит к прекращению моделирования передачи информации в системе с решающей обратной связью с адресным переспросом.

ДивитисяДодаткова інформація

Автори англійськоюKozlov Oleksandr Leonidovych, Hryshko Artur Vitaliiovych, Koroliova Liubov Anatoliiovna

Автори російськоюКозлов Александр Леонидович, Грушко Артур Витальевич, Королева Любовь Анатольевна

МПК / Мітки

МПК: G06F 15/00

Мітки: пристрій, процесу, інформації, передачі, моделювання

Код посилання

<a href="https://ua.patents.su/8-23270-pristrijj-dlya-modelyuvannya-procesu-peredachi-informaci.html" target="_blank" rel="follow" title="База патентів України">Пристрій для моделювання процесу передачі інформації</a>

Попередній патент: Пристрій для компостування органо-мінеральних відходів

Наступний патент: Установка для розливу сплавів

Випадковий патент: Спосіб отримання трести конопель осіннього приготування з паралельним розташуванням стебел