Пристрій для додавання послідовності чисел із плаваючою точкою

Номер патенту: 50428

Опубліковано: 15.10.2002

Автори: Долголенко Олександр Миколайович, Луцький Георгій Михайлович, Порєв Віктор Миколайович, Блінова Тетяна Олександрівна

Формула / Реферат

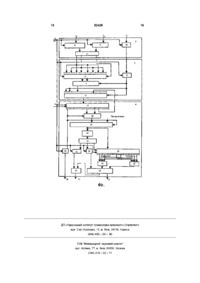

Пристрій для додавання послідовності чисел із плаваючою точкою, що містить тактовий вхід, блок керування, який містить вхід знака, вхід мантиси, вхід порядку, тригер керування, регістри мантиси та порядку, перший вузол пам'яті, причому інформаційні входи регістра мантиси, регістра порядку й тригера керування приєднані відповідно до входу мантиси, входу порядку і входу знака блока керування, а тактові входи регістра мантиси й регістра порядку з'єднані з тактовим входом пристрою, та блок підсумовування, який містить регістр мантиси, тригер переносу, суматор мантиси, причому тактовий вхід пристрою з'єднаний з тактовими входами регістра мантиси та тригера переносу, який відрізняється тим, що додатково введено блок формування результату, який містить вхід обнулення, регістр, комутатор результату, суматор результату, першу групу із m (n-1)- входових елементів "АБО", де n – розрядність мантиси, ![]() а Рмакс - максимальний порядок доданків, другий вузол пам'яті, тригер знака, регістр порядку, тригер перестановок, регістр результату, другу групу з

а Рмакс - максимальний порядок доданків, другий вузол пам'яті, тригер знака, регістр порядку, тригер перестановок, регістр результату, другу групу з ![]() (n-1)- входових елементів "АБО", третю групу з

(n-1)- входових елементів "АБО", третю групу з ![]() (n-1) - входових елементів "АБО", третій вузол пам'яті, суматор порядків, вихід знака, вихід порядку, n- розрядний вихід мантиси, причому тактовий вхід пристрою з'єднаний з тактовими входами регістра, тригера знака, регістра порядку, тригера перестановок та регістра результату, а вхід обнулення зв'язаний з керуючим входом встановлення в нуль регістра, вихід якого зв'язаний із другою групою входів суматора мантиси блока підсумовування, вихід котрого приєднаний до входу регістра, вихід старшого розряду котрого з'єднаний з інформаційним входом тригера знака, з входом переносу суматора результату та з керуючим входом комутатора результату, перший та другий інформаційні входи котрого з'єднані відповідно з прямим та інверсним виходами m(n-1) молодших розрядів регістра, а вихід комутатора результату приєднаний до першої групи входів суматора результату, другу групу входів котрого підключено до входу "Логічний нуль", вихід суматора результату приєднаний до входів регістра результату, а також до відповідних входів першої групи (n-1)- входових елементів "АБО", виходи котрих з'єднані з m- розрядним адресним входом другого вузла пам'яті, перший, другий і m- розрядний третій, виходи котрого з'єднані відповідно з інформаційним входом регістра порядку, інформаційним входом тригера перестановок і з керуючими входами з керуючими входами встановлення в нуль кожної із m (n-1)- розрядних груп регістра результату, виходи усіх непарних (n-1)- розрядних груп виходів котрого з'єднані зі входами другої групи із (n-1)

(n-1) - входових елементів "АБО", третій вузол пам'яті, суматор порядків, вихід знака, вихід порядку, n- розрядний вихід мантиси, причому тактовий вхід пристрою з'єднаний з тактовими входами регістра, тригера знака, регістра порядку, тригера перестановок та регістра результату, а вхід обнулення зв'язаний з керуючим входом встановлення в нуль регістра, вихід якого зв'язаний із другою групою входів суматора мантиси блока підсумовування, вихід котрого приєднаний до входу регістра, вихід старшого розряду котрого з'єднаний з інформаційним входом тригера знака, з входом переносу суматора результату та з керуючим входом комутатора результату, перший та другий інформаційні входи котрого з'єднані відповідно з прямим та інверсним виходами m(n-1) молодших розрядів регістра, а вихід комутатора результату приєднаний до першої групи входів суматора результату, другу групу входів котрого підключено до входу "Логічний нуль", вихід суматора результату приєднаний до входів регістра результату, а також до відповідних входів першої групи (n-1)- входових елементів "АБО", виходи котрих з'єднані з m- розрядним адресним входом другого вузла пам'яті, перший, другий і m- розрядний третій, виходи котрого з'єднані відповідно з інформаційним входом регістра порядку, інформаційним входом тригера перестановок і з керуючими входами з керуючими входами встановлення в нуль кожної із m (n-1)- розрядних груп регістра результату, виходи усіх непарних (n-1)- розрядних груп виходів котрого з'єднані зі входами другої групи із (n-1) ![]() - входових елементів "АБО" таким чином, що виходи усіх k-x розрядів цих груп приєднані до входів k-ого елемента "АБО", і аналогічно, виходи усіх парних (n-1)- розрядних груп виходів регістра результату з'єднані зі входами третьої групи із (n-1)

- входових елементів "АБО" таким чином, що виходи усіх k-x розрядів цих груп приєднані до входів k-ого елемента "АБО", і аналогічно, виходи усіх парних (n-1)- розрядних груп виходів регістра результату з'єднані зі входами третьої групи із (n-1) ![]() - входових елементів "АБО" таким чином, що виходи усіх k-x розрядів цих груп приєднані до входів k-ого елемента "АБО", виходи другої групи елементів "АБО" та виходи третьої групи елементів "АБО" з'єднані відповідно з другим та третім адресними входами третього вузла пам'яті, перший адресний вхід якого приєднаний до виходу тригера перестановок, а перший вихід третього вузла пам'яті з'єднаний з другою групою входів суматора порядку, перша група входів котрого з'єднана з виходом регістра порядку, вихід суматора порядку з'єднаний з виходом порядку, вихід тригера знака з'єднаний з виходом знака, а другий вихід третього вузла пам'яті приєднаний до виходу мантиси, причому виходи регістрів мантиси та порядку блока керування з'єднані з адресними входами першого вузла пам'яті, а тактовий вхід пристрою з'єднаний з тактовим входом тригера керування, вихід котрого з'єднаний з інформаційним входом тригера переносу блока підсумовування, котрий містить комутатор, керуючий вхід якого з'єднаний з виходом тригера переносу, з входом переносу та з двома старшими розрядами першої групи входів суматора мантиси, вихід комутатора зв'язаний з молодшими розрядами першої групи входів суматора мантиси, перший та другий інформаційні входи комутатора з'єднані відповідно з прямим та інверсним виходами (n-1)·m- розрядного регістра мантиси, усі непарні (n-1)- розрядні групи інформаційних входів котрого з'єднані з першим (n-1)- розрядним виходом першого вузла пам'яті блока керування, другий (n-1)- розрядний вихід котрого зв'язаний з усіма парними (n-1)- розрядними групами інформаційних входів регістра мантиси блока підсумовування, керуючі входи встановлення в нуль кожної із m груп якого приєднані до третього m- розрядного виходу першого вузла пам'яті блока керування.

- входових елементів "АБО" таким чином, що виходи усіх k-x розрядів цих груп приєднані до входів k-ого елемента "АБО", виходи другої групи елементів "АБО" та виходи третьої групи елементів "АБО" з'єднані відповідно з другим та третім адресними входами третього вузла пам'яті, перший адресний вхід якого приєднаний до виходу тригера перестановок, а перший вихід третього вузла пам'яті з'єднаний з другою групою входів суматора порядку, перша група входів котрого з'єднана з виходом регістра порядку, вихід суматора порядку з'єднаний з виходом порядку, вихід тригера знака з'єднаний з виходом знака, а другий вихід третього вузла пам'яті приєднаний до виходу мантиси, причому виходи регістрів мантиси та порядку блока керування з'єднані з адресними входами першого вузла пам'яті, а тактовий вхід пристрою з'єднаний з тактовим входом тригера керування, вихід котрого з'єднаний з інформаційним входом тригера переносу блока підсумовування, котрий містить комутатор, керуючий вхід якого з'єднаний з виходом тригера переносу, з входом переносу та з двома старшими розрядами першої групи входів суматора мантиси, вихід комутатора зв'язаний з молодшими розрядами першої групи входів суматора мантиси, перший та другий інформаційні входи комутатора з'єднані відповідно з прямим та інверсним виходами (n-1)·m- розрядного регістра мантиси, усі непарні (n-1)- розрядні групи інформаційних входів котрого з'єднані з першим (n-1)- розрядним виходом першого вузла пам'яті блока керування, другий (n-1)- розрядний вихід котрого зв'язаний з усіма парними (n-1)- розрядними групами інформаційних входів регістра мантиси блока підсумовування, керуючі входи встановлення в нуль кожної із m груп якого приєднані до третього m- розрядного виходу першого вузла пам'яті блока керування.

Текст

Пристрій для додавання ПОСЛІДОВНОСТІ чисел із плаваючою точкою, що містить тактовий вхід, блок керування, який містить вхід знака, вхід мантиси, вхід порядку, тригер керування, регістри мантиси та порядку, перший вузол пам'яті, причому інформаційні входи регістра мантиси, регістра порядку й тригера керування приєднані ВІДПОВІДНО ДО входу мантиси, входу порядку і входу знака блока керування, а тактові входи регістра мантиси й регістра порядку з'єднані з тактовим входом пристрою, та блок підсумовування, який містить регістр мантиси, тригер переносу, суматор мантиси, причому тактовий вхід пристрою з'єднаний з тактовими входами регістра мантиси та тригера переносу, який відрізняється тим, що додатково введено блок формування результату, який містить вхід обнуления, регістр, комутатор результату, суматор результату, першу групу із m (n-1)входових елементів "АБО", де п - розрядність мат= нтиси, і ' -1' а Рмакс - максимальний порядок доданків, другий вузол пам'яті, тригер знака, регістр порядку, тригер перестановок, ре Г0 5т1 (л-Л пстр результату, другу групу з ' '? ' ч ' входових елементів "АБО", третю групу з (т - ,5т\) (п-1) _ в х о д о в и х елементів "АБО", третій вузол пам'яті, суматор порядків, вихід знака, вихід порядку, п- розрядний вихід мантиси, причому тактовий вхід пристрою з'єднаний з тактовими входами регістра, тригера знака, регістра порядку, тригера перестановок та регістра результату, а вхід обнуления зв'язаний з керуючим входом встановлення в нуль регістра, вихід якого зв'язаний із другою групою входів суматора мантиси блока підсумовування, вихід котрого приєднаний до входу регістра, вихід старшого розряду котрого з'єд наний з інформаційним входом тригера знака, з входом переносу суматора результату та з керуючим входом комутатора результату, перший та другий інформаційні входи котрого з'єднані ВІДПОВІДНО з прямим та інверсним виходами m(n-1) молодших розрядів регістра, а вихід комутатора результату приєднаний до першої групи входів суматора результату, другу групу входів котрого підключено до входу "Логічний нуль", вихід суматора результату приєднаний до входів регістра результату, а також до ВІДПОВІДНИХ ВХОДІВ першої групи (п-1)- входових елементів "АБО", виходи котрих з'єднані з т - розрядним адресним входом другого вузла пам'яті, перший, другий і т - розрядний третій, виходи котрого з'єднані ВІДПОВІДНО З інформаційним входом регістра порядку, інформаційним входом тригера перестановок і з керуючими входами з керуючими входами встановлення в нуль кожної із m (п-1)- розрядних груп регістра результату, виходи усіх непарних (п-1)- розрядних груп виходів котрого з'єднані зі входами другої групи із №*) | у Р т | . входових елементів "АБО" таким чином, що виходи усіх к-х розрядів цих груп приєднані до входів к-ого елемента "АБО", і аналогічно, виходи усіх парних (п-1)- розрядних груп виходів регістра результату з'єднані зі входами третьої групи із v 1 " " V Й " ! U'->*H U' - входових елементів "АБО" таким чином, що виходи усіх к-х розрядів цих груп приєднані до входів к-ого елемента "АБО", виходи другої групи елементів "АБО" та виходи третьої групи елементів "АБО" з'єднані ВІДПОВІДНО з другим та третім адресними входами третього вузла пам'яті, перший адресний вхід якого приєднаний до виходу тригера перестановок, а перший вихід третього вузла пам'яті з'єднаний з другою групою входів суматора порядку, перша група входів котрого з'єднана з виходом регістра порядку, вихід суматора порядку з'єднаний з виходом порядку, вихід тригера знака з'єднаний з виходом знака, а другий вихід третього вузла пам'яті приєднаний до виходу мантиси, причому виходи регістрів мантиси та порядку блока керування з'єднані з адресними входами першого вузла пам'яті, а тактовий вхід пристрою з'єднаний з тактовим входом тригера керування, вихід котрого з'єднаний з інформаційним входом тригера переносу 00 о ю 50428 блока підсумовування, котрий містить комутатор, керуючий вхід якого з'єднаний з виходом тригера переносу, з входом переносу та з двома старшими розрядами першої групи входів суматора мантиси, вихід комутатора зв'язаний з молодшими розрядами першої групи входів суматора мантиси, перший та другий інформаційні входи комутатора з'єднані ВІДПОВІДНО з прямим та інверсним виходами (n-1)»m- розрядного регістра мантиси, усі непа рні (п-1)- розрядні групи інформаційних входів котрого з'єднані з першим (п-1)- розрядним виходом першого вузла пам'яті блока керування, другий (п1)- розрядний вихід котрого зв'язаний з усіма парними (п-1)- розрядними групами інформаційних входів регістра мантиси блока підсумовування, керуючі входи встановлення в нуль кожної із m груп якого приєднані до третього т - розрядного виходу першого вузла пам'яті блока керування Винахід відноситься до обчислювальної техніки і може бути використаний при побудові обчислювальних систем у якості високопродуктивного блока, що забезпечує підвищену точність додавання ПОСЛІДОВНОСТІ чисел із плаваючою точкою Відомий пристрій для одночасного виконання операцій підсумовування над множиною чисел [див авторське свідоцтво СРСР № 558276, кл G06F7/50), що складається з однотипних блоків, причому кожний 1-й блок містить регістр часткового результату, вузол формування часткового результату, тригер зберігання молодшого розряду кінцевого результату, елемент І, регістр порядку, вузол формування порядку, елемент АБО та два логічних вузли Недолік цього пристрою - ПОСЛІДОВНІСТЬ чисел перед початком підсумовування треба заздалегідь сортувати, аналізуючи порядок доданків, результат підсумовування можна приймати тільки ра порядку (к + І)-го блока підсумовування, вихід m-го блоку підсумовування є виходом пристрою (к = 1 - ( т -1)), пристрій містить блок керування, який містить регістр керування, перший, другий, третій регістри порядку, перший, другий елементи І, тригер керування, регістр мантиси, схему порівняння, перший, другий суматори, перший, другий вузли пам'яті, зсувач, групу елементів І, перший, другий, третій та четвертий комутатори, причому виходи першого регістру порядку, за виключенням виходу знакового розряду, а також виходи розрядів другого регістра порядку, з другого по через L « J тактів, де І - КІЛЬКІСТЬ чисел, г - порядок, п - розрядність мантиси Найбільш близький за технічною суттю до пристрою, що пропонується, є вибраний як прототип пристрій для додавання ПОСЛІДОВНОСТІ чисел із плаваючою комою [див авторське свідоцтво СРСР № 1182512 А, кл G06F7/50, 1985], що скорочує апаратурні витрати завдяки введенню блока керування зі зв'язками Пристрій містить m блоків підсумовування, кожний з яких містить регістри порядку та мантиси, тригер переносу, суматори порядку та мантиси, елемент АБО, регістр молодшого розряду і три групи елементів І, причому у кожному блоці підсумовування виходи регістра порядку з'єднані зі входами першої групи суматора порядку та з ВІДПОВІДНИМИ входами елемента АБО, виходи регістра молодшого розряду з'єднані з першими входами елементів І першої групи, виходи молодших та старших розрядів регістра мантис з'єднані ВІДПОВІДНО з першими входами елементів І другої та третьої груп, виходи елементів І другої групи з'єднані з ВІДПОВІДНИМИ входами першої групи суматора мантис, вихід суми суматора мантис з'єднаний з інформаційним входом регістра молодшого розряду, тактовий вхід котрого з'єднаний з тактовими входами регістрів мантиси та порядку, тактовим входом тригера переносу і тактовим входом пристрою, вихід регістра порядку k - го блока підсумовування з'єднаний з інформаційним входом регіст ( 1 о Ы Л , д а / М - И > й , де Рнакс . максимальний порядок числа, п- розрядність мантиси, з'єднані ВІДПОВІДНО з першою та другою групами входів схеми порівняння, виходи регістра керування, виходи знакових розрядів першого та другого регістрів порядку, виходи схеми порівняння з'єднані ВІДПОВІДНО з адресними входами першого вузла пам'яті, виходи 5т 1) (""-О - входових елементів "АБО", третій вузол 28 пам'яті, суматор 29 порядків, вихід ЗО знака, вихід 31 порядку, п - розрядний вихід 32 мантиси, причому тактовий вхід 1 пристрою з'єднаний з тактовими входами регістра 17, тригера 22 знаку, регістра 23 порядку, тригера 24 перестановок та регістра 25 результату, а вхід 16 обнуления зв'язаний з керуючим входом встановлення в нуль регістра 17, вихід якого зв'язаний із другою групою входів суматора 15 мантиси блока 3 підсумовування, вихід суматора 15 мантиси приєднаний до входу регістра 17, вихід старшого розряду котрого з'єднаний з інформаційним входом тригера 22 знака, з входом переносу суматора 50428 19 результату та з керуючим входом комутатора 18 результату, перший та другий інформаційні входи котрого з'єднані ВІДПОВІДНО З прямим та інверсним виходами (п - 1) молодших розрядів регістра 17, а вихід комутатора 18 результату приєднаний до першої групи входів суматора 19 результаті, на другу групу входів котрого подається "Логічний нуль", вихід суматора 19 результату приєднаний до входів регістру 25 результату, а також до першої групи 20 (п - 1) - входових елементів "АБО", виходи котрих з'єднані з m - розрядним адресним входом другого вузла 21 пам'яті, перший, другий і т-розрядний третій виходи котрого з'єднані ВІДПОВІДНО з інформаційним входом регістра 23 порядку, інформаційним входом тригера 24 перестановок і з керуючими входами встановлення в нуль кожної із m (п - 1) - розрядних груп регістру 25 результату, виходи усіх непарних (п - 1) розрядних груп виходів котрого з'єднані зі входами другої групи 26 із ^п~ ' І и Р т ] . входових елементів "АБО" таким чином, що виходи усіх к-х розрядів цих груп приєднані до входів к-ого елемента "АБО", і аналогічно, виходи усіх парних (п - 1) розрядних груп виходів регістра 25 результату з'єднані зі входами третьої групи 27 із уп-1) {т - | \),5т \) _ входових елементів "АБО" таким чином, що виходи усіх к-х розрядів цих груп приєднані до входів к-ого елемента "АБО", виходи другої групи 26 елементів "АБО" та виходи третьої групи 27 елементів "АБО" з'єднані ВІДПОВІДНО З другим та третім адресними входами третього вузла 28 пам'яті, перший адресний вхід якого приєднаний до виходу тригера 24 перестановок, а перший вихід третього вузла 28 пам'яті з'єднаний з другою групою входів суматора 29 порядку, перша група входів котрого з'єднана з виходом регістра 23 порядку, вихід суматора 29 порядку з'єднаний з виходом 31 порядку, вихід тригера 22 знаку з'єднаний з виходом ЗО знака, а другий вихід третього вузла 28 пам'яті приєднаний до виходу 32 мантиси Примітка Гхі I I - найменше ціле число, що більше або дорівнює X, ІХІ І- -І - найбільше ціле число, що менше або дорівнює X X mod Y - залишок від ділення X на Y Перший, другий та третій вузли 11, 21, 28 пам'яті можуть бути реалізовані на базі мікросхем постійних запам'ятовуючих пристроїв, прошитих у ВІДПОВІДНОСТІ з таблицями 1, 2 та З Суматори 15, 19, 29 виконують підсумовування двох операндів із розповсюдженням переносів Усі тригери та регістри пристрою здійснюють запис інформації по передньому фронту тактового імпульсу Розглянемо, як працює пристрій для додавання ПОСЛІДОВНОСТІ чисел із плаваючою точкою Пристрій для додавання ПОСЛІДОВНОСТІ чисел із плаваючою точкою має два режими роботи "Початок додавання" та "Додавання" Різниця між цими двома режимами полягає в наступному Режим "Початок додавання" встановлюється 10 на протязі двох тактів роботи пристрою Після закінчення обчислення суми поточної ПОСЛІДОВНОСТІ робиться пропуск одного такту роботи, на наступному (першому) такті на входи пристрою подається перший доданок, потім на наступному (другому) такті подається другий доданок і на вхід 16 обнуління подається ВІДПОВІДНИЙ сигнал, щоби на початку обчислення суми нової ПОСЛІДОВНОСТІ чисел встановити в нуль регістр 17, в якому накопичується результат підсумовування Цей сигнал обнуління встановлюється тільки на один (другий) такт роботи пристрою В режимі роботи "Додавання" подаються тільки чергові доданки на вхід пристрою для додавання ПОСЛІДОВНОСТІ чисел із плаваючою точкою Отже, пристрій у цих двох режимах працює за одним алгоритмом Подача доданків здійснюється по одному за такт роботи пристрою Нехай на і-му такті роботи на вхід пристрою подано і-й доданок В блоці 2 керування відбувається перетворення цього числа з двійкової системи обчислення у систему обчислення з основою є = 2п 1 А саме, на вхід 5 мантиси подається нормалізована мантиса М х доданка, що представлений в прямому коді, на вхід 6 порядку - порядок Рх доданка, на вхід 7 знака - знак доданку 3 приходом переднього фронту тактового імпульсу ці дані записуються ВІДПОВІДНО у регістри 8, 9 мантиси та порядку і тригер 10 керування За допомогою першого вузла 11 пам'яті визначається Pxmod(n - 1), і ВІДПОВІДНО на Pxmod(n - 1) розрядів зсовується мантиса Мх, формуючи дві цифри числа Мх(є) у системі обчислення з основою є, а також обчислюється иРх/(п-1) J, щоби визначити, на які позиції числа Мх(є) поставити отримані дві цифри (ІНШІ цифри числа дорівнюватимуть нулю) Отже, на перший вихід першого 11 вузла пам'яті подається цифра числа Мх(є), що повинна потрапити на якусь непарну позицію, а на другий вихід першого 11 вузла пам'яті подається цифра числа Мх(є), що повинна потрапити на якусь парну позицію числа Мх(є) Третій вихід першого 11 вузла пам'яті визначає, на які саме позиції будуть записані нулі, а отже у ті позиції, що залишилися, будуть записані ці дві цифри На (і + 1)-му такті роботи у блоці 3 підсумовування відбувається перевід мантиси Мх(є) у доповняльний код та підсумовування и з накопиченою сумою, що по ланцюгу зворотного зв'язку поступає з регістра 17 блока 4 формування результату (на початку обчислення нової ПОСЛІДОВНОСТІ ЦЯ накопичена сума дорівнює нулю, тому що на другому такті роботи регістр 17 був встановлений в нуль) Спочатку, з приходом тактового імпульсу по його передньому фронту відбувається запис числа Мх(є) у регістр 13 мантиси Перевід мантиси Мх(є) у доповняльний код здійснюється у два етапи Спочатку комутатор 14 формує обернений код числа (інвертує число, якщо знак доданка дорівнює 1), потім при виконанні підсумовування на вхід переносу в молодший розряд суматора 15 мантиси подається знак доданка На (і + 2)-му такті роботи у блоці 4 формуван 50428 11 ня результату відбувається перевід накопиченої суми у прямий код, перевід її у двійкову систему числення та починається формування нормалізованого п - розрядного результату Перевід результату Мх(є) у прямий код здійснюється у два етапи Спочатку комутатор 18 результату інвертує число, якщо знак результату дорівнює 1, потім при виконанні підсумовування на вхід переносу в молодший розряд суматора 19 результату подається знак доданка, а на другу групу входів суматор 19 подаються сигнали "Логічний нуль" Формування нормалізованого п- розрядного результату теж проходить у декілька етапів Спочатку за допомогою першої групи 20 елементів "АБО" виявляються всі нульові (п - 1) - розрядні цифри результату Потім у другому вузлі 21 пам'яті визначається, скільки старших цифр результату ДОРІВНЮЄ НуЛЮ, І формуЄТЬСЯ W n "V L *Х '\П~Ч Ц) частина порядку числа Крім того, у другому вузлі 21 пам'яті формуються сигнал перестановки та сигнали встановлення в нуль регістра 25 результату На (і + 3)-му такті роботи у блоці 4 формування результату продовжується перевід результату у двійкову систему числення та формування нормалізованого п - розрядного результату По передньому фронту тактового сигналу у регістр 25 результату записуються тільки дві старші (п - 1) - розрядні групи ненульових розрядів, позаяк ІНШІ находилися під впливом сигналів встановлення в нуль За допомогою другої та третьої груп 26 і 27 елементів "АБО" їх відокремлено, тим самим відокремлено дві старші цифри мантиси, представленої у системі числення з основою є Перша відокремлена цифра може бути як на парній позиції, так і на непарній позиції Отже, коли на другий адресний вхід третього 28 вузла пам'яті поступає непарна цифра, вона може бути молодшою Для того, щоб знати це, на перший адресний вхід вузла пам'яті 28 подається сигнал перестановки із тригеру 24 перестановки, він дорівнює одиниці, якщо потрібно поміняти місцями старшу і молодшу цифри Таким чином формується 2(п - 1) - розрядне двійкове число За допомогою третього вузла 28 пам'яті на основі аналізу того, скільки нульових (вже двійкових) старших розрядів міститься у цьому числі, визначається Pxmod(n - 1), це число на Pxmod(n - 1) розрядів зсовуються уліво і формується п- розрядний результат, відкидаючи, якщо це потрібно зайві розряди) Частина порядку Pxmod(n - 1) результату з першого виходу третього вузла 28 пам'яті поступає в суматор 29 порядку, де підсумовується з частиною порядку 12 Нехай п = 4, Рнін - 1, Рнакс =14, обчислити S = а + b + c + d, де а = +0 1011, Ра = 0001, Ь = - 0 1010, Р ь = 1110, с = -0 1100, Р с =0011, d = +0 1010, P d = 1110 Точна сума повинна дорівнювати S = 0 100101, Р = 0011, а якщо привести до прийнятої розрядної сітки, то S = -0 1001, Р = 0011, якщо вирахувати так, як це робиться зазвичай у процесорах і без прийняття спеціальних програмних заходів підвищення точності, отримаємо S = 0 Обчислення, виконані пристроєм для додавання ПОСЛІДОВНОСТІ чисел із плаваючою точкою показано у таблиці 4 Отже, на (І + 3 = 7)-ому такті отримано правильний результат S= -0 1001, Р= 0011 Таким чином, для підсумовування ПОСЛІДОВНОСТІ з І чисел із плаваючою крапкою потрібно (І + 3) тактів роботи пристрою Перед початком обчислення нової ПОСЛІДОВНОСТІ чисел має бути хоча б один холостий такт При цьому, у ВІДМІННІСТЬ ВІД прототипу, запропонований пристрій для додавання ПОСЛІДОВНОСТІ чисел із плаваючою точкою більш легкий у керуванні, тому що виконує обчислення за передбачувану КІЛЬКІСТЬ тактів, що залежить тільки від числа доданків, потребує від зовнішньої керуючої системи завдання меншої КІЛЬКОСТІ керуючих сигналів Отже, у порівнянні з прототипом, запропонований пристрій при тієї ж самій точності має більшу швидкодію і простіший в керуванні, крім того має менше число блоків, розроблений з урахуванням діючих Стандарту на двійкову арифметику з плаваючою точкою (Р754) та Стандарту на арифметику з плаваючою точкою (ПТ) із різними основами системи числення й словами довільної довжини (Р854) 1 аблиця 1- Відповідність ВХОДІ» та вичщнв яершон. вузла 1 і нам'яті Входи вузла 1 ї Розряди мантиси А1А2А3А4 AiA 2 A.As Розради Непарна група порюту рсярядш (цифра) ООАі 0001 ___________ ооіе™ 0011 oW" Парна фупа ^ S — нуль груп ргорявв (цифр) 000011 _____ | Сипали встановленая в розршв (цифра) сіоошГ"' 000011 ___ ___ 000110 000110 001100 ____ -____. АіАгАзА» 0101 АЛО OALAJ А|АІАІА4 оно ти А,00 А|А_А_ ОЙАі А2А3А4 ЗОЙО ОАІАЗ AjA,0 А1А_АЇА1 •А' L . ЇОЙІ АЛ0 І 001100 001100 011000 011000 ААА, А1А2А3А4 1910 1011 1100 Л,00 А,АА ОП000 А,А_А.А, П01 ООАі АзАА 1110 0ЛіА г поооо поооо А1А2А3А4 {(п-ї) L Рх /(п-1) J) отже, на (і + 3)-му такті формується знак суми (вихід ЗО), порядок (вихід 31) та нормалізована мантиса (вихід 32) Слід відзначити, що при необхідності можна забезпечити отримання точного (тобто не обмеженого рамками розрядної сітки) m(n - 1) - розрядного результату або результату заданої точності, якщо знімати результат з виходів регістру 17 Наводимо приклад роботи пристрою для додавання ПОСЛІДОВНОСТІ чисел із плаваючою точкою Виходи вряа 11 пам'яті иам'т ГЇАЇАА 43А4О DA, A. 50428 13 14 Таблиця 2- Відігашшеть входів та ВИХОДІВ jspj ют вузла 2! шш'яп В*4ыи вузла 23 Цифри манїнси роэташовуктлля на належному шсш регістра ІЗ мантиси Виходи ov3oa 21 пам'яті пам'яті Порядок Виходи груш (n-llP./frl)} елементів " А Б О ' СШЇМЯ Сигнали встановлення в перестановки нуль груя розрядів (дифр) ООСЮ0О 0 0 000000 0O0G01 0 0 000001 M0Q1X 0 0 000011 0001ХХ 11 ї 000110 001ХХХ па 1001 иоо 0 001100 1 011000 0 110008 01ХХХХ ІХХХХХ П 101 100 000 000 001 011 11 101 011 Ш ШОПОП 11 Ш Ш Ш Ш01І01І П р и м і т к а - X - ябо 0, або І комбінації адресних ВХОДІВ, ЩО ІІЄ випивають ка роботу, не показано Таблиця 3- ВІДПОВІДНІСТЬ ВХОДІВ та ВИХОДІВ третього в у т 28 пан ятч Входи вузла 28 пан яп Виходи вузпа 1% ііам'ян Сиг над Непарна груза Парна група перестановки розрядів (цифра) розрядів СйЯфря.) 0 _ ІАіАз 0015 OlAj АЛА, A^AsAs ООШ AJA3A4A5 0 О0ї А,Л,А* 0001 АІАДЛ 1 A,AJAI ASAJAJ 1 AtA-Aj 001 X 000 000 № такту ООН 1 ЗАЛ OlAs П р л ч і т к а -Х-абоО,або 1, Порядок Мантиса AIA^AJA^ шо 000! 00 00 Вихід елемента 19 000000000000 100 101 такту 6 хід елемента 20 000S11 Знкіделемеята21 ^ AeAiAaAj 0 000011 оаоо нажі адраених лхвдів, що не впливають на роботу. не показано Вихід еіемента 25 Табдння Н -Обчис № такту л я 5 = Я + 6 + с +d Примітки Виходи елемеяпв 8 1 2 3 1011 Ї010 1100 9 0001 1110 ООП 4 5 1010 X ШО X 10 0 1 1 0 X На кожному таки наступає черговий операнд Почалося обрахування суми нової послідовності том) на другому такп відбулося встановлення в нуль регістра 17, в якому накопичується результат представлений у доповняльному КОДІ У суматорі 19 результату здійснений перевід результату у прямий код За доломогою першої групи елементів 'АБО" визначається, скільки груп роїрядш МІСТЯТЬ тільюінуш У другому вузлі 21 пам'яті визначаться перестановки, сигнали встановлення в нуль усіх У регістрі 25 результату залишияоаь тільки дш ненупьові цифри, ЯКІ за лопомогок) другої та третьої груп "АБО" будуть відокремиш. (500000000000100101 № такту Вмд елемента 28 "оТооТоТ Вчхш елемента 28 У вузлі 28 ці дві ннфри не бучи переставлені місцями (позанк сигнал перестановки дорівнює 0), в ш і ш у п J C I пулі к а початку нової мантиси, щоби сформувати нормалізоване число, ЧИСЛО ВГДКИНуТМЧ иуліВ 0011 ІООі Вихід блока 4 формування результату 31 ОП О ( г г т 6 ('

ДивитисяДодаткова інформація

Назва патенту англійськоюUnit for adding floating-point numbers

Назва патенту російськоюУстройство для сложения последовательности чисел с плавающей запятой

МПК / Мітки

МПК: G06F 7/507

Мітки: додавання, пристрій, плаваючою, точкою, чисел, послідовності

Код посилання

<a href="https://ua.patents.su/8-50428-pristrijj-dlya-dodavannya-poslidovnosti-chisel-iz-plavayuchoyu-tochkoyu.html" target="_blank" rel="follow" title="База патентів України">Пристрій для додавання послідовності чисел із плаваючою точкою</a>

Попередній патент: Стоматологічний бор

Наступний патент: Ультразвуковий витратомір

Випадковий патент: Пристрій для відключення каналізаційного трубопроводу квартирного підключення, з'єднаного з вертикальним каналізаційним трубопроводом