Пристрій для обчислювання степеневої функції

Номер патенту: 8486

Опубліковано: 30.09.1996

Автори: Горбачов Валерій Олександрович, Гусятін Володимир Михайлович, Тимченко Георгій Васильович, Лібероль Борис Давидович, Руденко Олег Григорович

Формула / Реферат

Устройство для вычисления степенной функции, содержащее блок сдвига аргумента, блок сдвига функции, управляющие входы которых соединены с соответствующими выходами блока управления сдвигом аргумента и блока управления сдвигом функции, блок памяти, первый адресный вход которого соединен с выходом блока сдвига аргумента, отличающееся тем, что, с целью расширения класса решаемых задач путем обеспечения вычисления функции для целочисленных как положительных, так и отрицательных степеней, уменьшения объема памяти при одновременном повышении быстродействия, в него введен блок форми ропания знака функции, причем вход модуля аргумента устройства подключен к информационному входу блока сдвига аргумента и входу блока управления сдвигом аргумента, вход модуля показателя степени устройства подключен к второму адресному входу блока памяти и первым входам блока управления сдвигом функции и блока формирования знака функции, второй вход и выход которого соединен с входом знака аргумента и выходом знака результата устройства, второй вход блока управления сдвигом функции соединен с выходом блока управления сдвигом аргумента, вход знака показателя степени подключен к третьим входам блока управления сдвигом функции и блока памяти, выход которого соединен с информационным входом блока сдвига функции, выход которого является выходом модуля результата.

Текст

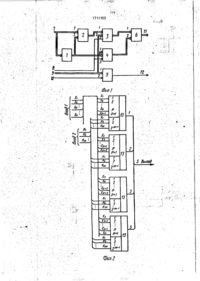

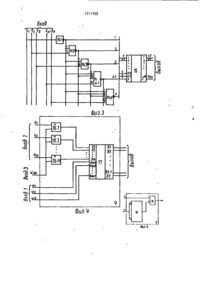

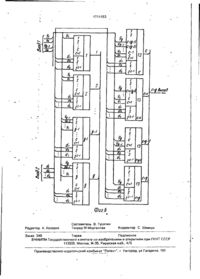

Изобретение относится к вычислительной технике и может быть использовано в специализированных ЭВМ, а также при разработке вычислительных устройств, изготавливаемых в составе больших интегральных схем. Цель изобретения - расширение класса решаемых задач за счет вычисления функции для целочисленных как положительных, так и отрицательных степеней, уменьшения объема памяти при одновременном повышении быстродействия. Поставленная цель достигается тем, что в устройство, содержащее блок памяти, блок управления сдвигом аргумента, блок сдвига аргумента, блок управлений сдвигом функции и блок сдвига функции, введен блок формирования знака функции с соответствующими связями. Устройство позволяет вычислять степенную функцию з неограниченной области изменения аргумента при одновременном повышении быстродействия, а также без изменения структуры увеличивать число целочисленных (отрицательных и положительных) значений показателя степени. 6 ил., 2 табл. Изобретение относится к вычислительной технике и может быть использовано в специализированных ЭВМ а также при разработке вычислительных устройств, изготавливаемых в составе больших интегральных схем Цель изобретения - расширение класса решаемых задач за счет вычисления функции для целочисленных как положительных, так и отрицательных степеней уменьшения объема памяти при одновременном повышении быстродействия. На фиг.1 представлена функциональная схема устройства вычисления степенной Функции; на фиг.2 - схема блока сдвига аргумента; на фиг.З - схема блока управления сдвигом аргумента; на фиг.4 - схема блока управления сдвигом функции, на фиг 5 схема блока формирования знака функции, на фиг.б - схема блока сдвига функции Устройство содержит блок 1 управления сдвигом аргумента, блок 2 сдвига аргумента, блок 3 памяти (постоянное запоминающее устройство), блок 4 управления сдвигом функции, блок 5 формирования знака функции, блок 6 сдвига функции, вход 7 модуля аргумента, вход 8 знака показателя степени, вход 9 модуля показателя степени, вход 10 знака аргумента, выход 11 модуля результата и выход 12 знака результата, мультиплексоры 13, элементы 14.1-14 Р И-НЕ, шифратор 15, элементы ИСКЛЮЧАЮЩЕЄ ИЛИ 16.1-?6т, блок 17 памяти, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 18 и элемент И 19. (21)4563108/24 (22) 15.03-89 (46)07.02.92. Бюл. №5 (71) Харьковский институт радиоэлектроники им. акад. М.К.Янгеля (72) В.М.Гусятин, В.А.Горбачев, О.Г Руд* sко. Б.Д.Либероль и Г.В.Тимченко (53)681.325(088.8) (56) Авторское свидетельство СССР Мг1298740,кл. G 06 Я 7/544, 1985. Авторское свидетельство СССР Nc 746544, кл. G 06 F 7/552, 1978. f 1711153 Устройство работает следующим обра-' зо м. n-рззрядный код аргумента х поступает на вход 7 модуля аргумента и далее на первый вход блока 2 сдвига аргумента (фиг.2). Этот блок состоит из S мультиплексоров 13.1-13.S, информационные входы которых образуют первый вход блока сдвига аргумента, их адресные гходы - второй вход сдвига аргумента а выходы всех мультиплексоров - S-разрядный выход блока сдвига аргумента Каждый из мультиплексоров содержит (Р-И) информационных входов, на которые поступают разряды аргумента X. Выбор номеров разрядов аргумента, подключаемых к каждому мультиплексору, осуществляется по следующему прэаилу. на каждый мультиплексор поступает по одному на каждый его вход (Р+1) разрядов аргумента так, что на первый вход поступает разряд аргугланта, номер которого равен номеру рассматриваемого мультиплексора, а с увеличением на единицу номера входа мультиплексора увеличивается на единицу и номер разряда аргумента, подключаемого к рассматриваемому мультиплексору. из (д+с) мультиплексоров, где с= р информационные входы которых образуют первый вход блока сдвига функции, их адресные входы - второй вход блока сдвига 5 функции, а выходы всех мультиплексоров (д+с)-рэзрядный выход блока сдвига функции. Каждый из мультиплексоров содержит (с+1) информационных входов, на которые поступают разряды выхода блока 10 памяти. Выбор номера мультиплексора и номера его выхода для каждого разряда блока памяти осуществляется в соответствии со следующим правилом;, каждый разряд выхода блока памяти поступает 15 одновременно на один из входов (с+1) мультиплексоров, начиная с мультиплексора, номер которого совпадает с номером рассматриваемого разряда, и кончая мультиплексором, номер которого больше на20 чального на с, в начальном мультиплексоре рассматриваемый разряд выхода блока памяти поступает на первый вход, а с увеличением на единицу номера мультиплексора увеличивается на единицу и номер его 25 входа, подключаемого к рассматриваемому разряду выхода блока памяти Правило иллюстрируется фиг.6 и табл 1 В табл.1 Р старших разрядов аргумента с входа на пересечении 1-й строки и j-ro столбца аргумента поступает на вход блока 1 управрасположен номер входа j-ro мультиплекления сдвигом аргумента (фиг.З), т-разряд- 30 сора, к которому подключается 1-й разряд ный выход которого, соединен с вторыми выхода ПЗУ. входами блока 4 управления сдвигом функОдин из вариантов схемотехнической ции (фиг 4) и блока 2 сдвига аргумента, В реализации блока управления сдвигом аргублоке 2 сдвига аргумента m-разрядный вымента приведен на фиг 3 Функциональное ход схемы управления сдвигом аргумента 35 назначение этой схемы состоит в том, чтобы лодхпючен поразрядно к m-рззрядному адопределить число К подряд стоящих нулей, ресному входу одновременно всех S мульначиная со старшего, в Р разрядах аргутиплексорсз мента х. Принцип работы схемы следующий: если 1-й (1 < ( < р) разряд аргумента Адрес блока 3 памяти оргэ ізуется следующим образом Первый вход (S младших 30 равен единице, а все старшие [1+(1-1)]-разразрядов адюеса) соединен с выходом блоряды аргумента равны нулю, на выходе кэ сдвига аргумента' на второй вход(гслеблока устанавливается двоичный код, дедующих разрядов адреса) с входа 9 сятичный эквивалент которого равен числу поступает г-рэзрядный подмодуля показанулей в (І-1) разрядах; если же все Р стартеля степени: третий вход (старший раз- 45 ших разрядов аргумента равны нулю, на ряд адреса) соединен с входом 8 знака выходе блока устанавливается двоичный показателя степени На первый и второй код. десятичный эквивалент которого равходы і/лока 8 формирования знака функвен р. Так. для случая р = 4, этот принцип ции (фиг.5) поступают соответственно моиллюстрируется табл.2, дуль показателя степени с входа 9 и знак 50 Р схем И- НЕ формируют унитарный раргумента с входа 10, выход блока соедиразрядный код (фиг.З) в і-м разряде которого нен с выходом 12 знака результата. Перпоявляется нуль, если t-й (1 < і 0, и а • К, Хк-2х4 = 2"7. если а < 0. Блок работает следующим обраОпределяем шаг разбиения интервала зом, m элементов ИСКЛЮЧАЮЩЕЕ ИЛИ реализуют поразрядную инверсию двоич1 « 2" 16 ного кода К, если а < 0, выходы этих элеменУмакс Д У Умакс тов образуют m младших адресов блоха памяти ПЗУ, а r-разрядный код - а -г старОпределяем число значащих разрядов ших адресов ПЗУ, по сформулированному двоичного кода аргумента в интервале табтаким образом адресу читается двоичный 10 личного представлений функции: код искомого произведения, На выходе блока формирования знака функции (фиг.5} устанавливается уровень логической единицы, если аргумент функции отрицательный и нечетный показатель степени. Элементы устройства могут быть реализованы на основе стандартных микросхем, например мультиплексоры второго и шестого блоков -на микросхемах К155 КП1, ПЗУ третьего и четвертого блоков - на микросхемах типа РТ556, шифратор и элементы И-НЕ первого блока - соответственно на микросхемах К155ИВ1 и К155ЛА2, элементы ИСКЛЮЧАЮЩЕЕ ИЛИ четвертого и пятого блоков - на микросхеме К155ЛП5, элемент И пятого блока - на микросхеме К155ЛИ1. Устройство позволяет вычислять степенную функцию y=x^ , где х - положительные и отрицательные действительные числа; а - положительные и отрицательные целые числа. Устройство осуществляет вычисление, используя следующее свойство степенной функции: изменение аргумента в d раз приводит к изменению функции в d* раз. Следовательно, если представить функцию в табличном виде на некотором минимальном интервале, то за счет только операции сдвига аргумента и табличного значения функции возможно вычисление искомого значения функции в неограниченной области изменения аргумента. При этом относительная погрешность вычисления степенной функции на всей области ее определения не будет превышать относительной погрешности ее табличного представления. Табличное представление степенной функции на интервале рассмотрим на примере функции у=х *1. Задаем у м а кс к 256, а относительная погрешность вычисления пусть будет равна 6у = 2' В этом случае значение абсолютной ПОГреШНОСТИ ДЛЯ ВСЄХ у Хк. или х < х н . т.е 30 35 40 45 50 55 Вводим следующее обозначение: х = Хн.если хе {хн, хк} . а соответствующие значения у = у п . Для всех х(/ {х и , хк} справедливо х = 2 к х п , а для соответствующих значений функции - у = 2 - у п , где к и Ы-целые числа, такие, что 0 < к < р (р= n-s), а 0 ^ к а 0. если х > хк и к < 0, если х 0} или вправо ( к < 0) на к разрядов. После такого сдвига значащие разряды аргумента попадают в интервал табличного представления функции, что позволяет получить ее табличное значение уп . Для получения искомого значения функции, полученное табличное значение уп следует сдвинуть на а -к разрядов в том же направлении, что и аргумент, если а 0. По такому способу вычисление функции осуществляется с абсолютной погрешностоЮ, не превышающей Д у для всех х, для которых у с+1 (s-1) с+2 ••• с Таблица 2 Х2 0 0 0 0 1 0 0 0 1 X хз 0 0 1 Х4 0 1 X X X X X кз К2 ki 0 0 0 0 1 1 0 0 0 1 0 1 0 0 0 1711153 фиг. 2 1711153 8хоЗ P-L A-; Фи г з 16-1 СЧІ 52. 16.2 in n m n сэ >&£ г сн 13 с*$ Z г*-* 9 /J с 1 2 2 ft-* Фиг.д Редактор А, Козориз Составитель В. Гусятин Техред М Моргентал Корректор С. Шевкун Заказ 340 Тираж Подписное ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35. Раушская наб., 4/5 Производственно-издательский комбинат "Патент", г Ужгород, ул Гагарина, 101

ДивитисяДодаткова інформація

Назва патенту англійськоюDevice for calculation of power function

Автори англійськоюHusiatyn Volodymyr Mykhailovych, Horbachov Valerii Oleksandrovych, Rudenko Oleh Hryhorovych, Liberol Borys Davydovych, Tymchenko Heorhii Vasyliovych

Назва патенту російськоюУстройство для вычисления степенной функции

Автори російськоюГусятин Владимир Михайлович, Горбачов Валерий Александрович, Руденко Олег Григорьевич, Либероль Борис Давидович, Тимченко Георгий Васильевич

МПК / Мітки

МПК: G06F 7/552

Мітки: пристрій, обчислювання, функції, степеневої

Код посилання

<a href="https://ua.patents.su/8-8486-pristrijj-dlya-obchislyuvannya-stepenevo-funkci.html" target="_blank" rel="follow" title="База патентів України">Пристрій для обчислювання степеневої функції</a>

Попередній патент: Пристрій для очищення стічних вод

Наступний патент: Муфельна електропіч

Випадковий патент: Киселиця з перестачем прямостоячим та солодкою голою