Цифровий т-генератор функцій

Номер патенту: 21406

Опубліковано: 02.12.1997

Автори: Федун Антон Леонідович, Корченко Олександр Григорович, Бурлака Олег Володимирович, Захаров Михайло Олександрович, Копач Лілія Василівна

Формула / Реферат

Цифровой Т-генератор функций, содержащий блок памяти, счетчик, дешифратор, накапливающий сумматор, первый коммутатор, второй коммутатор, третий коммутатор, первый регистр, второй регистр и первый умножитель, причем выход дешифратора подключен к первому адресному входу блока памяти, второй адресный вход которого соединен с выходом счетчика, входы старших и младших разрядов первого информационного входа генератора соединены соответственно с входами первой группы разрядов дешифратора и входами разрядов первого сомножителя первого умножителя, входы разрядов второго сомножителя которого соединены с выходом накапливающего сумматора, с первым входом первого коммутатора и с входом первого регистра, выход которого подключен к выходной информационной шине и первому входу второго коммутатора, выход которого соединен с первым входом накапливающего сумматора, второй вход которого подключен к выходу первого коммутатора, второй вход которого соединен с выходом первого умножителя, отличающийся тем, что он содержит второй и третий информационные входы, второй умножитель, третий регистр и четвертый коммутатор, причем вторая и третья группы входных разрядов дешифратора соединены соответственно с группой старших разрядов второго и третьего информационных входов, младшие разряды которых подключены соответственно к первому и второму входам четвертого коммутатора, третий вход которого соединен с выходом блока памяти, логическая единица подключена к первому входу третьего коммутатора, второй вход которого соединен с выходом третьего регистра, вход которого подключен ко входу второго регистра, второму входу второго коммутатора и выходу второго умножителя, первый, второй и третий входы которого соответственно соединены с выходом четвертого регистра, выходом третьего коммутатора и выходом второго регистра, с первого по двенадцатый разряды управляющей шины соответственно соединены с управляющими входами первого и второго умножителей, накапливающего сумматора, первого, второго и третьего регистров, первого, второго и третьего коммутаторов, двумя входами четвертого коммутатора и счетчика, а с первого по пятый разряды установочной шины соответственно подключены к установочным входам первого, второго и третьего регистров, накапливающего сумматора и счетчика.

Текст

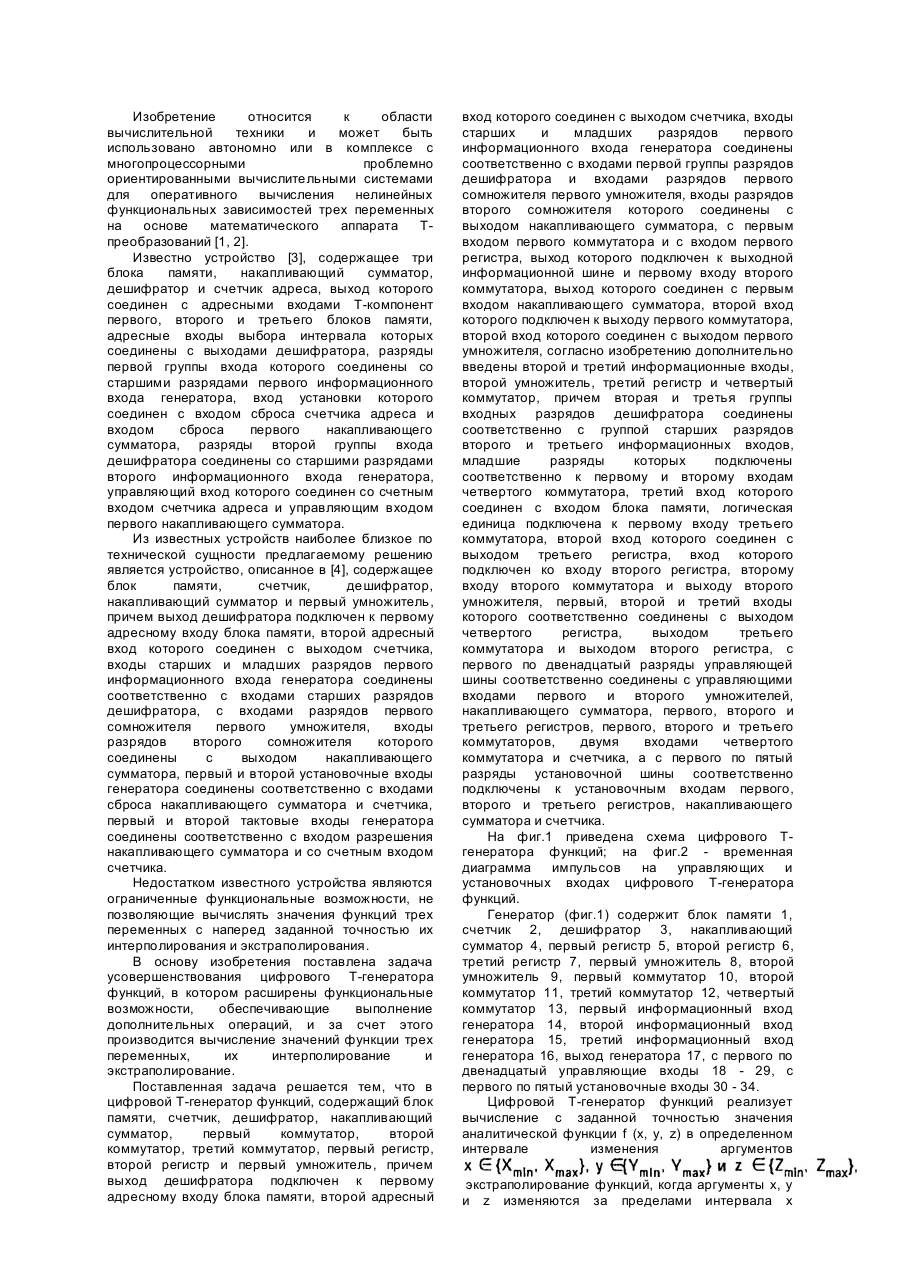

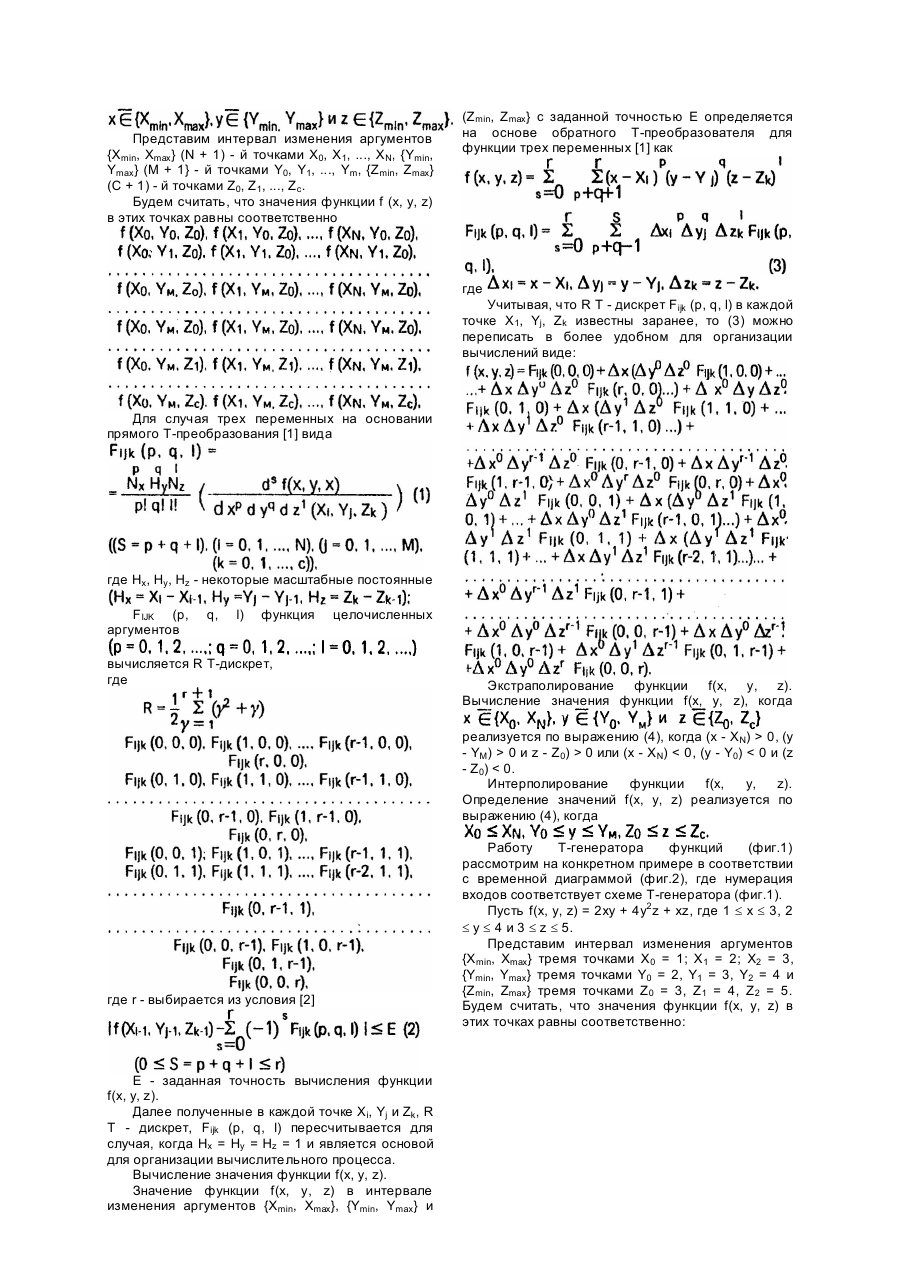

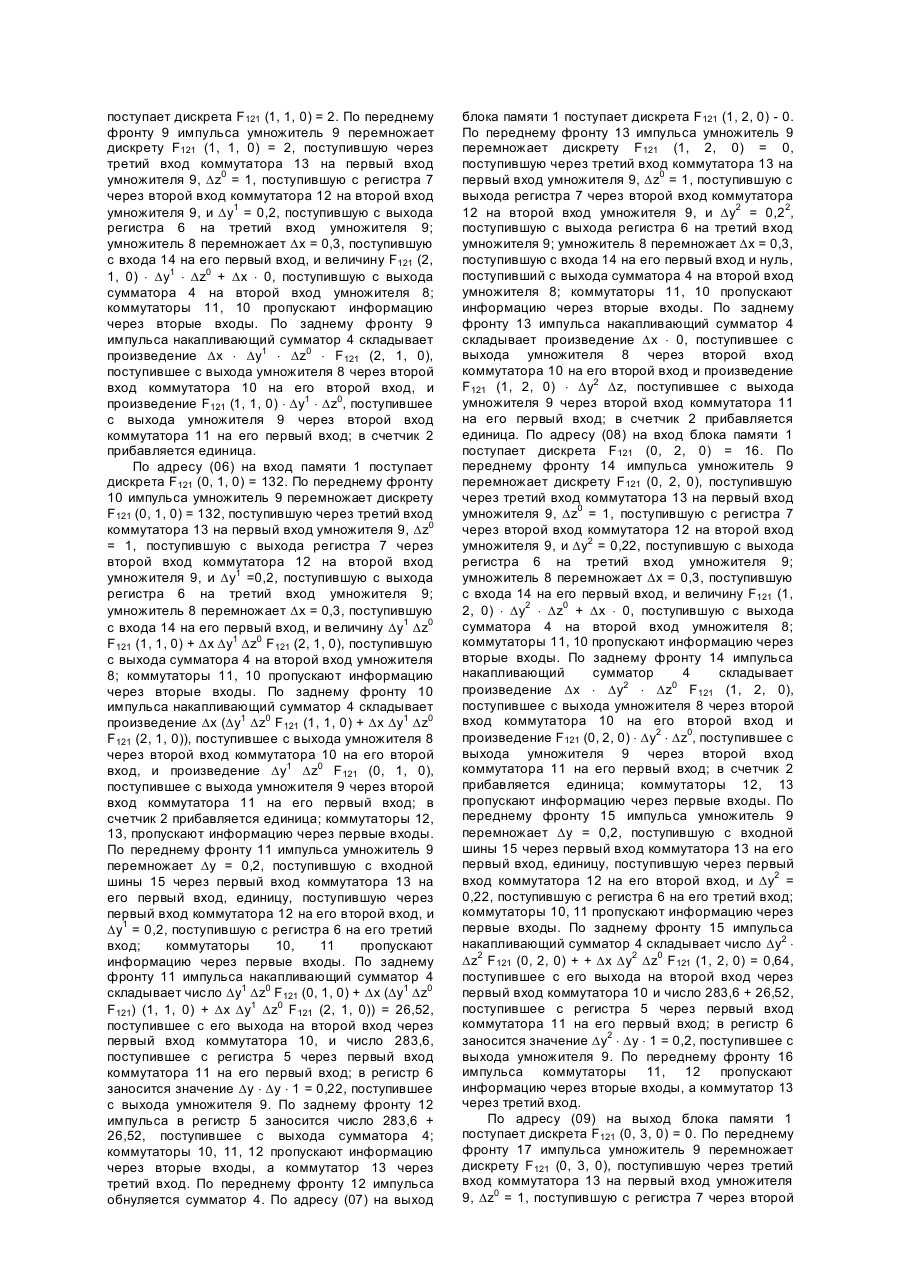

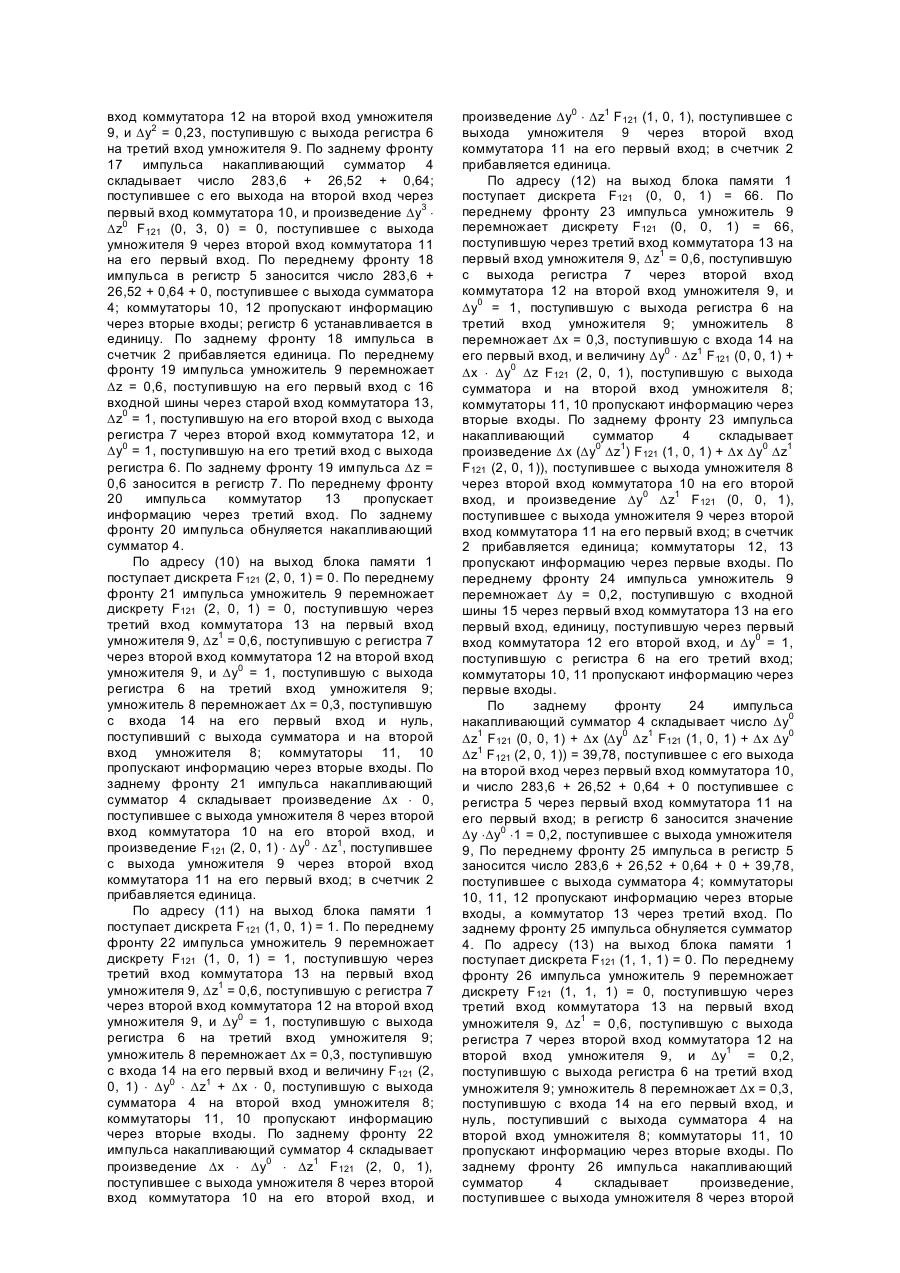

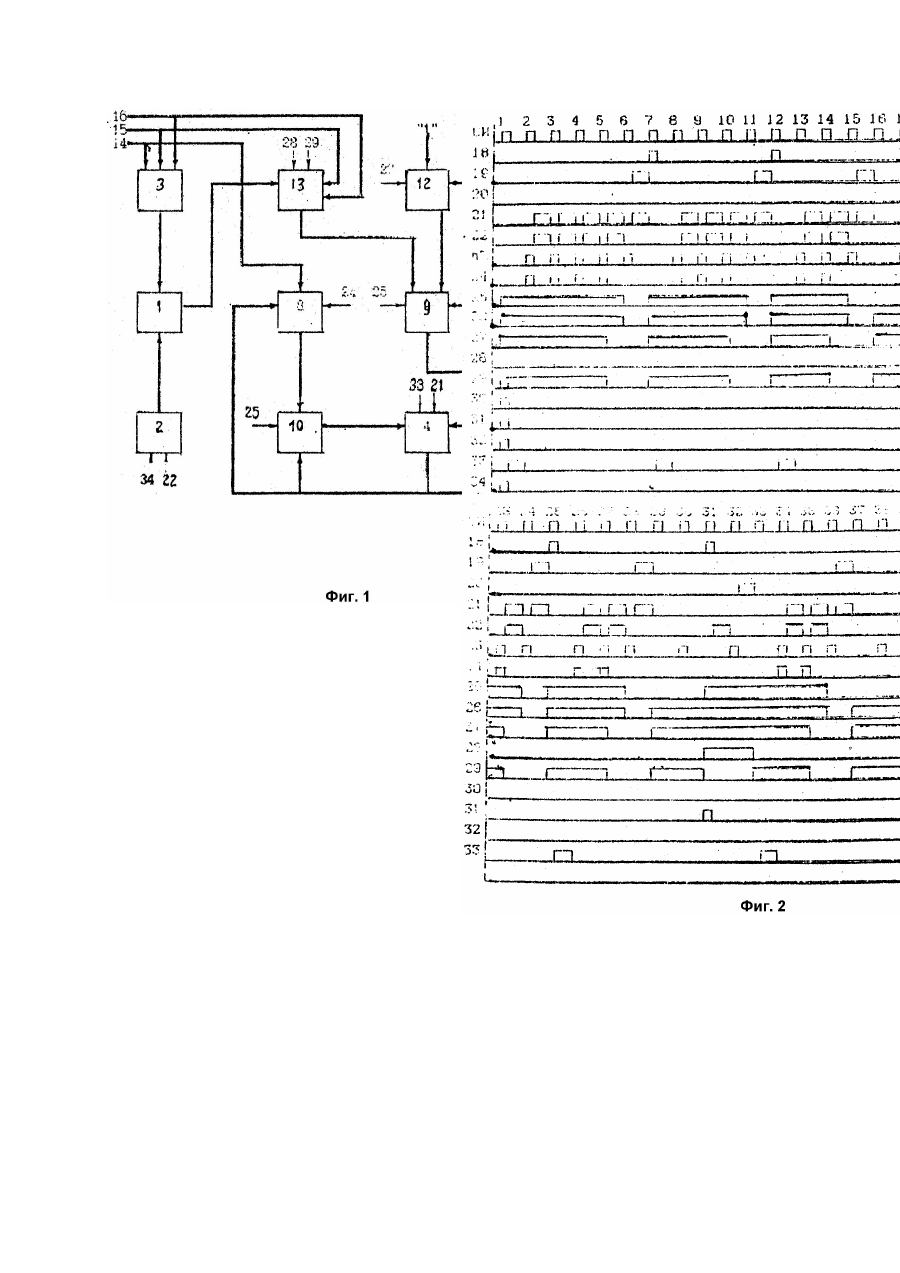

Изобретение относится к области вычислительной техники и может быть использовано автономно или в комплексе с многопроцессорными проблемно ориентированными вычислительными системами для оперативного вычисления нелинейных функциональных зависимостей трех переменных на основе математического аппарата Tпреобразований [1, 2]. Известно устройство [3], содержащее три блока памяти, накапливающий сумматор, дешифратор и счетчик адреса, выход которого соединен с адресными входами T-компонент первого, второго и третьего блоков памяти, адресные входы выбора интервала которых соединены с выходами дешифратора, разряды первой группы входа которого соединены со старшими разрядами первого информационного входа генератора, вход установки которого соединен с входом сброса счетчика адреса и входом сброса первого накапливающего сумматора, разряды второй группы входа дешифратора соединены со старшими разрядами второго информационного входа генератора, управляющий вход которого соединен со счетным входом счетчика адреса и управляющим входом первого накапливающего сумматора. Из известных устройств наиболее близкое по технической сущности предлагаемому решению является устройство, описанное в [4], содержащее блок памяти, счетчик, дешифратор, накапливающий сумматор и первый умножитель, причем выход дешифратора подключен к первому адресному входу блока памяти, второй адресный вход которого соединен с выходом счетчика, входы старших и младших разрядов первого информационного входа генератора соединены соответственно с входами старших разрядов дешифратора, с входами разрядов первого сомножителя первого умножителя, входы разрядов второго сомножителя которого соединены с выходом накапливающего сумматора, первый и второй установочные входы генератора соединены соответственно с входами сброса накапливающего сумматора и счетчика, первый и второй тактовые входы генератора соединены соответственно с входом разрешения накапливающего сумматора и со счетным входом счетчика. Недостатком известного устройства являются ограниченные функциональные возможности, не позволяющие вычислять значения функций трех переменных с наперед заданной точностью их интерполирования и экстраполирования. В основу изобретения поставлена задача усовершенствования цифрового T-генератора функций, в котором расширены функциональные возможности, обеспечивающие выполнение дополнительных операций, и за счет этого производится вычисление значений функции трех переменных, их интерполирование и экстраполирование. Поставленная задача решается тем, что в цифровой T-генератор функций, содержащий блок памяти, счетчик, дешифратор, накапливающий сумматор, первый коммутатор, второй коммутатор, третий коммутатор, первый регистр, второй регистр и первый умножитель, причем выход дешифратора подключен к первому адресному входу блока памяти, второй адресный вход которого соединен с выходом счетчика, входы старших и младших разрядов первого информационного входа генератора соединены соответственно с входами первой группы разрядов дешифратора и входами разрядов первого сомножителя первого умножителя, входы разрядов второго сомножителя которого соединены с выходом накапливающего сумматора, с первым входом первого коммутатора и с входом первого регистра, выход которого подключен к выходной информационной шине и первому входу второго коммутатора, выход которого соединен с первым входом накапливающего сумматора, второй вход которого подключен к выходу первого коммутатора, второй вход которого соединен с выходом первого умножителя, согласно изобретению дополнительно введены второй и третий информационные входы, второй умножитель, третий регистр и четвертый коммутатор, причем вторая и третья группы входных разрядов дешифратора соединены соответственно с группой старших разрядов второго и третьего информационных входов, младшие разряды которых подключены соответственно к первому и второму входам четвертого коммутатора, третий вход которого соединен с входом блока памяти, логическая единица подключена к первому входу третьего коммутатора, второй вход которого соединен с выходом третьего регистра, вход которого подключен ко входу второго регистра, второму входу второго коммутатора и выходу второго умножителя, первый, второй и третий входы которого соответственно соединены с выходом четвертого регистра, выходом третьего коммутатора и выходом второго регистра, с первого по двенадцатый разряды управляющей шины соответственно соединены с управляющими входами первого и второго умножителей, накапливающего сумматора, первого, второго и третьего регистров, первого, второго и третьего коммутаторов, двумя входами четвертого коммутатора и счетчика, а с первого по пятый разряды установочной шины соответственно подключены к установочным входам первого, второго и третьего регистров, накапливающего сумматора и счетчика. На фиг.1 приведена схема цифрового Tгенератора функций; на фиг.2 - временная диаграмма импульсов на управляющих и установочных входах цифрового T-генератора функций. Генератор (фиг.1) содержит блок памяти 1, счетчик 2, дешифратор 3, накапливающий сумматор 4, первый регистр 5, второй регистр 6, третий регистр 7, первый умножитель 8, второй умножитель 9, первый коммутатор 10, второй коммутатор 11, третий коммутатор 12, четвертый коммутатор 13, первый информационный вход генератора 14, второй информационный вход генератора 15, третий информационный вход генератора 16, выход генератора 17, с первого по двенадцатый управляющие входы 18 - 29, с первого по пятый установочные входы 30 - 34. Цифровой T-генератор функций реализует вычисление с заданной точностью значения аналитической функции f (x, y, z) в определенном интервале изменения аргументов экстраполирование функций, когда аргументы x, y и z изменяются за пределами интервала x Представим интервал изменения аргументов {Xmin, Xmах} (N + 1) - й точками X0, X1, ..., XN, {Ymin, Ymax} (M + 1} - й точками Y0, Y1, ..., Ym, {Zmin, Zmax} (C + 1) - й точками Z0, Z1, ..., Zc. Будем считать, что значения функции f (x, y, z) в этих точках равны соответственно (Zmin, Zmax} с заданной точностью E определяется на основе обратного T-преобразователя для функции трех переменных [1] как где Учитывая, что R T - дискрет Fijk (p, q, l) в каждой точке X1, Yj, Zk известны заранее, то (3) можно переписать в более удобном для организации вычислений виде: Для случая трех переменных на основании прямого T-преобразования [1] вида где Hx, Hy, Hz - некоторые масштабные постоянные FIJK (p, аргументов q, l) функция целочисленных вычисляется R T-дискрет, где Экстраполирование функции f(x, y, z). Вычисление значения функции f(x, y, z), когда реализуется по выражению (4), когда (x - XN) > 0, (y - YM) > 0 и z - Z0) > 0 или (x - XN) < 0, (y - Y0) < 0 и (z - Z0) MN, n > Mm, n > Mc) младших Dx1 = 0,3, Dy2 = 0,2 и Dz1 = 0,6 соответственно на первый вход умножителя 8, первый и второй входы коммутатора 13. В зависимости от входного кода на соответствующем выходе дешифратора 3 появляется единичный сигнал, который выбирает область блока памяти 1, в которой хранятся 20 T дискрет F121 (p, q, l), соответствующих точкам X1, Y2, Z1. По переднему фронту первого синхроимпульса производится установка счетчика 2, регистра 5 в ноль, регистров 6 и 7 в единицу; коммутаторы 10, 11, 12 пропускают информацию через вторые входы, а 13 через третий вход. По заднему фронту первого синхроимпульса обнуляется накапливающий сумматор 4. По адресу (00) на выход блока памяти 1 поступает дискрета F121 (3, 0, 0) = 0. По переднему фронту второго импульса умножитель 9 перемножает дискрету F 121 (3, 0, 0) = 0, поступившую через третий вход коммутатора 13 на первый вход умножителя 9, Dz0 = 1, поступившую с регистра 7 через второй вход коммутатора 12 на второй вход умножителя 9, и Dy0 = 1, поступившую с выхода регистра 6 на третий вход умножителя 9; умножитель 8 перемножает Dx = 0,3, поступившую с входа 14 на его первый вход, и нуль, поступивший с выхода сумматора 4 на второй вход умножителя 8; коммутаторы 11, 10 пропускают информацию через вторые входы. По заднему фронту второго импульса сумматор 4 складывает произведение Dx × 0, поступившее с выхода умножителя 8 через второй вход коммутатора 10 на его второй вход, и произведение F121 (3, 0, 0) Dy0Dz0, поступившее с выхода умножителя 9 через второй вход коммутатора 11 на его первый вход; в счетчик 2 прибавляется единица. По адресу (01) на выход блока памяти 1 поступает дискрета F121 (2, 0, 0) = 0. По переднему фронту третьего импульса умножитель 9 перемножает дискрету F121 (2, 0, 0) = 0, поступившую через третий вход коммутатора 13 на первый вход умножителя 9, Dz0 = 1, поступившую с регистра 7 через второй вход коммутатора 12 на второй вход умножителя 9, и Dy0 = 1, поступившую с выхода регистра 6 на третий вход умножителя 9; умножитель 8 перемножает Dx = 0,3, поступившую с входа 14 на его первый вход, и величину F121 (3, 0, 0) Dz0 Dy0 + Dx × 0, поступившую с выхода сумматора 4 на второй вход умножителя 8; коммутаторы 11, 10 пропускают информацию через вторые входы. По заднему фронту третьего импульса накапливающий сумматор 4 складывает произведение Dx × Dy0 Dz0 F121 (3, 0, 0), поступившее с выхода умножителя 8 через второй вход коммутатора 10 на его второй вход и произведение F121 (2, 0, 0) × Dy0 Dz0, поступившее с выхода умножителя 9 через второй вход коммутатора 11 на его первый вход; в счетчик 2 прибавляется единица. По адресу (02) на выход блока памяти 1 поступает дискрета F121 (1, 0, 0) = 12. По переднему фронту четвертого импульса умножитель 9 перемножает дискрету F121 (1, 0, 0) = 12, поступившую через третий вход коммутатора 13 на первый вход умножителя 9, Dz0 = 1, поступившую с выхода регистра 7 через второй вход коммутатора 12 на второй вход умножителя 9, и Dy0 = 1, поступившую с выхода регистра 6 на третий вход умножителя 9; умножитель 8 перемножает Dx = 0,3, поступившую с входа 14 на его первый вход, и величину Dy0 Dz0 F121 (2, 0, 0) + Dx Dy0 Dz0 F121 (2, 0, 0), поступившую с выхода сумматора 4 на второй вход умножителя 8; коммутаторы 11, 10 пропускают информацию через вторые входы. По заднему фронту четвертого импульса накапливающий сумматор 4 складывает произведение Dx (Dy0 z0 F121 (2, 0, 0) + Dx Dy0 Dz0 F121 (3, 0, 0)), поступившее с выхода умножителя 8 через второй вход коммутатора 10 на его второй вход, и произведение Dy0 Dz0 F121 (1, 0, 0), поступившее с выхода умножителя 9 через второй вход коммутатора 11 на его первый вход; в счетчик 2 прибавляется единица. По адресу (03) на выход блока памяти 1 поступает дискрета F121 (0, 0, 0) = 280. По переднему фронту пятого импульса умножитель 9 перемножает дискрету F121 (0, 0, 0) = 280, поступившую через третий вход коммутатора 13 на первый вход умножителя 9, Dz0 = 1, поступившую с выхода регистра 7 через второй вход коммутатора 12 на второй вход умножителя 9, и Dy0 = 1, поступившую с выхода регистра 6 на третий вход умножителя 9; умножитель 8 перемножает Dx = 0,3, поступившую с входа 14 на его первый вход, и величину Dy0 Dz0 Df 121 (1, 0, 0) + Dx (Dy0 Dz0 D F121 (2, 0, 0) + Dx Dy0 Dz0 F121 (3, 0, 0)), поступившую с выхода сумматора 4 на второй вход умножителя 8; коммутаторы 11, 10 пропускают информацию через вторые входы. По заднему фронту пятого импульса накапливающий сумматор 4 складывает произведение Dx (Dy0 Dz0 F121 (1, 0, 0) + + Dx (Dy0 Dz0 F121 (2, 0, 0) + Dx Dy0 Dz0 F121 (3, 0, 0))), поступившее с выхода умножителя 8 через второй вход коммутатора 10 на его второй вход, и произведение 1.1 F121 (0, 0, 0), поступившее с выхода умножителя 9 через второй вход коммутатора 11 на его первый вход; в счетчик 2 прибавляется единица; коммутаторы 12, 23 пропускают информацию через первые входы. По переднему фронту шестого импульса умножитель 9 перемножает y0 = 0,2, поступившую с входной шины 15 через первый вход коммутатора 3 на его первый вход, единицу, поступившую через первый вход коммутатора 12 на его второй вход, и Dy0 = 1, поступившую с регистра 6 на его третий вход; коммутаторы 10, 11 пропускают информацию через первые входы. По заднему фронту шестого импульса накапливающий 4 складывает число F121 (0, 0, 0) + Dx (Dy0 Dz0 F121 (1, 0, 0) + Dx (Dy0 Dz0 F121 (2, 0, 0) + Dx Dy0 Dz0 F121 (3, 0, 0))) = 283,6, поступившее с его выхода на второй вход через первый вход коммутатора 10, и число нуль; поступившее с регистра 5 через первый вход коммутатора 11 на его первый вход; в регистр 6 заносится значение Dy × 1x x1 = 0,2, поступившее с выхода умножителя 9. По переднему фронту седьмого импульса в регистр 5 заносится число 283,6, поступившее с выхода сумматора 4; коммутаторы 10, 11, 12 пропускают информацию через вторые входы, а коммутатор 13 через третий вход. По заднему фронту седьмого импульса обнуляется сумматор 4. По адресу (04) на выход блока памяти 1 поступает дискрета F121 (2, 1, 0) = 0. По переднему фронту восьмого импульса умножитель 9 перемножает дискрету F121 (2, 1, 0) = 0, поступившую через третий вход коммутатора 13 на первый вход умножителя 9, Dz0 = 1, поступившую с выхода регистра 7 через второй вход коммутатора 12 на второй вход умножителя 9, и Dy1 = 0,2, поступившую с выхода регистра 6 на третий вход умножителя 9; умножитель 8 перемножает Dx = 0,3, поступившую с входа 14 на его первый вход, и нуль, поступивший с выхода сумматора 4 на второй вход умножителя 8; коммутаторы 11, 10 пропускают информацию через вторые входы. По заднему фронту восьмого импульса накапливающий сумматор 4 складывает произведение Dx × 0, поступившее с выхода умножителя 8 через второй вход коммутатора 10 на его второй вход, и произведение F121 (2, 1, 0) Dy1 Dz0, поступившее с выхода умножителя 9 через второй вход коммутатора 11 на его первый вход; в счетчик 2 прибавляется единица. По адресу (05) на вход блока памяти 1 поступает дискрета F121 (1, 1, 0) = 2. По переднему фронту 9 импульса умножитель 9 перемножает дискрету F121 (1, 1, 0) = 2, поступившую через третий вход коммутатора 13 на первый вход умножителя 9, Dz0 = 1, поступившую с регистра 7 через второй вход коммутатора 12 на второй вход умножителя 9, и Dy1 = 0,2, поступившую с выхода регистра 6 на третий вход умножителя 9; умножитель 8 перемножает Dx = 0,3, поступившую с входа 14 на его первый вход, и величину F121 (2, 1, 0) × Dy1 × Dz0 + Dx × 0, поступившую с выхода сумматора 4 на второй вход умножителя 8; коммутаторы 11, 10 пропускают информацию через вторые входы. По заднему фронту 9 импульса накапливающий сумматор 4 складывает произведение Dx × Dy1 × Dz0 × F121 (2, 1, 0), поступившее с выхода умножителя 8 через второй вход коммутатора 10 на его второй вход, и произведение F121 (1, 1, 0) × Dy1 × Dz0, поступившее с выхода умножителя 9 через второй вход коммутатора 11 на его первый вход; в счетчик 2 прибавляется единица. По адресу (06) на вход памяти 1 поступает дискрета F121 (0, 1, 0) = 132. По переднему фронту 10 импульса умножитель 9 перемножает дискрету F121 (0, 1, 0) = 132, поступившую через третий вход коммутатора 13 на первый вход умножителя 9, Dz0 = 1, поступившую с выхода регистра 7 через второй вход коммутатора 12 на второй вход умножителя 9, и Dy1 =0,2, поступившую с выхода регистра 6 на третий вход умножителя 9; умножитель 8 перемножает Dx = 0,3, поступившую с входа 14 на его первый вход, и величину Dy1 Dz0 F121 (1, 1, 0) + Dx Dy1 Dz0 F121 (2, 1, 0), поступившую с выхода сумматора 4 на второй вход умножителя 8; коммутаторы 11, 10 пропускают информацию через вторые входы. По заднему фронту 10 импульса накапливающий сумматор 4 складывает произведение Dx (Dy1 Dz0 F121 (1, 1, 0) + Dx Dy1 Dz0 F121 (2, 1, 0)), поступившее с выхода умножителя 8 через второй вход коммутатора 10 на его второй вход, и произведение Dy1 Dz0 F121 (0, 1, 0), поступившее с выхода умножителя 9 через второй вход коммутатора 11 на его первый вход; в счетчик 2 прибавляется единица; коммутаторы 12, 13, пропускают информацию через первые входы. По переднему фронту 11 импульса умножитель 9 перемножает Dy = 0,2, поступившую с входной шины 15 через первый вход коммутатора 13 на его первый вход, единицу, поступившую через первый вход коммутатора 12 на его второй вход, и Dy1 = 0,2, поступившую с регистра 6 на его третий вход; коммутаторы 10, 11 пропускают информацию через первые входы. По заднему фронту 11 импульса накапливающий сумматор 4 складывает число Dy1 Dz0 F121 (0, 1, 0) + Dx (Dy1 Dz0 F121) (1, 1, 0) + Dx Dy1 Dz0 F121 (2, 1, 0)) = 26,52, поступившее с его выхода на второй вход через первый вход коммутатора 10, и число 283,6, поступившее с регистра 5 через первый вход коммутатора 11 на его первый вход; в регистр 6 заносится значение Dy × Dy × 1 = 0,22, поступившее с выхода умножителя 9. По заднему фронту 12 импульса в регистр 5 заносится число 283,6 + 26,52, поступившее с выхода сумматора 4; коммутаторы 10, 11, 12 пропускают информацию через вторые входы, а коммутатор 13 через третий вход. По переднему фронту 12 импульса обнуляется сумматор 4. По адресу (07) на выход блока памяти 1 поступает дискрета F121 (1, 2, 0) - 0. По переднему фронту 13 импульса умножитель 9 перемножает дискрету F121 (1, 2, 0) = 0, поступившую через третий вход коммутатора 13 на первый вход умножителя 9, Dz0 = 1, поступившую с выхода регистра 7 через второй вход коммутатора 12 на второй вход умножителя 9, и Dy2 = 0,22, поступившую с выхода регистра 6 на третий вход умножителя 9; умножитель 8 перемножает Dx = 0,3, поступившую с входа 14 на его первый вход и нуль, поступивший с выхода сумматора 4 на второй вход умножителя 8; коммутаторы 11, 10 пропускают информацию через вторые входы. По заднему фронту 13 импульса накапливающий сумматор 4 складывает произведение Dx × 0, поступившее с выхода умножителя 8 через второй вход коммутатора 10 на его второй вход и произведение F121 (1, 2, 0) × Dy2 Dz, поступившее с выхода умножителя 9 через второй вход коммутатора 11 на его первый вход; в счетчик 2 прибавляется единица. По адресу (08) на вход блока памяти 1 поступает дискрета F121 (0, 2, 0) = 16. По переднему фронту 14 импульса умножитель 9 перемножает дискрету F121 (0, 2, 0), поступившую через третий вход коммутатора 13 на первый вход умножителя 9, Dz0 = 1, поступившую с регистра 7 через второй вход коммутатора 12 на второй вход умножителя 9, и Dy2 = 0,22, поступившую с выхода регистра 6 на третий вход умножителя 9; умножитель 8 перемножает Dx = 0,3, поступившую с входа 14 на его первый вход, и величину F121 (1, 2, 0) × Dy2 × Dz0 + Dx × 0, поступившую с выхода сумматора 4 на второй вход умножителя 8; коммутаторы 11, 10 пропускают информацию через вторые входы. По заднему фронту 14 импульса накапливающий сумматор 4 складывает произведение Dx × Dy2 × Dz0 F121 (1, 2, 0), поступившее с выхода умножителя 8 через второй вход коммутатора 10 на его второй вход и произведение F121 (0, 2, 0) × Dy2 × Dz0, поступившее с выхода умножителя 9 через второй вход коммутатора 11 на его первый вход; в счетчик 2 прибавляется единица; коммутаторы 12, 13 пропускают информацию через первые входы. По переднему фронту 15 импульса умножитель 9 перемножает Dy = 0,2, поступившую с входной шины 15 через первый вход коммутатора 13 на его первый вход, единицу, поступившую через первый вход коммутатора 12 на его второй вход, и Dy2 = 0,22, поступившую с регистра 6 на его третий вход; коммутаторы 10, 11 пропускают информацию через первые входы. По заднему фронту 15 импульса накапливающий сумматор 4 складывает число Dy2 × Dz2 F121 (0, 2, 0) + + Dx Dy2 Dz0 F121 (1, 2, 0) = 0,64, поступившее с его выхода на второй вход через первый вход коммутатора 10 и число 283,6 + 26,52, поступившее с регистра 5 через первый вход коммутатора 11 на его первый вход; в регистр 6 заносится значение Dy2 × Dy × 1 = 0,2, поступившее с выхода умножителя 9. По переднему фронту 16 импульса коммутаторы 11, 12 пропускают информацию через вторые входы, а коммутатор 13 через третий вход. По адресу (09) на выход блока памяти 1 поступает дискрета F121 (0, 3, 0) = 0. По переднему фронту 17 импульса умножитель 9 перемножает дискрету F121 (0, 3, 0), поступившую через третий вход коммутатора 13 на первый вход умножителя 9, Dz0 = 1, поступившую с регистра 7 через второй вход коммутатора 12 на второй вход умножителя 9, и Dy2 = 0,23, поступившую с выхода регистра 6 на третий вход умножителя 9. По заднему фронту 17 импульса накапливающий сумматор 4 складывает число 283,6 + 26,52 + 0,64; поступившее с его выхода на второй вход через первый вход коммутатора 10, и произведение Dy3 × Dz0 F121 (0, 3, 0) = 0, поступившее с выхода умножителя 9 через второй вход коммутатора 11 на его первый вход. По переднему фронту 18 импульса в регистр 5 заносится число 283,6 + 26,52 + 0,64 + 0, поступившее с выхода сумматора 4; коммутаторы 10, 12 пропускают информацию через вторые входы; регистр 6 устанавливается в единицу. По заднему фронту 18 импульса в счетчик 2 прибавляется единица. По переднему фронту 19 импульса умножитель 9 перемножает Dz = 0,6, поступившую на его первый вход с 16 входной шины через старой вход коммутатора 13, Dz0 = 1, поступившую на его второй вход с выхода регистра 7 через второй вход коммутатора 12, и Dy0 = 1, поступившую на его третий вход с выхода регистра 6. По заднему фронту 19 импульса Dz = 0,6 заносится в регистр 7. По переднему фронту 20 импульса коммутатор 13 пропускает информацию через третий вход. По заднему фронту 20 импульса обнуляется накапливающий сумматор 4. По адресу (10) на выход блока памяти 1 поступает дискрета F121 (2, 0, 1) = 0. По переднему фронту 21 импульса умножитель 9 перемножает дискрету F121 (2, 0, 1) = 0, поступившую через третий вход коммутатора 13 на первый вход умножителя 9, Dz1 = 0,6, поступившую с регистра 7 через второй вход коммутатора 12 на второй вход умножителя 9, и Dу0 = 1, поступившую с выхода регистра 6 на третий вход умножителя 9; умножитель 8 перемножает Dx = 0,3, поступившую с входа 14 на его первый вход и нуль, поступивший с выхода сумматора и на второй вход умножителя 8; коммутаторы 11, 10 пропускают информацию через вторые входы. По заднему фронту 21 импульса накапливающий сумматор 4 складывает произведение Dx × 0, поступившее с выхода умножителя 8 через второй вход коммутатора 10 на его второй вход, и произведение F121 (2, 0, 1) × Dy0 × Dz1, поступившее с выхода умножителя 9 через второй вход коммутатора 11 на его первый вход; в счетчик 2 прибавляется единица. По адресу (11) на выход блока памяти 1 поступает дискрета F121 (1, 0, 1) = 1. По переднему фронту 22 импульса умножитель 9 перемножает дискрету F121 (1, 0, 1) = 1, поступившую через третий вход коммутатора 13 на первый вход умножителя 9, Dz1 = 0,6, поступившую с регистра 7 через второй вход коммутатора 12 на второй вход умножителя 9, и Dy0 = 1, поступившую с выхода регистра 6 на третий вход умножителя 9; умножитель 8 перемножает Dx = 0,3, поступившую с входа 14 на его первый вход и величину F 121 (2, 0, 1) × Dy0 × Dz1 + Dx × 0, поступившую с выхода сумматора 4 на второй вход умножителя 8; коммутаторы 11, 10 пропускают информацию через вторые входы. По заднему фронту 22 импульса накапливающий сумматор 4 складывает произведение Dx × Dy0 × Dz1 F121 (2, 0, 1), поступившее с выхода умножителя 8 через второй вход коммутатора 10 на его второй вход, и произведение Dy0 × Dz1 F121 (1, 0, 1), поступившее с выхода умножителя 9 через второй вход коммутатора 11 на его первый вход; в счетчик 2 прибавляется единица. По адресу (12) на выход блока памяти 1 поступает дискрета F121 (0, 0, 1) = 66. По переднему фронту 23 импульса умножитель 9 перемножает дискрету F121 (0, 0, 1) = 66, поступившую через третий вход коммутатора 13 на первый вход умножителя 9, Dz1 = 0,6, поступившую с выхода регистра 7 через второй вход коммутатора 12 на второй вход умножителя 9, и Dy0 = 1, поступившую с выхода регистра 6 на третий вход умножителя 9; умножитель 8 перемножает Dx = 0,3, поступившую с входа 14 на его первый вход, и величину Dy0 × Dz1 F121 (0, 0, 1) + Dx × Dy0 Dz F121 (2, 0, 1), поступившую с выхода сумматора и на второй вход умножителя 8; коммутаторы 11, 10 пропускают информацию через вторые входы. По заднему фронту 23 импульса накапливающий сумматор 4 складывает произведение Dx (Dy0 Dz1) F121 (1, 0, 1) + Dx Dy0 Dz1 F121 (2, 0, 1)), поступившее с выхода умножителя 8 через второй вход коммутатора 10 на его второй вход, и произведение Dy0 Dz1 F121 (0, 0, 1), поступившее с выхода умножителя 9 через второй вход коммутатора 11 на его первый вход; в счетчик 2 прибавляется единица; коммутаторы 12, 13 пропускают информацию через первые входы. По переднему фронту 24 импульса умножитель 9 перемножает Dy = 0,2, поступившую с входной шины 15 через первый вход коммутатора 13 на его первый вход, единицу, поступившую через первый вход коммутатора 12 его второй вход, и Dy0 = 1, поступившую с регистра 6 на его третий вход; коммутаторы 10, 11 пропускают информацию через первые входы. По заднему фронту 24 импульса накапливающий сумматор 4 складывает число Dy0 Dz1 F121 (0, 0, 1) + Dx (Dy0 Dz1 F121 (1, 0, 1) + Dx Dy0 Dz1 F121 (2, 0, 1)) = 39,78, поступившее с его выхода на второй вход через первый вход коммутатора 10, и число 283,6 + 26,52 + 0,64 + 0 поступившее с регистра 5 через первый вход коммутатора 11 на его первый вход; в регистр 6 заносится значение Dy ×Dy0 ×1 = 0,2, поступившее с выхода умножителя 9, По переднему фронту 25 импульса в регистр 5 заносится число 283,6 + 26,52 + 0,64 + 0 + 39,78, поступившее с выхода сумматора 4; коммутаторы 10, 11, 12 пропускают информацию через вторые входы, а коммутатор 13 через третий вход. По заднему фронту 25 импульса обнуляется сумматор 4. По адресу (13) на выход блока памяти 1 поступает дискрета F121 (1, 1, 1) = 0. По переднему фронту 26 импульса умножитель 9 перемножает дискрету F121 (1, 1, 1) = 0, поступившую через третий вход коммутатора 13 на первый вход умножителя 9, Dz1 = 0,6, поступившую с выхода регистра 7 через второй вход коммутатора 12 на второй вход умножителя 9, и Dy1 = 0,2, поступившую с выхода регистра 6 на третий вход умножителя 9; умножитель 8 перемножает Dx = 0,3, поступившую с входа 14 на его первый вход, и нуль, поступивший с выхода сумматора 4 на второй вход умножителя 8; коммутаторы 11, 10 пропускают информацию через вторые входы. По заднему фронту 26 импульса накапливающий сумматор 4 складывает произведение, поступившее с выхода умножителя 8 через второй вход коммутатора 11 на его первый вход; в счетчик 2 прибавляется единица. По адресу (14) на вход блока памяти 1 поступает дискрета F121 (0, 1, 1) = 32. По переднему фронту 27 импульса умножитель 9 перемножает дискрету F121 (0, 1, 1), поступившую через третий вход коммутатора 13 на первый вход умножителя 9, Dz1 = 0,6, поступившую с регистра 7 через второй вход коммутатора 12 на второй вход умножителя 9, и Dy1 = 0,2, поступившую с выхода регистра 6 на третий вход умножителя 9; умножитель 8 перемножает Dx = 0,3, поступившую с входа 14 на его первый вход, и величину F121 (1, 1, 1) × Dy1 × Dz1 + Dx × 0, поступившую с выхода сумматора 4 на второй вход умножителя 8; коммутаторы 11, 10 пропускают информацию через вторые входы. По заднему фронту 27 импульса накапливающий сумматор 4 складывает произведение Dx × Dy1 × Dz1 F121 (1, 1, 1), поступившее с выхода умножителя 8 через второй вход коммутатора 10 на его второй вход, и произведение F121 (0, 1, 1) × Dy1 × Dz1, поступившее с выхода умножителя 9 через второй вход коммутатора 11 на его первый вход; в счетчик 2 прибавляется единица; коммутаторы 12, 13 пропускают информацию через первые входы. По переднему фронту 28 импульса умножитель 9 перемножает Dy = 0,2, поступившую с входной шины 15 через первый вход коммутатора 13 на его первый вход, единицу, поступившую через первый вход коммутатора 12 на его второй вход, и Dy1 = 0,2, поступившую с регистра 6 на его третий вход; коммутаторы 10, 11 пропускают информацию через первые входы. По заднему фронту 28 импульса накапливающий сумматор 4 складывает число Dy1 Dz1 F121 (0, 1, 1) + Dx Dy1 Dz1 F121 (1, 1, 1) = 3,84, поступившее с его выхода на второй вход через первый вход коммутатора 10, и число 283,6 + 26,52 + 0,64 + 0 + 39,78, поступившее с регистра 5 через первый вход коммутатора 11 на его первый вход; в регистр 6 заносится значение Dy × Dy × 1 = 0,22, поступившее с выхода умножителя 9. По переднему фронту 29 импульса коммутаторы 11, 12 пропускают информацию через вторые входы, а коммутатор 13 через третий вход. По адресу (15) на выход блока памяти 1 поступает дискрета F121 (0, 2, 1) = 4. По переднему фронту 30 импульса умножитель 9 перемножает дискрету F121 (0, 2, 1), поступившую через третий вход коммутатора 13 на первый вход умножителя 9, Dx1 = 0,6, поступившую с регистра 7 через второй вход коммутатора 12 на второй вход умножителя 9, и Dy2 = 0,22, поступившую с выхода регистра 6 на третий вход умножителя 9. По заднему фронту 30 импульса накапливающий сумматор 4 складывает число 283,6 + 26,52 + 0,64 + 0 + 39,78 + 3,84, поступившее с его выхода на второй вход через первый вход коммутатора 10, и произведение Dy2 Dz1 F121 (0, 2, 1) = 0,096, поступившее с выхода умножителя 9 через второй вход коммутатора 11 на его первый вход. По переднему фронту 31 импульса в регистр 5 заносится число 283,6 + 26,52 + 0,64 + 0 + 39,78 + 3,84 + 0,096, поступившее с выхода сумматора 4; коммутаторы 10, 12 пропускают информацию через вторые входы; регистр 6 устанавливается в единицу. По заднему фронту 31 импульса в счетчик 2 прибавляется единица. По переднему фронту 32 импульса умножитель 9 перемножает Dz = 0,6, поступившую на его первый вход с 16 входной шины через второй вход коммутатор 13, Dz = 0,6, поступившую на его второй вход с выхода регистра 7 через второй вход коммутатора 12, и Dy0 = 1 поступившую на его третий вход с выхода регистра 6. По заднему фронту 32 импульса Dz2 = 0,62 заносится в регистр 7. По переднему фронту 33 импульса коммутатор 13 пропускает информацию через третий вход. По заднему фронту 33 импульса обнуляется накапливающий сумматор 4. По адресу (16) на выход блока памяти 1 поступает дискрета F121 (1, 0, 2) = 0. По переднему фронту 34 импульса умножитель 9 перемножает дискрету F121 (1, 0, 2) = 0, поступившую через третий вход коммутатора 13 на первый вход умножителя 9, Dz2 = 0,62, поступившую с выхода регистра 7 через второй вход коммутатора 12 на второй вход умножителя 9, и Dy0 = 1, поступившую с выхода регистра 6 на третий вход умножителя 9; умножитель 8 перемножает Dx = 0,3, поступившую с входа 14 на его первый вход, и нуль, поступивший с выхода сумматора 4 на второй вход умножителя 8; коммутаторы 11, 10 пропускают информацию через вторые входы. По заднему фронту 34 импульса накапливающий сумматор 4 складывает произведение Dx × 0, поступившее с выхода умножителя 8 через второй вход коммутатора 11 на его первый вход; в счетчик 2 прибавляется единица. По адресу (17) на вход блока памяти 1 поступает дискрета F121 (0, 0, 2) = 0. По переднему фронту 35 импульса умножитель 9 перемножает дискрету F121 (0, 0, 2), поступившую через третий вход коммутатора 13 на первый вход умножителя 9, Dz2 = 0,62, поступившую с регистра 7 через второй вход коммутатора 12 на второй вход умножителя 9, и Dy0 = 1, поступившую с выхода регистра 6 на третий вход умножителя 9; умножитель 8 перемножает Dx = 0,3, поступившую с входа 14 на его первый вход, и величину F121 (1, 0, 2) × Dy0 × Dz2 + Dx × 0, поступившую с выхода сумматора 4 на второй вход умножителя 8; коммутаторы 11, 10 пропускают информацию через вторые входы. По заднему фронту 35 импульса накапливающий сумматор 4 складывает произведение Dx × Dy0 × Dz2 F121 (1, 0, 2), поступившее с выхода умножителя 8 через второй вход коммутатора 10 на его второй вход, и произведение F121 (0, 0, 2) × Dy0 × Dz2, поступившее с выхода умножителя 9 через второй вход коммутатора 11 на его первый вход; в счетчик 2 прибавляется единица; коммутаторы 12, 13 пропускают информацию через первые входы. По переднему фронту 36 импульса умножитель 9 перемножает Dy = 0,2, поступившую с входной шины 15 через первый вход коммутатора 13 на его первый вход, единицу, поступившую через первый вход коммутатора 12 на его второй вход, и Dy0 =1, поступившую с регистра 6 на его третий вход;коммутаторы 10, 11 пропускают информацию через первые входы. По заднему фронту 36 импульса накапливающий сумматор 4 складывает число Dy0 Dz2 F121 (0, 0, 2) + Dx Dy0 Dz2 F121 (1, 0, 2) = 0, поступившее с его выхода на второй вход через первый вход коммутатора 10, и число 283,6 + 26,52 + 0,64 + 0 + 29,78 + 3,84 + 0,096, поступившее с регистра 5 через первый вход коммутатора 11 на его первый вход; в регистр 6 заносится значение Dy × Dy0 × 1 =0,2, поступившее с выхода умножителя 9. По переднему фронту 37 импульса коммутаторы 11, 12 пропускают информацию через вторые входы, а коммутатор 13 через третий вход. По адресу (18) на выход блока памяти 1 поступает дискрета F121 (0, 1, 2) = 0. По переднему фронту 38 импульса умножитель 9 перемножает дискрету F121 (0, 1, 2), поступившую через третий вход коммутатора 13 на первый вход умножителя 9, Dz2 = 0,62, поступившую с регистра 7 через второй вход коммутатора 12 на второй вход умножителя 9, и Dy1 = 0,2, поступившую с выхода регистра 6 на третий вход умножителя 9. По заднему фронту 38 импульса накапливающий сумматор 4 складывает число 283,6 + 26,52 + 0,64 + 0 + 39,78 + 3,84 + 0,096 + 0, поступившее с его выхода на второй вход через первый вход коммутатора 10, и произведение Dy1 × Dz2 × DF121 (0, 1, 2) = 0, поступившее с выхода умножителя 9 через второй вход коммутатора 11 на его первый вход. По переднему фронту 39 импульса в регистр 5 заносится число 283,6 + 26,52 + 0,64 + 0 + 39,78 + 3,84 + 0,096 + 0 + 0, поступившее с выхода сумматора 4; коммутаторы 10, 12 пропускают информацию через вторые входы; регистр 6 устанавливается в единицу. По заднему фронту 39 импульса в счетчик 2 прибавляется единица. По переднему фронту 40 импульса умножитель 9 перемножает Dz = = 0,6, поступившую на его первый вход с 16 входной шины через второй вход коммутатора 13, Dz2 = 0,62, поступившую на его второй вход с выходам регистра 7 через второй вход коммутатора 12, и Dy0 = 1, поступившую на его третий вход с выхода регистра 6. По заднему фронту 40 импульса Dz3 = 0,63 заносится в регистр 7. По переднему фронту 41 импульса коммутатор 13 пропускает информацию через третий вход, а коммутатор 10 через первый вход. По адресу (19) на выход блока памяти 1 поступает дискрета F121 (0, 0, 3) = 0. По переднему фронту 42 импульса умножитель 9 перемножает дискрету F121 (0, 0, 3) = 0, поступившую через третий вход коммутатора 13 на первый вход умножителя 9, Dz3 = 0,63, поступившую с выхода регистра 7 через второй вход коммутатора 12 на второй вход умножителя 9, и Dy0 = 1, поступаемую с выхода регистра 6 на третий вход умножителя 9. По заднему фронту 42 импульса сумматор 4 складывает число 283,6 + 26,52 + 0,64 + 0 + 39,78 + 3,84 + 0,096 + 0 + 0, поступившее с его выхода на второй вход через первый вход коммутатора 10, и произведение Dy0 × Dz3 F121 (0, 0, 3) = 0, поступившее на его первый вход с выхода умножителя 9 через второй вход коммутатора 11. По переднему фронту 43 импульса в регистр 5 с выхода накапливающего сумматора 4 заносится число 283,6 + 26,52 + 0,64 + 0 + 39,78 + 3,84 + 0,096 + 0 + 0 + 0 = 354,476. На информационный выход 17 с выхода регистра 5 поступает вычислительное значение функции f(x, y, z) = 354,476 с заданной точностью E, представленной выражением (2), T - дискреты Fijk (p, q, l) которой записаны в блоке памяти 1, а количество импульсов равно 43. При реализации операции экстраполирования вычислительный процесс аналогичен описанному выше с той лишь разницей, что на (n - mN), (n - mM) и (n - mc) младших разрядов входов 14, 15 и 16 подается значение DxN = x - XN > 0 или Dx0 = x - X0 0 или Dy0 = y - Y0 0 или Dz0 = z - Z0 < 0 соответственно. В режиме интерполирования функций цифровой T-генератор функций работает аналогично режиму вычисления значения функции, т.е. на входы 14, 15 и 16 подается n-разрядный код значения аргументов x, y и z, причем X0 £ x £ XN, Y0 £ y £ YM, Z0 £ z £ Zc. В соответствии с изложенным предлагаемое устройство можно достаточно эффективно использовать в качестве расширения функциональных возможностей в многопроцессорных вычислительных машинах, ориентированных для реализации широкого класса задач в натуральном масштабе времени, например, управление технологическими процессами или динамическим объемом в режиме его нормального функционирования. Использование новых элементов - умножителя, регистра и коммутатора, а также новых связей между ними, зафиксированных в формуле изобретения, выгодно отличает предлагаемое устройство от указанного прототипа. В отличие от прототипа, в котором производится вычисление значений функций, их интерполирование и экстраполирование от двух переменных, в предлагаемом устройстве, благодаря применению метода T-преобразований для трехмерных функций, расширены функциональные возможности за счет вычисления значений функций от трех независимых переменных, их интерполирование и экстраполирование. При изготовлении T-генератора функций можно использовать следующую элементную базу: блок памяти 1 (К556РТ5, К556РТ7, К565РУ5Д2), счетчик 2 (К155ИЕ5, К155ИЕ7), дешифратор 3 (К155ИДЗ), сумматор 4 (К155ИМ3, КР1802ВС1), регистры 5, 6 и 7 (К155ИР13), умножители 8 и 9 (К1518ВЖ1, КР1802ВР5) и коммутаторы 10, 11, 12 и 13 (К155ЛП10).

ДивитисяДодаткова інформація

Назва патенту англійськоюDigital function generator

Автори англійськоюKorchenko Oleksandr Hryhorovych, Zakharov Mykhailo Oleksandrovych, Kopach Lilia Vasylivna, Burlaka Oleh Volodymyrovych, Fedun Anton Leonidovych

Назва патенту російськоюЦифровой генератор функций

Автори російськоюКорченко Александр Григорьевич, Захаров Михаил Александрович, Копач Лилия Васильевна, Бурлака Олег Владимирович, Федун Антон Леонидович

МПК / Мітки

МПК: G06F 1/02

Мітки: т-генератор, функцій, цифровий

Код посилання

<a href="https://ua.patents.su/9-21406-cifrovijj-t-generator-funkcijj.html" target="_blank" rel="follow" title="База патентів України">Цифровий т-генератор функцій</a>

Попередній патент: Склад для парафінування прищеплень “вопарет”

Наступний патент: Спосіб керування режимом роботи грохота

Випадковий патент: Спосіб діагностики хвороби пейроні