Обчислювальний пристрій

Номер патенту: 59112

Опубліковано: 10.05.2011

Автори: Жабіна Валентина Валеріївна, Клименко Ірина Анатоліївна

Формула / Реферат

Обчислювальний пристрій, що містить n блоків обробки інформації, n регістрів команд, блок вводу даних, блок виводу даних, блок буферної пам'яті даних, блок буферної пам'яті команд, регістр даних, регістр адреси, блок пам'яті операндів, блок пам'яті управляючих слів, комутатор, блок мікропрограмного управління, причому інформаційний вхід пристрою з'єднаний з першим інформаційним входом блока вводу даних, вихід якого з'єднаний з першим інформаційним входом комутатора, вихід якого з'єднаний з інформаційним входом блока буферної пам'яті даних, перший інформаційний вихід якого з'єднаний з інформаційним входом регістра даних, другий інформаційний вихід блока буферної пам'яті даних з'єднаний з інформаційним входом регістра адреси, вихід якого з'єднаний з адресним входом блока пам'яті управляючих слів і адресним входом блока пам'яті операндів, перший вихід регістра даних з'єднаний з інформаційними входами блока пам'яті управляючих слів, блока пам'яті операндів і першим інформаційним входом блока буферної пам'яті команд, другий інформаційний вхід якого з'єднаний з інформаційним виходом блока пам'яті операндів, інформаційний вихід блока пам'яті управляючих слів з'єднаний з третім інформаційним входом блока буферної пам'яті команд, перший вихід якого з'єднаний з інформаційним входом блока виведення даних, вихід якого є виходом пристрою, другий вихід блока буферної пам'яті команд з'єднаний з інформаційними входами блоків обробки інформації, інформаційні виходи яких з'єднані відповідно з інформаційними входами з другого по (n+1)-й комутатора, перший вихід блока мікропрограмного управління з'єднаний з управляючим входом блока вводу даних, вихід ознаки даних якого з'єднаний з першим входом режиму блока мікропрограмного управління, другий вихід якого з'єднаний з управляючим входом комутатора, кожен і-й вихід (і=1, ..., n) третьої групи управляючих виходів блока мікропрограмного управління з'єднаний з управляючим входом і-го блока обробки інформації, вихід ознаки якого з'єднаний з і-м входом другої групи входів режиму блока мікропрограмного керування, вихід ознаки зайнятості блока буферної пам'яті даних з'єднаний з третім входом режиму блока мікропрограмного управління, четвертий вихід якого з'єднаний з управляючим входом блока буферної пам'яті даних, п'ятий і шостий виходи блока мікропрограмного управління з'єднані відповідно з входами запису/читання регістра адреси і регістра даних, вихід ознаки якого з'єднаний з четвертим входом режиму блока мікропрограмного управління, сьомий і восьмий виходи якого з'єднані відповідно з входами запису/читання блока пам'яті управляючих слів і блока пам'яті операндів, вихід ознаки якого з'єднаний з п'ятим входом режиму блока мікропрограмного управління, дев'ятий вихід якого з'єднаний з управляючим входом блока буферної пам'яті команд, вихід ознаки якого з'єднаний з шостим входом режиму блока мікропрограмного управління, десятий вихід якого з'єднаний з управляючим входом блока виводу, вихід ознаки якого з'єднаний з сьомим входом режиму блока мікропрограмного управління, інформаційні виходи регістрів команд з'єднані з четвертим інформаційним входом блока буферної пам'яті команд, другий інформаційний вихід якого з'єднаний з інформаційними входами кожного і-го регістра команд (i=1, ..., n), управляючі входи яких з'єднані з i-ми виходами одинадцятої групи керуючих виходів блока мікропрограмного управління, який відрізняється тим, що до складу пристрою введені n блоків таймерів виконання операції, інформаційні виходи яких з'єднані з п'ятим інформаційним входом блока буферної пам'яті команд, третій інформаційний вихід якого з'єднаний з інформаційними входами кожного і-го блока таймера виконання операції (i=1, ..., n), управляючі входи яких з'єднані з i-ми виходами восьмої групи керуючих виходів блока мікропрограмного управління, кожен і-й вихід (i=1, ..., n) дванадцятої групи управляючих виходів якого з'єднаний з управляючим входом i-го блока таймера виконання команди.

Текст

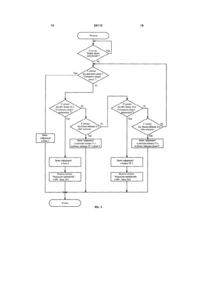

Обчислювальний пристрій, що містить n блоків обробки інформації, n регістрів команд, блок вводу даних, блок виводу даних, блок буферної пам'яті даних, блок буферної пам'яті команд, регістр даних, регістр адреси, блок пам'яті операндів, блок пам'яті управляючих слів, комутатор, блок мікропрограмного управління, причому інформаційний вхід пристрою з'єднаний з першим інформаційним входом блока вводу даних, вихід якого з'єднаний з першим інформаційним входом комутатора, вихід якого з'єднаний з інформаційним входом блока буферної пам'яті даних, перший інформаційний вихід якого з'єднаний з інформаційним входом регістра даних, другий інформаційний вихід блока буферної пам'яті даних з'єднаний з інформаційним входом регістра адреси, вихід якого з'єднаний з адресним входом блока пам'яті управляючих слів і адресним входом блока пам'яті операндів, перший вихід регістра даних з'єднаний з інформаційними входами блока пам'яті управляючих слів, блока пам'яті операндів і першим інформаційним входом блока буферної пам'яті команд, другий інформаційний вхід якого з'єднаний з інформаційним виходом блока пам'яті операндів, інформаційний вихід блока пам'яті управляючих слів з'єднаний з третім інформаційним входом блока буферної пам'яті команд, перший вихід якого з'єднаний з інформаційним входом блока виведення даних, вихід якого є виходом пристрою, другий вихід блока буферної пам'яті команд з'єднаний з інформаційними входами блоків обробки інформації, інформаційні виходи яких з'єднані відповідно з інформаційними входами з другого по (n+1)-й комутатора, перший вихід блока мікропрограмного управління з'єднаний з управляючим входом блока вводу даних, вихід ознаки даних якого з'єднаний з першим входом режиму блока мікропрограмного управління, другий вихід якого з'єднаний з управляючим входом комутато 2 (19) 1 3 Корисна модель стосується обчислювальної техніки і може бути застосований при побудові високопродуктивних обчислювальних систем. Відомий обчислювальний пристрій [1], який містить блоки вводу і виводу даних, блоки обробки інформації, блоки буферної пам'яті даних і команд, пристрої пам'яті управляючих слів і операндів, регістри адреса і даних. Недоліком даного пристрою є те, що вихід з ладу блока обробки інформації приводить до неправильного результату обчислень, тому що в пристрої не передбачені засоби для виконання повторних обчислень у випадку неправильного виконання команди. Відомий обчислювальний пристрій [2], який містить блоки обробки інформації, блок вводу даних, блок виводу даних, блок буферної пам'яті даних, блок буферної пам'яті команд, регістр даних, регістр адреса, блок пам'яті операндів, блок пам'яті управляючих слів, комутатор, блок мікропрограмного управління, регістр додаткової пам'яті операнду. У випадку відмовлення блока обробки інформації операнд невиконаної команди повторно записується в середовище формування команд і передається в справний блок обробки інформації. Недоліком даного пристрою є те, що при відмовленні блока обробки інформації в середовище формування команд із додаткової пам'яті операндів передається тільки один операнд. Передбачається, що до цього моменту часу в середовищі формування команд зберігається управляюче слово й другий операнд. Однак, це можливо тільки тоді, коли в середовище формування команд не можуть надходити управляючі слова і дані з однаковими іменами (номерами) до повного завершення даного алгоритму. Це обмежує функціональні можливості пристрою, тому що не дозволяє виконувати алгоритми в потоковому режимі (нові обчислення починаються до завершення старих), а також при багаторазовому повторенні однакових обчислювальних процесів у циклічному режимі (реалізуються однакові алгоритми з різними даними). Неможливість суміщення процесів на рівні алгоритмів (задач) приводить також до зниження продуктивності пристрою. Найбільш близьким до корисної моделі по технічній сутності є обчислювальний пристрій [3], який містить n блоків обробки інформації, блок вводу даних, блок виводу даних, блок буферної пам'яті даних, блок буферної пам'яті команд, регістр даних, регістр адреси, блок пам'яті операндів, блок пам'яті управляючих слів, комутатор, блок мікропрограмного управління, причому інформаційний вхід пристрою управління з'єднаний з першим інформаційним входом блоку вводу даних, вихід якого з'єднаний з першим інформаційним входом комутатора, вихід якого з'єднаний з інформаційним входом блоку буферної пам'яті даних, перший інформаційний вихід якого з'єднаний з інформаційним входом регістра даних, другий інформаційний вихід блоку буферної пам'яті даних з'єднаний з інформаційним входом регістра адре 59112 4 си, вихід якого з'єднаний з адресним входом блока пам'яті управляючих слів і адресним входом блока пам'яті операндів, перший вихід регістра даних з'єднаний з інформаційними входами блоку пам'яті управляючих слів, блоку пам'яті операндів і першим інформаційним входом блока буферної пам'яті команд, другий інформаційний вхід якого з'єднаний з інформаційним входом блока пам'яті операндів, інформаційний вихід блоку пам'яті управляючих слів, з'єднаний з третім інформаційним входом блоку буферної пам'яті команд, перший вихід якого з'єднаний з інформаційним входом блоку виведення даних, вихід якого є виходом пристрою, другий вихід блоку буферної пам'яті команд з'єднаний з інформаційними входами блоків обробки інформації, інформаційні виходи яких з'єднані відповідно з інформаційними входами з другого по (n+1)-й комутатора, перший вихід блока мікропрограмного управління з'єднаний з управляючим входом блоку вводу даних, вихід ознаки даних якого з'єднаний з першим входом режиму блоку мікропрограмного управління, другий вихід якого з'єднаний з управляючим входом комутатора, кожен і-й вихід (і=1, ... n) третьої групи управляючих виходів блоку мікропрограмного управління з'єднаний з управляючим входом i-го блоку обробки інформації, вихід ознаки зайнятості блоку буферної пам'яті даних з'єднаний з третім входом режиму блоку мікропрограмного управління, четвертий вихід якого з'єднаний з управляючим входом блоку буферної пам'яті даних, п'ятий і шостий виходи блоку мікропрограмного управління з'єднані відповідно з входами запису/читання регістра адреси і регістра даних, вихід ознаки якого з'єднаний з четвертим входом режиму блоку мікропрограмного управління, сьомий і восьмий виходи якого з'єднані відповідно з входами запису/читання блоку пам'яті управляючих слів і блоку пам'яті операндів, другий вихід ознаки якого з'єднаний з п'ятим входом режиму блоку мікропрограмного управління, дев'ятий вихід якого з'єднаний з управляючим входом блока буферної пам'яті команд, вихід ознаки якого з'єднаний з шостим входом режиму блоку мікропрограмного управління, десятий вихід якого з'єднаний з управляючим входом блоку виводу, вихід ознаки якого з'єднаний з сьомим входом режиму блоку мікропрограмного управління, до складу пристрою введені n регістрів команд, інформаційні виходи яких з'єднані з четвертим інформаційним входом блока буферної пам'яті команд, другий інформаційний вихід якого з'єднаний з інформаційними входами кожного і-го регістра команд (i=1, ..., n), управляючі входи яких з'єднаний з i-ми виходами одинадцятої групи управляючих виходів блока мікропрограмного управління. Достоїнствами даного пристрою є підвищення функціональних можливостей пристроїв за рахунок реалізації циклічних процесів та обчислень в режимі потоку задач. Підвищується ефективність використання ресурсів системи. Немає необхідно 5 сті зберігати фрагменти команди в середовищі формування команди. Це дозволяє суміщати обчислювальні процеси не тільки на рівні команд, а і на рівні алгоритмів, що забезпечує зменшення часу виконання перетворення інформації. Недоліком даного пристрою є непродуктивні витрати часу на реконфігурацію системи під час відмови обчислювального блоку. Час спрацьовування таймера може бути більшим ніж, ніж час необхідний для виконання команди. Це вносить додаткову часову затримку під час реконфігурації системи. В основу корисної моделі поставлено задачу підвищення функціональних можливостей і продуктивності пристрою при відмовленні блоків обробки інформації за рахунок зменшення часу реконфігурації системи. Поставлена задача вирішується тим, що в обчислювальному пристрої, який містить n блоків обробки інформації, n регістрів команд, блок вводу даних, блок виводу даних, блок буферної пам'яті даних, блок буферної пам'яті команд, регістр даних, регістр адреси, блок пам'яті операндів, блок пам'яті управляючих слів, комутатор, блок мікропрограмного управління, причому інформаційний вхід пристрою з'єднаний з першим інформаційним входом блоку вводу даних, вихід якого з'єднаний з першим інформаційним входом комутатора, вихід якого з'єднаний з інформаційним входом блоку буферної пам'яті даних, перший інформаційний вихід якого з'єднаний з інформаційним входом регістра даних, другий інформаційний вихід блоку буферної пам'яті даних з'єднаний з інформаційним входом регістра адреси, вихід якого з'єднаний з адресним входом блока пам'яті управляючих слів і адресним входом блока пам'яті операндів, перший вихід регістра даних з'єднаний з інформаційними входами блоку пам'яті управляючих слів, блоку пам'яті операндів і першим інформаційним входом блока буферної пам'яті команд, другий інформаційний вхід якого з'єднаний з інформаційним виходом блока пам'яті операндів, інформаційний вихід блоку пам'яті управляючих слів з'єднаний з третім інформаційним входом блоку буферної пам'яті команд, перший вихід якого з'єднаний з інформаційним входом блоку виведення даних, вихід якого є виходом пристрою, другий вихід блоку буферної пам'яті команд з'єднаний з інформаційними входами блоків обробки інформації, інформаційні виходи яких з'єднані відповідно з інформаційними входами з другого по (n+1)-й комутатора, перший вихід блока мікропрограмного управління з'єднаний з управляючим входом блоку вводу даних, вихід ознаки даних якого з'єднаний з першим входом режиму блоку мікропрограмного управління, другий вихід якого з'єднаний з управляючим входом комутатора, кожен і-й вихід (i=1, ... n) третьої групи управляючих виходів блоку мікропрограмного управління з'єднаний з управляючим входом і-го блоку обробки інформації, вихід ознаки якого з'єднаний з i-м входом другої групи входів режиму блока мікропрограмного управління, вихід ознаки зайнятості блока буферної пам'яті даних з'єднаний з третім входом режиму блока мікропрограмного управління, четвертий вихід якого з'єднаний з 59112 6 управляючим входом блока буферної пам'яті даних, п'ятий і шостий виходи блоку мікропрограмного управління з'єднані відповідно з входами запису/читання регістра адреси і регістра даних, вихід ознаки якого з'єднаний з четвертим входом режиму блоку мікропрограмного управління, сьомий і восьмий виходи якого з'єднані відповідно з входами запису/читання блоку пам'яті управляючих слів і блоку пам'яті операндів, вихід ознаки якого з'єднаний з п'ятим входом режиму блоку мікропрограмного управління, дев'ятий вихід якого з'єднаний з управляючим входом блока буферної пам'яті команд, вихід ознаки якого з'єднаний з шостим входом режиму блоку мікропрограмного управління, десятий вихід якого з'єднаний з управляючим входом блоку виводу, вихід ознаки якого з'єднаний з сьомим входом режиму блоку мікропрограмного управління, інформаційні виходи регістрів команд з'єднані з четвертим інформаційним входом блока буферної пам'яті команд, другий інформаційний вихід якого з'єднаний з інформаційними входами кожного і-го регістра команд (i=1, ..., n), управляючі входи яких з'єднаний з i-ми виходами одинадцятої групи управляючих виходів блока мікропрограмного управління. Згідно з винаходом до складу пристрою введені n блоків таймерів виконання операції інформаційні виходи яких з'єднані з п'ятим інформаційним входом блока буферної пам'яті команд, третій інформаційний вихід якого з'єднаний з інформаційними входами кожного і-то блока таймеру виконання операції (i=1, ..., n), управляючі входи яких з'єднаний з i-ми виходами восьмої групи управляючих виходів блока мікропрограмного управління, кожен /-й вихід (i=1, ... n) дванадцятої групи управляючих виходів якого з'єднаний з управляючим входом і-то блоку таймеру виконання команди. На Фіг. 1 представлена структурна схема обчислювального пристрою; на Фіг. 2 формат управляючого слова; на Фіг. 3 - формат слова даних; на Фіг. 4 - алгоритм завантаження в блок буферної пам'яті даних управляючих слів, слів даних і результатів виконання команди; на Фіг. 5 - алгоритм розподілу команд між блоками обробки інформації. Обчислювальний пристрій містить блок 1 вводу даних, інформаційний вихід якого підключений до першого інформаційного входу комутатора 2, вихід якого зв'язаний з інформаційним входом блока 3 буферні пам'яті даних. Управляючий вхід і вихід ознаки даних блока 1 вводу даних з'єднані з відповідним входом і виходом блока 4 мікропрограмного управління, вихід якого підключений до управляючого входу комутатора 2. Управляючий вхід блока 3 буферної пам'яті даних, що забезпечує занесення інформації і просування черги, підключений до виходу блока 4 мікропрограмного управління, відповідний вхід якого з'єднаний з виходом сигналів блока 3 буферної пам'яті даних, що характеризують ступінь його заповнення ("Буфер зайнятий" і "Буфер порожній"). До інформаційних входів регістра даних 5 і регістра адреси 6 підключені відповідно перший і другий інформаційний виходи блока 3 буферної пам'яті даних. Входи запису/читання регістрів 5 7 данихі 6 адреса підключені до виходів блока 4 мікропрограмного управління, а вихід одного розряду регістра даних 5 (ознака типу інформації) підключений до відповідного входу блока 4 мікропрограмного управління. Інформаційний вихід регістра адреси 6 зв'язаний з адресними входами блока 7 пам'яті операндів і блока 8 пам'яті управляючих слів. Інформаційний вихід регістра даних 5 підключений до інформаційних входів блока 7 пам'яті операндів, блока 8 пам'яті управляючих слів і до першого інформаційного входу блока 9 буферної пам'яті команд (вхід першого операнда). В блок 9 буферної пам'яті команд записується команда, що умовно розбита на три складових (перший операнд, другий операнд, управляюче слово). Другий і третій інформаційні входи блока 9 буферної пам'яті команд з'єднані відповідно з інформаційними виходами блока 7 пам'яті операндів (другий операнд) і блока 8 пам'яті управляючих слів (управляюче слово). До входів запису/читання блока 7 пам'яті операндів і блока 8 пам'яті управляючих слів підключені відповідні виходи блока 4 мікропрограмного управління. Вихід блока 4 зв'язаний із входом одного інформаційного розряду (ознаки наявності операнда) блока 7 пам'яті операндів, а вихід цього розряду з'єднаний із входом режиму блоку 4. Виходи, що вказують на ступінь заповнення, а так само і управляючі входи запису і просування черги блока 9 підключені до відповідних входів і виходів блока 4. Перший інформаційний вихід блока 9 буферної пам'яті команд підключений до інформаційного входу блока 13 виводу даних, управляючий вхід і вихід ознаки готовності якого зв'язані з відповідними виходом і входом блока 4. Другий інформаційний вихід блока 9 буферної пам'яті команд підключений до інформаційних входів блоків обробки інформації 10.1, ..., 10.n і до інформаційних входів регістрів команд 11.1, ..., 11.n, управляючі входи яких зв'язані з відповідною групою управляючих виходів блока 4 мікропрограмного управління. Третій інформаційний вихід блока 9 буферної пам'яті команд підключений до інформаційних входів блоків таймерів виконання операції 12.112.n управляючі входи яких зв'язані з відповідною групою управляючих виходів блока 4 мікропрограмного управління. Групи управляючих входів і виходів блока 4 мікропрограмного управління підключені до відповідних виходів і входів блоків обробки інформації 10.1, ..., 10.n, інформаційні виходи яких з'єднані з інформаційними входами комутатора 2. Інформаційний вхід блоку 1 вводу даних зв'язаний з інформаційним входом пристрою 14, інформаційний вихід 15 якого з'єднаний з інформаційним виходом блока 13 виводу даних. Для реалізації блока 3 буферної пам'яті даних і блока 9 буферної пам'яті команд можна використовувати будь-який запам'ятовуючий пристрій, що працює за принципом "Першим увійшов - першим вийшов" (FIFO). 59112 8 Для кожного з блоків 10.1, ..., 10.n обробки інформації використовується таймер, який формує сигнал, що відповідає інтервалові часу tr. Обчислювальний пристрій працює наступним чином. Вихідна для обчислень інформація поступає з інформаційного входу пристрою 13 через блок 1 вводу даних і являє собою послідовність управляючих слів і слів даних. Управляюче слово, формат якого представлений на Фіг. 2, містить gрозрядне поле коду операції, розряд номера операнда, що обчислюється, s-розрядне поле номера наступної операції, розряд ознаки типу інформації, m-розрядне поле номера операції (де q, s, m - цілі числа). У склад управляючого слова введено поле Т часу очікування результату виконання конкретної операції. Розряд ознаки типу інформації для всіх управляючих слів має значення "1". Інформація, що записується в інші поля управляючого слова, визначається заданим графом алгоритму обчислень, який будується незалежно від числа n блоків обробки інформації. Довжина q поля коду операції (Фіг. 2) визначається кількістю команд і повинна включати не менш log2N розрядів. Розрядність m повинна забезпечувати можливість запису найбільшого номера операції (вершини на графі), а розрядність s - або максимального номера, або максимальної по модулю різниці номеру операцій. Розрядність поля значення операнда (Фіг. 3) залежить від форми і точності представлення операндів. Це поле може включати знакові розряди, мантису і порядок. У вихідному стані блоки 3 буферної пам'яті даних і 9 буферної пам'яті команд порожні (виробляються сигнали "Буфер порожній"). Ланцюги установки вихідного стану умовно не показані. При функціонуванні пристрою можна виділити наступні процеси: - ввод у блок 3 буферної пам'яті інформації з блока 1 вводу даних і з блоків обробки інформації 10.1, ..., 10.n (у випадку справної роботи блоків 10.1, ..., 10.n); - формування команди і занесення її в блок 9 буферної пам'яті команд; - розподіл команд між блоками 10.1, ..., 10...n обробки інформації (для подальшої обробки) і блоком 12 виводу даних. Розглянемо роботу пристрою у випадку, коли відмовлення блоків інформації відсутні. Перший із зазначених процесів ілюструється алгоритмом на Фіг. 4. Блок 4 аналізує сигнал "Буфер даних заповнений" блока 3 буферної пам'яті даних. При відсутності указаного сигналу, коли в блок 3 буферної пам'яті даних можна записати інформацію, блок 4 перевіряє сигнал на виході ознаки даних блока 1 вводу даних і сигнали на виходах ознаки завершення операції блоків обробки інформації 10.1, ..., 10.n. Наявність першого із указаних сигналів свідчить про те, що блок 1 вводу даних прийняв дані з інформаційного входу 14 пристрою. У цьому випадку за управляючими сигналами блока 4 мікропрограмного управління інформація з блока 1 через комутатор 2 записується в блок 3. Аналогічним образом відбувається запис у блок 3 із блока 10.j у випадку його готовності до передачі даних, тобто 9 готовності результату. В останньому випадку в блок 10.j обробки інформації передається сигнал "Результат прийнятий" із блока 4 мікропрограмного управління і блок 10.j знімає сигнал ознаки завершення операції. Якщо блок 3 не готовий до запису (заповнений), то виконується очікування моменту, коли запис буде можливий (зніметься сигнал "Буфер даних заповнений"). Якщо блок 10.j обробки інформації не виставляє сигналу ознаки завершення операції, то блок 4 мікропрограмного управління перевіряє наявність сигналу закінчення часу виконання команди від блока 12.j таймеру виконання операції (сигнал «Час вийшов»), таймер налаштований на час, за який результат повинен бути отриманий обов'язково, якщо блок 10.j не вийшов з ладу. Коли блок 10.J обробки інформації працює правильно, тобто сигнал від таймера 12.j відсутній перевіряється сигнал ознаки завершення операції в наступному блоці 10.(j+1) обробки інформації. У процесі ввода вихідної інформації з блока 1 вводу даних спочатку вводиться управляюче слово, а потім слово даних для відповідної операції. Процес формування команди здійснюється в такий спосіб. Управляюче слово записується в блок 8 управляючих слів за адресом, що відповідає номеру операції. Перше із спів даних, що надходять, для цієї операції записується по тому же адресу в блок 7 пам'яті операндів. Далі управляюче слово й один з операндов очікують надходження з блоку 3 даних відсутнього операнда, після чого виконується компонування команди. Команда містить управляюче слово, два операнда, номер операції і записується в блок 9 (у чергу для виконання), причому номер операції записується з регістра 6. Алгоритм формування команди наступний. Блок 4 мікропрограмного управління аналізує сигнал "Буфер порожній" блока 3 буферної пам'яті даних. При відсутності зазначеного сигналу (у блоці є хоча б одне слово) слово з його виходу записується в регістри адреса 6 і даних 5, причому в регістр 6 записується поле номера операції (див. Фіг. 2 і Фіг. 3). Блок 4 перевіряє в регістрі даних 5 ознаку типу інформації, що має одиничне значення для управляючих слів і нульове - для слова даних. Якщо ознака типу інформації дорівнює "1", то в блок 8 записується управляюче слово. Одночасно з цим у блок 7 записується " 1" у розряд ознаки наявності операнда (це означає, що для даного управляючого слова в блоці 7 немає жодного операнда). У процесі запису адресом для блоків пам'яті операндів 7 і управляючих слів 8 є вміст регістра 6. У блок 8 дані записуються з регістра 5, у блок 7 одиничне значення на вхід розряду ознаки наявності операнда подається з блока 4 мікропрограмного управління. У випадку якщо в регістрі 5 ознака типу інформації дорівнює "0" (слово є даними), здійснюється перевірка ознаки наявності операнда в блоці 7 пам'яті операндів. Для цього здійснюється читання блоків 7 і 8 і аналіз ознаки наявності операнда. Якщо ця ознака дорівнює "1" (у блоці 7 пам'яті операндів немає операнда для даного управляючого слова) здійснюється запис у блок 7 слова з регістра 5. Одночасно з цим в ознаку наявності 59112 10 операнда записується "0" (для даної операції є один операнд). Якщо ознака наявності операнда дорівнює "0" і відсутній сигнал "Буфер заповнений" готова до виконання команда (управляюче слово з блока 8 пам'яті управляючих слів, один операнд із блока 7, другий операнд із регістра даних 5 і номер операції з регістра 6) записуються в блок 9 буферної пам'яті команд. Розряд ознаки наявності операнда в блоці 7 встановлюється в "1". Якщо в блоці 9 є хоча б одна команда (немає сигналу "Буфер порожній"), то блок 4 аналізує поле типу команди на виходах блока 9 і забезпечує передачу команди в блок 13 виводу даних або в один із блоків обробки інформації 10.j. Якщо команда має обчислювальний характер (додавання, множення і т.д.), передача її в блок 10.j. здійснюється відповідно до алгоритму, наведеному на Фіг. 5. Готовий до прийому команди блок 10.j обробки інформації видає в блок 4 сигнал "Готовність прийому команди". Указаний сигнал формується тільки після перевірки працездатності блока убудованими схемами контролю або тестом. Блок 4 по черзі аналізує готовність кожного блока обробки інформації 10.1, ..., 10.n, здатного виконати дану команду. Блок 4 передає готовому блокові 10.j управляючий сигнал "Прийняти команду". Команда з блока 9 буферної пам'яті команд передається в блок 10.j обробки інформації. Одночасно з цим за відповідними сигналами блоку 4 мікропрограмного управління команда з блока 9 записується в регістр команд 11.j, а відповідний час виконання команди із поля управляючого слова записується в блок 12.j таймеру виконання операції. Далі блок 10.j скидає сигнал "Готовність прийому команди" і починає виконання своєї команди. Після зняття сигналу "Готовність прийому команди" блок 4 мікропрограмного управління виробляє сигнал "Просунути чергу" для блока 9 буферної пам'яті команд. Описаний процес формування команди повторюється циклічно. У процесі обробки команди кожен блок 10.j обробки інформації обмінюється з блоком 4 мікропрограмного управління двома вхідними і двома вихідними управляючими сигналами. Одна пара сигналів (вхідний і вихідний) використовуються для вводу команди, а інша для видачі результату після виконання команди. Операнди, що не мають змістовного значення, у блоках 10.1, ..., 10.n не обробляються. У роботі обчислювального пристрою можуть виникнути збої в роботі одного або декількох блоків обробки інформації. Збої можуть виникнути після того, як виставлений сигнал "Готовність приймання команди" або після того, як він знятий. В обох випадках необхідно повторити команду, що повинна була виконуватися або виконувалася в несправному блоці обробки інформації. Розглянемо випадок, коли блок 10.j обробки інформації не знімає сигнал "Готовність прийому команди", тобто він вийшов з ладу до початку виконання команди. Як видно з алгоритму на Фіг. 5, блок 4 мікропрограмного управління аналізує, чи знятий сигнал "Готовність прийому команди" на інтервалі часу t≥tr. Час tr вибирається таким чином, що за даний інтервал часу блок обробки ін 11 формації при правильному функціонуванні обов'язково прийме команду і зніме сигнал "Готовність прийому команди". Якщо по закінченню часу її цього не відбулося, то блок 4 мікропрограмного управління повторює процедуру передачі команди наступному (i+1)-му блокові обробки інформації. Таким чином, якщо є хоча б один працездатний блок, то команда буде передана йому. Розглянемо другий випадок, коли блок 10.j виходить з ладу після зняття сигналу "Готовність прийому команди". У цьому випадку використовується таймер, що реалізований у блоці 12.j таймеру виконання операції, налаштований індивідуально на час Ті виконання кожної окремої операції. Таймер в блоці 12.j запускається сигналом запису часу виконання відповідної команди, що надходить від блоку управління 4 із затримкою на час tr. При зчитуванні результату операції (Фіг. 4) блок 4 мікропрограмного управління по черзі перевіряє сигнал "Готовність видачі результату" у кожнім блоці 10.j, а при його відсутності перевіряє сигнал "Час вийшов" у кожнім блоці 12.j, що сигналізує про закінчення часу Tj, який виділявся для виконання цієї операції. Якщо сигнал "Готовність видачі результату" формується протягом відрізка часу Tj, то результат вважається правильним і записується в блок 3 буферної пам'яті даних. Якщо після закінчення часу Tj блок 10.j не виставив сигнал "Готовність видачі результату", здійснюється повторний запис команди в блок 9 буферної пам'яті команд із регістра команди 11.j з урахуванням стану буфера. У наслідок цього невиконана команда повторно ставиться в чергу в блоці 9 буферної пам'яті команд і буде передана в справний блок обробки інформації. Повторний запис команди здійснюється за допомогою сигналу "Записати з регістра команд 11.j у блок 9" який надходить із блока 4 мікропрограмного управління на управляючий вхід відповідного регістра команди 11.j. У запропонованому пристрої при відмовленні будь-якого обчислювального блока виконується реконфігурація системи, під час якої невиконана 59112 12 команда повторно записується в буфер готових команд, незалежно від інформації наявної в середовищі формування команд в даний момент часу, і буде виконана в працездатному обчислювальному блоці. У формат кожної команди введений час очікування виконання даної команди. Під час відправлення команди на виконання у блок обробки даних час виконання команди завантажується в блок таймеру виконання команди, який запускається завантаженням слова команди у блок обробки даних. Це дозволяє зменшити час затримки під час реконфігурації системи за виходу з ладу блоків обробки даних, за рахунок індивідуального налаштування блоків таймерів виконання операцій на час необхідний для виконання кожної операції. Це, у свою чергу, забезпечує скорочення часу перетворення інформації, тобто, у загальному випадку, підвищення продуктивності пристрою. Таким чином, поставлена мета - підвищення функціональних можливостей і продуктивності пристрою за рахунок зменшення часу затримки під час ре-конфігурацію системи за відмов устаткування, за допомогою запропонованого технічного рішення досягається. Літературні джерела: 1. Пат. на изобр. № 1709331 СССР, МКИ G06 F 15/16; 15/80. Вычислительная система: / В.И. Жабин, Г.В. Гончаренко, В.В. Ткаченко (СССР) - № 4797732/24; Заявлено 28.02.90; Опубл. 30.01.92, Бюл. № 4. - 17 с. 2. Пат. на изобр. № 2030785 СССР, МКВ G 06 F 15/16. Вычислительное устройство / B.I. Жабін, Г.В. Гончаренко, В.В. Макаров, В.В. Ткаченко (Україна). - № 4867678: Заявлено 21.09.1990; Опубл. 10.03.1995. - 23 с. 3. Дек. пат. № 7727 України, МКВ G 06 F 15/16, 15/76. Обчислювальній пристрій / І.А. Жуков, B.I. Жабін, І.А. Клименко, В.В. Ткаченко (Україна). - № 20040907712: Заявлено 22.09.2004; Опубл. 15.07.2005, Бюл. № 7. - 9 с. 13 59112 14 15 59112 16 17 Комп’ютерна верстка Д. Шеверун 59112 Підписне 18 Тираж 23 прим. Міністерство освіти і науки України Державний департамент інтелектуальної власності, вул. Урицького, 45, м. Київ, МСП, 03680, Україна ДП “Український інститут промислової власності”, вул. Глазунова, 1, м. Київ – 42, 01601

ДивитисяДодаткова інформація

Назва патенту англійськоюComputing unit

Автори англійськоюKlymenko Iryna Anatoliivna, Zhabina Valentyna Valeriivna

Назва патенту російськоюВычислительное устройство

Автори російськоюКлименко Ирина Анатольевна, Жабина Валентина Валерьевна

МПК / Мітки

МПК: G06F 15/16

Мітки: обчислювальній, пристрій

Код посилання

<a href="https://ua.patents.su/9-59112-obchislyuvalnijj-pristrijj.html" target="_blank" rel="follow" title="База патентів України">Обчислювальний пристрій</a>

Попередній патент: Спосіб стрічкового обробітку ґрунту з локальним внесенням добрив

Наступний патент: Лазерний двокомпонентний допплерівський анемометр

Випадковий патент: Теплообмінний блок теплоутилізатора