Спосіб аналого-цифрового перетворення та пристрій для його реалізації

Формула / Реферат

1. Спосіб аналого-цифрового перетворення, що полягає в синхронному накопиченні й осередненні сигналу в точках квантування, який відрізняється тим, що фіксують значення цифрового рівня, досягнутого сигналом, а наступні коди сигналу порівнюють із зафіксованим значенням, причому запам’ятовують моменти часу перетворень, код сигналів яких відрізняється від зафіксованого на одиницю молодшого розряду, та підраховують число таких перетворень, поки код сигналу не зміниться більш чим на одиницю молодшого розряду відносно зафіксованого значення, що відповідає перетинанню сигналу з наступним цифровим рівнем, після чого визначають момент часу, у який цифровий код найбільш точно відповідав аналоговому сигналу шляхом осереднення значень часу, у які були отримані коди сигналу, відмінні від зафіксованого значення.

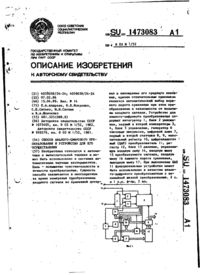

2. Пристрій аналого-цифрового перетворення, що містить аналого-цифровий перетворювач (АЦП), генератор імпульсів, тригер, два лічильники, суматор, перший компаратор, логічні елементи «АБО», «ТА», причому настановний вхід тригера з’єднаний з електронною обчислювальною машиною (ЕОМ), вихід тригера зв’язаний із входом генератора імпульсів, вихід якого зв’язаний з першим входом елемента «ТА», а вихід «Менше» компаратора зв’язаний з першим входом елемента «АБО», який відрізняється тим, що до нього введені чотири регістри, другий компаратор, мультиплексор, причому другий вхід елемента «ТА» з’єднаний з виходом тригера, вихід елемента «ТА» підключений до стробувальних входів першого лічильника, АЦП, першого регістра та першого компаратора, вихід АЦП з’єднаний з інформаційним входом першого регістра, вихід якого з’єднаний із входами другого та третього регістрів, першим входом першого компаратора, вихід другого регістра з’єднаний із другим входом першого компаратора, вихід «Більше» якого підключений до другого входу елемента «АБО», вихід якого з’єднаний зі стробувальними входами суматора, другого лічильника та з першим стробувальним входом третього регістра, вихід якого з’єднаний з першим входом другого компаратора та входом четвертого регістра, вихід якого з’єднаний з першим входом мультиплексора та другим входом другого компаратора, стробувальний вхід якого з’єднаний з виходом елемента «АБО», інформаційний вихід першого лічильника з’єднаний з першим входом суматора, а вихід «Дорівнює нулю» зі стробувальним входом другого регістра, вихід суматора підключений до другого входу мультиплексора та другого входу того ж суматора, вихід «Менше нуля» четвертого регістра з’єднаний зі стробувальними входами четвертого та третього регістрів, інкрементуючий вхід якого з’єднаний з виходом «Більше» першого компаратора, вихід другого компаратора з’єднаний із ЕОМ та із входами скидання тригера, суматора, другого лічильника, вихід якого зв’язаний із третім входом мультиплексора, керуючий вхід і інформаційний вихід якого підключені до ЕОМ, що підключена також до входів «-1» першого лічильника та четвертого регістра.

Текст

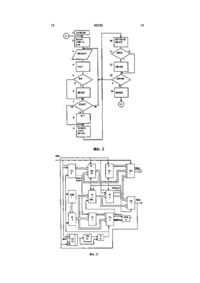

1 Спосіб аналого-цифрового перетворення, що полягає в синхронному накопиченні й осередненні сигналу в точках квантування, який відрізняється тим, що фіксують значення цифрового рівня, досягнутого сигналом, а наступні коди сигналу порівнюють із зафіксованим значенням, причому запам'ятовують моменти часу перетворень, код сигналів яких відрізняється від зафіксованого на одиницю молодшого розряду, та підраховують число таких перетворень, поки код сигналу не зміниться більш чим на одиницю молодшого розряду відносно зафіксованого значення, що відповідає перетинанню сигналу з наступним цифровим рівнем, після чого визначають момент часу, у який цифровий код найбільш точно відповідав аналоговому сигналу шляхом осереднення значень часу, у які були отримані коди сигналу, ВІДМІННІ ВІД зафіксованого значення 2 Пристрій аналого-цифрового перетворення, що містить АЦП, генератор імпульсів, тригер, два лічильники, суматор, перший компаратор, ЛОГІЧНІ елементи «ИЛИ», «И», причому настановний вхід тригера з'єднаний з ЕОМ, вихід тригера зв'язаний із входом генератора імпульсів, вихід якого зв'язаний з першим входом елемента «И», а вихід «Меньше» компаратора зв'язаний з першим входом елемента «ИЛИ», який відрізняється тим, що до нього введені чотири регістри, другий компаратор, мультиплексор, причому другий вхід елемен Винахід відноситься до аналого-цифрової обчислювальної техніки й може бути використаний для аналого-цифрового перетворення сигналів ВІДОМІ способи аналого-цифрового перетворення та пристрої для їхньої реалізації (Гитис Э И Аналого-цифровые преобразователи - М , 1981 с 71) При надходженні на вхід АЦП сигналу з перешкодою, зменшення впливу перешкод можна та «И» з'єднаний з виходом тригера, вихід елемента «И» підключений до стробувальних входів першого лічильника, АЦП, першого регістра та першого компаратора, вихід АЦП з'єднаний з інформаційним входом першого регістра, вихід якого з'єднаний із входами другого та третього регістрів, першим входом першого компаратора, вихід другого регістра з'єднаний із другим входом першого компаратора, вихід «Больше» якого підключений до другого входу елемента «ИЛИ», вихід якого з'єднаний зі стробувальними входами суматора, другого лічильника та з першим стробувальним входом третього регістра, вихід якого з'єднаний з першим входом другого компаратора та входом четвертого регістра, вихід якого з'єднаний з першим входом мультиплексора та другим входом другого компаратора, стробувальний вхід якого з'єднаний з виходом елемента «ИЛИ», інформаційний вихід першого лічильника з'єднаний з першим входом суматора, а вихід «Равно нулю» зі стробувальним входом другого регістра, вихід суматора підключений до другого входу мультиплексора та другого входу того ж суматора, вихід «Меньше нуля» четвертого регістра з'єднаний зі стробувальними входами четвертого та третього регістрів, шкрементуючий вхід якого з'єднаний з виходом «Больше» першого компаратора, вихід другого компаратора з'єднаний із ЕОМ та із входами скидання тригера, суматора, другого лічильника, вихід якого зв'язаний із третім входом мультиплексора, керуючий вхід і інформаційний вихід якого підключени до ЕОМ, що підключена також до входів «-1» першого лічильника та четвертого регістра досягти при використанні статистичної обробки результатів перетворень Передбачається, що спектри сигналу й шуму значною мірою не перекриваються та спектр шуму лежить в області більш високих частот, що дозволяє вважати сигнал постійним протягом вибірки При підвищенні точності аналого-цифрового перетворення методом цифрового інтегрування використовуються (О 62142 вибірки з m результатів перетворення, у кожному з яких виходить деяке значення вихідного коду LI, При цифровому інтегруванні на виході АЦП відбувається підсумовування цих кодів Для одержання результату статистичної обробки необхідно здійснити ділення отриманої суми кодів на число членів у вибірці m Результат осереднення відносять до середини інтервалу осереднення, оскільки при перетворенні можна вважати, що за час осереднення Тус=тТкв, де Ткв - період квантування, похідна вхідного сигналу не змінює знака, й апроксимувати цю ділянку прямої Оптимальне значення інтервалу осереднення одержують виходячи з умови мінімуму дисперсії осередненого результату Недоліки таких методів у тому, що вони дають погані результати щодо точності при сумірності рівня шуму та кванта, оскільки в цьому випадку відбувається зсув оцінок вихідного сигналу, складність полягає й у визначенні інтервалу осереднення, тому що в більшості випадків невідомий коефіцієнт кореляції вхідного сигналу Пристрій, що реалізує описаний спосіб, включає аналого-цифровий перетворювач, дільник частоти з коефіцієнтом ділення, рівним КІЛЬКОСТІ перетворень на інтервалі осереднення, суматор для підсумовування вихідних кодів АЦП, генератор тактових імпульсів, що синхронізує роботу пристрою, а також лічильник поточного часу та зсувний регістр для визначення середини інтервалу осереднення, до якої відносять результат осереднення, буферний регістр За синхроімпульсом АЦП здійснює перетворення вхідного сигналу, і код з його виходу надходить на один із входів суматора, а на другий вхід суматора - код із буферного регістра (у початковий момент часу регістр обнулений), сума переписується до регістра, та процес повторюється доти, доки не заповниться лічильник числа перетворень, за сигналом з якого сума з буферного регістра надходить на дільник частоти, тобто відбувається Осереднення накопичених кодів Відомий пристрій для введення аналогової інформації (ас СРСР №1425644 від 06 08 86 G06F3/05), у якому описаний спосіб аналогоцифрового перетворення, заснований на синхронному накопиченні й осередненні сигналів уточках квантування здійснюється підсумовування заданого числа реалізацій, отриманих у результаті перетворення вхідного стаціонарного сигналу Накопичена сума в точках квантування поділяється на КІЛЬКІСТЬ реалізацій Осереднена реалізація виходить у тимчасових точках, закодованих за першою реалізацією Недолік цього способу полягає в тому, що здійснюється осереднення сигналу, який уже містить погрішність дискретизації, що приводить до зсуву статистичних оцінок і, отже, до зниження точності перетворення Пристрій для здійснення відомого способу містить два аналого-цифрові перетворювачі, блок диференціювання, дільник частоти з перемінним коефіцієнтом ділення, тригер, генератор імпульсів, два лічильники - адреси й поточного часу, блок оперативної пам'яті, суматор, компаратор, керований дільник частоти, ЛОГІЧНІ елементи "ИЛИ", "И" Робота пристрою починається за сигналом "Пуск", що надходить на настановний вхід тригера, вихід якого дозволяє запуск генератора імпульсів Аналоговий сигнал, що реєструється, надходить на вхід АЦП і блоку диференціювання Сигнал, пропорційний швидкості зміни вхідного, надходить на вхід другого АЦП, код з виходу якого керує керованим дільником частоти, імпульси з якого через елемент "ИЛИ" надходять на вхід запуску першого АЦП і на вхід лічильника адреси З виходу першого АЦП інформаційний сигнал надходить на вхід дільника частоти, де поділяється на задану КІЛЬКІСТЬ реалізацій, а потім на один із входів суматора, на другий вхід якого надходить сигнал з відповідної чарунки блоку пам'яті Результат записується за цією ж адресою При реєстрації першої реалізації в цій же чарунці записується час з виходу лічильника поточного часу Запис реалізацій припиняється по заповненні лічильника адреси, сигнал переповнення якого скидає настановний тригер, лічильники При реєстрації другої реалізації до компаратора із чарунки пам'яті, зазначеної лічильником адреси, подається код часу, у який зроблений запис сигналу, що знаходиться в пам'яті за цією ж адресою На другий вхід компаратора надходить код часу з виходу лічильника поточного часу, при збігу кодів виробляється імпульс, що через елемент "ИЛИ" спробує другий АЦП Оцифроване значення вхідного сигналу з виходу АЦП проходить через дільник, надходить на один із входів суматора Потім процес повторюється, але запис до пам'яті здійснюється за наступною адресою По закінченні реєстрації у блоці пам'яті зафіксовані осереднена реалізація та її тимчасовий код, причому залежно від крутості вхідного сигналу змінюється крок квантування Недолік цього пристрою полягає втому, що він знижує тільки вплив випадкових перешкод на стаціонарний сигнал, що у свою чергу не дозволяє істотно підвищити точність перетворення В основу винаходу покладена задача створення способу аналого-цифрового перетворення та пристрою, що реалізує цей спосіб, які володіють високою точністю перетворення за рахунок зменшення погрішності дискретизації Зазначений технічний результат досягається тим, що у способі, який включає синхронне накопичення й осереднення сигналу, додатково фіксується значення цифрового рівня, досягнутого сигналом, а наступні коди сигналу порівнюють із зафіксованим значенням, причому запам'ятовують моменти часу перетворень, код сигналів яких відрізняється від зафіксованого на одиницю молодшого розряду, і підраховують число таких перетворень, поки код сигналу не зміниться більш чим на одиницю молодшого розряду відносно зафіксованого значення, що відповідає перетинанню сигналу з наступним цифровим рівнем, після чого визначають момент часу, у який цифровий код найбільш точно відповідав аналоговому сигналу шляхом осереднення значень часу, у які були отримані коди сигналу, ВІДМІННІ ВІД зафіксованого значення Таким чином, завдяки виділенню з усього масиву перетворень тих, коди яких відповідають конкретним цифровим рівням, знижується погріш 62142 ність дискретизації Сукупність наведених ВІДМІННИХ ознак способу, що заявляється, дозволяє підвищити точність аналого-цифрового перетворення шляхом зменшення погрішності дискретизації за рахунок виділення з усього масиву перетворень найбільш точних, а погрішність, обумовлена впливом випадкової перешкоди, знижується завдяки тому, що виділяються перетворення, код сигналу в яких мав стійке значення Зазначений технічний результат досягається тим, що до відомого пристрою, що містить АЦП, генератор імпульсів, тригер, два лічильники, суматор, перший компаратор, ЛОГІЧНІ, елементи "ИЛИ", "И", причому настановний вхід тригера з'єднаний з ЕОМ, вихід тригера зв'язаний із входом генератора імпульсів, вихід якого зв'язаний з першим входом елемента "И", а вихід "Меньше" компаратора зв'язаний з - першим входом елемента "ИЛИ", додатково введені чотири регістри, другий компаратор, мультиплексор, причому другий вхід елемента "И" з'єднаний з виходом тригера, вихід елемента "И" підключений до стробувальних входів першого лічильника, АЦП, першого регістра та першого компаратора, вихід АЦП з'єднаний з інформаційним входом першого регістра, вихід якого з'єднаний із входами другого та третього регістрів, першим входом першого компаратора, вихід другого регістра з'єднаний із другим входом першого компаратора, вихід "Больше" якого підключений до другого входу елемента "ИЛИ", вихід якого з'єднаний зі стробувальними входами суматора, другого лічильника та з першим стробувальним входом третього регістра, вихід якого з'єднаний з першим входом другого компаратора та входом четвертого регістра, вихід якого з'єднаний з першим входом мультиплексора та другим входом другого компаратора, стробувальний вхід якого з'єднаний з виходом елемента "ИЛИ", інформаційний вихід першого лічильника з'єднаний з першим входом суматора, а вихід "Равно нулю" зі стробувальним входом другого регістра, вихід суматора підключений до другого входу мультиплексора та другого входу того ж суматора, вихід "Меньше нуля" четвертого регістра з'єднаний зі стробувальними входами четвертого та третього регістра, шкрементуючий вхід якого з'єднаний з виходом «Больше» першого компаратора, вихід другого компаратора з'єднаний із входами скидання тригера, суматора, другого лічильника, вихід якого зв'язаний із третім входом мультиплексора, керуючий вхід і інформаційний вихід якого підключені до ЕОМ, що підключена також до входів «-1» першого лічильника та четвертого регістра Сукупність наведених ВІДМІННИХ ознак дозволяє підвищити точність аналого-цифрового перетворення пристрою за рахунок зменшення погрішності дискретизації На фіг 1 наведені графіки впливу шуму квантування й випадкової перешкоди на результат перетворення сигналу На фіг 2 наведена блок-схема способу аналого-цифрового перетворення На фіг 3 наведена структурна схема пристрою аналого-цифрового перетворення На фіг 4 наведена тимчасова діаграма почат кового запуску пристрою На фіг 5 наведена тимчасова діаграма роботи пристрою у разі зменшення коду сигналу відносно зафіксованого значення На фіг 6 наведена тимчасова діаграма роботи пристрою при збільшенні коду сигналу на одиницю відносно попереднього значення, але рівності його зафіксованому значенню На фіг 7 наведений приклад конкретного виконання регістра поточного рівня На фіг 8 наведений приклад конкретного виконання регістра попереднього коду На фіг 9 наведений приклад конкретного виконання лічильника поточного часу На фіг 10 наведений приклад конкретного виконання суматора На фіг 11 наведений приклад конкретного виконання мультиплексора Запропонований спосіб пояснюється схемою, наведеною на фіг 1 По координатних осях відкладені проміжки, рівні періоду перетворення АЦП Та і напрузі, що відповідає кроку квантування (різниця між сусідніми цифровими рівнями дорівнює одиниці молодшого розряду АЦП) q Далі зображені наступні сигнали U - вхідний, повільно наростаючий сигнал, К - вихідний цифровий сигнал, UB - амплітуда випадкової перешкоди, приведеної до входу З усієї ПОСЛІДОВНОСТІ перетворень найбільш точний результат мають найближчі до моменту перетинання аналогового сигналу й чергового цифрового рівня -tn+i, tn+2 і т д За відсутності перешкоди з амплітудою, меншою за крок квантування, для забезпечення найбільшої точності треба з усього масиву цифрової інформації виділити тільки ці найбільш точні перетворення Перешкода з амплітудою UB породжує в околі точок перетинання ЛІНІЙ сигналу та цифрового рівня інтервали нестійкого стану молодшого розряду АЦП [tn'+i, tn"+i] і [tn'+2, tn"+2] Визначити ці інтервали з точністю, рівною періоду перетворення Та і виділити моменти найбільш точних перетворень дозволяє пропонований спосіб аналого-цифрового перетворення, блок-схема якого наведена на фіг 2 Тут використані наступні умовні позначки SI - сума часу одержання перетворень, коди в яких менші за досягнуті цифрові значення, І - поточний час, J - число відхилень коду сигналу від зафіксованого цифрового значення - перехід, КР - попередній код, КТ - поточний код, ИР - зафіксоване цифрове значення рівня, перетятого аналоговим сигналом, ИТ - поточне цифрове значення сигналу, Е - коригувальна одиниця Перетворення здійснюється в такий спосіб уводиться код сигналу КТ і визначається час його одержання І Якщо це код, що відповідає новому цифровому рівню, то відразу попередній код уважається рівним уведеному Після цього попередній і поточний коди порівнюються Якщо виявлена рівність, то вводиться наступний код, якщо коди нерівні, то накопичується сума часу одержання кодів, ВІДМІННИХ від зафіксованого, збільшується 62142 число таких відхилень J і фіксується поточне цифрове значення сигналу ИТ, при цьому якщо поточний код зменшився на одиницю, цифрове значення не змінюється, а якщо збільшився - теж збільшується Після ЦЬОГО порівнюється зафіксоване цифрове значення сигналу ИР і поточне ИТ Якщо вони рівні, то вводиться наступний код, а якщо нове цифрове значення більше, то, отже, і сигнал має нове цифрове значення Для визначення наближеного моменту часу, у який сигнал отримав старе цифрове значення, накопичену суму часу одержання перетворень SI поділяють на число відхилень коду сигналу від старого цифрового значення J Після ЦЬОГО сума часу та число відхилень обнуляються, уводиться наступний код сигналу й описані дії повторюються, але фіксується значення нового цифрового рівня, перетятого сигналом У такий спосіб з ПОСЛІДОВНОСТІ перетворень виділяються перетворення, моменти одержання яких відповідають моментам перетинань аналогового сигналу з цифровими рівнями Отримані перетворення можуть використовуватися для подальшого опрацювання Пристрій аналого-цифрового перетворення (фігЗ) містить АЦП 1, регістри 2, 3, 4, 5, компаратори 6 і 7, лічильники 8 і 9, суматор 10, мультиплексор 11, тригер 12, генератор імпульсів 13, елемент 14 "И", елемент 15 "ИЛИ" Вихід АЦП 1 з'єднаний з інформаційним входом регістра 2 поточного коду, вихід якого з'єднаний з інформаційним входом регістра 3 попереднього коду, регістра 4 поточного рівня й першим входом компаратора 6 Вихід регістра 3 попереднього коду зв'язаний із другим входом компаратора 6, вихід "Меньше" якого з'єднаний з першим входом елемента 15 "ИЛИ", а вихід "Больше" компаратора 6 - із другим входом елемента 15 "ИЛИ" й шкрементуючим входом регістра 4 поточного рівня, вихід якого зв'язаний з інформаційним входом регістра 5 попереднього рівня й першим входом компаратора 7, інформаційний вихід регістра 5 підключений до першого входу мультиплексора 11 і другого входу компаратора 7, а вихід "Меньше нуля" регістра 5 з'єднаний зі стробувальним входом цього ж регістра та регістра 4 поточного рівня Вихід компаратора 7 з'єднаний із ЕОМ та із входом скидання тригера 12, суматора 10 і лічильника 9, вихід якого зв'язаний із третім входом мультиплексора 11 Інформаційний вихід лічильника 8 поточного часу підключений до першого входу суматора 10, вихід якого з'єднаний із другим входом цього ж суматора 10 і другим входом мультиплексора 11, а вихід "Равно нулю" лічильника 8 з'єднаний з першим стробувальним входом регістра 3 Настановний вхід тригера 12, входи " - 1 " регістра 5 попереднього рівня й лічильника 8 поточного часу, керуючий вхід та інформаційний вихід мультиплексора 11 підключені до ЕОМ Вихід тригера 12 зв'язаний із входом генератора 13 імпульсів і першим входом елемента 14 "И", вихід генератора 13 імпульсів приєднаний до другого входу елемента 14 "И", вихід якого підключений до стробувальних входів АЦП 1, регістра 2 поточного коду, компаратора 6 і лічильника 8 поточного часу Вихід елемента 15 "ИЛИ" з'єднаний із стробувальними входа 8 ми регістра 4 поточного рівня, компаратора 7, лічильника 9 і суматора 10 Пристрій працює в такий спосіб У вихідний стан пристрій установлюється за сигналами від ЕОМ до лічильника 8 поточного часу й регістра 5 попереднього перетятого рівня заноситься "-1" На настановний вхід тригера 12 надходить сигнал "Пуск" Сигнал з виходу тригера 12 дозволяє запуск генератора 13 і подачу через елемент 14 "И" синхроімпульсів з виходу генератора на стробувальні входи АЦП 1 і регістра поточного коду 2, по яких відбувається перетворення вхідного сигналу, що надходить на вхід АЦП 1, і запис коду з його виходу до регістра 2, а також нарощування лічильника 8 поточного часу Якщо це перший уведений код, тобто після нарощування лічильник 8 виявиться обнуленим, то за сигналом зі спеціального виходу цього лічильника "Равно нулю" поточний код з регістра 2 перепишеться до регістра попереднього коду 3 Якщо вводиться перший код, то в регістрі 5 попереднього перетятого рівня міститься "-1" і сигнал, що свідчить про це, зі спеціального виходу регістра 5 дозволяє перезапис поточного коду з регістра 2 до регістра 4 поточного рівня та з регістра 4 до регістра 5 попереднього рівня За синхроімпульсом з елемента 14 "И", затриманим на час запису до регістрів 2 і 3, здійснюється порівняння кодів з цих регістрів компаратором 6 (від попереднього коду віднімається поточний), і на виході компаратора 6 формується сигнал "Больше", що відповідає зменшенню коду на одиницю й "Меньше", що відповідає збільшенню коду на одиницю порівняно з попереднім Якщо виявлена нерівність кодів, то на виході елемента 15 "ИЛИ" формується сигнал, що дозволяє нарощування числа відхилень у лічильнику 9, підсумовування часу одержання поточного коду з лічильника 8 поточного часу з раніше накопиченою сумою в суматорі 10 і порівняння значень попереднього й поточного перетятих рівнів компаратором 7 При цьому, якщо поточний код менший за попередній, то за сигналом "Больше" з виходу компаратора 6 здійснюється збільшення на одиницю вмісту регістра 4 поточного рівня, тобто в цьому разі вважається, що сигнал має старе цифрове значення й це значення відновлюється в регістрі 4 збільшенням поточного коду на одиницю За сигналом з виходу елемента 15 "ИЛИ" компаратором 7 порівнюються коди з регістра 5 попереднього рівня й регістра 4 поточного рівня Компаратор 7 формує сигнали у випадку розбіжності порівнюваних кодів, що свідчить про те, що вхідний сигнал досяг наступного цифрового рівня та його код збільшився на одиницю За цим сигналом відбувається скидання лічильника 9, суматора 10, тригера 12, внаслідок чого тригер 12 забороняє проходження через елемент 14 "И" імпульсної ПОСЛІДОВНОСТІ з виходу генератора 13 Крім того, сигнал з виходу компаратора 7 сприймається ЕОМ, що формує керуючі імпульси для вибірки інформації мультиплексором На вихід мультиплексора 11 під впливом керуючих сигналів виставляються по черзі коди, що відповідають числу відхилень кодів сигналу від зафіксованого значення цифрового рівня та значенню зафіксованого цифрового рівня Визначення моменту найбільш точного пе 62142 ретворення здійснюється ЕОМ шляхом ділення накопиченої суми часу одержання кодів сигналу, що відхилилися від зафіксованого значення, на число таких відхилень У такий спосіб з ПОСЛІДОВНОСТІ перетворень, у яких коди сигналу були рівні чи менші на одиницю, ніж значення цифрового рівня, перетятого сигналом, буде обрано одне, яке відповідає моменту перетинання вхідного сигналу з даним цифровим рівнем Всі описані дії повторюються після подачі на вхід настановного тригера 12 сигналу "Пуск" від ЕОМ, по якому тригер переходить до одиничного стану й дозволяє проходження імпульсної ПОСЛІДОВНОСТІ з виходу генератора 13 Для реалізації пропонованого способу аналого-цифрового перетворення необхідно виконати ПОСЛІДОВНІСТЬ дій, наведену на блок-схемі (фіг 2) блок 2 - обнуління суматора часу одержання перетворень, ВІДМІННИХ від зафіксованого значення (SI), обнуління лічильника числа відхилень кодів сигналу від зафіксованого значення (J), значення в лічильнику поточного часу (І) і цифрове значення рівня, перетятого сигналом " - 1 " , обнуління коригувальної одиниці Е, блок 3 - уведення коду сигналу КТ, блок 4 - нарощування поточного часу, блок 5 визначення початкового моменту часу (порівняння поточного часу І та "0"), блок 6 - якщо початковий момент часу (уведений 1-ий код), то блок 6 - попередній код (КР) вважає рівним уведеному, інакше блок 7 - порівняння попереднього й поточного кодів якщо коди рівні - перехід на блок 3, якщо попередній код більший за поточний, то блок 8 - завдання коригувальної одиниці, інакше - блок 9 накопичення суми поточного часу (SI), нарощування числа відхилень коду сигналу від зафіксованого значення, присвоєння поточному цифровому значенню сигналу (ИТ) значення з коригувальною одиницею і переприсвоювання поточного коду попередньому, блок 11 - перевірка, чи була зміна цифрового значення сигналу якщо не було (зафіксоване значення дорівнює " - 1 " (менше за "0")), то блок 12 - фіксується цифрове значення сигналу, тобто вважається рівним поточному цифровому значенню, інакше - блок 13 - порівнюються зафіксоване й поточне цифрові значення сигналу якщо вони рівні, то перехід на блок 3, інакше - блок 14 визначення моменту часу найбільш точного перетворення - ділення суми часу одержання перетворень, коди яких ВІДМІННІ від зафіксованого цифрового значення, на число таких кодів (J), перехід на блок 2 Розглянемо приклад конкретної реалізації Як АЦП 1 може бути використана мікросхема К572ПВ1, для включення якої необхідне джерело опорної напруги, операційний підсилювач і генератор тактових імпульсів Регістри поточного коду 2 та попереднього коду 3 можуть бути реалізовані на двох мікросхемах КР580ИР82, при цьому будуть використовуватися 12 молодших розрядів Регістр поточного рівня переходу 4 можна реалізувати на трьох мікросхемах КР1533ИЕ7 (фіг 7) Запис до регістра здійснюється за командою на вході дозволу паралельного завантаження, а збільшення вмісту на одиницю - за позитивним пере 10 падом тактового імпульсу на тактовому вході для лічби на збільшення Для реалізації регістра 5 попереднього рівня переходу можна використовувати дві мікросхеми КР580ИР82, одну мікросхему КР1533ТМ2 й одну мікросхему КР1533ЛАЗ (фіг 8) Одиниця у знаковому розряді заноситься установкою тригера в одиницю, після чого сигнал з виходу тригера надходить на логічний елемент "И-НЕ", що формує імпульс "Разрешение записи" до регістра 5 Для реалізації лічильника поточного часу 8 можна використовувати три мікросхеми КР1533ИЕ7, три мікросхеми К155ЛЕЗ й одну мікросхему КР1533ЛА1 (фіг 9) На виході елемента "И-НЕ" буде сформований імпульс, що свідчить про нульовий стан лічильника Лічильник числа переходів 9 може бути реалізований на базі мікросхеми КР1533ИЕ5 Як суматора 10 можна взяти три мікросхеми К555ИМ7 і три мікросхеми КР1533ИР15 (фіг 10) У початковий момент здійснюється скидання регістра, що відповідає обнулінню суматора Підсумовування здійснюється за імпульсами, що надходять на тактовий вхід суматора Компаратори 6 і 7 можна реалізувати на трьох мікросхемах КР 1533ИПЗ Мультиплексор 11 можна реалізувати на двох мікросхемах К155КП1 та одній мікросхемі КР1533КП11 (фіг 11) Під час вибору інформації процесор подає керуючі сигнали на 16-входовий мультиплексор і ВІДПОВІДНИЙ керуючий сигнал на 2входовий мультиплексор, тобто формується 5розрядний керуючий код Як логічний елемент 15 "ИЛИ" можна взяти мікросхему КР1533ЛЕ1, а як елемент 14 "И" - мікросхему К155ЛЕЗ У вимірювальній і перетворювальній техніці широко застосовуються ШВИДКОДІЮЧІ АЦП в інтегральному виконанні Під час проектування серійних АЦП враховуються основні складові погрішності перетворення За методикою (Аналогоцифровые преобразователи / Под ред Бахтиарова Г Д , - М , 1980 - с 159) потужність статистичної помилки АЦП дорівнює 2 G кв - потужність шуму квантування, Рдоп - потужність додаткових шумів Pflon=±Uh •(и, )2+(0,5сс+0,5кпацп)2, Де Uh - зона гістерезису компаратора, Gcj, - середньоквадратичне відхилення зони невизначеності компаратора, UCMK - напруга зсуву компаратора, Ucc - напруга, обумовлена синфазним сигналом, иСмаЦп - напруга зсуву АЦП, иКПацп - зміна коефіцієнта передачі АЦП Втрати у відношенні сигнал/шум визначаються за відношенням Т^ідсиУ-з кв Величину Pflon-G2KB розглядають як верхню границю припустимої статистичної погрішності Збільшення Рдоп означає фактично втрату молодшого розряду й перехід від m-розрядного АЦП до (т-і)-розрядного ВІДОМІ структурні методи поліпшення характе 62142 12 11 ристик АЦП (Моисеев В С Системное проектироний спосіб аналого-цифрового перетворення знивание преобразователей информации -Л , 1982 жує величину GKB, забезпечує більш точне предс 105), що дозволяє зменшити помилку перетвоставлення корисного сигналу та сигналурення Наступне за аналого-цифровим перетвоперешкоди, що підвищує точність подальшого старенням статистичне вирівнювання інформації дотистичного опрацювання даних зволяє зменшити шумову та динамічну складові Нехай ДІІд - поточна погрішність дискретизації, помилки, а також величини Uh, і Єф Автоматична а ДІІду - поточна погрішність дискретизації після компенсація статистичної погрішності з викорисзастосування пропонованого способу аналоготанням зразкових сигналів дозволяє зменшити цифрового перетворення Тоді ВеЛИЧИНИ UcMK, ІІсмацп, UCc, ІІкпацп ВиріВНЮВаННЯ ТЭ компенсація ведуть до зменшення потужності додаткових шумів, і, отже, зменшуються втрати у відношенні сигнал/шум 1 Для підвищення точності перетворення потрібно зменшити потужність шуму квантування G№, але серійний АЦП має фіксоване число розрядів, обране з вищенаведених співвідношень, і змінити його ми не можемо При статистичному вирівнюванні середньоквадратична помилка GKB, викликана обмеженою розрядністю інформації, приводить до зсуву статистичних оцінок і збільшення, погрішності результату (Гитис Э И , Пискунов Е А Аналого-цифровые преобразователи - М , 1981 - с 770) Пропонова ФІГ. І о < диду < дид При лінійному законі зміни приведеного до входу сигналу д и д у = / d / d t / d = AU A /L, Де d=Ta - період дискретизації, L - число інтервалів Та, що розміщаються в інтервалі [t n ' + 1, t n " + i] З наведених співвідношень видно, що, чим менший інтервал перетворення й модуль похідної вхідного сигналу, тим менша погрішність результату 13 62142 14 15 62142 16 17 Комп'ютерна верстка А Ярославцева 62142 Підписне 18 Тираж39 прим Міністерство освіти і науки України Державний департамент інтелектуальної власності, Львівська площа, 8, м Київ, МСП, 04655, Україна ДП "Український інститут промислової власності", вул Сім'ї Хохлових, 15, м Київ, 04119

ДивитисяДодаткова інформація

Назва патенту англійськоюMethod of signal analog-to-digital conversion and the device for the realization of the method

Автори англійськоюMaschenko Serhii Valeriovych

Назва патенту російськоюСпособ аналого-цифрового преобразования сигнала и устройство для осуществления способа

Автори російськоюМащенко Сергей Валерьевич

МПК / Мітки

МПК: G06F 3/05

Мітки: реалізації, перетворення, пристрій, аналого-цифрового, спосіб

Код посилання

<a href="https://ua.patents.su/9-62142-sposib-analogo-cifrovogo-peretvorennya-ta-pristrijj-dlya-jjogo-realizaci.html" target="_blank" rel="follow" title="База патентів України">Спосіб аналого-цифрового перетворення та пристрій для його реалізації</a>

Попередній патент: Спосіб одержання 2,3,4,5-тетрафторбензоїлфториду та 2,3,4,5-тетрафторбензотрифториду

Наступний патент: Затискний патрон

Випадковий патент: Дискретний дренаж за підпірною стінкою