Аналого-цифровий перетворювач

Формула / Реферат

Аналого-цифровий перетворювач, який містить конденсаторну матрицю, схему порівняння, ключовий елемент, блок маскування, регістр послідовного наближення, дешифратор, лічильник калібрувань та лічильник адрес, блок оперативної та блок постійної пам'яті, перший мультиплексор, блок додавання, вихідний регістр, блок керування, шини вхідного аналогового сигналу, опорної напруги, нульового потенціалу, керуючих сигналів, сигналу станів, вихідну аналогову та вихідну цифрову, причому вхідну аналогову шину з'єднано з першим входом основної конденсаторної матриці, другий та третій входи якої з'єднано з шиною опорної напруги та відповідним виходом шини керуючих сигналів, а вихід якої з'єднано з вихідною аналоговою шиною, яку в свою чергу з'єднано з інверсним входом схеми порівняння та першим входом ключового елемента, другий вхід якого підключено до відповідного виходу шини керуючих сигналів блока керування, прямий вхід схеми порівняння з'єднано з шиною нульового потенціалу, а вихід схеми порівняння з'єднано з виходом ключового елемента, першим входом блока маскування, першим входом основного регістра послідовного наближення, другий і третій входи основного регістра послідовного наближення з'єднані з виходом дешифратора та відповідними виходами шини керуючих сигналів, другий вихід основного регістра послідовного наближення з'єднано з відповідними входами шини сигналів стану, вхід лічильника калібрування з'єднано з відповідними виходами шини керуючих сигналів, вхід лічильника адрес також з'єднано з відповідними виходами шини керуючих сигналів, керуючі входи блока постійної пам'яті та блока оперативної пам'яті з'єднано з відповідними виходами шини керуючих сигналів, вихід блока постійної пам'яті з'єднано з першим входом першого мультиплексора, другий вхід якого з'єднано з виходом вихідного регістра, а керуючий вхід з відповідними виходами шини керуючих сигналів, вихід першого мультиплексора з'єднано з інформаційним входом блока оперативної пам'яті, вихід якого з'єднано з другим входом блока маскування, вихід якого з'єднано з першим входом блока додавання, другий вхід якого з'єднано з виходом вихідного регістра, а вихід блока додавання з'єднано з інформаційним входом вихідного регістра, керуючий вхід якого з'єднано з відповідними виходами шини керуючих сигналів, вихід вихідного регістра також з'єднано з вихідною цифровою шиною перетворювача, який відрізняється тим, що в нього введено другий і третій мультиплексор, регістр згортки-розгортки, обчислювальний пристрій та тригер знака, причому вихід лічильника адрес підключено до входу дешифратора та першого входу другого мультиплексора, до другого входу якого підключено вихід лічильника калібрувань, а до третього входу другого мультиплексора підключено відповідний вихід шини керування, вихід другого мультиплексора підключено до адресних входів блоків постійної і оперативної пам'яті, до четвертого входу першого мультиплексора підключено вихід обчислювального пристрою, перший вхід якого підключено до відповідного виходу шини керування, а другий вхід обчислювального пристрою підключено до виходу блока оперативної пам'яті, перший вихід основного регістра послідовного наближення підключено до першого входу третього мультиплексора, до другого входу якого підключено вихід регістра згортки-розгортки, вхід якого підключено до відповідного виходу шини керування, до третього входу третього мультиплексора підключено відповідний вихід шини керування, а вихід третього мультиплексора підключено до четвертого входу основної конденсаторної матриці, перший вхід тригера знака підключено до виходу схеми порівняння, другий вхід тригера знака підключено до відповідного виходу шини керування, а вихід підключено до другого, знакового входу вихідного регістра.

Текст

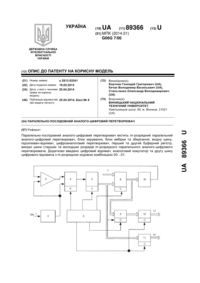

Реферат: Аналого-цифровий перетворювач належить до цифрової вимірювальної і обчислювальної техніки та може бути використано для перетворення аналогових величин в цифрові. До відомого пристрою було введено другий і третій мультиплексори, регістр згортки-розгортки, обчислювальний пристрій та регістр знака, причому вихід лічильника адрес підключено до входу дешифратора та першого входу другого мультиплексора, до другого входу якого підключено вихід лічильника калібрувань, а до третього входу другого мультиплексора підключено відповідний вихід шини керування, вихід другого мультиплексора підключено до адресних входів блоків постійної і оперативної пам'яті, до четвертого входу першого мультиплексора підключено вихід обчислювального пристрою, перший вхід якого підключено до відповідного виходу шини керування, а другий вхід обчислювального пристрою підключено до виходу блока оперативної пам'яті, перший вихід основного регістра послідовного наближення підключено до першого входу третього мультиплексора, до другого входу якого підключено вихід регістра згортки-розгортки, вхід якого підключено до відповідного виходу шини керування, до третього входу третього мультиплексора підключено відповідний вихід шини керування, а вихід третього мультиплексора підключено до четвертого входу основної конденсаторної матриці, перший вхід тригера знака підключено до виходу схеми порівняння, другий вхід тригера знака підключено до відповідного виходу шини керування, а вихід підключено до другого, знакового входу вихідного регістра. Технічним результатом є підвищення точності перетворювача за рахунок того, що вдалось суттєво зменшити методичну похибку цифрового калібрування. UA 108294 C2 (12) UA 108294 C2 UA 108294 C2 5 10 15 Винахід належить до галузі цифрової вимірювальної і обчислювальної техніки і може бути використаний для перетворення аналогових величин в цифрові. Відомий спосіб аналого-цифрового перетворення та пристрій на його основі (McCreary J.L., Gray P.R. All-MOS charge redistribution analog-to-digital conversion techniques-Part 1 // IEEE J. Solid-State Circuits.-1975. - Vol.10. -P.371-379.,) заснований на використанні процесу перерозподілу заряду між конденсаторами двійково-зваженої конденсаторної матриці, в процесі якого формується вихідний код. Перетворення здійснюється послідовно в три етапи: дискретизації, перехідної фази та врівноваження. На етапі дискретизації верхні обкладинки конденсаторної матриці замкнені на шину нульового потенціалу, а на нижні обкладинки подається вхідна напруга Uвх . На етапі перехідної фази верхні обкладинки конденсаторної матриці від'єднуються від шини нульового потенціалу, а нижні під'єднуються до неї, що призводить до формування на верхніх обкладинках матриці, які підключено до входу схеми порівняння, напруги - Uвх . Далі виконується операція врівноваження, яка полягає в покроковому під'єднанні до нижніх обкладинок конденсаторів матриці починаючи з конденсатора найбільшої ємності джерела опорної напруги. На першому кроці врівноваження схема є дільником напруги між двома конденсаторами однакової ємності - "старшим" конденсатором матриці та конденсатором, що утворюється рештою конденсаторів матриці. Таким чином, напруга U х на вході схеми порівняння дорівнюватиме Uх Uвх Uоп / 2 . 20 Схема порівняння визначає знак напруги U х і формує відповідний розряд вихідного коду. У випадку, коли Uх 0 (Uвх Uоп / 2) старший двійковий розряд встановлюється в "1". У випадку Uх 0 (Uвх Uоп / 2) , 25 старший двійковий розряд встановлюється в "0", а нижня обкладинка відповідного конденсатора комутується на шину нульового потенціалу. Аналогічно визначаються значення інших розрядів, які є результатами перетворення. На етапі визначення останнього (наймолодшого) розряду вхідна напруга компаратора дорівнюватиме U x Uвх bn 1 30 35 40 45 50 Uоп U U U bn 2 оп ... b1 оп оп n 1 4 4 2 2n , де bi {0,1} - розрядні коефіцієнти, отримані на попередніх тактах врівноваження. Відомий пристрій аналого-цифрового перетворення містить конденсаторну матрицю, що складається з n двійково-зважених конденсаторів та додаткового (n 1) -го конденсатора, номінал якого збігається з номіналом конденсатора матриці найменшої ємності, (n 1) ключових елементів для комутації відповідних конденсаторів, (n 2) -й та (n 3) -й ключовий елемент, шину для підключення джерела опорної напруги, аналогову вхідну шину, схему порівняння, блок керування та пам'яті, шину тактового генератора, вихідну цифрову шину, причому верхні обкладинки всіх конденсаторів матриці підключено до першого (прямого) входу схеми порівняння та (n 2) -го ключового елемента, який комутує шину нульового потенціалу, нижні обкладинки з 1-го по (n 1) -й конденсатор підключено до відповідних двопозиційних комутуючих елементів з 1-го по (n 1) -й, які в одній позиції комутуються на шину нульового потенціалу, а в іншій - на (n 3) -й комутуючий елемент, який в одній позиції комутується на аналогову вхідну шину, а в іншій - на шину для підключення джерела опорної напруги, другий (інверсний) вхід схеми порівняння підключено до шини нульового потенціалу, а вихід до першого входу блока керування та пам'яті, на другий вхід якого підключено шину тактового генератора, перші (n 1) виходів цього блока підключено до керуючих входів комутуючих елементів з 1-го по (n 1) , (n 2) -й та (n 3) -й виходи відповідно до керуючих входів (n 2) -го та (n 3) -го комутуючих елементів, останні n виходів підключено до вихідної цифрової шини. Недоліками цього способу та пристрою є низька точність, обумовлена похибками виготовлення інтегральних конденсаторів та низька параметрична надійність перетворення, що призводить до зниження точності при змінені умов навколишнього середовища, зокрема температури. За прототип вибрано спосіб та пристрій аналого-цифрового перетворення (Патент України №94779, бюл. № 11, 2011 p.). 1 UA 108294 C2 5 10 15 20 25 30 35 40 45 50 55 60 Спосіб аналого-цифрового перетворення, який базується на застосуванні процесу перерозподілу заряду на конденсаторній матриці і складається з двох етапів: етапу калібрування старших, неточних розрядів перетворювача і етапу безпосереднього перетворення, причому процедуру калібрування здійснюють виключно в цифровій формі, для чого на вхід конденсатора, що калібрують, подають опорну напругу, далі відповідний заряд перерозподіляють на конденсаторах основної і додаткової конденсаторних матриць, в процесі чого розраховують двійковий еквівалент ваги розряду, що калібрують, і записують в оперативну пам'ять, згадану процедуру виконують для всіх старших неточних розрядів, на етапі основного перетворення вхідну напругу подають на основну конденсаторну матрицю, після чого відповідний заряд перерозподіляють на конденсаторах матриці, в процесі чого визначають двійковий еквівалент вхідного сигналу шляхом додавання ваг точних та відкаліброваних неточних розрядів. Пристрій містить основну та додаткову конденсаторні матриці, схему порівняння, ключовий елемент, блок маскування, основний та додатковий регістри послідовного наближення, дешифратор, лічильник калібрувань та лічильник адрес, блок оперативної та блок постійної пам'яті, мультиплексор, блок додавання, вихідний регістр, блок керування, шини вхідного аналогового сигналу, опорної напруги, нульового потенціалу, керуючих сигналів, сигналу станів, вихідну аналогову та вихідну цифрову, причому вхідну аналогову шину з'єднано з першим входом основної конденсаторної матриці, другий та третій вхід якої з'єднано з шиною опорної напруги та відповідним виходом шини керуючих сигналів, а вихід якої з'єднано з вихідною аналоговою шиною, яку в свою чергу з'єднано з інверсним входом схеми порівняння та першим входом ключового елемента, другий вхід якого підключено до відповідного виходу шини керуючих сигналів блока керування, прямий вхід схеми порівняння з'єднано з шиною нульового потенціалу, а вихід з'єднано з виходом ключового елемента, першим входом блока маскування, першими входами основного та додаткового регістрів послідовного наближення, другий і третій входи основного регістра послідовного наближення з'єднані з виходом дешифратора та відповідними виходами шини керуючих сигналів, перший вихід основного регістра послідовного наближення з'єднано з четвертим входом основної конденсаторної матриці, а другий вихід з'єднано з відповідними входами шини сигналів стану, перший вихід додаткового регістра послідовного наближення з'єднано з першим входом додаткової конденсаторної матриці, другий вхід якої з'єднано з шиною опорної напруги, а вихід з вихідною аналоговою шиною, другий вхід додаткового регістра послідовного наближення з'єднано з відповідними виходами шини керуючих сигналів, а другий вихід з відповідним входам шини сигналів стану, вихід лічильника калібрування з'єднано зі входом дешифратора та першим входом лічильника адрес, а вхід з'єднано з відповідними виходами шини керуючих сигналів, другий вхід лічильника адрес також з'єднано з відповідними виходами шини керуючих сигналів, а вихід з адресними входами блока постійної пам'яті та блока оперативної пам'яті, керуючі входи яких з'єднано з відповідними виходами шини керуючих сигналів, вихід блока постійної пам'яті з'єднано з першим входом мультиплексору, другий вхід якого з'єднано з виходом вихідного регістра, а керуючий вхід з відповідними виходами шини керуючих сигналів, вихід мультиплексоруа з'єднано з інформаційним входом блока оперативної пам'яті, вихід якого з'єднано з другим входом блока маскування, а вихід з першим входом блока додавання, другий вхід якого з'єднано з виходом вихідного регістра, а вихід з'єднано з інформаційним входом вихідного регістра, керуючий вхід якого з'єднано з відповідними виходами шини керуючих сигналів, вихід вихідного регістра також з'єднано з вихідною цифровою шиною перетворювача. Недоліком способу та пристрою є низька точність, обумовлена застосуванням схеми калібрування за стратегією знизу-догори (ваги старших "неточних" розрядів визначаються на основі попередньо визначених ваг молодших "неточних" розрядів), що призводить до накопичення методичної похибки в процесі калібрування. В основу винаходу поставлена задача створення способу аналого-цифрового перетворення, що базується на використанні вагової надлишковості, і в якому змінення операції самокалібрування дає можливість суттєво зменшити похибку калібрування ваг старших "неточних" розрядів і як наслідок підвищити точність пристрою в цілому. В основу винаходу поставлено задачу створення аналого-цифрового перетворювача, в якому за рахунок введення нових блоків і зв'язків між ними досягається зменшення методичної похибки калібрування ваг розрядів, що дасть змогу підвищити точність пристрою. Поставлена задача вирішується тим, що в способі аналого-цифрового перетворення, який базується на застосуванні процесу перерозподілу заряду на конденсаторній матриці і складається з двох етапів: етапу калібрування старших, неточних розрядів перетворювача і етапу безпосереднього перетворення, причому процедуру калібрування здійснюють виключно в 2 UA 108294 C2 5 10 15 20 25 30 35 40 45 50 55 60 цифровій формі, в процесі якої визначають двійкові еквіваленти ваг всіх старших неточних розрядів, і записують в оперативну пам'ять, а на етапі основного перетворення вхідну напругу подають на основну конденсаторну матрицю, після чого відповідний заряд перерозподіляють на конденсаторах матриці, в процесі чого визначають двійковий еквівалент вхідного сигналу шляхом додавання ваг точних та відкаліброваних неточних розрядів, причому в процесі калібрування опорну напругу подають на вхід конденсатора, що відповідає одному зі старших неточних розрядів, далі відповідний заряд перерозподіляють на конденсаторах, що відповідають іншим неточним розрядам, а залишковий заряд перерозподіляють на конденсаторах, що відповідають молодшим, точним розрядам, визначаючи таким чином сумарну похибку групи старших розрядів, процедура повторюється для різних груп старших розрядів після чого на основі отриманих значень розраховуються двійкові еквіваленти ваг неточних розрядів. Поставлена задача вирішується тим, що в аналого-цифровий перетворювач, який містить основну конденсаторну матрицю, схему порівняння, ключовий елемент, блок маскування, основний регістр послідовного наближення, дешифратор, лічильник калібрувань та лічильник адрес, блок оперативної та блок постійної пам'яті, мультиплексор, блок додавання, вихідний регістр, блок керування, шини вхідного аналогового сигналу, опорної напруги, нульового потенціалу, керуючих сигналів, сигналу станів, вихідну аналогову та вихідну цифрову, причому вхідну аналогову шину з'єднано з першим входом основної конденсаторної матриці, другий та третій вхід якої з'єднано з шиною опорної напруги та відповідним виходом шини керуючих сигналів, а вихід якої з'єднано з вихідною аналоговою шиною, яку в свою чергу з'єднано з інверсним входом схеми порівняння та першим входом ключового елемента, другий вхід якого підключено до відповідного виходу шини керуючих сигналів блока керування, прямий вхід схеми порівняння з'єднано з шиною нульового потенціалу, а вихід з'єднано з виходом ключового елемента, першим входом блока маскування, першим входами основного регістра послідовного наближення, другий і третій входи основного регістра послідовного наближення з'єднані з виходом дешифратора та відповідними виходами шини керуючих сигналів, другий вихід основного регістра послідовного наближення з'єднано з відповідними входами шини сигналів стану, вхід лічильника калібрування з'єднано з відповідними виходами шини керуючих сигналів, вхід лічильника адрес також з'єднано з відповідними виходами шини керуючих сигналів, керуючі входи блока постійної пам'яті та блока оперативної пам'яті з'єднано з відповідними виходами шини керуючих сигналів, вихід блоку постійної пам'яті з'єднано з першим входом мультиплексора, другий вхід якого з'єднано з виходом вихідного регістра, а керуючий вхід з відповідними виходами шини керуючих сигналів, вихід мультиплексора з'єднано з інформаційним входом блока оперативної пам'яті, вихід якого з'єднано з другим входом блока маскування, вихід якого з'єднано з першим входом блока додавання, другий вхід якого з'єднано з виходом вихідного регістра, а вихід з'єднано з інформаційним входом вихідного регістра, керуючий вхід якого з'єднано з відповідними виходами шини керуючих сигналів, вихід вихідного регістра також з'єднано з вихідною цифровою шиною перетворювача, введено, другий і третій мультиплексор, регістр згортки-розгортки, обчислювальний пристрій та регістр знака, причому вихід лічильника адрес підключено до входу дешифратора та першого входу другого мультиплексора, до другого входу якого підключено вихід лічильника калібрувань, а до третього входу відповідний вихід шини керування, вихід другого мультиплексора підключено до адресних входів блоків постійної і оперативної пам'яті, до четвертого входу мультиплексора підключено вихід обчислювального пристрою, перший вхід якого підключено до відповідного виходу шини керування, а другий до виходу блока оперативної пам'яті, перший вихід основного регістра послідовного наближення підключено до першого входу третього мультиплексора, до другого входу якого підключено вихід регістра згортки-розгортки, вхід якого підключено до відповідного виходу шини керування, до третього входу третього мультиплексора підключено відповідний вихід шини керування, а вихід третього мультиплексора підключено до четвертого входу основної конденсаторної матриці, перший вхід тригера знака підключено до виходу схеми порівняння, другий вхід до відповідного виходу шини керування, а вихід підключено до другого, знакового входу вихідного регістра. Суть винаходу пояснює креслення. Пристрій містить вхідну аналогову шину 18, яку з'єднано з першим входом конденсаторної матриці 9, другий та третій вхід якої з'єднано з шиною опорної напруги 10 та відповідним виходом шини керуючих сигналів 20, а вихід якої з'єднано з вихідною аналоговою шиною 21, яку в свою чергу з'єднано з інверсним входом схеми порівняння 15 та першим входом ключового елемента 12, другий вхід якого підключено до відповідного виходу шини керуючих сигналів 20 блока керування 1, прямий вхід схеми порівняння 15 з'єднано з шиною нульового потенціалу 11, 3 UA 108294 C2 5 10 15 20 25 30 35 40 а вихід з'єднано з виходом ключового елемента 12, першим входом блока маскування 14, першим входом регістра послідовного наближення 8 та першим входом тригера знака 16, другий вхід якого з'єднано з відповідним виходом шини керуючих сигналів 20, другий вхід регістра послідовного наближення 8 з'єднаний з виходом дешифратора 7, а третій вхід регістра послідовного наближення 8 з'єднаний з відповідним виходом шини керуючих сигналів 20, перший вихід регістра послідовного наближення 8 з'єднано з першим входом третього мультиплексора 22, а другий вихід з'єднано з відповідними входами шини сигналів стану 23, вихід лічильника калібрування 6 з'єднано з другим входом другого мультиплексора 24, а вхід з'єднано з відповідними виходами шини керуючих сигналів 20, вхід лічильника адрес 5 також з'єднано з відповідними виходами шини керуючих сигналів 20, а вихід лічильника адрес 5 з'єднано з першим входом другого мультиплексора 24 та входом дешифратора 7, третій вхід другого мультиплексора 24 з'єднано з відповідним виходом шини керуючих сигналів 20, а вихід з адресними входами блока постійної пам'яті 2 та блока оперативної пам'яті 4, керуючі входи яких з'єднано з відповідними виходами шини керуючих сигналів 20, вихід блока постійної пам'яті 2 з'єднано з першим входом першого мультиплексору 3, другий вхід якого з'єднано з виходом вихідного регістра 13, а третій керуючий вхід з відповідними виходами шини керуючих сигналів 20, вихід першого мультиплексора 3 з'єднано з інформаційним входом блока оперативної пам'яті 4, вихід якого з'єднано з другим входом блока маскування 14, а вихід з першим входом блока додавання 17, другий вхід якого з'єднано з виходом вихідного регістра 13, а вихід з'єднано з першим інформаційним входом вихідного регістра 13, другий знаковий вхід якого з'єднано з виходом тригера знака 16, керуючий вхід вихідного регістра 13 з'єднано з відповідними виходами шини керуючих сигналів 20, вихід вихідного регістра 13 також з'єднано з вихідною цифровою шиною перетворювача 19, перший та другий входи обчислювального пристрою 25 з'єднано з виходом блока оперативної пам'яті 4 та відповідним виходом шини керуючих сигналів 20, а вихід обчислювального пристрою 25 з'єднано з четвертим входом першого мультиплексора 3, вхід регістра згортки-розгортки 26 з'єднано з відповідним виходом шини керуючих сигналів 20, а вихід з другим входом третього мультиплексора 22, третій вхід якого з'єднано з відповідним виходом шини керуючих сигналів 20, а вихід з четвертим входом конденсаторної матриці 9. Спосіб аналого-цифрового перетворення реалізується таким чином. Розрядна сітка перетворювача розбивається на групи з m "неточних" (старших) та (n-m) "точних" (молодших), визначені ваги (n-m) точних розрядів фіксуються в блоці постійної пам'яті 2 на етапі виготовлення перетворювача. Організація роботи передбачається у двох режимах: самокалібрування і основного перетворення, причому перший передує другому. У режимі самокалібрування визначаються ваги "неточних" розрядів. Ця процедура здійснюється таким чином. На конденсатор конденсаторної матриці 9, який відповідає "неточному" розряду, подається опорна напруга з шини опорної напруги 10, після чого відповідний заряд перерозподіляється між конденсаторами молодших "неточних" розрядів, що утворюють з даним розрядом рекурентне співвідношення. Залишковий, неврівноважений заряд, який обумовлений відхиленнями "неточних" розрядів, перерозподіляється між конденсаторами, що відповідають молодшими, "точним" розрядам. Тобто фактично за допомогою молодших, "точних" розрядів вимірюється сумарне відхилення групи старших "неточних" розрядів, що утворюють рекурентне співвідношення. У випадку α=1,618 при калібруванні старшого "неточного" розряду справедливим буде вираз: (Qn 1 Qn 1) (Qn 2 Qn 2 ) (Qn 3 Qn 3 ) 45 n m 1 iK i i 0 , де Qn 1 , Qn 2 , Qn 3 - абсолютні значення відхилень ваг (n 1) -го, (n 2) -го та (n-3)-го розрядів відповідно, i {0,1} - двійкова цифра в i-ому розряді коду, отриманому при калібруванні (n 1) -го розряду, Ki - цифровий еквівалент і-го точного розряду. n m 1 iK i yn 1 50 Позначивши результат калібрування (n 1) -го розряду i 0 умовою рекурентності вираз, що описує калібрування набуває вигляду: , та скориставшись Qn 1 Qn 2 Qn 3 yn 1 . Здійснивши аналогічним чином калібрування решти "неточних" розрядів та врахувавши припущення про те, що сума відхилень ваг розрядів дорівнює нулю отримаємо систему рівнянь: 4 UA 108294 C2 Qn 1 Qn 1 Qn 3 Qn 3 Qn 4 0 Qn m 2 0 Qn m 1 0 Qn m 0 0 Qn 2 Qn 3 Qn 4 0 0 0 0 0 0 0 Qn m 2 Qn m 1 Qn m yn m 2 0 5 Qn 2 Qn 2 0 0 0 Qn m 1 Qn m y n m 1 0 0 y n 1 yn2 . Структура лівої частини виразу за виключенням першого рядку залежить від типу рекурентного співвідношення між вагами розрядів. Розв'язок системи рівнянь дозволить розрахувати значення відхилень "неточних" розрядів. У випадку α=1,618 відхилення молодшого (n-m)-го розряду може бути розраховано як m 1 y n i ((i 2) 1) Qn m i 1 (m 2) 1 , де ( j) j -та цифра ряду Фібоначчі з параметром p 1. Підставивши Qn m в відповідне рівняння системи можна Qn m 1 : розрахувати Qn m 1 Qn m yn m1 . Аналогічним чином розраховуються відхилення інших "неточних" 10 ' розрядів. Відкориговане значення і-го "неточного" розряду визначається виразом: Qi Qi Q . Результати розрахунків записуються в блок оперативної пам'яті 4. У режимі основного перетворення вхідний аналоговий сигнал з шини 18 подасться на конденсаторну матрицю 9 після чого здійснюється його перерозподіл. В процесі перерозподілу визначається цифровий еквівалент вхідного аналогового сигналу за формулою K( A вх ) 15 20 25 30 35 40 45 n 1 Qi'bi i0 . Пристрій працює у режимі самокалібрування і основного перетворення. Режим самокалібрування автоматично запускається після включення пристрою, а також може бути ініційований за певних умов, наприклад при зміні температури середовища. Після включення пристрою за командою блока керування 1 з блока постійної пам'яті 2 через перший мультиплексор 3 в блок оперативної пам'яті 4 записуються ідеальні значення ваг розрядів за адресами, що послідовно формуються лічильником адрес 5 і через другий мультиплексор 24 подаються на адресний вхід блока оперативноїпам'яті 4. На даному етапі лічильник калібрувань 6 працює синхронно з лічильником адрес 5, тому наприкінці даного етапу його вміст відповідатиме адресі найстаршого розряду. Цей етап є підготовчим і виконується тільки один раз після включення пристрою. Далі в регістрі згортки-розгортки 26 встановлюється в "1" розряд, що відповідає старшому "неточному" розряду. Код з виходу регістру згортки-розгортки 26 через третій мультиплексом 22 подається на вхід конденсаторної матриці 9. В результаті нижню платівку конденсатора, що відповідає найстаршому "неточному" розряду буде підключено до шини опорної напруги 10, в той же час нижні платівки конденсаторів решти матриці 9 буде скомутовано на шину нульового потенціалу 11, ключовий елемент 12 переведено в замкнутий стан. Внаслідок цього на старшому "неточному" конденсаторі накопичиться заряд відповідно до його ємності. На наступному кроці за командою блока керування 1 в регістрі згортки-розгортки 26 здійснюється операція розгортки з одночасним розмиканням ключового елемента 12. Це приведе до перерозподілу заряду зі старшого "неточного" конденсатора на відповідні молодші "неточні" конденсатори матриці 9. Таким чином, напруга на вихідній аналоговій шині 21 відповідатиме різниці між номіналами старшого "неточного" конденсатора та відповідними молодшими "неточними" конденсаторами. Якщо ця напруга матиме від'ємний знак (номінал старшого "неточного" конденсатора, більший за суму номіналів відповідних молодших "неточних" конденсаторів), то знак фіксується в тригері знака 16 і починається процес визначення різницевої напруги за допомогою "точних" розрядів. Для цього за командою блоку керування 1 здійснюється онулення вмісту вихідного регістру 13 та встановлення в лічильнику адрес 5 адреси ваги старшого "точного" розряду, в результаті чого на виході дешифратору 7 з'являється одиниця в розряді, що відповідає старшому "точному" розряду Далі за допомогою регістра послідовного наближення 8 починаючи з даного розряду, здійснюється процедура врівноваження. На кожному кроці врівноваження значення лічильника адрес 5 зменшуватиметься на "1" та через другий мультиплексор 24 подається на адресний вхід блока оперативної пам'яті 4. Таким чином на другий вхід блока маскування 14 буде подаватись кодовий еквівалент ваги розряду, який в даний момент бере участь у врівноваженні. 5 UA 108294 C2 5 10 15 20 25 30 35 40 45 На перший вхід блока маскування 14 подається сигнал з виходу схеми порівняння 15, який керує додаванням кодового еквівалента даного розряду до вмісту накопичувального регістра, що утворюється блоком додавання 17 і вихідним регістром 13. У випадку, коли різницева напруга має додатній знак (номінал старшого "неточного" конденсатора менший за суму номіналів відповідних молодших "неточних" конденсаторів), він також фіксується в тригері знака 16, а ключовий елемент 12 замикається. Далі за командою блока керування 1 в регістрі згорткирозгортки 26 здійснюється операція згортки з одночасним розмиканням ключового елемента 12. Після цього виконується операція врівноваження аналогічно тому, що було описано вище. По завершенні старший (знаковий) розряд регістра 13 встановлюється в "0" або "1" відповідно до вмісту тригера знака 16. Таким чином по завершенні врівноваження в регістрі 13 буде знаходитись число, що характеризує неузгодженість номіналів конденсаторів старших "неточних" розрядів конденсаторної матриці 9, пов'язаних рекурентним зв'язком. На наступному етапі вміст лічильника калібрувань 6 збільшується на одиницю і через другий мультиплексор 24 подається на адресний вхід блока оперативної пам'яті 4, а вміст регістра 13 через перший мультиплексор 3 потрапляє на інформаційний вхід блока оперативної пам'яті 4. Далі за командою блока керування 1 відповідне значення неузгодженості номіналів старших "неточних" конденсаторів записується в блок оперативної пам'яті 4. На наступному етапі здійснюється зсув на один розряд вправо вмісту регістра згортки-розгортки 26, після чого відбувається визначення розбалансування ваг відхилень для наступної групи "неточних" розрядів конденсаторної матриці 9, пов'язаних рекурентним співвідношенням, і фіксація цього значення в блоці оперативній пам'яті 4. Аналогічним чином визначається розбаланс всіх інших груп "неточних" розрядів. На наступному етапі за допомогою обчислювального пристрою 25 відбувається розрахунок відхилення ваги наймолодшого "неточного" розряду на основі виразу, наведеного в описі методу. Для цього на вхід обчислювального пристрою 25 з блоку оперативної пам'яті 4 послідовно подаються результати розбалансувань окремих груп "неточних" розрядів, визначені на попередньому кроці. По завершенні розрахунку відхилення ваги наймолодшого "неточного" розряду записується в блок оперативної пам'яті 4, а далі на його основі послідовно здійснюється розрахунок відхилень ваг інших "неточних" розрядів. На наступному етапі в обчислювальному пристрої 25 розраховуються і заносяться в блок оперативної пам'яті 4 робочі значення неточних розрядів шляхом додавання до ідеальних значень відповідних відхилень, визначених в процесі калібрування. В режимі основного перетворення вхідна напруга подається на вхідну аналогову шину 18, нижні платівки всіх конденсаторів конденсаторної матриці 9 під'єднуються до вхідної аналогової шини 18, а ключовий елемент 12 переводиться в замкнутий стан, внаслідок чого на конденсаторній матриці 9 накопичується заряд, що відповідає вхідній напрузі. На наступному кроці нижні платівки всіх конденсаторів матриці 9 перемикаються на шину нульового потенціалу 11 одночасно з розмиканням ключового елемента 12, внаслідок чого напруга на вихідній аналоговій шині 21 буде дорівнювати вхідній напрузі з від'ємним знаком. В той же час відбувається ініціалізація цифрової частини перетворювача, яка полягає в очищенні вмісту вихідного регістру 13 та встановлення лічильника адрес 5 в стан, якій відповідає адресі найстаршого розряду. Далі починається безпосередньо процес аналого-цифрового перетворення, під час якого на кожному кроці з блока оперативної пам'яті 4 вибирається цифровий еквівалент відповідного розряду і залежно від значення на виході схеми порівняння 15 додається до вмісту вихідного регістра 13 аналогічно як це відбувалось під час калібрування. По завершенні перетворення у вихідному регістрі 13 формується цифровий еквівалент вхідної напруги, який подається на вихідну цифрову шину 19. ФОРМУЛА ВИНАХОДУ 50 55 60 Аналого-цифровий перетворювач, який містить конденсаторну матрицю, схему порівняння, ключовий елемент, блок маскування, регістр послідовного наближення, дешифратор, лічильник калібрувань та лічильник адрес, блок оперативної та блок постійної пам'яті, перший мультиплексор, блок додавання, вихідний регістр, блок керування, шини вхідного аналогового сигналу, опорної напруги, нульового потенціалу, керуючих сигналів, сигналу станів, вихідну аналогову та вихідну цифрову, причому вхідну аналогову шину з'єднано з першим входом основної конденсаторної матриці, другий та третій входи якої з'єднано з шиною опорної напруги та відповідним виходом шини керуючих сигналів, а вихід якої з'єднано з вихідною аналоговою шиною, яку в свою чергу з'єднано з інверсним входом схеми порівняння та першим входом ключового елемента, другий вхід якого підключено до відповідного виходу шини керуючих сигналів блока керування, прямий вхід схеми порівняння з'єднано з шиною нульового 6 UA 108294 C2 5 10 15 20 25 30 потенціалу, а вихід схеми порівняння з'єднано з виходом ключового елемента, першим входом блока маскування, першим входом основного регістра послідовного наближення, другий і третій входи основного регістра послідовного наближення з'єднані з виходом дешифратора та відповідними виходами шини керуючих сигналів, другий вихід основного регістра послідовного наближення з'єднано з відповідними входами шини сигналів стану, вхід лічильника калібрування з'єднано з відповідними виходами шини керуючих сигналів, вхід лічильника адрес також з'єднано з відповідними виходами шини керуючих сигналів, керуючі входи блока постійної пам'яті та блока оперативної пам'яті з'єднано з відповідними виходами шини керуючих сигналів, вихід блока постійної пам'яті з'єднано з першим входом першого мультиплексора, другий вхід якого з'єднано з виходом вихідного регістра, а керуючий вхід з відповідними виходами шини керуючих сигналів, вихід першого мультиплексора з'єднано з інформаційним входом блока оперативної пам'яті, вихід якого з'єднано з другим входом блока маскування, вихід якого з'єднано з першим входом блока додавання, другий вхід якого з'єднано з виходом вихідного регістра, а вихід блока додавання з'єднано з інформаційним входом вихідного регістра, керуючий вхід якого з'єднано з відповідними виходами шини керуючих сигналів, вихід вихідного регістра також з'єднано з вихідною цифровою шиною перетворювача, який відрізняється тим, що в нього введено другий і третій мультиплексор, регістр згортки-розгортки, обчислювальний пристрій та тригер знака, причому вихід лічильника адрес підключенодо входу дешифратора та першого входу другого мультиплексора, до другого входу якого підключено вихід лічильника калібрувань, а до третього входу другого мультиплексора підключено відповідний вихід шини керування, вихід другого мультиплексора підключено до адресних входів блоків постійної і оперативної пам'яті, до четвертого входу першого мультиплексора підключено вихід обчислювального пристрою, перший вхід якого підключено до відповідного виходу шини керування, а другий вхід обчислювального пристрою підключено до виходу блока оперативної пам'яті, перший вихід основного регістра послідовного наближення підключено до першого входу третього мультиплексора, до другого входу якого підключено вихід регістра згорткирозгортки, вхід якого підключено до відповідного виходу шини керування, до третього входу третього мультиплексора підключено відповідний вихід шини керування, а вихід третього мультиплексора підключено до четвертого входу основної конденсаторної матриці, перший вхід тригера знака підключено до виходу схеми порівняння, другий вхід тригера знака підключено до відповідного виходу шини керування, а вихід підключено до другого, знакового входу вихідного регістра. 7 UA 108294 C2 Комп’ютерна верстка І. Скворцова Державна служба інтелектуальної власності України, вул. Василя Липківського, 45, м. Київ, МСП, 03680, Україна ДП “Український інститут промислової власності”, вул. Глазунова, 1, м. Київ – 42, 01601 8

ДивитисяДодаткова інформація

Автори англійськоюZakharchenko Serhii Mykhailovych

Автори російськоюЗахарченко Сергей Михайлович

МПК / Мітки

МПК: H03M 1/26

Мітки: перетворювач, аналого-цифровий

Код посилання

<a href="https://ua.patents.su/10-108294-analogo-cifrovijj-peretvoryuvach.html" target="_blank" rel="follow" title="База патентів України">Аналого-цифровий перетворювач</a>

Попередній патент: Спосіб лікування генералізованого пародонтиту у стадії загострення

Наступний патент: Пружний елемент

Випадковий патент: Спосіб вирощування посівних томатів