Комп’ютерна система комерційного обліку електроенергії, реєстрації аварійних режимів та проведення безперервної діагностики електричного обладнання тягових підстанцій

Номер патенту: 61758

Опубліковано: 17.11.2003

Автори: Ковзель Микола Олегович, Стасюк Ілона Олександрівна, Гінайло Андрій Вікторович, Сопель Михайло Федорович, Семенова Наталія Володимирівна, Стогній Борис Сергійович, Тутик Володимир Львович, Мартинюк Максим Володимирович

Формула / Реферат

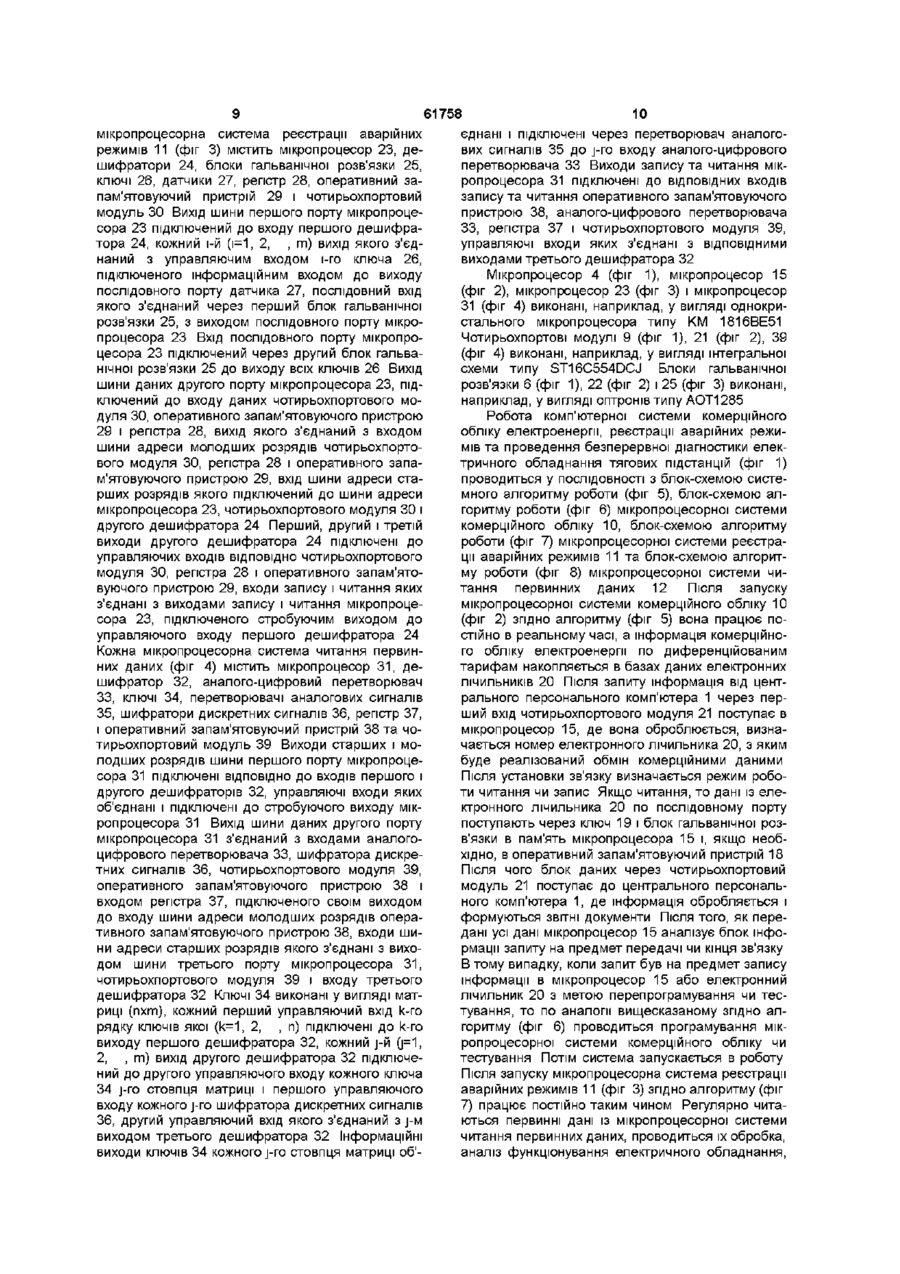

1. Комп'ютерна система комерційного обліку електроенергії, реєстрації аварійних режимів та проведення безперервної діагностики електричного обладнання тягових підстанцій, що включає дешифратор, регістр, блок гальванічної розв'язки, яка відрізняється тим, що її доповнено центральним персональним комп'ютером, мікропроцесорними модулями та модемами, причому кожний мікропроцесорний модуль включає мікропроцесор, дешифратор, блок гальванічної розв'язки, ключі, оперативний запам'ятовуючий пристрій, чотирипортовий модуль, мікропроцесорну систему комерційного обліку, мікропроцесорну систему реєстрації аварійних режимів, мікропроцесорну систему безперервної діагностики і мікропроцесорну систему читання первинних даних, причому вихід шини першого порту мікропроцесора підключений до входу першого дешифратора, кожний k-й (k=1, 2, 3, 4) вихід якого з'єднаний з управляючим входом k-го ключа, вихід послідовного порту мікропроцесора підключений через перший блок гальванічної розв'язки з входом послідовного порту мікропроцесорної системи комерційного обліку, мікропроцесорної системи реєстрації аварійних режимів, мікропроцесорної системи безперервної діагностики і мікропроцесорної системи читання первинних даних, виходи послідовних портів яких підключені через відповідні ключі і другий блок гальванічної розв'язки до входу послідовного порту мікропроцесора, вихід шини даних другого порту мікропроцесора підключений до входу оперативного запам'ятовуючого пристрою, чотирипортового модуля і через регістр до входу шини молодших адрес оперативного запам'ятовуючого пристрою, шини адрес старших розрядів якого з'єднані з виходом третього порту мікропроцесора, входом другого дешифратора і входом адреси чотирипортового модуля, виходи запису та читання мікропроцесора з'єднані з входами запису та читання чотирипортового модуля, мікропроцесорної системи читання первинних даних і оперативного запам'ятовуючого пристрою, управляючі входи яких підключені до відповідних виходів другого дешифратора, управляючий вхід першого дешифратора з'єднаний з стробувальним виходом мікропроцесора, перший вихід чотирипортового модуля кожного j-гo (j=1, 2, ..., n) мікропроцесорного модуля підключений відповідно через перший та другий модеми до j-го входу послідовного порту центрального персонального комп'ютера, а перший і другий виходи послідовних портів мікропроцесорної системи читання первинних даних підключені відповідно до других виходів послідовних портів мікропроцесорної системи реєстрації аварійних режимів і мікропроцесорної системи безперервної діагностики.

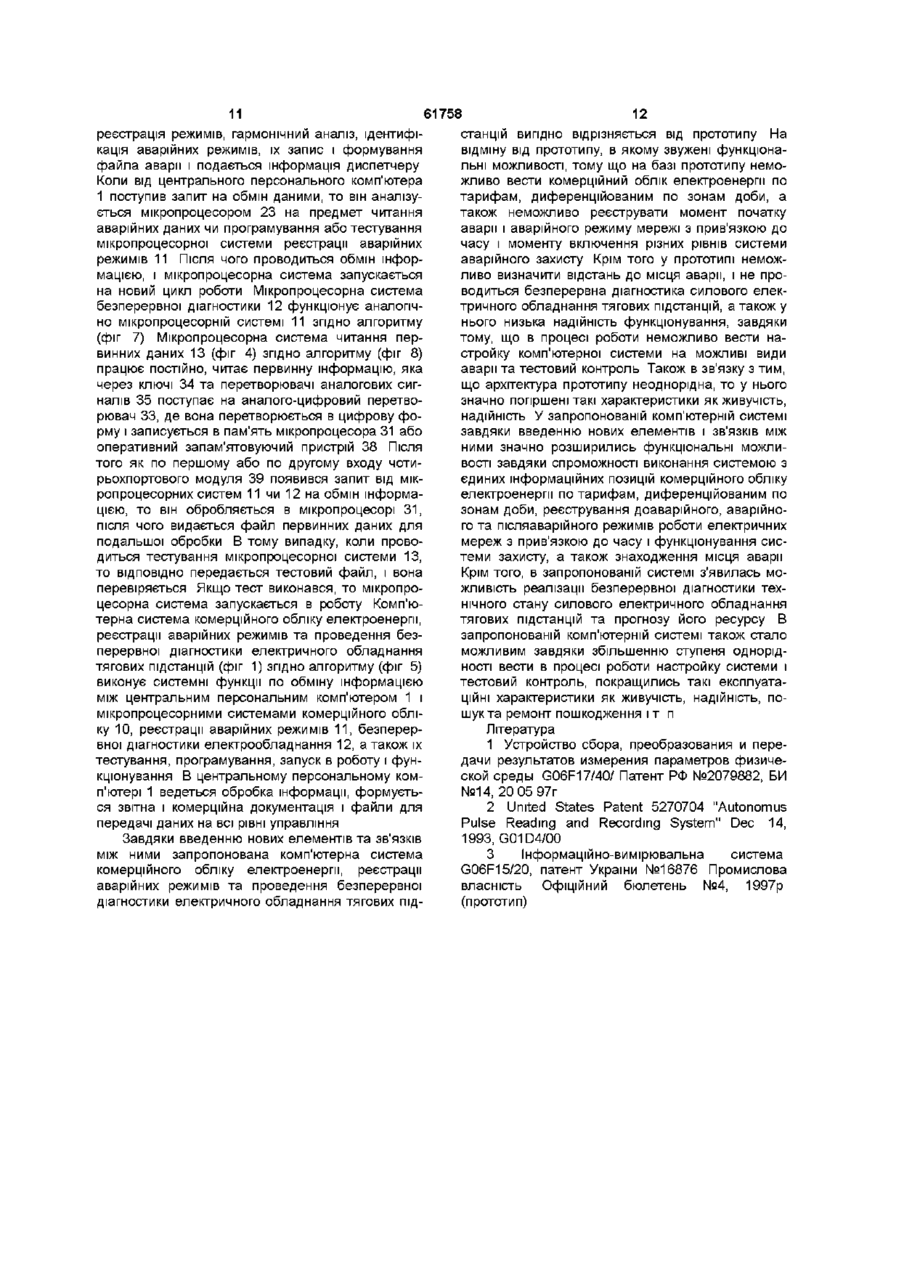

2. Комп'ютерна система за п. 1, яка відрізняється тим, що мікропроцесорна система комерційного обліку містить мікропроцесор, дешифратор, регістр, оперативний запам'ятовуючий пристрій, ключі, електронні лічильники, чотирипортовий модуль і блоки гальванічної розв'язки, причому вихід шини першого порту мікропроцесора підключений до входу дешифратора, кожний k-й (k=1, 2, ..., n) вихід якого з'єднаний з управляючим входом k-го ключа, підключеного інформаційним входом до виходу послідовного порту електронного лічильника, вхід послідовного порту якого підключений через перший блок гальванічної розв'язки з виходом послідовного порту мікропроцесора, вхід послідовного порту якого підключений через другий блок гальванічної розв'язки до інформаційних виходів ключів, вихід шини даних другого порту мікропроцесора підключений до входу даних чотирипортового модуля, оперативного запам'ятовуючого пристрою і регістра, підключеного своїм виходом до входу шини адреси молодших розрядів оперативного запам'ятовуючого пристрою, з'єднаного входами шини адреси старших розрядів з виходом шини адреси мікропроцесора і входом шини адреси чотирипортового модуля, вхідні шини запису і читання якого підключені до відповідного виходу шин запису і читання мікропроцесора і входу шин запису і читання оперативного запам'ятовуючого пристрою, перший стробувальний вихід мікропроцесора з'єднаний з управляючим входом дешифратора (n+1)-й і (n+2)-й виходи якого з'єднані з управляючими входами оперативного запам'ятовуючого пристрою і чотирипортового модуля, а другий стробуючий вихід мікропроцесора підключений до управляючого входу регістра.

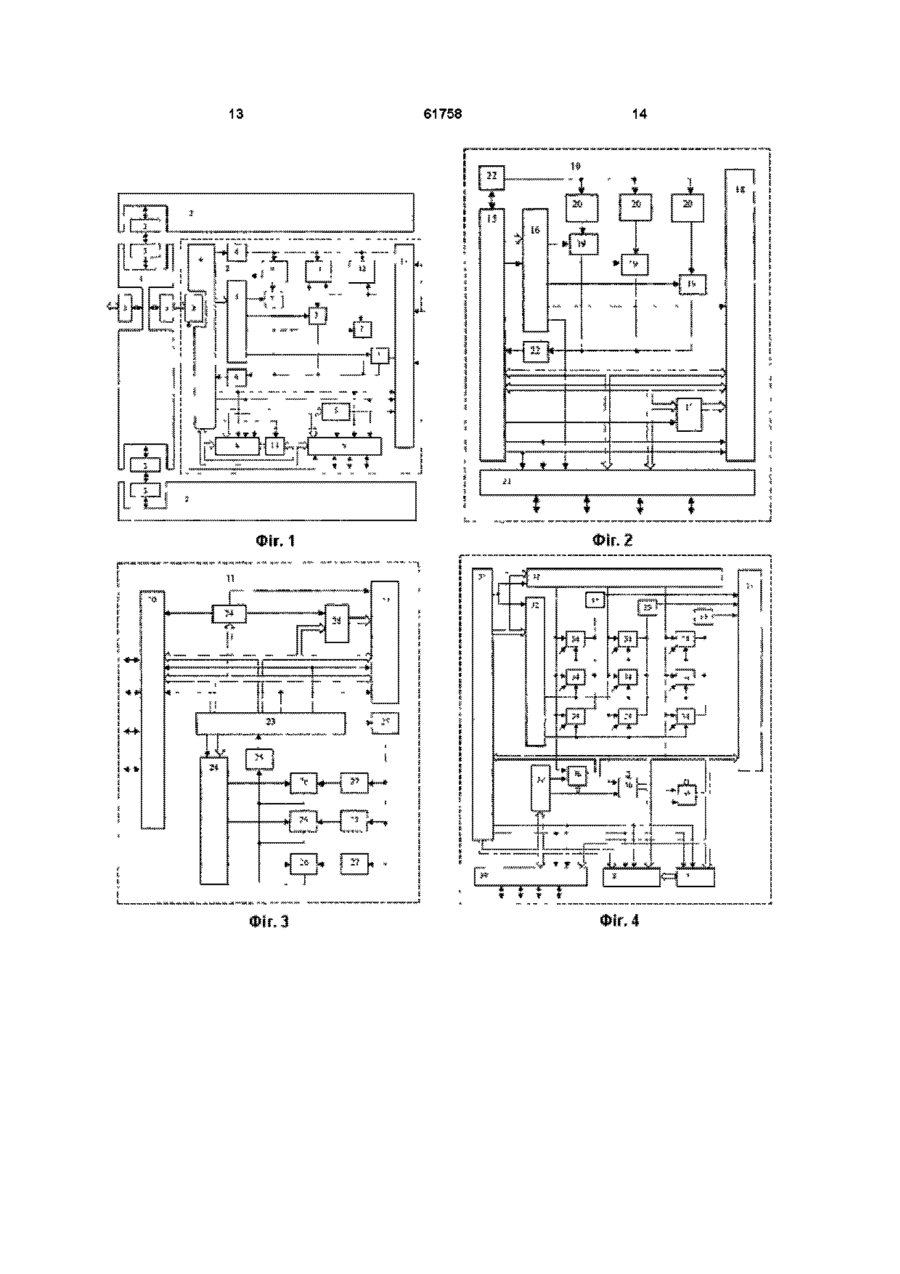

3. Комп'ютерна система за пп. 1, 2, яка відpізняється тим, що мікропроцесорна система реєстрації аварійних режимів містить мікропроцесор, дешифратори, блоки гальванічної розв'язки, ключі, датчики, регістр, оперативний запам'ятовуючий пристрій і чотирипортовий модуль, причому вихід шини першого порту мікропроцесора підключений до входу першого дешифратора, кожний і-й (і=1, 2, ..., m) вихід якого з'єднаний з управляючим входом і-го ключа, підключеного інформаційним входом до виходу послідовного порту датчика, послідовний вхід якого з'єднаний через перший блок гальванічної розв'язки з виходом послідовного порту мікропроцесора, вхід послідовного порту якого підключений через другий блок гальванічної розв'язки до виходів всіх ключів, вихід шини даних другого порту мікропроцесора підключений до входу даних чотирипортового модуля, оперативного запам'ятовуючого пристрою і регістра, вихід якого з'єднаний з входом шини адреси молодших розрядів оперативного запам'ятовуючого пристрою вхід шини адреси старших розрядів якого підключений до шини адреси мікропроцесора, чотирипортового модуля і другого дешифратора, а перший, другий і третій виходи другого дешифратора підключені до управляючих входів відповідно чотирипортового модуля, регістра і оперативного запам'ятовуючого пристрою, входи запису і читання яких з'єднані з виходами запису і читання мікропроцесора, підключеного стробувальним виходом до управляючого входу першого дешифратора.

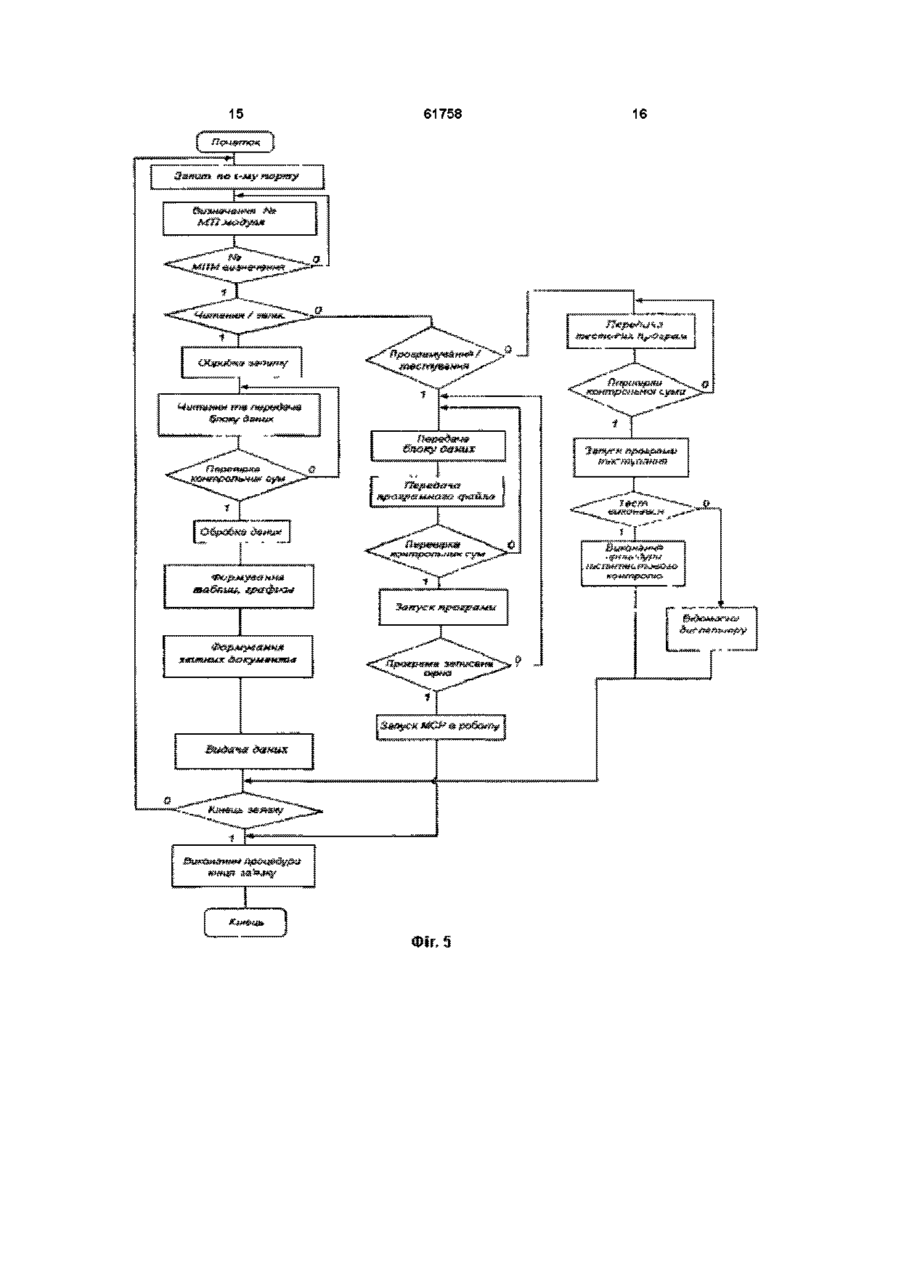

4. Комп'ютерна система за пп. 1, 2, 3, яка відрізняється тим, що мікропроцесорна система читання первинних даних містить мікропроцесор, дешифратори, аналого-цифровий перетворювач, ключі, перетворювачі аналогових сигналів, шифратори дискретних сигналів, регістр, оперативний запам'ятовуючий пристрій та чотирипортовий модуль, причому виходи старших і молодших розрядів шини першого порту мікропроцесора підключені відповідно до входів першого і другого дешифраторів, управляючі входи яких об'єднані і підключені до стробового виходу мікропроцесора вихід шини даних другого порту якого з'єднаний з входами аналого-цифрового перетворювача, шифраторами дискретних сигналів, чотирипортового модуля, оперативного запам'ятовуючого пристрою і входом регістра, підключеного своїм виходом до входу шини адреси молодших розрядів оперативного запам'ятовуючого пристрою входи шини адреси старших розрядів якого з'єднані з виходом шини третього порту мікропроцесора, чотирипортового модуля і входу третього дешифратора, ключі виконані у вигляді матриці (nxm) кожний перший управляючий вхід к-го рядка ключів якої (к=1, 2, ..., n) підключені до к-го виходу першого дешифратора, кожний j-й (j=1, 2, …, m) вихід другого дешифратора, підключений до другого управляючого входу кожного ключа j-гo стовпця матриці і першого управляючого входу кожного j-гo шифратора дискретних сигналів другий управляючий вхід якого з'єднаний з j-м виходом третього дешифратора, інформаційні виходи ключів кожного j-гo стовпця матриці об'єднані і підключені через перетворювач аналогових сигналів до j-гo входу аналого-цифрового перетворювача, а виходи запису та читання мікропроцесора підключені до відповідних входів запису та читання оперативного запам'ятовуючого пристрою, аналого-цифрового перетворювача, регістра і чотирипортового модуля, управляючі входи яких з'єднані з відповідними виходами третього дешифратора.

Текст

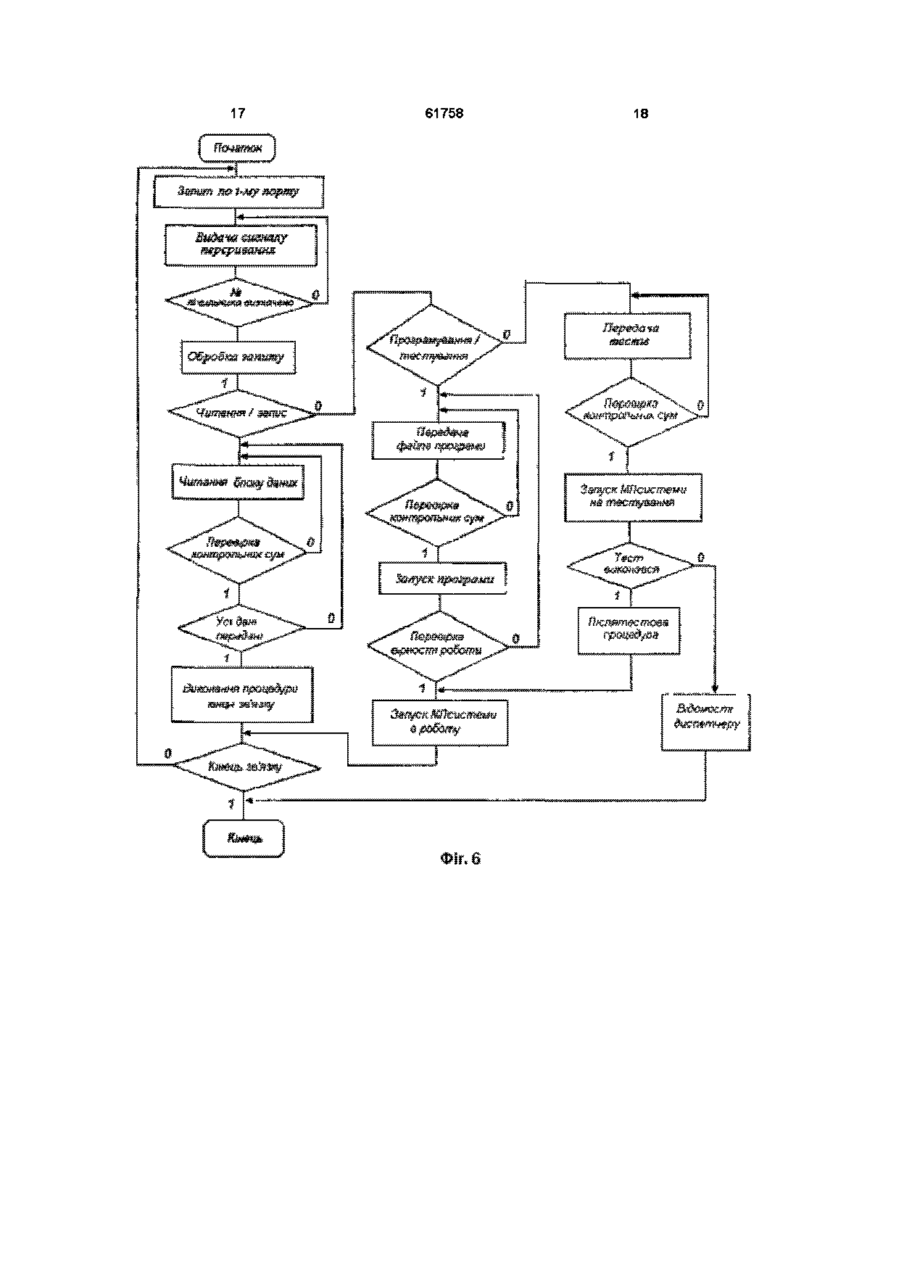

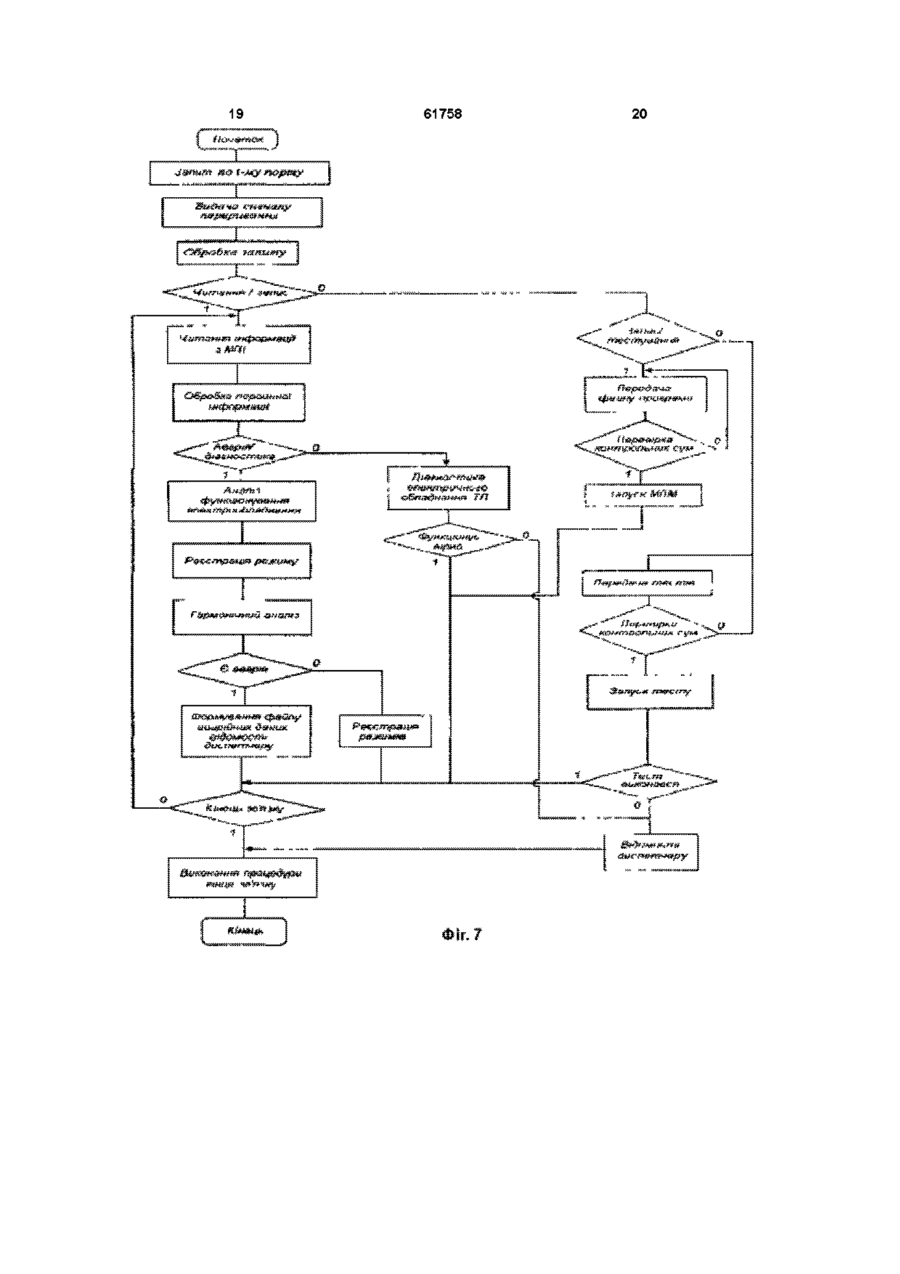

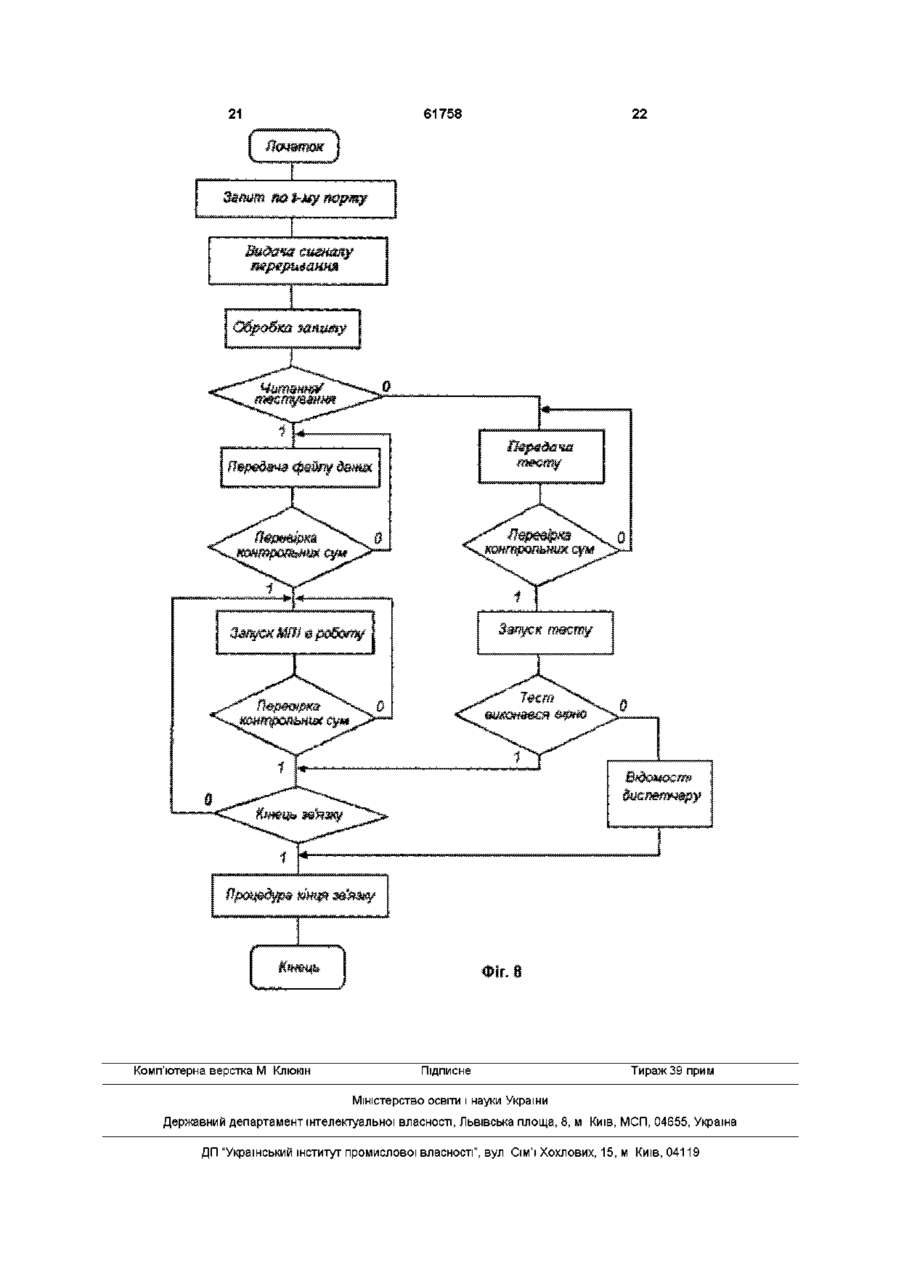

1 Комп'ютерна система комерційного обліку електроенергії, реєстрації аварійних режимів та проведення безперервної діагностики електричного обладнання тягових підстанцій, що включає дешифратор, регістр, блок гальванічної розв'язки, яка відрізняється тим, що и доповнено центральним персональним комп'ютером, мікропроцесорними модулями та модемами, причому кожний мікропроцесорний модуль включає мікропроцесор, дешифратор, блок гальванічної розв'язки, ключі, оперативний запам'ятовуючий пристрій, чотирипортовий модуль, мікропроцесорну систему комерційного обліку, мікропроцесорну систему реєстрації аварійних режимів, мікропроцесорну систему безперервної діагностики і мікропроцесорну систему читання первинних даних, причому вихід шини першого порту мікропроцесора підключений до входу першого дешифратора, кожний k-й (к=1, 2, З, 4) вихід якого з'єднаний з управляючим входом к-го ключа, вихід послідовного порту мікропроцесора підключений через перший блок гальванічної розв'язки з входом послідовного порту мікропроцесорної системи комерційного обліку, мікропроцесорної системи реєстрації аварійних режимів, мікропроцесорної системи безперервної діагностики і мікропроцесорної системи читання первинних даних, виходи послідовних портів яких підключені через ВІДПОВІДНІ ключі і другий блок гальванічної розв'язки до входу послідовного порту мікропроцесора, вихід шини даних другого порту мікропроцесора підключений до входу оперативного запам'ятовуючого пристрою, чотирипортового модуля і через регістр до входу шини молодших адрес оперативного запам'ятовуючого пристрою шини адрес старших розрядів якого з єднані з виходом третього порту мікропроцесора, входом другого дешифратора і входом адреси чотирипортового модуля, виходи запису та читання мікропроцесора з'єднані з входами запису та читання чотирипортового модуля, мікропроцесорної системи читання первинних даних і оперативного запам'ятовуючого пристрою, управляючі входи яких підключені до ВІДПОВІДНИХ виходів другого дешифратора, управляючий вхід першого дешифратора з'єднаний з стробувальним виходом мікропроцесора, перший вихід чотирипортового модуля кожного j-ro (|=1, 2, , п) мікропроцесорного модуля підключений ВІДПОВІДНО через перший та другий модеми floj-ro входу послідовного порту центрального персонального комп'ютера, а перший і другий виходи послідовних портів мікропроцесорної системи читання первинних даних підключені ВІДПОВІДНО до других виходів послідовних портів мікропроцесорної системи реєстрації аварійних режимів і мікропроцесорної системи безперервної діагностики 2 Комп'ютерна система за п 1, яка відрізняється тим, що мікропроцесорна система комерційного обліку містить мікропроцесор, дешифратор, регістр, оперативний запам'ятовуючий пристрій, ключі, електронні лічильники, чотирипортовий модуль і блоки гальванічної розв'язки, причому вихід шини першого порту мікропроцесора підключені до входу дешифратора, кожний k-й (к=1, 2, , п) вихід якого з'єднаний з управляючим входом к-го ключа, підключеного інформаційним входом до виходу послідовного порту електронного лічильника, вхід послідовного порту якого підключений через перший блок гальванічної розв'язки з виходом послідовного порту мікропроцесора, вхід послідовного порту якого підключений через другий блок гальванічної розв'язки до інформаційних виходів ключів, вихід шини даних другого порту мікропроцесора підключений до входу даних чотирипортового модуля, оперативного запам'ятовуючого пристрою і регістра, підключеного своїм виходом до входу шини адреси молодших розрядів оперативного запам'ятовуючого пристрою, з'єднаного входами шини адреси старших розрядів з виходом шини адреси мікропроцесора і входом шини адреси чотирипортового модуля, ВХІДНІ шини запису і 00 ю (О 61758 4 Комп'ютерна система за пп 1, 2, 3, яка відрізчитання якого підключені до ВІДПОВІДНОГО виходу няється тим, що мікропроцесорна система читаншин запису і читання мікропроцесора і входу шин ня первинних даних містить мікропроцесор, дезапису і читання оперативного запам'ятовуючого шифратори, аналого-цифровий перетворювач, пристрою, перший стробувальний вихід мікропроключі, перетворювачі аналогових сигналів, шифцесора з'єднаний з управляючим входом дешифратори дискретних сигналів, регістр, оперативний ратора (п+1)-й і (п+2)-й виходи якого з'єднані з запам'ятовуючий пристрій та чотирипортовий моуправляючими входами оперативного запам'ятодуль, причому виходи старших і молодших розрявуючого пристрою і чотирипортового модуля, а дів шини першого порту мікропроцесора підключедругий стробуючий вихід мікропроцесора підклюні ВІДПОВІДНО до входів першого і другого чений до управляючого входу регістра дешифраторів, управляючі входи яких об'єднані і З Комп'ютерна система за пп 1, 2, яка підключені до стробового виходу мікропроцесора відрізняється тим, що мікропроцесорна система вихід шини даних другого порту якого з'єднаний з реєстрації аварійних режимів містить мікропроцевходами аналого-цифрового перетворювача, шисор, дешифратори, блоки гальванічної розв'язки, фраторами дискретних сигналів, чотирипортового ключі, датчики, регістр, оперативний запам'ятовумодуля, оперативного запам'ятовуючого пристрою ючий пристрій і чотирипортовий модуль, причому і входом регістра, підключеного своїм виходом до вихід шини першого порту мікропроцесора підклювходу шини адреси молодших розрядів оперативчений до входу першого дешифратора, кожний і-й ного запам'ятовуючого пристрою входи шини ад0=1, 2, , т ) вихід якого з'єднаний з управляючим реси старших розрядів якого з'єднані з виходом входом і-го ключа, підключеного інформаційним шини третього порту мікропроцесора, чотирипорвходом до виходу послідовного порту датчика, тового модуля і входу третього дешифратора, послідовний вхід якого з'єднаний через перший ключі виконані у вигляді матриці (nxm) кожний пеблок гальванічної розв'язки з виходом послідовнорший управляючий вхід к-го рядка ключів якої (к=1, го порту мікропроцесора, вхід послідовного порту 2, , п) підключені до к-го виходу першого дешифякого підключений через другий блок гальванічної ратора, кожний j-й 0-1, 2, , т ) вихід другого дерозв'язки до виходів всіх ключів, вихід шини даних шифратора, підключений до другого управляючого другого порту мікропроцесора підключений до входу кожного ключа j-ro стовпця матриці і першовходу даних чотирипортового модуля, оперативго управляючого входу кожного j-ro шифратора ного запам'ятовуючого пристрою і регістра, вихід дискретних сигналів другий управляючий вхід якоякого з'єднаний з входом шини адреси молодших го з'єднаний з j-м виходом третього дешифратора, розрядів оперативного запам'ятовуючого приінформаційні виходи ключів кожного j-ro стовпця строю вхід шини адреси старших розрядів якого матриці об'єднані і підключені через перетворювач підключений до шини адреси мікропроцесора, чоаналогових сигналів до j-ro входу аналоготирипортового модуля і другого дешифратора, а цифрового перетворювача, а виходи запису та перший, другий і третій виходи другого дешифрачитання мікропроцесора підключені до ВІДПОВІДНИХ тора підключені до управляючих входів ВІДПОВІДНО ВХОДІВ запису та читання оперативного запам'яточотирипортового модуля, регістра і оперативного вуючого пристрою, аналого-цифрового перетвозапам'ятовуючого пристрою, входи запису і читанрювача, регістра і чотирипортового модуля, ня яких з'єднані з виходами запису і читання мікуправляючі входи яких з'єднані з ВІДПОВІДНИМИ ропроцесора, підключеного стробувальним виховиходами третього дешифратора дом до управляючого входу першого дешифратора Винахід належить до обчислювальної та вимірювальної техніки і може бути використаний для комерційного обліку електроенергії по тарифам, диференційованим за часом доби, реєстрацію доаварійних, аварійних і після аварійних режимів тягових мереж та знаходження місця пошкодження, а також проведення безперервної діагностики електричного обладнання тягових підстанцій і залишкового ресурсу Відомий пристрій [1] виконуючий функції збору, передачі та перетворення інформації параметрів фізичного середовища, що включає електронну обчислювальну машину, датчики, аналогоцифровий перетворювач, блок дешифрацм, запам'ятовуючий пристрій і блок регістрів, підключених своїми управляючими входами до ВІДПОВІДНИХ ВХОДІВ формувачів інформації, а вихід аналогоцифрового перетворювача підключений до входу запам'ятовуючого пристрою Недоліком відомого пристрою є невисока надійність і обмежені функціональні можливості в зв'язку з тим, що у відомому пристрої проводиться тільки реєстрація параметрів фізичного середовища, а не виконуються функції комерційного обліку електроенергії, реєстрація аварійних режимів, а також не виконується діагностика контролюємого фізичного середовища Відомий пристрій [2] автономного запису та читання, що включає центральний процесор, датчики, комутаційний модуль і автономний запам'ятовуючий пристрій, причому вихід кожного датчика підключений до автономного запам'ятовуючого пристрою, який з'єднаний своїм виходом через комутаційний модуль з центральним процесором У відомому пристрої вимірюєма величина перетворюється в ПОСЛІДОВНІСТЬ імпульсів, КІЛЬКІСТЬ яких пропорційна вимірювальній величині, які накопичуються в запам'ятовуючому пристрої і дані 61758 через ВІДПОВІДНІ ключі і другий блок гальванічної поступають в центральний процесор розв'язки до входу послідовного порту мікропроНедоліком відомого пристрою є обмежені фунцесора, вихід шини даних другого порту мікропрокціональні можливості в зв'язку з тим, що він викоцесора підключений до входу оперативного запанує тільки інформаційно-вимірювальні функції, і м'ятовуючого пристрою, чотирьохпортового зовсім не виконує функції безперервної діагностимодуля і через регістр до входу шини молодших ки, реєстрації аварійних режимів тягових електриадресів оперативного Запам'ятовуючого пристрою чних мереж, а також функції комерційного обліку шини адресів старших розрядів якого з'єднані з електроенергії виходом третього порту мікропроцесора, входом Найбільш близьким за своєю технічною суттєдругого дешифратора і входом адреси чотирьохвістю є інформаційно-вимірювальна система [3], портового модуля, виходи запису та читання мікяка включає лічильник, аналого-цифровий переропроцесора з'єднані з входами запису та читання творювач, регістри, дешифратор, блок гальваніччотирьохпортового модуля, мікропроцесорної сисної розв'язки і електронну обчислювальну машину, теми читання первинних даних і оперативного заінформаційний вихід якої підключений до інфорпам'ятовуючого пристрою, управляючі входи яких маційного входу дешифратора, а вихід аналогопідключені до ВІДПОВІДНИХ виходів другого дешифцифрового перетворювача з'єднаний з інформаратора, управляючий вхід першого дешифратора, ційними входами першого та другого регістрів з'єднаний з стробуючим виходом мікропроцесора, Недоліком даного пристрою є обмежені функперший вихід чотирьохпортового модуля кожного ціональні можливості, низька надійність і рівень j-го Q=1,2, , п) мікропроцесорного модуля піддіагностики в зв'язку з тим, що в відомому пристрої ключені ВІДПОВІДНО через перший та другий модене виконуються з єдиних інформаційних позицій ми до j-ro входу послідовного порту центрального функції комерційного обліку електроенергії по таперсонального комп'ютера, а перший і другий вирифам, диференційованим за часом доби, реєстходи послідовних портів мікропроцесорної системи рації доаварійних, аварійних та післяаварійних читання первинних даних підключені ВІДПОВІДНО ДО режимів роботи електричних мереж і знаходження других виходів послідовних портів мікропроцесормісця аварії з прив'язкою до часу і функціонування ної системи реєстрації аварійних режимів і мікросистеми захисту, а також функції безперервної процесорної системи безперервної діагностики, діагностики електричного обладнання тягових мемікропроцесорна система комерційного обліку реж містить мікропроцесор, дешифратор, регістр, опеВ основу винаходу поставлено задачу розширативний запам'ятовуючий пристрій, ключі, електрення функціональних можливостей, завдяки ронні лічильники, чотирьохпортовий модуль і блоспроможності виконання з єдиних інформаційних ки гальванічної розв'язки, причому вихід шини позицій комерційного обліку споживаємої електрипершого порту мікропроцесора підключені до вхочної енергії по тарифам, диференційованим за ду дешифратора, кожний k-й (к=1, 2, , п) вихід часом доби, безперервної діагностики електричноякого з'єднаний з управляючим входом к-то ключа, го обладнання тягових підстанцій і реєстрації доапідключеного інформаційним входом до виходу варійних, аварійних та після аварійних режимів послідовного порту електронного лічильника, вхід тягових мереж з прив'язкою до часу і функціонупослідовного порту якого підключений через первання системи захисту, а також визначення відший блок гальванічної розв'язки з виходом послістані до місця короткого замикання [3] Поставледовного порту мікропроцесора, вхід послідовного на мета досягається тим, що комп'ютерна система порту якого підключений через другий блок галькомерційного обліку електроенергії, реєстрації ванічної розв'язки до інформаційних виходів клюаварійних режимів та проведення безперервної чів, вихід шини даних другого порту мікропроцесодіагностики електричного обладнання тягових підра підключений до входу даних чотирьохпортового станцій доповнена центральним персональним модуля, оперативного запам'ятовуючого пристрою комп'ютером, мікропроцесорними модулями та і регістра, підключеного своїм виходом до входу модемами, причому кожний мікропроцесорний шини адреси молодших розрядів оперативного модуль включає мікропроцесор, дешифратор, запам'ятовуючого пристрою, з'єднаного входами блок гальванічної розв'язки, ключі, оперативний шини адреси старших розрядів з виходом шини запам'ятовуючий пристрій, чотирьохпортовий моадреси мікропроцесора і входом шини адреси чодуль, мікропроцесорну систему комерційного облітирьохпортового модуля, ВХІДНІ шини запису і чику, мікропроцесорну систему реєстрації аварійних тання якого підключені до ВІДПОВІДНОГО виходу шин режимів, мікропроцесорну систему безперервної запису і читання мікропроцесора і входу шин запидіагностики і мікропроцесорну систему читання су і читання оперативного запам'ятовуючого припервинних даних, причому вихід шини першого строю, перший стробуючий вихід мікропроцесора порту мікропроцесора підключений до входу перз'єднаний з управляючим входом дешифратора шого дешифратора, кожний k-й (к=1, 2, 3, 4) вихід (п+1)-й і (п+2)-й виходи якого з'єднані з управляюякого з'єднаний з управляючим входом к-го ключа, чими входами оперативного запам'ятовуючого вихід послідовного порту мікропроцесора підклюпристрою і чотирьохпортового модуля, а другий чений через перший блок гальванічної розв'язки з стробуючий вихід мікропроцесора підключений до входом послідовного порту мікропроцесорної сисуправляючого входу регістра теми комерційного обліку, мікропроцесорної системи реєстрації аварійних режимів, мікропроцесоЗавдяки введенню мікропроцесорних модулів рної системи безперервної діагностики і включаючих мікропроцесорну систему комерційномікропроцесорної системи читання первинних даго обліку, мікропроцесорну систему реєстрації них, виходи послідовних портів яких підключені аварійних режимів і мікропроцесорну систему без 61758 8 13, виходи послідовних портів яких підключені чеперервної діагностики і введенню нових звязків рез ВІДПОВІДНІ ключі 7 і другий блок гальванічної між ними, а також матричної організації архітектурозв'язки 6 до входу послідовного порту мікропрори комп'ютерна система комерційного обліку елекцесора 4 Вихід ШИНИ даних другого порту мікротроенергії, реєстрації аварійних режимів та провепроцесора 4 підключений до входу оперативного дення безперервної діагностики обладнання запам'ятовуючого пристрою 8, чотирьохпортового тягових підстанцій забезпечує значне розширення модуля 9 і через регістр 14 до входу шини молодфункціональних можливостей завдяки новій спроших адресів оперативного запам'ятовуючого приможності виконання з єдиних інформаційних позистрою 8, шини адреси старших розрядів якого цій комерційний облік споживаємої електроенергії з'єднані з виходом третього порту мікропроцесора по тарифам, диференційованим за часом доби, 4, входами другого дешифратора 5 і входами адбезперервну діагностику електричного обладнання реси чотирьохпортового модуля 9 Виходи запису тягових підстанцій і реєстрацію доаварійних, авата читання мікропроцесора 4 з'єднані з виходами рійних та після аварійних режимів тягових мереж з запису та читання чотирьохпортового модуля 9, прив'язкою до часу і функціонування системи замікропроцесорної системи читання первинних дахисту, а також знаходження відстані до місця аваних 13 і оперативного запам'ятовуючого пристрою рії Крім того, значно покращена надійність систе8, управляючі входи яких підключені до ВІДПОВІДми завдяки можливості з точки зору матричної НИХ ВИХОДІВ другого дешифратора 5 Управляючий архітектури настройки и в процесі роботи на можвхід першого дешифратора 5 з'єднаний з стробуливі типи авари, а також тестування Значно поючим входом мікропроцесора 4 Перший вихід ліпшились також експлуатаційні показники завдяки чотирьохпортового модуля кожного j-ro мікропрооднорідній матричній організації, такі, як пошук цесорного модуля (|=1, 2, , п) підключений ВІДПОнесправності, можливість резервування та розшиВІДНО через перший та другий модеми 3 до j-ro рення системи входу послідовного порту центрального персонаНа фіг 1 наведено структурну схему комп'юльного комп'ютера 1 Перший і другий виходи потерної системи комерційного обліку електроенерслідовних портів мікропроцесорної системи читангії, реєстрації аварійних режимів та проведення ня первинних даних 13 підключені ВІДПОВІДНО ДО безперервної діагностики електричного обладнандругих входів послідовних портів мікропроцесорної ня тягових підстанцій, на фіг 2 наведено мікросистеми реєстрації аварійних режимів 11 і мікропроцесорну систему комерційного обліку, на фіг З процесорної системи безперервної діагностики 12 наведено мікропроцесорну систему реєстрації Кожна мікропроцесорна система комерційного аварійних режимів, на фіг 4 наведено мікропроцеобліку 10 (фіг 2) містить мікропроцесор 15, дешисорну систему читання первинних даних, на фіг 5 фратор 16, регістр 17, оперативний запам'ятовуюнаведено блок-схему алгоритму функціонування чий пристрій 18, ключі 19, електронні лічильники комп'ютерної системи комерційного обліку, реєст20, чотирьох портовий модуль 21 і блоки гальванірації аварійних режимів та проведення безперервчної розв'язки 22 Вихід ШИНИ першого порту мікної діагностики електричного обладнання тягових ропроцесора 15 підключений до входу дешифрапідстанцій, на фіг 6 наведено блок-схему алгоритора 16, кожний k-й (к=1, 2, , п) вихід якого тму функціонування мікропроцесорної системи з'єднаний з управляючим входом k-го ключа 19, комерційного обліку, на фіг 7 наведено блокпідключеного інформаційним входом до виходу схему алгоритму функціонування мікропроцесорпослідовного порту електронного лічильника 20, ної системи реєстрації аварійних режимів, на фіг 8 вхід послідовного порту якого підключений через наведено блок-схему алгоритму мікропроцесорної перший блок гальванічної розв'язки 22 з виходом системи читання первинних даних Комп'ютерна послідовного порту мікропроцесора 15 Вхід послісистема комерційного обліку електроенергії, редовного порту мікропроцесора 15 з'єднаний через єстрації аварійних режимів та проведення безпедругий блок гальванічної розв'язки 22 до інформарервної діагностики електричного обладнання тяційних виходів ключів 19 Вхід ШИНИ даних другого гових підстанцій включає центральний порту мікропроцесора 15 підключений до входу персональний комп'ютер 1, мікропроцесорні модуданих чотирьохпортового модуля 21, оперативнолі 2, та модеми 3, причому кожний мікропроцесорго запам'ятовуючого пристрою 18 і регістра 17, ний модуль 2 включає мікропроцесор 4, дешифрапідключеного своїм виходом до входу шини адретор 5, блоки гальванічної розв'язки 6, ключі 7, си молодших розрядів оперативного запам'ятовуоперативний запам'ятовуючий пристрій 8, чотиючого пристрою 18, з'єднаного входами шини адрьохпортовий модуль 9, мікропроцесорну систему реси старших розрядів з виходом шини адреси комерційного обліку 10, мікропроцесорну систему мікропроцесора 15 і входом шини адреси чотиреєстрації аварійних режимів 11, мікропроцесорну рьохпортового модуля 21 Шини запису мікропросистему безперервної діагностики 12, мікропроцецесора 15 підключені ВІДПОВІДНО до входів шин сорну систему читання первинних даних 13 і резапису і читання чотирьохпортового модуля 21 і гістр 14 Вихід ШИНИ першого порту мікропроцесооперативного запам'ятовуючого пристрою 18 Пера 4 підключений до входу першого дешифратора рший стробуючий вихід мікропроцесора 15 з'єдна5, кожний k-й (к=1, 2, 3, 4) вихід якого з'єднаний з ний з управляючим входом дешифратора 16, управляючим входом k-го ключа 7 Вихід послідо(п+1)-й і (п+2)-й виходи якого з'єднані з управляювного порту мікропроцесора 4 підключений через чими входами оперативного запам'ятовуючого блок гальванічної розв'язки 6 з входом послідовнопристрою 18 і чотирьохпортового модуля 21 Друго порту мікропроцесорних систем комерційного гий стробуючий вихід мікропроцесора 15 підклюобліку 10, реєстрації аварійних режимів 11, безпечений до управляючого входу регістра 17 Кожна рервної діагностики 12 і читання первинних даних 61758 10 мікропроцесорна система реєстрації аварійних єднані і підключені через перетворювач аналогорежимів 11 (фіг 3) містить мікропроцесор 23, девих сигналів 35 до j-ro входу аналого-цифрового шифратори 24, блоки гальванічної розв'язки 25, перетворювача 33 Виходи запису та читання мікключі 26, датчики 27, регістр 28, оперативний заропроцесора 31 підключені до ВІДПОВІДНИХ входів пам'ятовуючий пристрій 29 і чотирьохпортовий запису та читання оперативного запам'ятовуючого модуль ЗО Вихід ШИНИ першого порту мікропроцепристрою 38, аналого-цифрового перетворювача сора 23 підключений до входу першого дешифра33, регістра 37 і чотирьохпортового модуля 39, тора 24, кожний і-й (і=1, 2, , т ) вихід якого з'єдуправляючі входи яких з'єднані з ВІДПОВІДНИМИ наний з управляючим входом і-го ключа 26, виходами третього дешифратора 32 підключеного інформаційним входом до виходу Мікропроцесор 4 (фіг 1), мікропроцесор 15 послідовного порту датчика 27, послідовний вхід (фіг 2), мікропроцесор 23 (фіг 3) і мікропроцесор якого з'єднаний через перший блок гальванічної 31 (фіг 4) виконані, наприклад, у вигляді однокрирозв'язки 25, з виходом послідовного порту мікростального мікропроцесора типу KM 1816ВЕ51 процесора 23 Вхід ПОСЛІДОВНОГО порту мікропроЧотирьохпортові модулі 9 (фіг 1), 21 (фіг 2), 39 цесора 23 підключений через другий блок гальва(фіг 4) виконані, наприклад, у вигляді інтегральної нічної розв'язки 25 до виходу всіх ключів 26 Вихід схеми типу ST16C554DCJ Блоки гальванічної шини даних другого порту мікропроцесора 23, підрозв'язки 6 (фіг 1), 22 (фіг 2) і 25 (фіг 3) виконані, ключений до входу даних чотирьохпортового монаприклад, у вигляді оптронів типу АОТ1285 дуля ЗО, оперативного запам'ятовуючого пристрою Робота комп'ютерної системи комерційного 29 і регістра 28, вихід якого з'єднаний з входом обліку електроенергії, реєстрації аварійних режишини адреси молодших розрядів чотирьохпортомів та проведення безперервної діагностики елеквого модуля ЗО, регістра 28 і оперативного запатричного обладнання тягових підстанцій (фіг 1) м'ятовуючого пристрою 29, вхід шини адреси стапроводиться у ПОСЛІДОВНОСТІ з блок-схемою систерших розрядів якого підключений до шини адреси много алгоритму роботи (фіг 5), блок-схемою алмікропроцесора 23, чотирьохпортового модуля ЗО і горитму роботи (фіг 6) мікропроцесорної системи другого дешифратора 24 Перший, другий і третій комерційного обліку 10, блок-схемою алгоритму виходи другого дешифратора 24 підключені до роботи (фіг 7) мікропроцесорної системи реєстрауправляючих входів ВІДПОВІДНО чотирьохпортового ції аварійних режимів 11 та блок-схемою алгоритмодуля ЗО, регістра 28 і оперативного запам'ятому роботи (фіг 8) мікропроцесорної системи чивуючого пристрою 29, входи запису і читання яких тання первинних даних 12 Після запуску з'єднані з виходами запису і читання мікропроцемікропроцесорної системи комерційного обліку 10 сора 23, підключеного стробуючим виходом до (фіг 2) згідно алгоритму (фіг 5) вона працює поуправляючого входу першого дешифратора 24 стійно в реальному часі, а інформація комерційноКожна мікропроцесорна система читання первинго обліку електроенергії по диференційованим них даних (фіг 4) містить мікропроцесор 31, детарифам накопляється в базах даних електронних шифратор 32, аналого-цифровий перетворювач ЛІЧИЛЬНИКІВ 20 Після запиту інформація від цент33, ключі 34, перетворювачі аналогових сигналів рального персонального комп'ютера 1 через перший вхід чотирьохпортового модуля 21 поступає в 35, шифратори дискретних сигналів 36, регістр 37, мікропроцесор 15, де вона оброблюється, визнаі оперативний запам'ятовуючий пристрій 38 та чочається номер електронного лічильника 20, з яким тирьохпортовий модуль 39 Виходи старших і мобуде реалізований обмін комерційними даними лодших розрядів шини першого порту мікропроцеПісля установки зв'язку визначається режим робосора 31 підключені ВІДПОВІДНО до входів першого і ти читання чи запис Якщо читання, то дані із еледругого дешифраторів 32, управляючі входи яких ктронного лічильника 20 по послідовному порту об'єднані і підключені до стробуючого виходу мікпоступають через ключ 19 і блок гальванічної розропроцесора 31 Вихід ШИНИ даних другого порту в'язки в пам'ять мікропроцесора 15 і, якщо необмікропроцесора 31 з'єднаний з входами аналогохідно, в оперативний запам'ятовуючий пристрій 18 цифрового перетворювача 33, шифратора дискреПісля ЧОГО блок даних через чотирьохпортовий тних сигналів 36, чотирьохпортового модуля 39, модуль 21 поступає до центрального персональоперативного запам'ятовуючого пристрою 38 і ного комп'ютера 1, де інформація обробляється і входом регістра 37, підключеного своїм виходом формуються ЗВІТНІ документи Після ТОГО, ЯК передо входу шини адреси молодших розрядів операдані усі дані мікропроцесор 15 аналізує блок інфотивного запам'ятовуючого пристрою 38, входи ширмації запиту на предмет передачі чи кінця зв'язку ни адреси старших розрядів якого з'єднані з вихоВ тому випадку, коли запит був на предмет запису дом шини третього порту мікропроцесора 31, інформації в мікропроцесор 15 або електронний чотирьохпортового модуля 39 і входу третього лічильник 20 з метою перепрограмування чи тесдешифратора 32 Ключі 34 виконані у вигляді маттування, то по аналогії вищесказаному згідно алриці (nxm), кожний перший управляючий вхід к-го горитму (фіг 6) проводиться програмування мікрядку ключів якої (к=1, 2, , п) підключені до к-го ропроцесорної системи комерційного обліку чи виходу першого дешифратора 32, кожний j-й 0=1, тестування Потім система запускається в роботу 2, , т ) вихід другого дешифратора 32 підключеПісля запуску мікропроцесорна система реєстрації ний до другого управляючого входу кожного ключа аварійних режимів 11 (фіг 3) згідно алгоритму (фіг 34 j-ro стовпця матриці і першого управляючого 7) працює постійно таким чином Регулярно читавходу кожного j-ro шифратора дискретних сигналів ються первинні дані із мікропроцесорної системи читання первинних даних, проводиться їх обробка, 36, другий управляючий вхід якого з'єднаний з J-M аналіз функціонування електричного обладнання, виходом третього дешифратора 32 Інформаційні виходи ключів 34 кожного j-ro стовпця матриці об' 12 11 61758 реєстрація режимів, гармонічний аналіз, ідентифістанцій вигідно відрізняється від прототипу На кація аварійних режимів, їх запис і формування відміну від прототипу, в якому звужені функціонафайла аварії і подається інформація диспетчеру льні можливості, тому що на базі прототипу немоКоли від центрального персонального комп'ютера жливо вести комерційний облік електроенергії по 1 поступив запит на обмін даними, то він аналізутарифам, диференційованим по зонам доби, а ється мікропроцесором 23 на предмет читання також неможливо реєструвати момент початку аварійних даних чи програмування або тестування аварії і аварійного режиму мережі з прив'язкою до мікропроцесорної системи реєстрації аварійних часу і моменту включення різних рівнів системи режимів 11 Після ЧОГО проводиться обмін інфораварійного захисту Крім того у прототипі неможмацією, і мікропроцесорна система запускається ливо визначити відстань до місця аварії, і не прона новий цикл роботи Мікропроцесорна система водиться безперервна діагностика силового елекбезперервної діагностики 12 функціонує аналогічтричного обладнання тягових підстанцій, а також у но мікропроцесорній системі 11 згідно алгоритму нього низька надійність функціонування, завдяки (фіг 7) Мікропроцесорна система читання пертому, що в процесі роботи неможливо вести навинних даних 13 (фіг 4) згідно алгоритму (фіг 8) стройку комп'ютерної системи на можливі види працює постійно, читає первинну інформацію, яка аварії та тестовий контроль Також в зв'язку з тим, через ключі 34 та перетворювачі аналогових сигщо архітектура прототипу неоднорідна, то у нього налів 35 поступає на аналого-цифровий перетвозначно погіршені такі характеристики як живучість, рювач 33, де вона перетворюється в цифрову фонадійність У запропонованій комп'ютерній системі рму і записується в пам'ять мікропроцесора 31 або завдяки введенню нових елементів і зв'язків МІЖ оперативний запам'ятовуючий пристрій 38 Після ними значно розширились функціональні можлитого як по першому або по другому входу чотивості завдяки спроможності виконання системою з рьохпортового модуля 39 появився запит від мікєдиних інформаційних позицій комерційного обліку ропроцесорних систем 11 чи 12 на обмін інформаелектроенергії по тарифам, диференційованим по цією, то він обробляється в мікропроцесорі 31, зонам доби, реєстрування доаварійного, аварійнопісля чого видається файл первинних даних для го та післяаваріиного режимів роботи електричних подальшої обробки В тому випадку, коли провомереж з прив'язкою до часу і функціонування сисдиться тестування мікропроцесорної системи 13, теми захисту, а також знаходження місця аварії то ВІДПОВІДНО передається тестовий файл, і вона Крім того, в запропонованій системі з'явилась моперевіряється Якщо тест виконався, то мікропрожливість реалізації безперервної діагностики техцесорна система запускається в роботу Комп'юнічного стану силового електричного обладнання терна система комерційного обліку електроенергії, тягових підстанцій та прогнозу його ресурсу В реєстрації аварійних режимів та проведення беззапропонованій комп'ютерній системі також стало перервної діагностики електричного обладнання можливим завдяки збільшенню ступеня однорідтягових підстанцій (фіг 1) згідно алгоритму (фіг 5) ності вести в процесі роботи настройку системи і виконує системні функції по обміну інформацією тестовий контроль, покращились такі експлуатаміж центральним персональним комп'ютером 1 і ційні характеристики як живучість, надійність, помікропроцесорними системами комерційного облішук та ремонт пошкодження і т п ку 10, реєстрації аварійних режимів 11, безперерЛітература вної діагностики електрообладнання 12, а також їх тестування, програмування, запуск в роботу і фун1 Устройство сбора, преобразования и перекціонування В центральному персональному комдачи результатов измерения параметров физичеп'ютері 1 ведеться обробка інформації, формуєтьской среды G06F17/40/ Патент РФ №2079882, БИ ся звітна і комерційна документація і файли для №14, 20 05 97г передачі даних на всі рівні управління 2 United States Patent 5270704 "Autonomus Pulse Reading and Recording System" Dec 14, 1993, G01D4/00 Завдяки введенню нових елементів та зв'язків між ними запропонована комп'ютерна система 3 Інформаційно-вимірювальна система комерційного обліку електроенергії, реєстрації G06F15/20, патент України №16876 Промислова аварійних режимів та проведення безперервної власність Офіційний бюлетень №4, 1997р діагностики електричного обладнання тягових під(прототип) 13 61758 14 15 61758 16 17 61758 18 19 61758 20 21 Комп'ютерна верстка М Клюкш 61758 22 Підписне Тираж39 прим Міністерство освіти і науки України Державний департамент інтелектуальної власності, Львівська площа, 8, м Київ, МСП, 04655, Україна ДП "Український інститут промислової власності", вул Сім'ї Хохлових, 15, м Київ, 04119

ДивитисяДодаткова інформація

Назва патенту англійськоюComputer system for metering consumed electric energy, recording emergency events, and continuously monitoring electrical equipment of traction substations

Автори англійськоюStohnii Borys Serhiiovych, Sopel Mykhailo Fedorovych, Tutyk Volodymyr Lvovych, Hinailo Andrii Viktorovych, Martyniuk Maksym Volodymyrovych

Назва патенту російськоюКомпьютерная система для учета потребляемой электроэнергии, регистрации аварийных событий и непрерывного контроля электрооборудования тяговых подстанций

Автори російськоюСтогний Борис Сергеевич, Сопель Михаил Федорович, Тутик Владимир Львович, Гинайло Андрей Викторович, Мартынюк Максим Владимирович

МПК / Мітки

МПК: G06F 17/40, G06F 17/20

Мітки: аварійних, безперервної, комп'ютерна, електричного, підстанцій, режимів, проведення, реєстрації, електроенергії, комерційного, діагностики, обладнання, тягових, обліку, система

Код посилання

<a href="https://ua.patents.su/11-61758-kompyuterna-sistema-komercijjnogo-obliku-elektroenergi-reehstraci-avarijjnikh-rezhimiv-ta-provedennya-bezperervno-diagnostiki-elektrichnogo-obladnannya-tyagovikh-pidstancijj.html" target="_blank" rel="follow" title="База патентів України">Комп’ютерна система комерційного обліку електроенергії, реєстрації аварійних режимів та проведення безперервної діагностики електричного обладнання тягових підстанцій</a>

Попередній патент: Пристрій і спосіб ультразвукової ударної обробки

Наступний патент: Привід круглов’язальної машини

Випадковий патент: Безглинистий вапняний буровий розчин