Пристрій цифрового формування променів

Номер патенту: 55954

Опубліковано: 27.12.2010

Автори: Халілов Едуард Маггерамович, Фалєєв Ігор Михайлович, Соловей Володимир Юхимович, Павлюк Олег Євгенович, Карпенко Євген Валерійович, Зацерковський Руслан Олексійович, Ковальчук Костянтин Володимирович, Зубченко Ігор Васильович

Формула / Реферат

Пристрій цифрового формування променів, що містить М-канальний формувач цифрових комплексних сигналів, складений з М канальних аналого-цифрових перетворювачів (АЦП), з'єднаних входами з виходами М канальних підсилювачів, арифметичний блок, який відрізняється тим, що введено цифровий квадратурний перетворювач частоти, що містить блок постійної пам'яті косинусних та синусних відліків гетеродинного сигналу, селектор цифрових косинусних та синусних відліків гетеродинного сигналу, підключений входами cos, sin відповідно до виходів u, v блока постійної пам'яті косинусних та синусних відліків гетеродинного сигналу, помножувач-накопичувач цифрового квадратурного перетворення частоти, з'єднаний першим входом за допомогою шини даних з М виходами М-канального формувача цифрових комплексних сигналів, а другим входом - з виходом селектора цифрових косинусних та синусних відліків гетеродинного сигналу, при цьому М-канальний формувач цифрових комплексних сигналів виконано у вигляді М регістрів канальних синфазних відліків ξ, М регістрів канальних квадратурних відліків η, входи яких об'єднано та підключено до виходів відповідного канального АЦП, М селекторів канальних синфазних відліків ξ, та канальних квадратурних відліків η, з'єднаних першим входом з виходом регістра канального синфазного відліку ξ, другим входом - з виходом регістра канального квадратурного відліку η відповідного каналу, виходами підключених до шини даних, а арифметичний блок виконано у вигляді блока оперативної пам'яті вхідних та проміжних комплексних відліків швидкого перетворення Фур'є (ШПФ), помножувача-накопичувача ШПФ, регістра дійсних відліків ШПФ Re, регістра уявних відліків ШПФ Іm, селектора дійсних та уявних відліків ШПФ, блока постійної пам'яті обертаючих множників ШПФ, блока постійної пам'яті комплексних спектрів амплітудно-фазових розподілів точної стабілізації, блока управління, синхровиходи якого за допомогою шини управління підключено до синхровходів М канальних АЦП, до синхровходів М регістрів канальних синфазних відліків ξ, M регістрів канальних квадратурних відліків η, регістра дійсних відліків ШПФ Re, регістра уявних відліків ШПФ Іm, до синхровходів помножувача-накопичувача цифрового квадратурного перетворювання частоти, помножувача-накопичувача ШПФ, синхровиходи та адресні виходи блока управління за допомогою шини управління підключено до синхровходів та адресних входів М селекторів канальних синфазних відліків ξ, та канальних квадратурних відліків η, селектора цифрових косинусних та синусних відліків гетеродинного сигналу, селектора дійсних та уявних відліків ШПФ, до синхровходів та адресних входів блока постійної пам'яті косинусних та синусних відліків гетеродинного сигналу, блока оперативної пам'яті вхідних та проміжних комплексних відліків ШПФ, блока постійної пам'яті обертаючих множників ШПФ, блока постійної пам'яті комплексних спектрів амплітудно-фазових розподілів точної стабілізації, а вхід сполучено з джерелом управляючих сигналів - Т, при цьому вихід блока постійної пам'яті обертаючих множників ШПФ об'єднано з виходом блока постійної пам'яті комплексних спектрів амплітудно-фазових розподілів точної стабілізації і підключено до другого входу помножувача-накопичувача ШПФ, який з'єднано першим входом з виходом блока оперативної пам'яті вхідних та проміжних комплексних відліків ШПФ, а виходом - з входами даних регістра дійсних відліків ШПФ Re та регістра уявних відліків Іm, виходи яких з'єднано з входами селектора дійсних та уявних відліків ШПФ, вихід якого об'єднано з виходом помножувача-накопичувача цифрового квадратурного перетворювання частоти і підключено до входу даних блока оперативної пам'яті вхідних та проміжних комплексних відліків ШПФ.

Текст

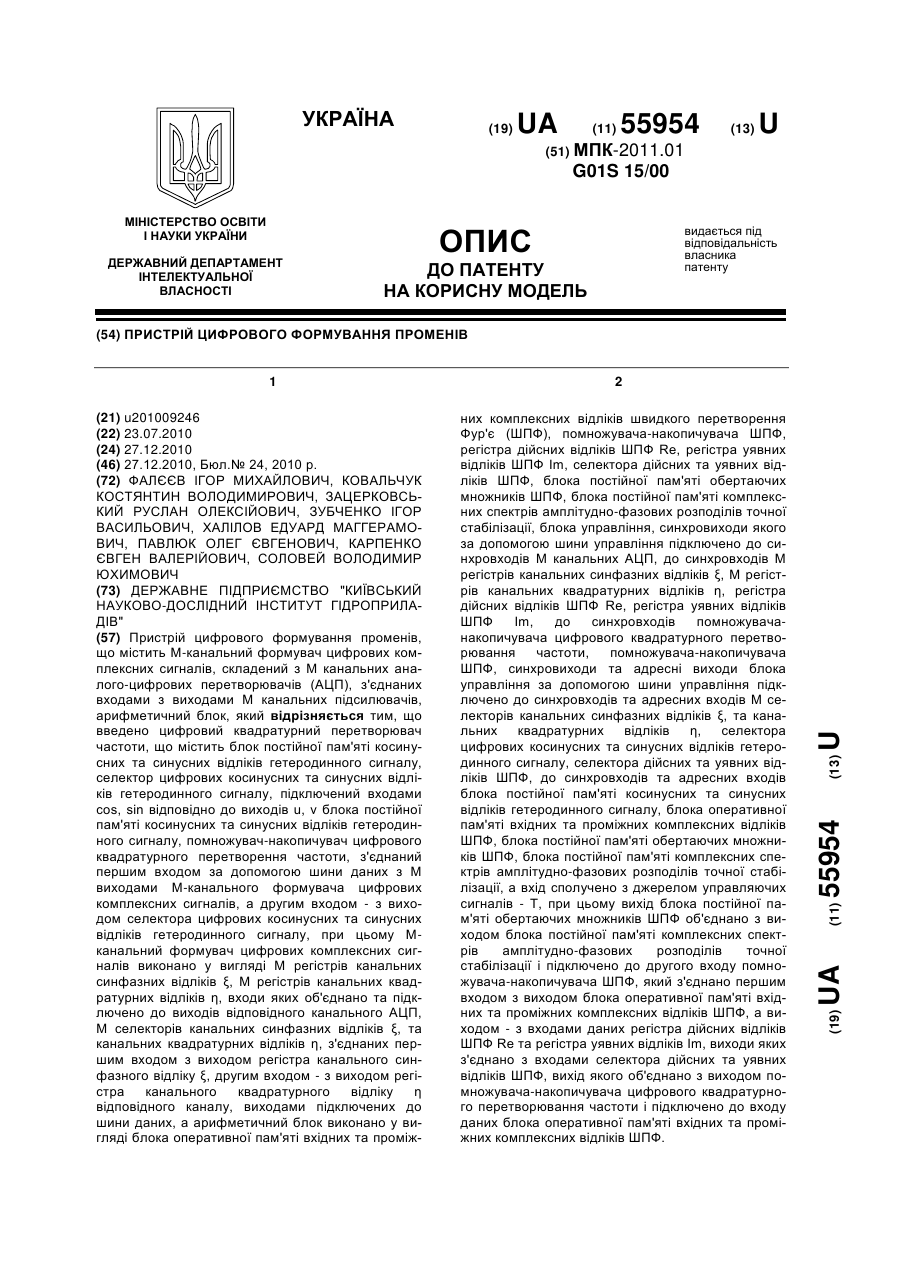

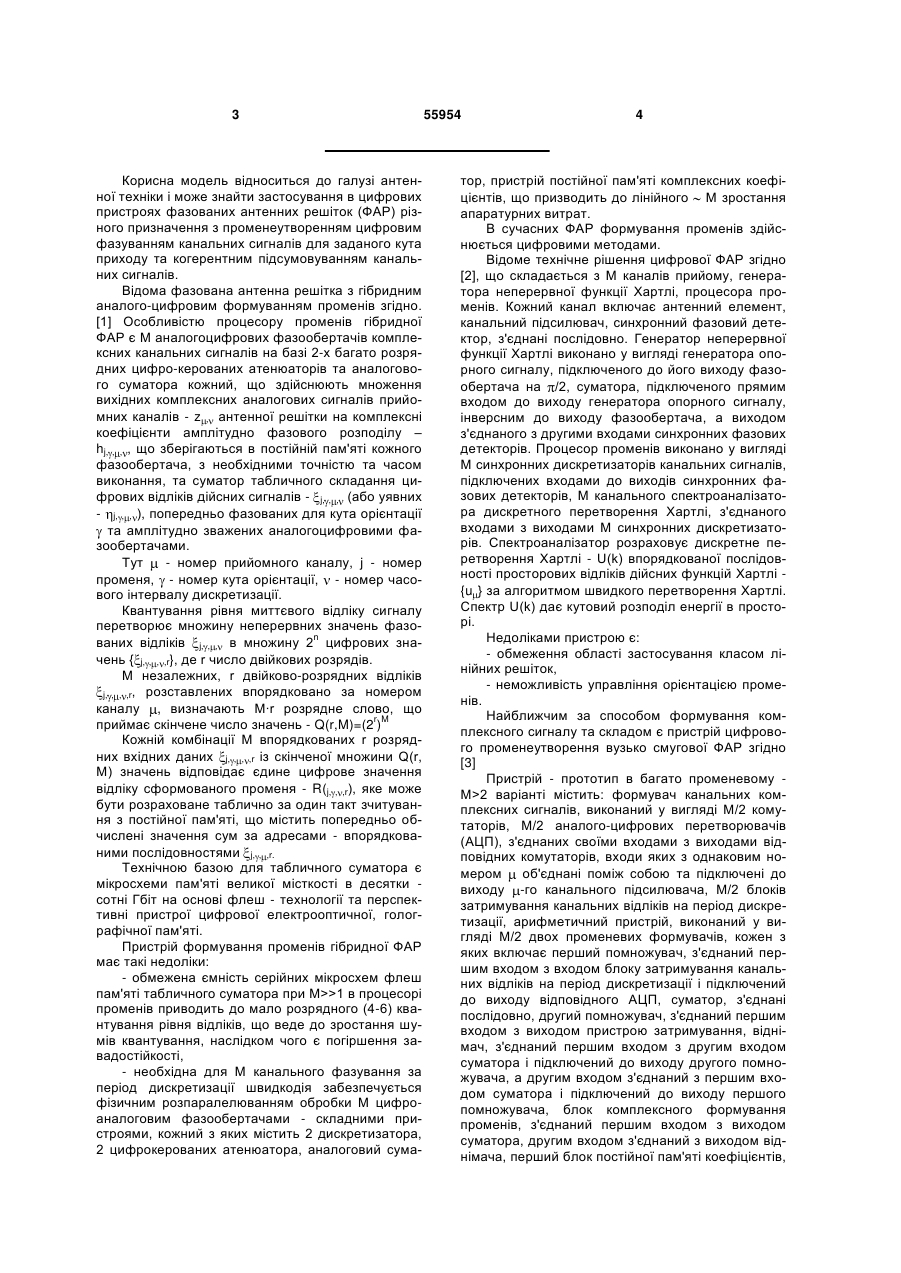

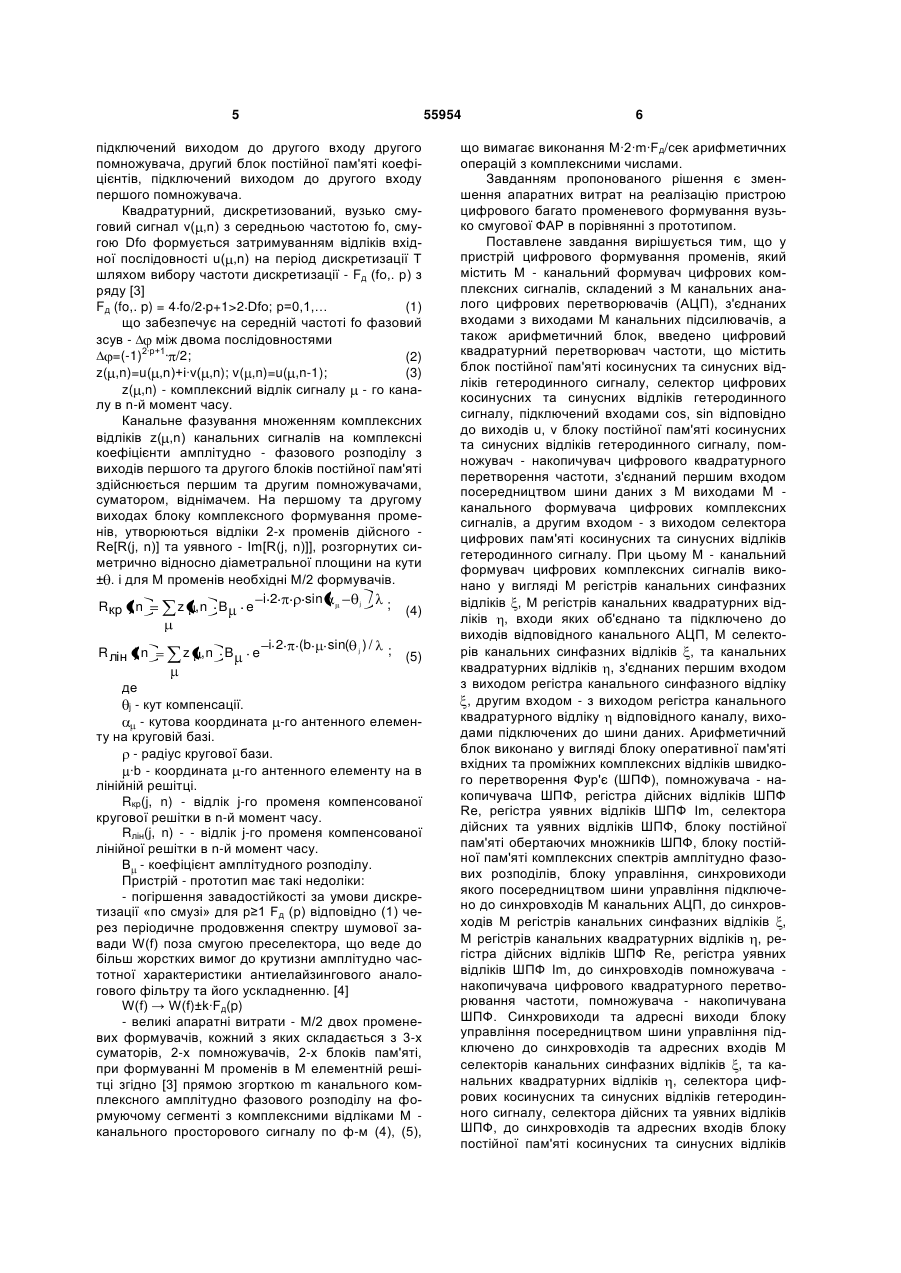

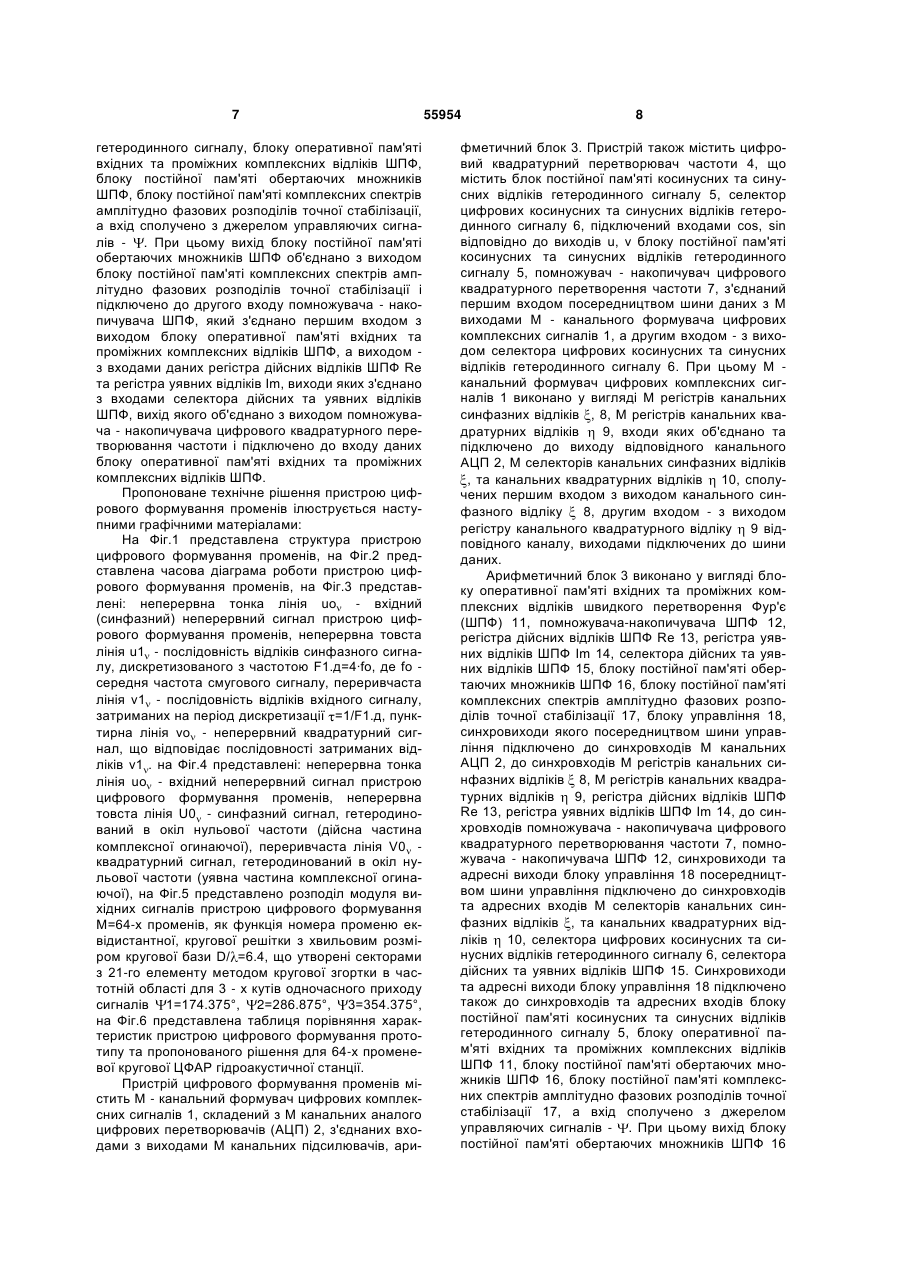

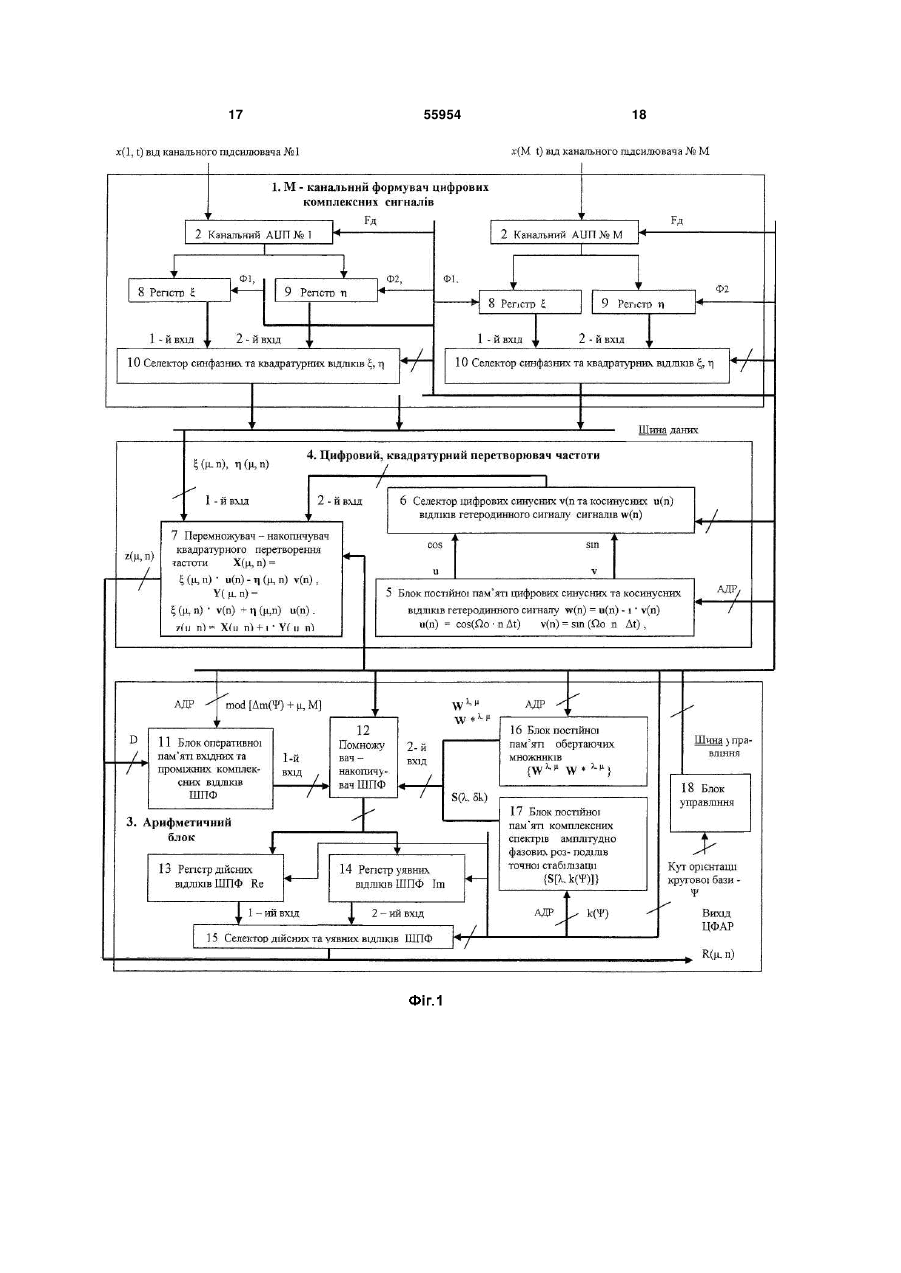

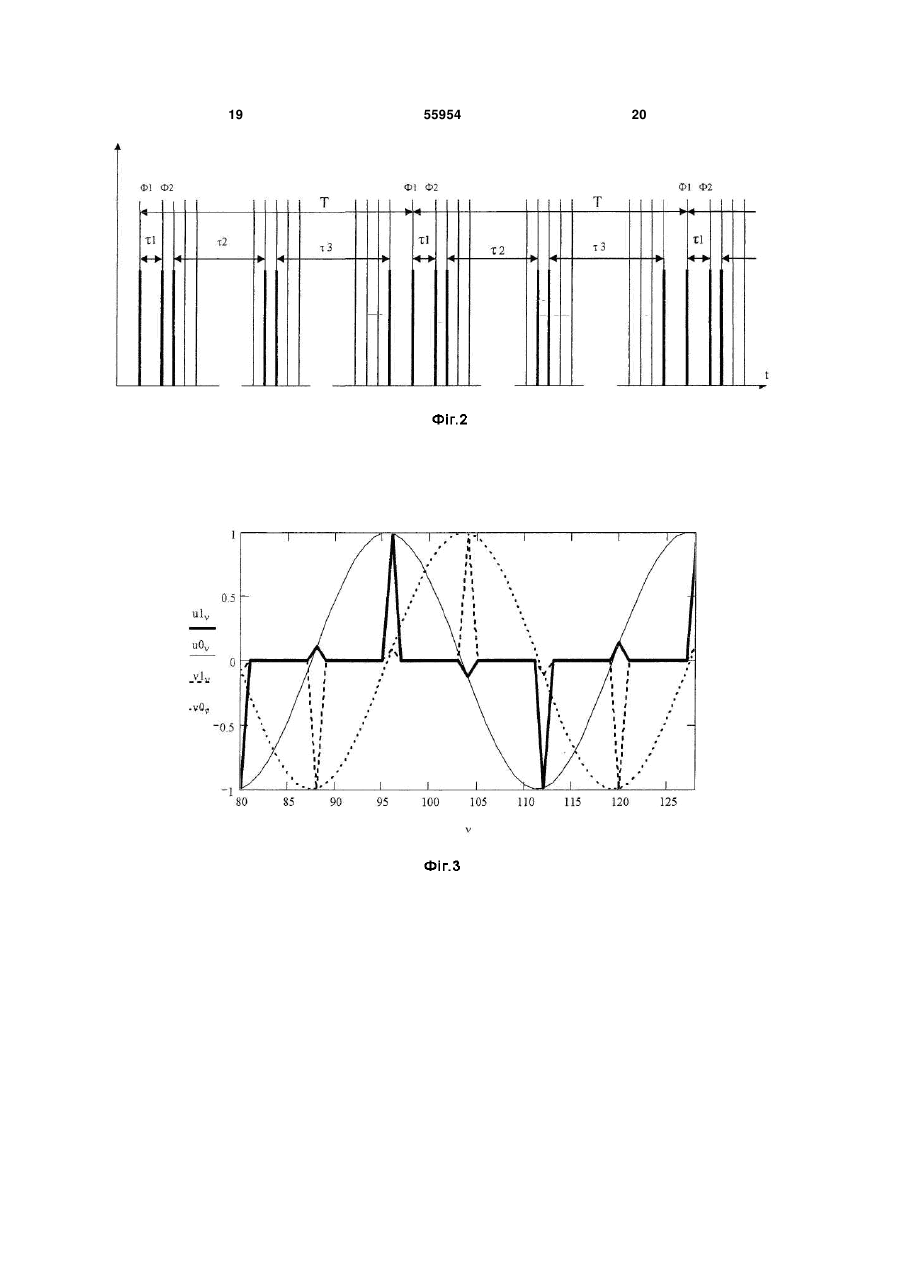

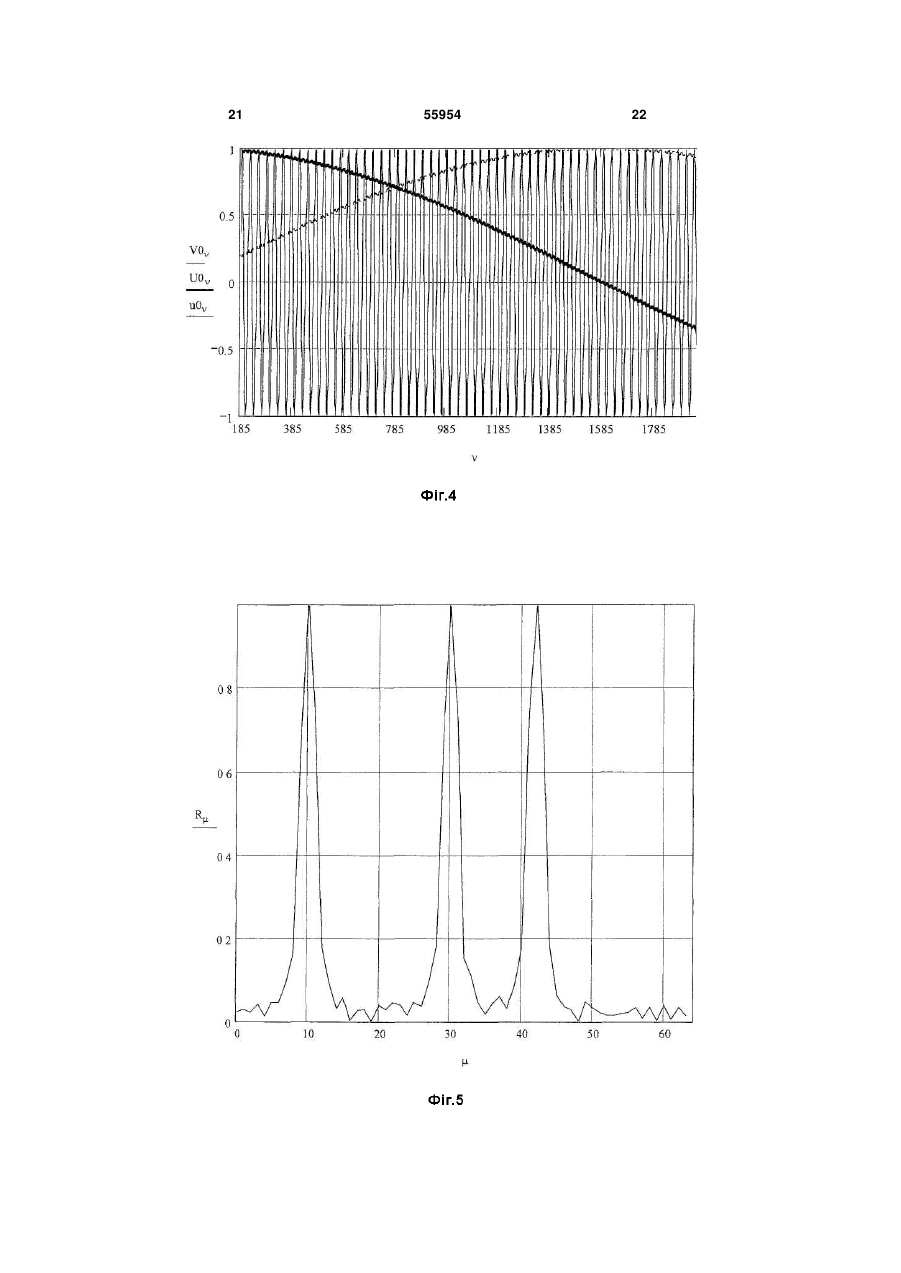

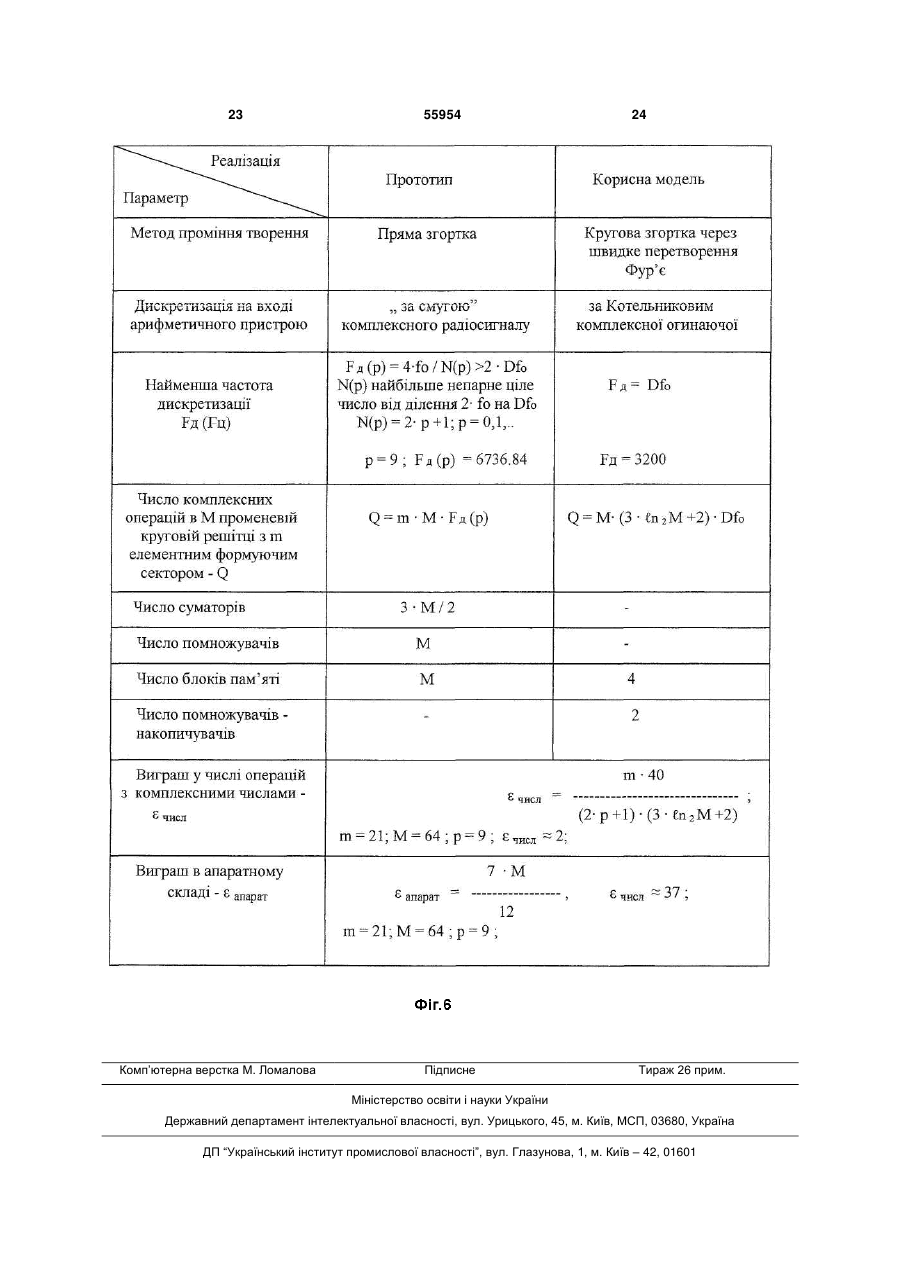

Пристрій цифрового формування променів, що містить М-канальний формувач цифрових комплексних сигналів, складений з М канальних аналого-цифрових перетворювачів (АЦП), з'єднаних входами з виходами М канальних підсилювачів, арифметичний блок, який відрізняється тим, що введено цифровий квадратурний перетворювач частоти, що містить блок постійної пам'яті косинусних та синусних відліків гетеродинного сигналу, селектор цифрових косинусних та синусних відліків гетеродинного сигналу, підключений входами cos, sin відповідно до виходів u, v блока постійної пам'яті косинусних та синусних відліків гетеродинного сигналу, помножувач-накопичувач цифрового квадратурного перетворення частоти, з'єднаний першим входом за допомогою шини даних з М виходами М-канального формувача цифрових комплексних сигналів, а другим входом - з виходом селектора цифрових косинусних та синусних відліків гетеродинного сигналу, при цьому Мканальний формувач цифрових комплексних сигналів виконано у вигляді М регістрів канальних синфазних відліків ξ, М регістрів канальних квадратурних відліків η, входи яких об'єднано та підключено до виходів відповідного канального АЦП, М селекторів канальних синфазних відліків ξ, та канальних квадратурних відліків η, з'єднаних першим входом з виходом регістра канального синфазного відліку ξ, другим входом - з виходом регістра канального квадратурного відліку η відповідного каналу, виходами підключених до шини даних, а арифметичний блок виконано у вигляді блока оперативної пам'яті вхідних та проміж 2 (19) 1 3 Корисна модель відноситься до галузі антенної техніки і може знайти застосування в цифрових пристроях фазованих антенних решіток (ФАР) різного призначення з променеутворенням цифровим фазуванням канальних сигналів для заданого кута приходу та когерентним підсумовуванням канальних сигналів. Відома фазована антенна решітка з гібридним аналого-цифровим формуванням променів згідно. [1] Особливістю процесору променів гібридної ФАР є М аналогоцифрових фазообертачів комплексних канальних сигналів на базі 2-х багато розрядних цифро-керованих атенюаторів та аналогового суматора кожний, що здійснюють множення вихідних комплексних аналогових сигналів прийомних каналів - z , антенної решітки на комплексні коефіцієнти амплітудно фазового розподілу – hj, , , , що зберігаються в постійній пам'яті кожного фазообертача, з необхідними точністю та часом виконання, та суматор табличного складання цифрових відліків дійсних сигналів - j, , , (або уявних - j, , , ), попередньо фазованих для кута орієнтації та амплітудно зважених аналогоцифровими фазообертачами. Тут - номер прийомного каналу, j - номер променя, - номер кута орієнтації, - номер часового інтервалу дискретизації. Квантування рівня миттєвого відліку сигналу перетворює множину неперервних значень фазованих відліків j, , , в множину 2n цифрових значень { j, , , ,r}, де r число двійкових розрядів. М незалежних, r двійково-розрядних відліків j, , , ,r, розставлених впорядковано за номером каналу , визначають М∙r розрядне слово, що приймає скінчене число значень - Q(r,M)=(2r)M Кожній комбінації М впорядкованих r розрядних вхідних даних j, , , ,r із скінченої множини Q(r, M) значень відповідає єдине цифрове значення відліку сформованого променя - R(j, , ,r), яке може бути розраховане таблично за один такт зчитування з постійної пам'яті, що містить попередньо обчислені значення сум за адресами - впорядкованими послідовностями j, , ,r. Технічною базою для табличного суматора є мікросхеми пам'яті великої місткості в десятки сотні Гбіт на основі флеш - технології та перспективні пристрої цифрової електрооптичної, голографічної пам'яті. Пристрій формування променів гібридної ФАР має такі недоліки: - обмежена ємність серійних мікросхем флеш пам'яті табличного суматора при М>>1 в процесорі променів приводить до мало розрядного (4-6) квантування рівня відліків, що веде до зростання шумів квантування, наслідком чого є погіршення завадостійкості, - необхідна для М канального фазування за період дискретизації швидкодія забезпечується фізичним розпаралелюванням обробки М цифроаналоговим фазообертачами - складними пристроями, кожний з яких містить 2 дискретизатора, 2 цифрокерованих атенюатора, аналоговий сума 55954 4 тор, пристрій постійної пам'яті комплексних коефіцієнтів, що призводить до лінійного М зростання апаратурних витрат. В сучасних ФАР формування променів здійснюється цифровими методами. Відоме технічне рішення цифрової ФАР згідно [2], що складається з М каналів прийому, генератора неперервної функції Хартлі, процесора променів. Кожний канал включає антенний елемент, канальний підсилювач, синхронний фазовий детектор, з'єднані послідовно. Генератор неперервної функції Хартлі виконано у вигляді генератора опорного сигналу, підключеного до його виходу фазообертача на /2, суматора, підключеного прямим входом до виходу генератора опорного сигналу, інверсним до виходу фазообертача, а виходом з'єднаного з другими входами синхронних фазових детекторів. Процесор променів виконано у вигляді М синхронних дискретизаторів канальних сигналів, підключених входами до виходів синхронних фазових детекторів, М канального спектроаналізатора дискретного перетворення Хартлі, з'єднаного входами з виходами М синхронних дискретизаторів. Спектроаналізатор розраховує дискретне перетворення Хартлі - U(k) впорядкованої послідовності просторових відліків дійсних функцій Хартлі {u } за алгоритмом швидкого перетворення Хартлі. Спектр U(k) дає кутовий розподіл енергії в просторі. Недоліками пристрою є: - обмеження області застосування класом лінійних решіток, - неможливість управління орієнтацією променів. Найближчим за способом формування комплексного сигналу та складом є пристрій цифрового променеутворення вузько смугової ФАР згідно [3] Пристрій - прототип в багато променевому М>2 варіанті містить: формувач канальних комплексних сигналів, виконаний у вигляді М/2 комутаторів, М/2 аналого-цифрових перетворювачів (АЦП), з'єднаних своїми входами з виходами відповідних комутаторів, входи яких з однаковим номером об'єднані поміж собою та підключені до виходу -го канального підсилювача, М/2 блоків затримування канальних відліків на період дискретизації, арифметичний пристрій, виконаний у вигляді М/2 двох променевих формувачів, кожен з яких включає перший помножувач, з'єднаний першим входом з входом блоку затримування канальних відліків на період дискретизації і підключений до виходу відповідного АЦП, суматор, з'єднані послідовно, другий помножувач, з'єднаний першим входом з виходом пристрою затримування, віднімач, з'єднаний першим входом з другим входом суматора і підключений до виходу другого помножувача, а другим входом з'єднаний з першим входом суматора і підключений до виходу першого помножувача, блок комплексного формування променів, з'єднаний першим входом з виходом суматора, другим входом з'єднаний з виходом віднімача, перший блок постійної пам'яті коефіцієнтів, 5 55954 підключений виходом до другого входу другого помножувача, другий блок постійної пам'яті коефіцієнтів, підключений виходом до другого входу першого помножувача. Квадратурний, дискретизований, вузько смуговий сигнал v( ,n) з середньою частотою fo, смугою Dfo формується затримуванням відліків вхідної послідовності u( ,n) на період дискретизації Т шляхом вибору частоти дискретизації - Fд (fo,. p) з ряду [3] Fд (fo,. p) = 4 fo/2 p+1>2 Dfo; р=0,1,… (1) що забезпечує на середній частоті fo фазовий зсув - ∆ між двома послідовностями ∆ =(-1)2∙р+1∙ /2; (2) z( ,n)=u( ,n)+і∙v( ,n); v( ,n)=u( ,n-1); (3) z( ,n) - комплексний відлік сигналу - го каналу в n-й момент часу. Канальне фазування множенням комплексних відліків z( ,n) канальних сигналів на комплексні коефіцієнти амплітудно - фазового розподілу з виходів першого та другого блоків постійної пам'яті здійснюється першим та другим помножувачами, суматором, віднімачем. На першому та другому виходах блоку комплексного формування променів, утворюються відліки 2-х променів дійсного Re[R(j, n)] та уявного - Im[R(j, n)]], розгорнутих симетрично відносно діаметральної площини на кути ± . і для М променів необхідні М/2 формувачів. i2 sin / ; j Rкр j, n z ,n B e (4) R лін j, n z ,n B e i2 (b sin( j ) / ; (5) де j - кут компенсації. - кутова координата -го антенного елементу на круговій базі. - радіус кругової бази. ∙b - координата -го антенного елементу на в лінійній решітці. Rкр(j, n) - відлік j-го променя компенсованої кругової решітки в n-й момент часу. Rлін(j, n) - - відлік j-го променя компенсованої лінійної решітки в n-й момент часу. В - коефіцієнт амплітудного розподілу. Пристрій - прототип має такі недоліки: - погіршення завадостійкості за умови дискретизації «по смузі» для р≥1 Fд (р) відповідно (1) через періодичне продовження спектру шумової завади W(f) поза смугою преселектора, що веде до більш жорстких вимог до крутизни амплітудно частотної характеристики антиелайзингового аналогового фільтру та його ускладненню. [4] W(f) → W(f)±k∙Fд(p) - великі апаратні витрати - М/2 двох променевих формувачів, кожний з яких складається з 3-х суматорів, 2-х помножувачів, 2-х блоків пам'яті, при формуванні М променів в М елементній решітці згідно [3] прямою згорткою m канального комплексного амплітудно фазового розподілу на формуючому сегменті з комплексними відліками М канального просторового сигналу по ф-м (4), (5), 6 що вимагає виконання М∙2∙m∙Fд/сек арифметичних операцій з комплексними числами. Завданням пропонованого рішення є зменшення апаратних витрат на реалізацію пристрою цифрового багато променевого формування вузько смугової ФАР в порівнянні з прототипом. Поставлене завдання вирішується тим, що у пристрій цифрового формування променів, який містить М - канальний формувач цифрових комплексних сигналів, складений з М канальних аналого цифрових перетворювачів (АЦП), з'єднаних входами з виходами М канальних підсилювачів, а також арифметичний блок, введено цифровий квадратурний перетворювач частоти, що містить блок постійної пам'яті косинусних та синусних відліків гетеродинного сигналу, селектор цифрових косинусних та синусних відліків гетеродинного сигналу, підключений входами cos, sin відповідно до виходів u, v блоку постійної пам'яті косинусних та синусних відліків гетеродинного сигналу, помножувач - накопичувач цифрового квадратурного перетворення частоти, з'єднаний першим входом посередництвом шини даних з М виходами М канального формувача цифрових комплексних сигналів, а другим входом - з виходом селектора цифрових пам'яті косинусних та синусних відліків гетеродинного сигналу. При цьому М - канальний формувач цифрових комплексних сигналів виконано у вигляді М регістрів канальних синфазних відліків , М регістрів канальних квадратурних відліків , входи яких об'єднано та підключено до виходів відповідного канального АЦП, М селекторів канальних синфазних відліків , та канальних квадратурних відліків , з'єднаних першим входом з виходом регістра канального синфазного відліку , другим входом - з виходом регістра канального квадратурного відліку відповідного каналу, виходами підключених до шини даних. Арифметичний блок виконано у вигляді блоку оперативної пам'яті вхідних та проміжних комплексних відліків швидкого перетворення Фур'є (ШПФ), помножувача - накопичувача ШПФ, регістра дійсних відліків ШПФ Re, регістра уявних відліків ШПФ Іm, селектора дійсних та уявних відліків ШПФ, блоку постійної пам'яті обертаючих множників ШПФ, блоку постійної пам'яті комплексних спектрів амплітудно фазових розподілів, блоку управління, синхровиходи якого посередництвом шини управління підключено до синхровходів М канальних АЦП, до синхровходів М регістрів канальних синфазних відліків , М регістрів канальних квадратурних відліків , регістра дійсних відліків ШПФ Re, регістра уявних відліків ШПФ Іm, до синхровходів помножувача накопичувача цифрового квадратурного перетворювання частоти, помножувача - накопичувана ШПФ. Синхровиходи та адресні виходи блоку управління посередництвом шини управління підключено до синхровходів та адресних входів М селекторів канальних синфазних відліків , та канальних квадратурних відліків , селектора цифрових косинусних та синусних відліків гетеродинного сигналу, селектора дійсних та уявних відліків ШПФ, до синхровходів та адресних входів блоку постійної пам'яті косинусних та синусних відліків 7 гетеродинного сигналу, блоку оперативної пам'яті вхідних та проміжних комплексних відліків ШПФ, блоку постійної пам'яті обертаючих множників ШПФ, блоку постійної пам'яті комплексних спектрів амплітудно фазових розподілів точної стабілізації, а вхід сполучено з джерелом управляючих сигналів - . При цьому вихід блоку постійної пам'яті обертаючих множників ШПФ об'єднано з виходом блоку постійної пам'яті комплексних спектрів амплітудно фазових розподілів точної стабілізації і підключено до другого входу помножувача - накопичувача ШПФ, який з'єднано першим входом з виходом блоку оперативної пам'яті вхідних та проміжних комплексних відліків ШПФ, а виходом з входами даних регістра дійсних відліків ШПФ Re та регістра уявних відліків Іm, виходи яких з'єднано з входами селектора дійсних та уявних відліків ШПФ, вихід якого об'єднано з виходом помножувача - накопичувача цифрового квадратурного перетворювання частоти і підключено до входу даних блоку оперативної пам'яті вхідних та проміжних комплексних відліків ШПФ. Пропоноване технічне рішення пристрою цифрового формування променів ілюструється наступними графічними матеріалами: На Фіг.1 представлена структура пристрою цифрового формування променів, на Фіг.2 представлена часова діаграма роботи пристрою цифрового формування променів, на Фіг.3 представлені: неперервна тонка лінія uo - вхідний (синфазний) неперервний сигнал пристрою цифрового формування променів, неперервна товста лінія u1 - послідовність відліків синфазного сигналу, дискретизованого з частотою F1.д=4∙fo, де fo середня частота смугового сигналу, переривчаста лінія v1 - послідовність відліків вхідного сигналу, затриманих на період дискретизації =1/F1.д, пунктирна лінія vo - неперервний квадратурний сигнал, що відповідає послідовності затриманих відліків v1 . на Фіг.4 представлені: неперервна тонка лінія uo - вхідний неперервний сигнал пристрою цифрового формування променів, неперервна товста лінія U0 - синфазний сигнал, гетеродинований в окіл нульової частоти (дійсна частина комплексної огинаючої), переривчаста лінія V0 квадратурний сигнал, гетеродинований в окіл нульової частоти (уявна частина комплексної огинаючої), на Фіг.5 представлено розподіл модуля вихідних сигналів пристрою цифрового формування М=64-х променів, як функція номера променю еквідистантної, кругової решітки з хвильовим розміром кругової бази D/ =6.4, що утворені секторами з 21-го елементу методом кругової згортки в частотній області для 3 - х кутів одночасного приходу сигналів 1=174.375°, 2=286.875°, 3=354.375°, на Фіг.6 представлена таблиця порівняння характеристик пристрою цифрового формування прототипу та пропонованого рішення для 64-х променевої кругової ЦФАР гідроакустичної станції. Пристрій цифрового формування променів містить М - канальний формувач цифрових комплексних сигналів 1, складений з М канальних аналого цифрових перетворювачів (АЦП) 2, з'єднаних входами з виходами М канальних підсилювачів, ари 55954 8 фметичний блок 3. Пристрій також містить цифровий квадратурний перетворювач частоти 4, що містить блок постійної пам'яті косинусних та синусних відліків гетеродинного сигналу 5, селектор цифрових косинусних та синусних відліків гетеродинного сигналу 6, підключений входами cos, sin відповідно до виходів u, v блоку постійної пам'яті косинусних та синусних відліків гетеродинного сигналу 5, помножувач - накопичувач цифрового квадратурного перетворення частоти 7, з'єднаний першим входом посередництвом шини даних з М виходами М - канального формувача цифрових комплексних сигналів 1, а другим входом - з виходом селектора цифрових косинусних та синусних відліків гетеродинного сигналу 6. При цьому М канальний формувач цифрових комплексних сигналів 1 виконано у вигляді М регістрів канальних синфазних відліків , 8, М регістрів канальних квадратурних відліків 9, входи яких об'єднано та підключено до виходу відповідного канального АЦП 2, М селекторів канальних синфазних відліків , та канальних квадратурних відліків 10, сполучених першим входом з виходом канального синфазного відліку 8, другим входом - з виходом регістру канального квадратурного відліку 9 відповідного каналу, виходами підключених до шини даних. Арифметичний блок 3 виконано у вигляді блоку оперативної пам'яті вхідних та проміжних комплексних відліків швидкого перетворення Фур'є (ШПФ) 11, помножувача-накопичувача ШПФ 12, регістра дійсних відліків ШПФ Re 13, регістра уявних відліків ШПФ Іm 14, селектора дійсних та уявних відліків ШПФ 15, блоку постійної пам'яті обертаючих множників ШПФ 16, блоку постійної пам'яті комплексних спектрів амплітудно фазових розподілів точної стабілізації 17, блоку управління 18, синхровиходи якого посередництвом шини управління підключено до синхровходів М канальних АЦП 2, до синхровходів М регістрів канальних синфазних відліків 8, М регістрів канальних квадратурних відліків 9, регістра дійсних відліків ШПФ Re 13, регістра уявних відліків ШПФ Іm 14, до синхровходів помножувача - накопичувача цифрового квадратурного перетворювання частоти 7, помножувача - накопичувача ШПФ 12, синхровиходи та адресні виходи блоку управління 18 посередництвом шини управління підключено до синхровходів та адресних входів М селекторів канальних синфазних відліків , та канальних квадратурних відліків 10, селектора цифрових косинусних та синусних відліків гетеродинного сигналу 6, селектора дійсних та уявних відліків ШПФ 15. Синхровиходи та адресні виходи блоку управління 18 підключено також до синхровходів та адресних входів блоку постійної пам'яті косинусних та синусних відліків гетеродинного сигналу 5, блоку оперативної пам'яті вхідних та проміжних комплексних відліків ШПФ 11, блоку постійної пам'яті обертаючих множників ШПФ 16, блоку постійної пам'яті комплексних спектрів амплітудно фазових розподілів точної стабілізації 17, а вхід сполучено з джерелом управляючих сигналів - . При цьому вихід блоку постійної пам'яті обертаючих множників ШПФ 16 9 55954 об'єднано з виходом блоку постійної пам'яті комплексних спектрів амплітудно фазових розподілів точної стабілізації 17 і підключено до другого входу помножувача - накопичувача ШПФ 12, який з'єднано першим входом з виходом блоку оперативної пам'яті вхідних та проміжних комплексних відліків ШПФ 11, а виходом з входами даних регістра дійсних відліків ШПФ Re 13 та регістра уявних відліків ШПФ Іm 14, виходи яких з'єднано з входами селектора дійсних та уявних відліків ШПФ 15, вихід якого об'єднано з виходом помножувача накопичувача цифрового квадратурного перетворювання частоти 7 і підключено до входу даних блоку оперативної пам'яті вхідних та проміжних комплексних відліків ШПФ 11. Пристрій цифрового формування променів Мканальної кругової антени функціонує в такий спосіб. За даними про кут повороту антени , що над S ,k B e i o / c sin k ) e i2 [k( )]=k( )∙ ; (10) Пристрій цифрового формування променів ФАР в кожному періоді дискретизації Т=1/Fд формує М канальних, цифрових, комплексних сигналів, квадратурно гетеродинує цифрові, комплексні сигнали на нульову частоту, формує М променів, стабілізованих по куту круговою згорткою комплексної функції m канального амплітудно фазового розподілу з просторовою реалізацією М відліків комплексної огинаючої кругової решітки в області просторових частот. Формування М канальних, цифрових, комплексних сигналів. Блок управління 18 формує на синхровходах канальних АЦП 2 періодичну, з частотою дискретизації Fд послідовність парних синхроімпульсів Ф1, Ф2 з часовим зсувом між ними 1. 1=1/4∙fo; (11) fo - середня частота сигналу зі смугою Dfo. На часовому інтервалі 1 неперервні, вихідні, дійсні коливання канальних підсилювачів - х( , t) канальними АЦП 2 синхронно дискретизуються з часовим зсувом 1, перетворюються у цифрові відліки і записуються до М регістрів канальних синфазних відліків 8 по синхроімпульсу Ф1, до М регістрів канальних квадратурних відліків 9 по синхроімпульсу Ф2, утворюючи в такий спосіб М wn e i ГТН nT un i v n;un cos ГТН n T ; v n Селектор цифрових відліків синфазного u(n) та квадратурного v(n) відліків гетеродинного сигналу 6 послідовно підключає виходи u, v блоку постійної пам'яті косинусних та синусних відліків гетеродинного сигналу w(n) 5 до другого входу помножувача - накопичувача квадратурного перетворювання частоти 7. Помножувач - накопичувач 10 ходить від датчика кута з періодом ∆ 5мс, блок управління 18 розраховує код грубої стабілізації ∆m( ) та адреси запису ( ) для блоку оперативної пам'яті вхідних та проміжних відліків комплексних сигналів ШПФ 11 і код точної стабілізації - адресу k( ) для блоку постійної пам'яті комплексних, попередньо розрахованих спектрів амплітудно фазових розподілів точної стабілізації S[ , k( )] 17. У випадку лінійної решітки код грубої стабілізації ∆m( ) 0, і адреси запису для блоку оперативної пам'яті вхідних та проміжних відліків комплексних сигналів ШПФ 11 не залежать від . ∆m( )=entire ( /∆ ); ∆ =2∙ /М; (6) → ( )=mod [ +∆m( ), M]; (7) k( )=entire {[ -∆ ∙∆m( )]/ }; (8) entire(x ) - ціла частина числа х. - точність стабілізації / M; , 0,...M 1 ; (9) канальних, цифрових, комплексних сигналів ( , ). Т = Fд-1; t → n∙T = tn; n = 1/Т; (12) х( , t) → х ( , n) → ( , n); ( , n) = ( , n - n); (13) ( , n) = ( , n) + i∙ ( , n); (14) = 0,…М-1; = 0,1,… У вузько смуговому наближенні - Dfo ≤ 0.1∙fo (15) o = 2∙ ∙fo; o∙ 1 = /2; ( , n) А(n)∙cos[ o∙n∙Т + o/с∙ ∙cos( - Ф)]; (16) З врахуванням (13), (15) ( , n) А(n)∙cos[ o∙(n - n)∙Т + (17) o/c∙ ∙cos( - Ф)] = А(n)∙sin[ o∙n∙Т + o/c∙ ∙cos( - Ф)]; А(n) - миттєва амплітуда в n -й момент часу, і = √-1; Ф - кут приходу сигналу. Квадратурне гетеродинування На часовому інтервалі 2 по синхросигналам та адресним командам блоку управління 18 дійсні відліки ( , n) та уявні відліки ( , n) через селектори канальних синфазних відліків та канальних квадратурних відліків 10 поступають на перший вхід помножувача - накопичувача квадратурного перетворювання частоти 7. Синхронно блок постійної пам'яті косинусних та синусних відліків гетеродинного сигналу w(n) 5 формує на своїх виходах u, v послідовність цифрових відліків синфазного u(n) та квадратурного v(n). гетеродинного сигналів. sin ГТН n T ; (18) квадратурного перетворення частоти 7 за командами на його синхровходах від блоку управління 18 послідовно перемножує відліки канальних комплексних сигналів ( , n) з відліками комплексного гетеродинного сигналу w(n). 11 55954 ' 12 ' ,n ,n w n ,n i ,n un ' ,n ,n u n ,n A n cos ,n A n sin i vn ' ГТН n T o/с cos Ф /с cos Ф ' За умови o ,n o ГТН A n cos o / с o ,n A n sin /с cos cos Ф Ф ; ; (24) (25) (26) o ,n o ,n i o ,n ; Ф-ли (24), (25) визначають відповідно синфазний о( , n) та квадратурний о( , n) відліки комплексної огинаючої о( , n) вихідного дійсного сигналу - го канального підсилювача х(( , n). Дійсні - о( , n) та уявні - о( , n) відліки комплексної огинаючої о( , n) канальних сигналів з виходу помножувача - накопичувача квадратурного перетворення частоти 7 командами на його синхровходах з виходів блоку управління 18 записуються в блок оперативної пам'яті вхідних та проміжних відліків комплексних сигналів та ШПФ 11 синхросигналами за адресами mod [∆m( ) + , М], на його управляючих входах, сформованими блоком управлінням 18, що забезпечує «грубу» компенсацію повороту антени на кут . Кругова згортка в області просторових частот формування променів На першому етапі часового інтервалу виконання кругової згортки – 3 арифметичний блок 3 виконує пряме дискретне перетворення Фур'є на масиві М просторових відліків комплексної огинаючої канальних сигналів { о( , n) n - го періоду дискретизації Т методом ШПФ за адресними командами та синхросигналами, що їх блок управління 18 формує на відповідних управляючих входах блоку оперативної пам'яті вхідних та проміжних комплексних відліків ШПФ 11, блоку постійної пам'яті обертаючих множників 16, помножувача - накопичувача ШПФ 12, регістра дійсних відліків ШПФ Re 13, регістра уявних відліків ШПФ Im 14, селектора дійсних та уявних відліків ШПФ 15. ; W e i 2 /M; Z n, o ,n W (27) , 0,1 M 1 ; ,... (28) Re Z n, i Im Z n, ; Помножувач - накопичувач ШПФ 12 виконує М/2∙ℓn2 М базових операцій ШПФ -«метелик» на множині вихідних відліків блоку оперативної пам'яті вхідних та проміжних комплексних відліків ШПФ 11 на своєму першому вході та вихідних відліках Z n, ,n ; ,n ,n v n ,n u n ; з врахуванням(16) - (18) ГТН n T o i ' (20) ,n v n ; ' ,n (19) (21) (22) ; (23) ; блоку постійної пам'яті обертаючих множW ників 16 на своєму другому вході. Проміжні результати обчислень з виходу помножувача - накопичувача ШПФ 12 заносяться: дійсні - в регістр дійсних відліків ШПФ Re 13, уявні - в регістр уявних відліків ШПФ Im 14 і через селектор дійсних та уявних відліків ШПФ. 15 записуються в блок оперативної пам'яті вхідних та проміжних комплексних відліків ШПФ 11 за адресами даних попереднього кроку обчислень, що більше не використовуються згідно графу ШПФ. На другому етапі часового інтервалу виконання кругової згортки - 3 арифметичний блок 3 за адресними командами та синхросигналами, що їх блок управління 18 формує на відповідних управляючих входах блоку оперативної пам'яті комплексних даних ШПФ 11, блоку постійної пам'яті комплексних спектрів амплітудно фазових розподілів точної стабілізації 17, помножувача - накопичувача ШПФ 12, регістра дійсних обчислюваних відліків Re 13, регістра уявних обчислюваних відліків Im 14, селектора дійсних та уявних відліків ШПФ 15, розраховує комплексний спектр кругової згортки E(n, ,k). Помножувач - накопичувач ШПФ 12 виконує множення вихідних комплексних відліків попередньо розрахованого спектру Z(n, ) блоку оперативної пам'яті комплексних даних ШПФ 11 на своєму першому вході та вихідних відліків S[ ,k( )] блоку постійної пам'яті комплексних спектрів амплітудно фазових розподілів точної стабілізації 17 на своєму другому вході за ф-ми (30), (31). E[n, ,k( )] = Z(n, )∙S( , k( ))] = G[ , k( )] + (29) і∙H[( , k( )]; G[ , k( )] = Re Z(n, )∙e [S ( , k( ))] - Im[Z(n, (30) )]∙Im[S( , k( ))]; H[ , k( )] = Re [Z(n, )]∙Im[S( , k( ))] + Im[Z(n, (31) )]∙Re[S( , k( ))]; Дійсні складові G( , k) та уявні складові H( , k) комплексних добутків E(n, ,k)} з виходу помножувача - накопичувана ШПФ 12 заносяться: дійсні - в регістр дійсних відліків ШПФ Re 13, уявні - в регістр уявних відліків ШПФ Im 14 і через селектор дійсних та уявних відліків ШПФ 15 записуються в блок оперативної пам'яті вхідних та проміжних комплексних відліків ШПФ 11 відповідно за адресами даних Re [Z(n, )], Im[Z(n, )], відпрацьованих на попередньому кроці обчислень. На третьому етапі часового інтервалу виконання кругової згортки – 3 арифметичний блок 3 13 55954 виконує зворотне дискретне перетворення Фур'є на масиві М комплексних добутків {Е(n, ,k)} n - го періоду дискретизації Т за адресними командами та синхросигналами, що їх блок управління 18 формує на відповідних управляючих входах блоку оперативної пам'яті вхідних та проміжних комплексних відліків ШПФ 11, блоку постійної пам'яті обертаючих множників 16, помножувача - накопичувача ШПФ 12, регістра дійсних відліків ШПФ Re 13, регістра уявних відліків ШПФ Im 14, селектора дійсних та уявних відліків ШПФ 15. (32) W * (e i 2 / M )* ei 2 / M ; R n, k, 1/ M E n, , k W * ; (33) 0,1 M 1 ; ,... Помножувач - накопичувач ШПФ 12 виконує базову операцію ШПФ - «метелик» на вихідних відліках блоку оперативної пам'яті комплексних даних ШПФ 11 на своєму першому вході та вихідних відліках (W )* блоку постійної пам'яті обертаючих множників 16 на своєму другому вході. Дійсні - Re[R (n,k, )] та уявні - Im[R (n,k, )] відліки - го променю R(в,к, ) в регістрі дійсних о відліків ШПФ Re 13, в регістрі уявних відліків ШПФ Im 14, сформовані зворотним перетворенням Фур'є, через селектор дійсних та уявних відліків ШПФ 15 поступають на вихід цифрового формувача ФАР. Базова операція ШПФ - «метелик» зводиться до q1 арифметичних операцій з комплексними числами: 1-му множенню та 2 - м додаванням. q1=3; М = 2g точкове ШПФ вимагає q2 базових операцій «метелик». [5] q2=М/2∙ℓn2М; Повний алгоритм цифрового формування М променів включає: М комплексних множень квадратурного перетворення частоти, 2∙q1∙q3 арифметичних операцій з комплексними числами прямого - зворотного ШПФ, М комплексних множень комплексних відліків спектру ШПФ просторової реалізації відліків із комплексними відліками спектру амплітудно фазового розподілу за період дискретизації Т=1/Fд Число комплексних арифметичних операцій за 1 сек у пропонованому пристрої цифрового формування променів складає Qмодель оп/сек Qмодель = (M + 2∙q1∙q2 + M) / T = М∙(2 (34) +3∙ℓn2М)∙Fд. винахід., (оп/сек); Вузько смугові сигнали відповідають умові Df ≤ 0.1∙fo; Відліки о( , n), о( , n) комплексної огинаючої канальних сигналів о( , n) статистично незалежні і частота дискретизації за Котельниковим, що вимагає 2-х незалежних відліків за період найвищої частоти в спектрі сигналу, може бути вибрана з умови Fд. модель. ≥ Df = 0.1∙fo; (35) Число комплексних арифметичних операцій за 1 сек в пристрої - прототипі цифрового формування променів методом прямого обчислення кругової згортки m відліків комплексного амплітудно фазового розподілу з вибіркою М комплексних відліків кругової решітки складає Q (р)прототип. (оп/сек.) 14 Q (р)прототип. = М/2∙2∙m∙F(p)д. прототип., (оп/сек.); F(р)прототип. = 4∙fo/2∙р + 1 > 2∙Dfo; p = 0,1,.. Виграш в числі комплексних операцій складає числ (р) числ (р) = Q (р)прототип./Qмодель. = m∙40/(2∙р + (36) 1)∙(2 + 3∙ℓn2 М); В пристрої, що заявляється найменша частота дискретизації Fд.винахід., комплексної огинаючої вузько смугового сигналу з середньою частотою вхідного сигналу - fo = 3.2∙104Гц, смугою – Dfo = 3∙103Гц, для якого відносна смуга складає Df/fo=0.0625, може бути вибраною згідно (35) Fд. модель. = 0.1∙fo = 3.2∙103Гц. За тих же умов: fo = 3.2∙104Гц, Dfo = 3∙103Гц найменша частота дискретизації «за смугою» в пристрої прототипі згідно (1) відповідає значенню р = 9 і дорівнює F(p)д.прототип. = 4∙fo/(2∙р + 1) = 4∙3.2∙104/(2∙9 + 1) = 1.28∙105/19 = 6736.84 > 2∙Dfo = 6∙103 Гц; Для m = 21; М = 64; р = 9; числ(р) = m∙40/(2∙р + 1)∙(2+3∙ℓn2M) 2; Множення 2-х комплексних чисел зводиться до 6 - ти арифметичних дій з дійсними числами. q (комплексне множення) = 6 арифметичних дій з дійсними числами. Базова операція ШПФ - «метелик», еквівалентна 1-му комплексному множенню та 2 - м комплексним складанням, зводиться до 10 - ти арифметичних дій з дійсними числами q(комплексний «метелик») = 10 арифметичних дій з дійсними числами. Кругова згортка в області просторових частот методом ШПФ включає 2 - і процедури М точкового ШПФ та пряме множення 2-х комплексних М елементних спектрів і вимагає q(Т) арифметичних дій з дійсними числами за період дискретизації Т. q(Т) = 2∙М/2∙ℓn2М∙q(комплексний «метелик») + (37) М∙q (комплексне множення); Для М = 64 q(T) = 64∙6∙10 + 64∙6 = 4224; За 1 сек арифметичний блок 3 виконує Q оп/сек. Q = q(Т)∙Fд модель.; (38) Для М= 64; q(Т) = 4224; Fд.модель. = 3.2∙103Гц Q = 4224∙3.2∙103 = 13516 800 14∙106 оп/сек = 14 MIPS Помножувач - накопичувач за 1 - ну команду виконує множення - додавання і потрібна продуктивність арифметичного блоку на його базі не більша від 10 106 команд/сек. Цифровий, квадратурний перетворювач частоти 4 та арифметичний блок 3 можуть бути реалізовані, наприклад, на базі сигнальних процесорів ADSP 218хх продуктивністю Q = (20-30) MIPS, які мають у своєму складі один помножувач - накопичувач кожний [6] Пристрій цифрового формування М=64 променів кругової ФАР згідно пропонованої корисної моделі має у своєму складі: - помножувачів - накопичувачів - 2, - блоків постійної пам'яті - 3, - блоків оперативної пам'яті - 1, всього 6 компонентів цифрової техніки високої складності. Пристрій цифрового формування М=64 променів кругової ФАР прототипа має у своєму складі: - помножувачів - М, - сумматорів - 3∙М/2, 15 - блоків постійної пам'яті - М, всього 7∙М/2 компонентів цифрової техніки високої складності. Виграш в апаратному складі пропонованого цифрового пристрою у випадку М - канальної кругової ФАР відносно прототипу становить апар.. апар. = 7∙М/12; Для М = 64; апар. 37; Технічний результат - скорочення числа помножувачів, суматорів, блоків пам'яті в пристрої формування променів М - канальної кругової решітки відносно прототипу з арифметичним блоком в складі М/2 двох променевих формувачів прямої згортки досягнуто введенням цифрового, квадратурного перетворювача несучої частоти цифрових, комплексних, канальних сигналів на нульову частоту з попереднім прорідженням потоку даних М канальним формувачем комплексних сигналів, що зменшує кількість арифметичних операцій, необхідних для формування J=М променів в "реальному часі", та арифметичним блоком, що формує на відліках комплексної огинаючої канальних сигналів 55954 16 стабілізовані промені круговою згорткою в області просторових частот методом ШПФ. Джерела інформації: 1. Патент на корисну модель UA №46669 МПК Н01 Q 3/26, Н01 Q 21/00, G06 F 17/00. Публ. Бюл. №24. 2009р. 2. Патент на винахід UA №24895 А МПК H01 Q 21/00, G01 S 3/00, G06 F 17/14. Публ. Бюл. №0. 1998р. 3. Авторское свидетельство SU №1070494. МПК G01 S 3/80. Публ Бюл. №4.1984г. 4. Зиновьев А.П. Филиппов Л.И. Введение в теорию сигналов и цепей. с. 42, Москва «Высшая школа». 1975. 5. Солонина А.И, Улахович Д.А., Арбузов С.М., Соловьѐва Е.Б. Основы цифровой обработки сигналов, с. 208.Санкт - Петербург «БХВ - Петербург» 2003. 6. Корнеев В.В., Киселѐв А.В. Современные микропроцессоры, с. 311, 312. Санкт - Петербург «БХВ - Петербург» 2003. 17 55954 18 19 55954 20 21 55954 22 23 Комп’ютерна верстка М. Ломалова 55954 Підписне 24 Тираж 26 прим. Міністерство освіти і науки України Державний департамент інтелектуальної власності, вул. Урицького, 45, м. Київ, МСП, 03680, Україна ДП “Український інститут промислової власності”, вул. Глазунова, 1, м. Київ – 42, 01601

ДивитисяДодаткова інформація

Назва патенту англійськоюDevice for beams digital forming

Автори англійськоюFaleev Ihor Mykhaiklovych, Kovalchuk Kostiantyn Volodymyrovych, Zatserkovskyi Ruslan Oleksiiovych, Zubchenko Ihor Vasyyliovych, Khalilov Eduard Mahheramovych, Pavliuk Oleh Yevhenovych, Karpenko Yevhen Valeriiovych, Solovei Volodymyr Yukhymovych

Назва патенту російськоюУстройство цифрового формирования лучей

Автори російськоюФалеев Игорь Михайлович, Ковальчук Константин Владимирович, Зацерковский Руслан Алексеевич, Зубченко Игорь Васильевич, Халилов Эдуард Маггерамович, Павлюк Олег Евгениевич, Карпенко Евгений Валериевич, Соловей Владимир Ефимович

МПК / Мітки

МПК: G01S 15/00

Мітки: променів, формування, пристрій, цифрового

Код посилання

<a href="https://ua.patents.su/12-55954-pristrijj-cifrovogo-formuvannya-promeniv.html" target="_blank" rel="follow" title="База патентів України">Пристрій цифрового формування променів</a>

Попередній патент: Пристрій для подачі води

Наступний патент: Пристрій для отримання водню і чадного газу із водно-вугільної суспензії

Випадковий патент: Спосіб одержання вуглецевої волокнистої структури з целюлозного попередника