Пристрій паралельно-ієрархічного кодування-декодування інформації

Номер патенту: 99547

Опубліковано: 27.08.2012

Автори: Макаренко Роман Вікторович, Тимченко Леонід Іванович, Загоруйко Тетяна Андріївна, Кокряцька Наталья Іванівна

Формула / Реферат

Пристрій паралельно-ієрархічного кодування-декодування інформації, що містить перший та другий блоки пам'яті, входи читання та запису, інформаційні вхід і вихід, який відрізняється тим, що в нього введено блок комутації, блок перетворення інформації, генератор та блок декодування, вихід якого підключений до виходу пристрою, перший вхід підключений до виходу першого блока пам'яті, а другий і третій входи відповідно з'єднані з виходами другого блока пам'яті, вихід генератора з'єднаний з п'ятими входами блока комутації, першого блока пам'яті і другого блока пам'яті, вхід запису з'єднаний з першим входом генератора, четвертим входом блока комутації, а також з третіми входами першого і другого блоків пам'яті, вхід читання підключений до другого входу генератора, п'ятих входів першого і другого блоків пам'яті, перший вихід блока перетворення інформації з'єднаний з першим входом першого блока пам'яті, другий вихід блока перетворення інформації підключений до першого входу другого блока пам'яті, третій і четвертий виходи блока перетворення інформації з'єднані відповідно з другим та третім входами блока комутації, другий і третій виходи якого підключені відповідно до першого та другого входів блока перетворення інформації, а перший вихід блока комутації підключений до других входів першого і другого блоків пам'яті.

Текст

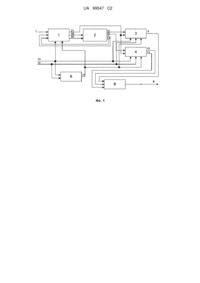

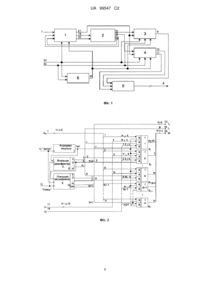

Реферат: Пристрій паралельно-ієрархічного кодування-декодування інформації належить до галузі обчислювальної техніки, пристрої пам'яті та обробки зображень, системи передачі даних. Пристрій паралельно-ієрархічного кодування-декодування інформації містить блок комутації, блок перетворення інформації, два блоки пам'яті, генератор, блок декодування, інформаційний вхід, входи запису і читання, а також вихід пристрою. За допомогою запропонованого пристрою досягається ущільнення інформації, а також забезпечення кращої швидкодії за рахунок введення в нього двох блоків пам'яті для паралельного збереження даних. UA 99547 C2 (12) UA 99547 C2 UA 99547 C2 5 10 15 20 25 30 35 40 45 50 55 60 Винахід належить до галузі обчислювальної техніки і може бути використаний в пристроях пам'яті та обробки зображень в системах передачі даних. Відомий універсальний пристрій кодування сигналів (патент РФ № 2037270, кл. 6 Н03М 9/00, G08В 25/10, 1993 p., Бюл. № 16), що містить перший блок регістрів, перший керуючий вхід якого є першим керуючим входом пристрою, перший регістр зсуву, лічильник і мультиплексор, подільники частоти, другий блок регістрів, формувач стробів, другий блок регістрів, регістр і формувач управляючих сигналів, інформаційні входи якого об'єднані з відповідними першими адресними входами першого і другого блока регістрів і є адресною шиною пристрою, другим і третім керуючими входами якого є перший і другий керуючі входи формувача керуючих сигналів, третій керуючий вхід якого з'єднаний з першим виходом формувача стробів, а перший, другий і третій виходи з'єднані відповідно із входами дозволу завантаження лічильника, другим керуючим входом першого лока регістрів і керуючим входом другого лока регістрів, другі адресні входи якого з'єднані з відповідними виходами першої групи виходів формувача стробів, а інформаційні входи об'єднані з відповідними інформаційними входами першого регістра зсуву і спільно з виходами першого блока регістрів є шиною обміну пристрою, тактовою шиною якого є тактовий вхід подільника частоти, вхід дозволу передустановки якого об'єднаний з першим керуючим входом першого блока регістрів і об'єднаний з входом зсуву першого регістра зсуву, перший керуючий вхід якого з'єднаний з четвертим виходом формувача керуючих сигналів, другий керуючий вхід якого - з другим виходом формувача стробів, перша група виходів - з відповідними входами перших інформаційних входів регістра, а друга група виходів - з відповідними адресними входами мультиплексор і відповідними входами групи входів формувача стробів, перший вхід якого об'єднаний з керуючим входом регістра, лічильним входом лічильника і підключений до першого виходу подільника частоти, виходи з другого по п'ятий якого з'єднані з відповідними інформаційними входами мультиплексор, перший вихід якого з'єднаний з тактовим входом другого регістра зсуву, а другий вихід - з другим входом формувача стробів, третій вхід якого з'єднаний з виходом позичення лічильника, входи передустановки якого з'єднані з відповідними виходами другого блока регістрів, при цьому четвертий вхід формувача стробів об'єднаний з першим керуючим входом першого блока регістрів, другі адресні і інформаційні входи якого з'єднані з відповідними виходами першої і другої груп виходів регістра відповідно, другі і треті інформаційні входи регістра з'єднані з відповідними входами відповідно другого регістра зсуву і другої групи виходів формувача стробів, третій вихід якого з'єднаний з третім керуючим входом першого лока регістрів, а четвертий вихід - з першим стробуючим входом мультиплексора, другий стробуючий вхід якого є шиною нульового потенціалу, причому інформаційний вхід другого регістра зсуву є інформаційним входом пристрою. Недоліком даного пристрою є низька швидкодія, яка обумовлена тим, що перед черговим циклом часової згортки виконується установка пристрою в вихідний стан. Відомий кодер (А. с. СРСР № 1783628, кл. 5 Н03М 13/00, 1992 р., Бюл. № 47), який містить перший тригер, накопичувач, інформаційні входи якого об'єднані з першими інформаційними входами першого регістра і є інформаційними входами пристрою, виходи накопичувача підключені до перших входів першого формувача імпульсів, виходи якого підключені до першого входу першого елемента І, суматор, вихід якого з'єднаний з інформаційним входом другого регістра, виходи якого з'єднані з першими входами другого формувача імпульсів, вихід якого підключений до першого входу другого елемента І, вихід якого і вихід першого елемента І підключені до першого і другого входам елемента АБО, вихід якого є виходом пристрою, третій регістр, блок порівняння, лічильник імпульсів, другий тригер, третій і четвертий формувачі імпульсів, комутатор, третій і четвертий елементи І і дешифратор, інформаційні входи третього регістра і першого тригера і перші входи третього і четвертого елементів І є відповідно входом встановлення, входом запуску, керуючим і тактовим входами пристрою, виходи третього регістра підключені до перших входів блока порівняння і входам дешифратора, виходи якого підключені до других входів першого і другого формувача імпульсів, першим входам третього формувача імпульсів і першій групі входів комутатора, виходи лічильника імпульсів підключені до других входів блока порівняння, вихід якого підключений до входу обнуління лічильника імпульсів і входу другого тригера, прямий вихід якого підключений до другого входу другого елемента І, інверсний вихід підключений до другого входу першого елемента І і входу четвертого формувача імпульсів, вихід якого з'єднаний з входами обнулення накопичувача, першого і другого регістрів і першого тригера, прямий і інверсний виходи якого підключені відповідно до других входів четвертого і третього елементів І, вихід третього елемента І підключений до тактових входів лічильника імпульсів, накопичувача, другого і першого регістрів, виходи першого регістра підключені до другої групи входів комутатора і других входів третього 1 UA 99547 C2 5 10 15 20 25 30 35 40 45 50 55 формувача імпульсів, виходи яких підключені відповідно до входів суматора і другого інформаційного входу першого регістра. Недоліком даного пристрою є низька швидкодія, яка обумовлена послідовним характером виконання операції кодування декодування інформації. Найбільш близьким за технічною суттю до заявленого винаходу є пристрій кодуваннядекодування числових послідовностей (А. с. СРСР № 1809541, кл. 5 Н03М 13/00, 1990 р., Бюл. № 14), що містить перший регістр, виходи якого з'єднані з першими адресними входами першого лока пам'яті, виходи якого підключені до перших входів суматора, перший лічильник імпульсів, виходи якого з'єднані з входами першого дешифратора, перший і другий виходи якого підключені до перших входів відповідно першого і другого елементів І, виходи яких з'єднані відповідно з першим і другим входами першого елемента АБО, вихід якого з'єднаний через перший елемент затримки із лічильним входом другого лічильника імпульсів, виходи якого з'єднані з входами другого дешифратора, вихід якого з'єднаний із лічильним входом третього лічильника імпульсів, виходи якого з'єднані з входами третього дешифратора і другими адресними входами першого блока пам'яті, перші адресні входи другого блока пам'яті об'єднані з адресними входами третього блока пам'яті, перші виходи третього блока пам'яті з'єднані з першими входами блока порівняння, перший елемент НІ, вхід якого об'єднаний з другим входом першого елемента І, вихід першого елемента НІ з'єднаний з другим входом другого елемента І, третій елемент І, вихід якого з'єднаний з першим входом другого елемента АБО, четвертий елемент І, вихід з'єднаний з першим входом третього елемента АБО, другий елемент НІ, вихід якого з'єднаний з першим входом п'ятого елемента І, шостий елемент І, вихід кого з'єднаний з першим входом четвертого елемента АБО, другий регістр, другий і третій елементи затримки, четвертий блок пам'яті, сьомий елемент І, а також п'ятий і шостий блоки пам'яті, елемент АБОНІ і четвертий елемент затримки, інформаційні входи першого регістра є інформаційними входами пристрою, входи зсуву інформації першого, другого регістрів і лічильний вхід першого лічильника імпульсів об'єднані і є входами синхронізації пристрою, інформаційні входи другого блока пам'яті підключені до відповідних виходів першого регістра, виходи другого блока пам'яті з'єднані з першими адресними входами шостого блока пам'яті, виходи якого з'єднані з інформаційними входами другого регістра, третій вихід першого дешифратора з'єднаний із входами "Читання" другого і третього блоків пам'яті і через третій елемент затримки - з входом "Читання" шостого блока пам'яті і входом другого елемента затримки, вихід якого з'єднаний з входом "Запис" другого регістра, вихід якого є виходом пристрою, вхід "Читання" першого блока пам'яті, входи "Запис" другого блока пам'яті, другий вхід п'ятого елемента І, перший вхід четвертого елемента І і вхід скиду першого лічильника об'єднані і підключені до виходу першого елемента АБО, вихід третього елемента АБО з'єднаний з входом скиду другого лічильника імпульсів, третій вхід першого елемента АБО, другі входи третього і четвертого елементів АБО об'єднані і є входами початкового встановлення пристрою, перший вихід третього дешифратора з'єднаний з входом другого елемента НІ, другий вихід - з першими входами шостого, сьомого елементів І і входом першого елемента НІ, другі входи четвертого, шостого елементів І об'єднані і підключені до виходу другого дешифратора, вихід четвертого елемента АБО підключений до виходу скиду третього лічильника, вхід "Запис" четвертого блока пам'яті об'єднаний з другим входом сьомого елемента І і підключений до виходу першого елемента затримки, адресні входи четвертого блока пам'яті об'єднані з однойменними входами третього блока пам'яті і підключені до виходів другого лічильника імпульсів, другі адресні входи другого блока пам'яті об'єднаю з другими входами блока порівняння і підключені до виходів третього лічильника, виходи суматора підключені до адресних входів п'ятого блока пам'яті і інформаційним входам четвертого блока пам'яті, виходи якого з'єднані з другими входами суматора, вихід п'ятого елемента І підключений до входу "Читання" четвертого блока пам'яті, вихід сьомого елемента І підключений до входу "Читання" п'ятого блока пам'яті і через четвертий елемент затримки - до входу "Запис" третього блока пам'яті, виходи п'ятого блока пам'яті підключені до інформаційних входів третього блока пам'яті, другі входи якого з'єднані з другими адресними входами шостого блока пам'яті, вихід блока порівняння з'єднаний з першим входом третього елемента І, другий вхід якого з'єднаний з першим входом елемента АБО-НІ і є входом керування режимом пристрою, другий вхід елемента АБО-НІ підключений до виходу першого елемента НІ, вихід другого елемента АБО підключений до третього адресного входу шостого блока пам'яті, вихід елемента АБО-НІ з'єднаний з другим входом другого елемента АБО. Недоліком даного пристрою є низька швидкодія через відсутність паралельно-ієрархічної пам'яті. 2 UA 99547 C2 5 10 15 20 25 30 35 40 45 50 55 В основу винаходу поставлено задачу створення пристрою кодування-декодування інформації, в якому за рахунок введення нових елементів і зв'язків підвищується швидкодія через можливість паралельного збереження і доступу до різноманітних підструктур багатовимірних даних. Поставлена задача вирішується тим, що пристрій паралельно-ієрархічного кодуваннядекодування інформації, що містить перший та другий блоки пам'яті та інформаційний вхід в нього введено блок комутації, блок перетворення інформації, генератор та блок декодування, вихід якого підключений до виходу пристрою, перший вхід підключений до виходу першого блока пам'яті, а другий і третій входи відповідно з'єднані з виходами другого блока пам'яті, вихід генератора з'єднаний з п'ятими входами блока комутації, першого блока пам'яті і другого блока пам'яті, вхід Запис з'єднаний з першим входом генератора, четвертим входом блока комутації, а також з третіми входами першого і другого блоків пам'яті, вхід "Читання" підключений до другого входу генератора, п'ятих входів першого і другого блоків пам'яті, перший вихід блока перетворення інформації з'єднаний з першим входом першого блока пам'яті, другий вихід блока перетворення інформації підключений до першого входу другого блока пам'яті, третій і четвертий виходи блока перетворення інформації з'єднані відповідно з другим та третім входами блока комутації, другий і третій виходи якого підключені відповідно до першого та другого входів блока перетворення інформації, а перший вихід блока комутації підключений до других входів першого і другого блоків пам'яті. На фіг. 1 представлена функціональна схема оперативного запам'ятовуючого пристрою (ОЗП) із ущільненням інформації на основі паралельно-ієрархічного перетворення; на фіг. 2 блок комутації; на фіг. 3 - часова діаграма роботи блока комутації; на фіг. 4 - структурна схема паралельно-ієрархічного (ПІ) перетворення; на фіг. 5 - структурна схема G перетворення; на фіг. 6 - структурна схема вибору елемента; на фіг. 7 - функціональна схема визначення хвостових елементів; на фіг. 8 - функціональна схема комутації для ОЗП чисел; на фіг. 9 функціональна схема комутації для ОЗП масок. Пристрій паралельно-ієрархічного кодування-декодування інформації (фіг. 1) містить блок комутації 1, блок перетворення інформації 2, блок пам'яті 3, блок пам'яті 4, генератор 5 та блок декодування 6, інформаційний вхід 7 пристрою. Вихід 8 блока декодування 6 підключений до виходу пристрою, перший вхід підключений до виходу 9 блока пам'яті 3, а другий і третій входи відповідно з'єднані з 10 і 11 виходами блока пам'яті 4, вихід 12 генератора 5 з'єднаний з п'ятими входами блока комутації 1, блока пам'яті 3 і блока пам'яті 4, вхід 13 "Запис" з'єднаний з першим входом генератора 5, четвертим входом блока комутації 1, а також з третіми входами блока пам'яті 3 і блока пам'яті 4, вхід 14 "Читання" підключений до другого входу генератора 5, п'ятих входів блока пам'яті 3 і блока пам'яті 4, вихід 15 блока перетворення інформації 2 з'єднаний з першим входом блока пам'яті 3, вихід 16 блока перетворення інформації 2 підключений до першого входу блока пам'яті 4, виходи 17 і 18 блока перетворення інформації 2 з'єднані відповідно з та другим та третім входами блока комутації 1, виходи 19 і 20 якого підключені відповідно до першого та другого входів блока перетворення інформації 2, а вихід 21 блока комутації 1 підключений до других входів блока пам'яті 3 і блока пам'яті 4. Пристрій паралельно-ієрархічного кодування-декодування інформації працює таким чином. Вхідна інформація з входу 7 паралельно надходить у блок комутації 1. Далі по входах 19 і 20 інформація надходить в блок перетворення інформації 2, де на виходах 15 і 16 відповідно формуються хвостові елементи А і маски L. Значення хвостових елементів А з виходу 15 блока перетворення інформації 2 і масок елементів L з виходу 16 блока перетворення 2 подаються відповідно в блок пам'яті 3 і блок пам'яті 4. Блок перетворення інформації 2 послідовно формує масиви всіх рівнів, що через виходи 17 і 18, надходять в блок комутації 1 і потім через виходи 19 і 20 блока комутації 1 надходять знову в блок перетворення інформації 2. По конвеєрному принципу відбувається перетворення на всіх рівнях до повної збіжності вхідної інформації, що надходить з входу 7 через вихід 21 блока комутації 1, що з'єднаний з другими входами блока пам'яті 3 і блока пам'яті 4, де і відбувається збіжність вхідної інформації. При цьому активний сигнал "Запис" на вході 13. Значення масок А і хвостових елементів L, що відповідно сформовані на виходах 15 і 16 блока перетворення інформації 2 відповідно, записуються у відповідні блок пам'яті 3 і блок пам'яті 4 по тактових імпульсах генератора 5. При читанні активізується сигнал "Читання" на вході 14 і з блока пам'яті 3, і блока пам'яті 4 у блок декодування 6 надходить інформація з виходу 9 блока пам'яті 3 і виходах 10 і 11 блока пам'яті 4. Там вона перетворюється у початковий вигляд і надходить на вихід 8. 3 UA 99547 C2 5 10 15 20 25 30 35 40 45 50 55 Блок комутації 1 (фіг. 2) здійснює комутацію сигналів на входи 19 і 20 блока перетворення інформації 2. Спочатку на вхід 7 блока комутації 1 комутуються вхідні масиви інформації НМ, потім на другий вхід масиви 1-го рівня U1 і потім на третій вхід масиви всіх інших рівнів U 2. Інформація з входу 7 НМ складається з Н масивів: М1, М2,…, МН, розмірність кожного з який дорівнює m слів (чисел). Розрядність слова К біт. Звідси можлива кількість різноманітних слів K дорівнює N=2 . Математичне моделювання процесу обробки масивів за алгоритмом паралельноієрархічного перетворення показало, що реально число гілок на будь-якому рівні не перевищує чотириразової кількості різноманітних елементів у вхідних масивах. Тобто в розглянутому пристрої передбачається, щo H 4N і m N. Генератор 5 працює на частоті f=1/. Формувач імпульсу 7 (фіг. 2) формує імпульс "Фі" тривалістю при надходженні на його вхід переднього фронту сигналу "Запис". Імпульс від формувача 7 надходить на входи схем І-АБО 8 і комутує на їх входи вхідну інформацію Н М. Задній фронт імпульсу "Фі" запускає в роботу лічильник-дешифратор А9, на виходах якого формуються зсунуті в часі імпульси, тривалістю . На рахунковий вхід лічильника-дешифратора А9 подається меандр від генератора. Імпульси з виходу лічильника-дешифратора А9 надходять на схеми І-АБО 8 і комутують на вихід рознесені в часі масиви 1-го рівня. Імпульс із другого виходу лічильника-дешифратора А9 по задньому фронту запускає в роботу лічильник дешифратор В10, на рахунковий вхід якого подається сигнал від генератора. На виході лічильника-дешифратора В10 формуються сигнали, що комутують на вхід блока перетворення 2 масиви другого і наступних рівнів. Часова діаграма роботи блока 1 подана на фіг. 3. Схема І в блоках I-АБО 8 являє собою набір двовходових вентилів, на один вхід яких подається скомутований сигнал, а на другий вхід - дозвіл. Блок перетворення 2 являє собою пристрій, функціональна схема якого подана на фіг. 4. Цей блок являє собою чисто логічний пристрій без елементів пам'яті. Перетворення в блоці перетворення 2 здійснюється паралельно за конвеєрним принципом. Основним елементом блока перетворення 2 є блок вибору числа з масиву G 11, у якому відбувається вибір числа з масиву і перетворення самого масиву. Всі блоки вибору числа з масиву G 11 ідентичні. Один із варіантів реалізації блока вибору числа з масиву G 11 поданий на фіг. 5. На вході блока вибору числа з масиву G 11 стоїть схема затримки 19, що у сумі з затримкою спрацювання всіх схем блока вибору числа з масиву G 11 дає час у мкс. Затримка потрібна для того, щоб перехідні процеси в попередньому блоці вибору числа з масиву G 11 закінчилися і на вході такого блока вибору числа з масиву G 11 на протязі мкс був стабільний сигнал, що забезпечує надійне зняття інформації. Час спрацювання всіх логічних схем блока вибору числа з масиву G 11 набагато менший за час затримки схеми блока затримки 19. З схеми блока затримки 19 інформація надходить на схему вибору елементу 20. Один із можливих варіантів цієї схеми представлена на фіг. 6. Схема паралельно аналізує всі числа масиву і на вихід видає код, розрядність якого дорівнює кількості чисел у масиві, а "одиниця" стоїть лише в тому розряді, яке число вибране, у всіх інших розрядах - "нулі". (Можливі й інші схеми вибору елементів, наприклад, схема надходить на знаходження мінімального числа масиву.) Далі зі схеми вибору елементу 20 код надходить на ключі 21, на інші входи яких подається масив чисел. Ключі 21 комутують на вихід тільки обране слово, що надходить на схему порівняння 22. Це слово також виводиться з блока вибору числа з масиву G 11, і є елементом для масиву наступного рівня або хвостовим елементом. На схему порівняння 22, крім обраного числа, подається весь масив чисел. Там відбувається порівняння і на виході схеми порівняння 22 формується двійковий код, розрядність якого дорівнює розрядності масиву, а одиниці стоять у тих розрядах коду, на місцях яких у масиві чисел знаходилися числа, рівні обраному, тобто масці. Код на виході схеми порівняння 22 і є маскою масиву на даному кроці перетворення. Цей код виводиться з блока вибору числа з масиву G 11 для запису в ОЗП масок, і подається на ключі 23. Код маски на вході блока ключів 16 інвертується і пропускає на вихід блока ключів 23 ті числа масиву, які не рівні обраному. Так здійснюється ПІ перетворення масиву з урахуванням обраного числа. Можливі й інші схеми, що реалізують ПІ перетворення. Наприклад, замість схеми порівняння 22 і ключів 23 застосувати схему вирахування числа з всіх елементів масиву. Результати перетворення блока вибору числа з масиву G 11 - це обрані числа, маски і перетворені масиви чисел. Обрані числа ai із блока вибору числа з масиву G 11 надходять на i схеми І 12 і схеми виявлення одиночних елементів 13. Схеми І 12 по черзі пропускають на вхід схеми АБО 14 масиви, сформовані на першому рівні. Управляють роботою ключів 12 сигнали Т 1 із блока комутації 1. 4 UA 99547 C2 5 10 15 20 25 30 35 40 45 50 При обробці масивів чисел на першому рівні на якомусь такті може з'явитися хвостовий елемент, який необхідно буде записати в ОЗП чисел 3 і не пересилати на подальшу обробку. Ці функції виконують схема АБО 14, схема виявлення одиночних елементів S 0 15 і схеми І 16. Так як масиви чисел при обробці на першому рівні формуються в різноманітні моменти часу, тоді достатньо однієї схеми виявлення одиночних елементів S0, на вхід якої масиви будуть надходити послідовно зі схеми АБО 14. Якщо сформований масив містить більш одного числа, не рівного нулю, тоді схема виявлення одиночних елементів S0 15 виробляє сигнал, який дозволяє проходження сформованого масиву на вхід блока комутації 1, через схему І 16. Якщо з'являється хвостовий елемент, то він через схему виявлення одиночних елементів S0 15 подається в ОЗП чисел. Для всіх інших рівнів, крім першого, якщо на черговому такті перетворення було вибрано в блоках вибору числа з масиву G 11 більш одного числа, то відповідна схема виявлення одиночних елементів 13 пропускає знову створений масив на вхід блока комутації 1. Якщо в такті перетворення вибрано тільки одне число, то це число буде бути хвостовим елементом і надалі в перетворенні брати участь не буде. Тоді, відповідна схема виявлення одиночних елементів 13 видає значення цього числа на вхід ОЗП чисел. Функціональна схема блока виявлення одиночних елементів 13 і блока виявлення одиночних елементів S0 15 подана на фіг. 7. Аналогічно передаються маски масивів з блоків вибору числа з масиву G 11 в ОЗП масок. При обробці масивів на першому рівні маски формуються в різні моменти часу, тому коди масок із виходів блоків вибору числа з масиву G 11 надходять на вентилі 17. Вентилі 17 управляються імпульсами на шині Т 1, що надходять з блока комутації 1, і послідовно пропускають коди масок на вхід схеми АБО 18. З виходу схеми АБО 18 маски записуються в ОЗП масок 4. Коди масок, сформовані на всіх інших рівнях, надходять безпосередньо в ОЗП масок 4. ОЗП чисел 3 і ОЗП масок 4 являють собою звичайні динамічні ОЗП, на входи яких подаються відповідно значення хвостових елементом і коди масок масивів. Управляють роботою ОЗП сигнали "Запис", "Читання" і сигнал від генератора 5. Якщо активний сигнал "Запис", тоді по тактових імпульсах генератора 5 інформація записується в ОЗП чисел 3 і ОЗП масок 4. При активному вхідному сигналі "Читання" аналогічно по імпульсах генератора відбувається читання інформації з ОЗП чисел 3 і ОЗП масок 4 у блок декодування 6. Особливістю блоків ОЗП чисел 3 і ОЗП масок 4 є те, що на їх входах стоять схеми, які комутують у потрібний момент вхідну інформацію. Запропонований пристрій паралельно-ієрархічного кодування-декодування забезпечує швидкодію за рахунок введення в нього двох блоків пам'яті для паралельного збереження даних. ФОРМУЛА ВИНАХОДУ Пристрій паралельно-ієрархічного кодування-декодування інформації, що містить перший та другий блоки пам'яті, входи читання та запису, інформаційні вхід і вихід, який відрізняється тим, що в нього введено блок комутації, блок перетворення інформації, генератор та блок декодування, вихід якого підключений до виходу пристрою, перший вхід підключений до виходу першого блока пам'яті, а другий і третій входи відповідно з'єднані з виходами другого блока пам'яті, вихід генератора з'єднаний з п'ятими входами блока комутації, першого блока пам'яті і другого блока пам'яті, вхід запису з'єднаний з першим входом генератора, четвертим входом блока комутації, а також з третіми входами першого і другого блоків пам'яті, вхід читання підключений до другого входу генератора, п'ятих входів першого і другого блоків пам'яті, перший вихід блока перетворення інформації з'єднаний з першим входом першого блока пам'яті, другий вихід блока перетворення інформації підключений до першого входу другого блока пам'яті, третій і четвертий виходи блока перетворення інформації з'єднані відповідно з другим та третім входами блока комутації, другий і третій виходи якого підключені відповідно до першого та другого входів блока перетворення інформації, а перший вихід блока комутації підключений до других входів першого і другого блоків пам'яті. 5 UA 99547 C2 6 UA 99547 C2 7 UA 99547 C2 8 UA 99547 C2 9 UA 99547 C2 10 UA 99547 C2 Комп’ютерна верстка М. Ломалова Державна служба інтелектуальної власності України, вул. Урицького, 45, м. Київ, МСП, 03680, Україна ДП “Український інститут промислової власності”, вул. Глазунова, 1, м. Київ – 42, 01601 11

ДивитисяДодаткова інформація

Назва патенту англійськоюDevice for parallel-hierarhical encoding/decoding information

Автори англійськоюTymchenko Leonid Ivanovych, Kokriatska Natalia Ivanivna, Zahoruiko Tetiana Andriivna, Makarenko Roman Viktorovych

Назва патенту російськоюУстройство параллельно-иерархического кодирования/декодирования информации

Автори російськоюТимченко Леонид Иванович, Кокряцкая Наталья Ивановна, Загоруйко Татьяна Андреевна, Макаренко Роман Викторович

МПК / Мітки

МПК: H03M 9/00, H03M 13/21

Мітки: пристрій, паралельно-ієрархічного, кодування-декодування, інформації

Код посилання

<a href="https://ua.patents.su/13-99547-pristrijj-paralelno-iehrarkhichnogo-koduvannya-dekoduvannya-informaci.html" target="_blank" rel="follow" title="База патентів України">Пристрій паралельно-ієрархічного кодування-декодування інформації</a>