Багаторозрядний суматор за змінним модулем з груповим переносом

Номер патенту: 100006

Опубліковано: 10.07.2015

Автори: Тесленко Олександр Кирилович, Кляченко Ярослав Михайлович, Шепотіннік Олександр Юрійович, Роговенко Андрій Іванович, Тарасенко Володимир Петрович

Формула / Реферат

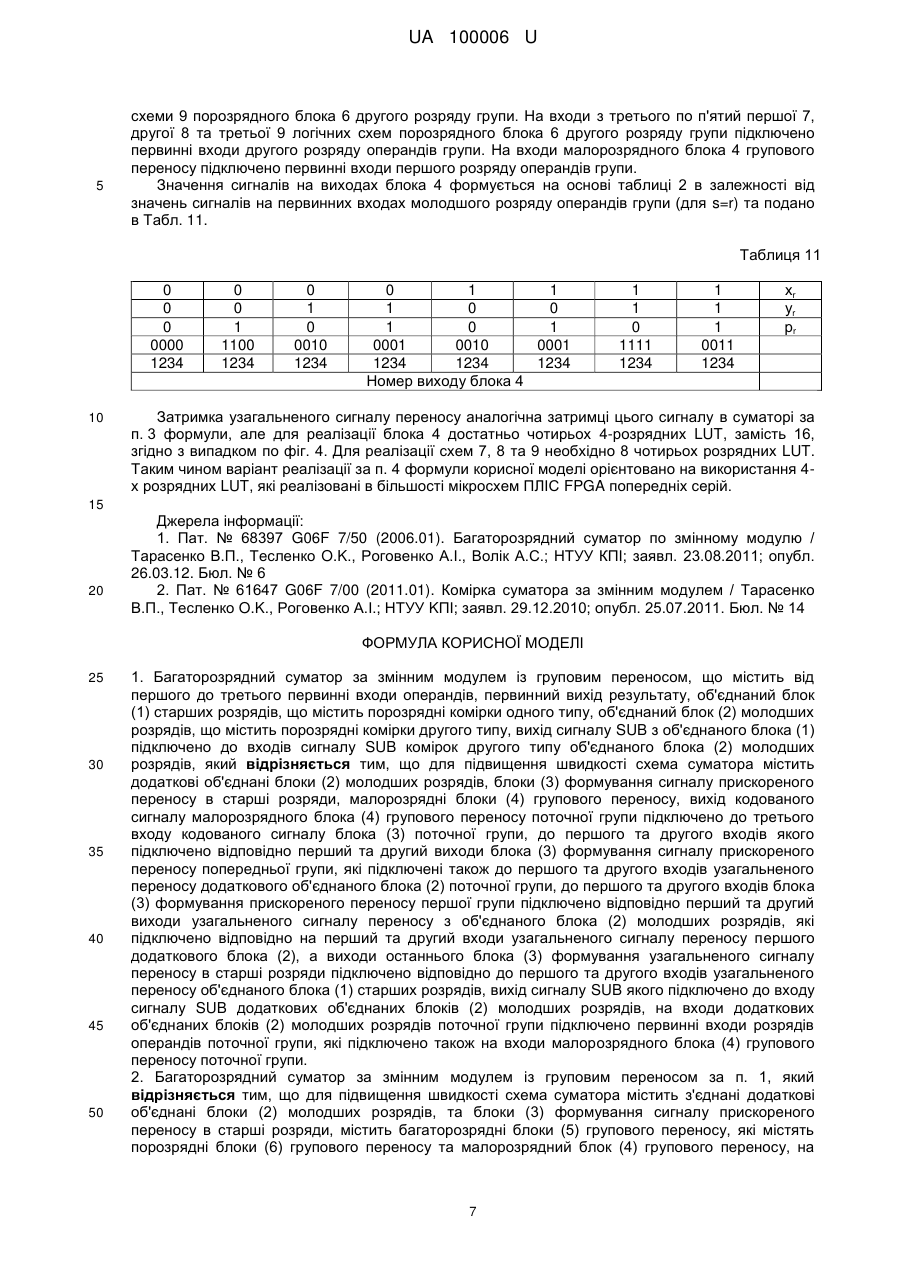

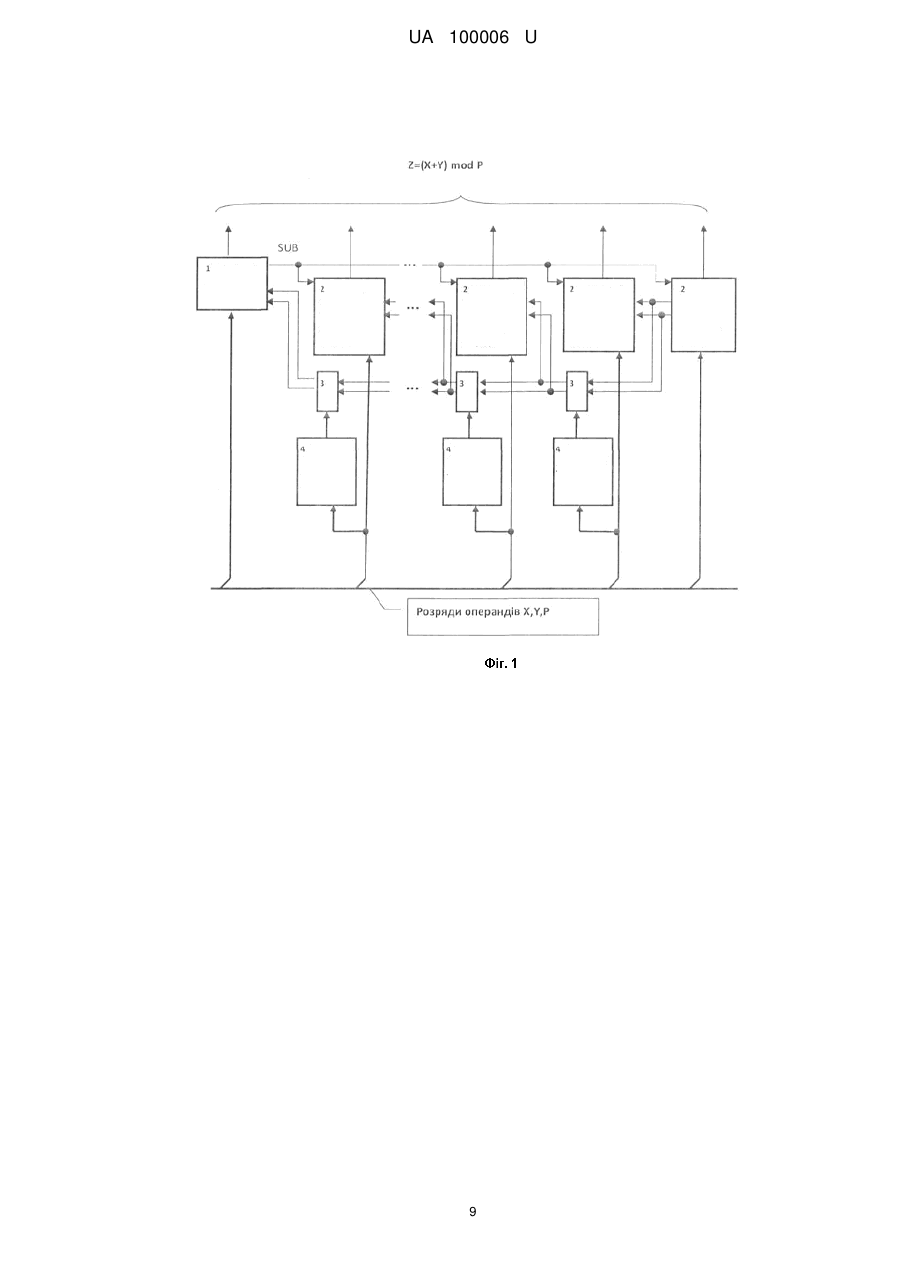

1. Багаторозрядний суматор за змінним модулем із груповим переносом, що містить від першого до третього первинні входи операндів, первинний вихід результату, об'єднаний блок (1) старших розрядів, що містить порозрядні комірки одного типу, об'єднаний блок (2) молодших розрядів, що містить порозрядні комірки другого типу, вихід сигналу SUB з об'єднаного блока (1) підключено до входів сигналу SUB комірок другого типу об'єднаного блока (2) молодших розрядів, який відрізняється тим, що для підвищення швидкості схема суматора містить додаткові об'єднані блоки (2) молодших розрядів, блоки (3) формування сигналу прискореного переносу в старші розряди, малорозрядні блоки (4) групового переносу, вихід кодованого сигналу малорозрядного блока (4) групового переносу поточної групи підключено до третього входу кодованого сигналу блока (3) поточної групи, до першого та другого входів якого підключено відповідно перший та другий виходи блока (3) формування сигналу прискореного переносу попередньої групи, які підключені також до першого та другого входів узагальненого переносу додаткового об'єднаного блока (2) поточної групи, до першого та другого входів блока (3) формування прискореного переносу першої групи підключено відповідно перший та другий виходи узагальненого сигналу переносу з об'єднаного блока (2) молодших розрядів, які підключено відповідно на перший та другий входи узагальненого сигналу переносу першого додаткового блока (2), а виходи останнього блока (3) формування узагальненого сигналу переносу в старші розряди підключено відповідно до першого та другого входів узагальненого переносу об'єднаного блока (1) старших розрядів, вихід сигналу SUB якого підключено до входу сигналу SUB додаткових об'єднаних блоків (2) молодших розрядів, на входи додаткових об'єднаних блоків (2) молодших розрядів поточної групи підключено первинні входи розрядів операндів поточної групи, які підключено також на входи малорозрядного блока (4) групового переносу поточної групи.

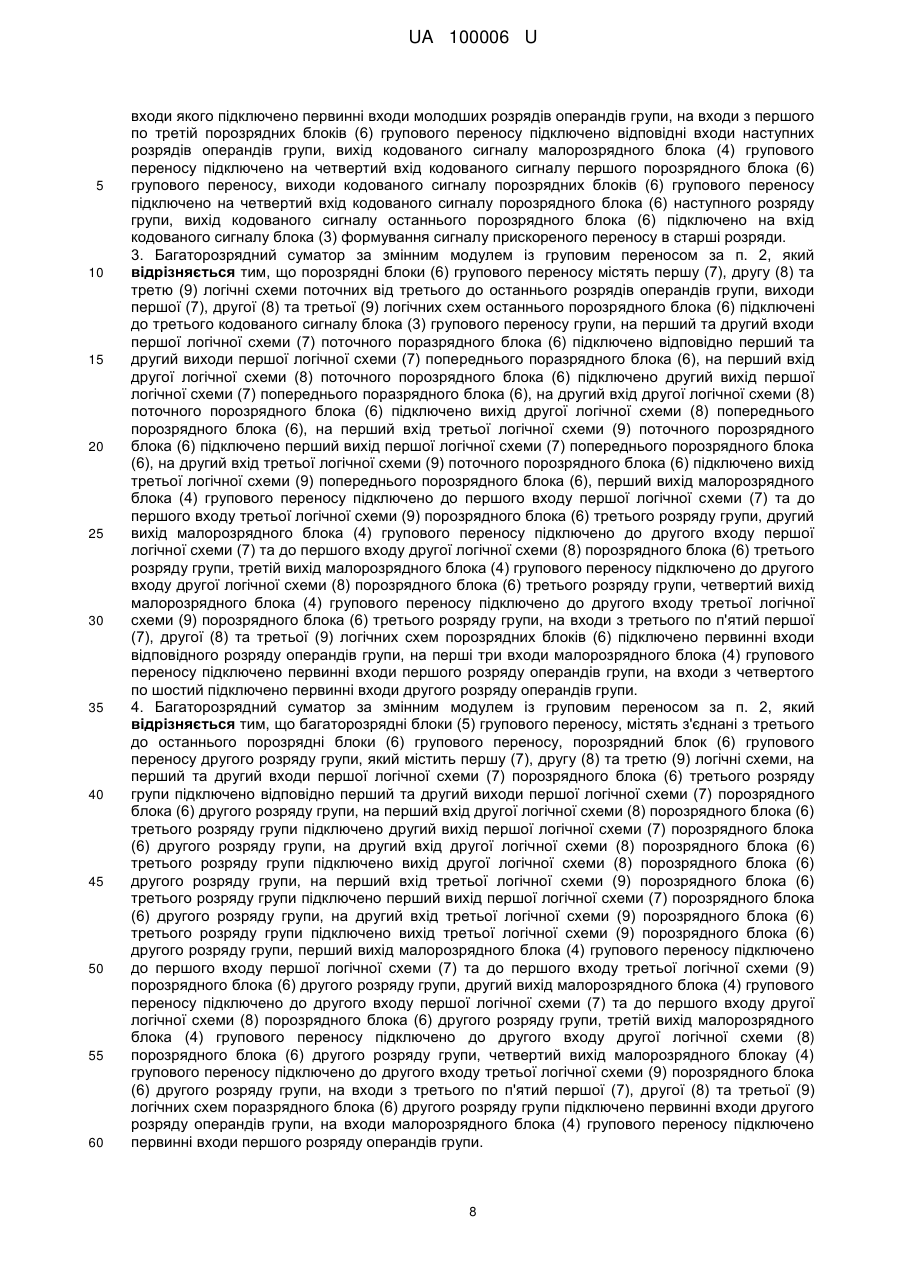

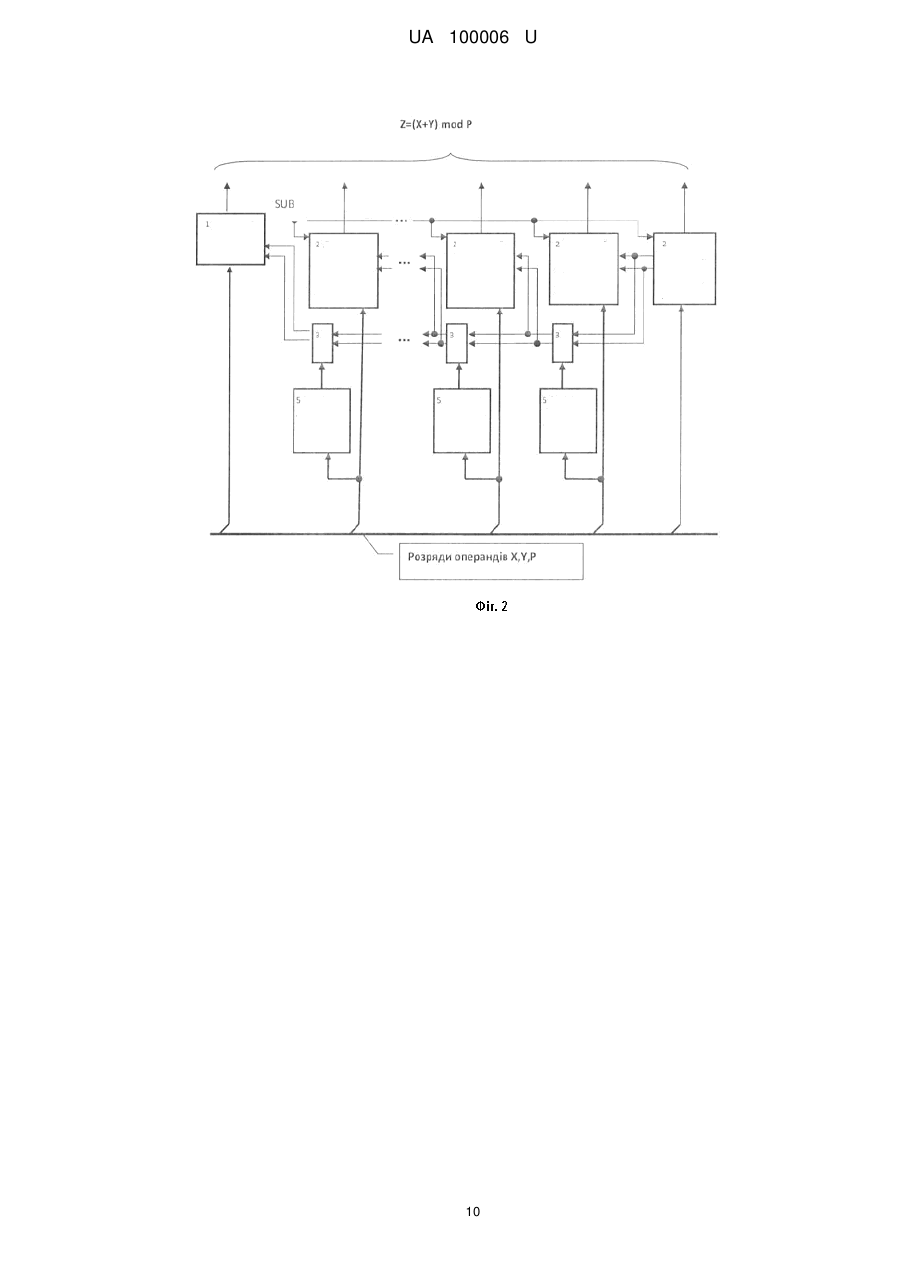

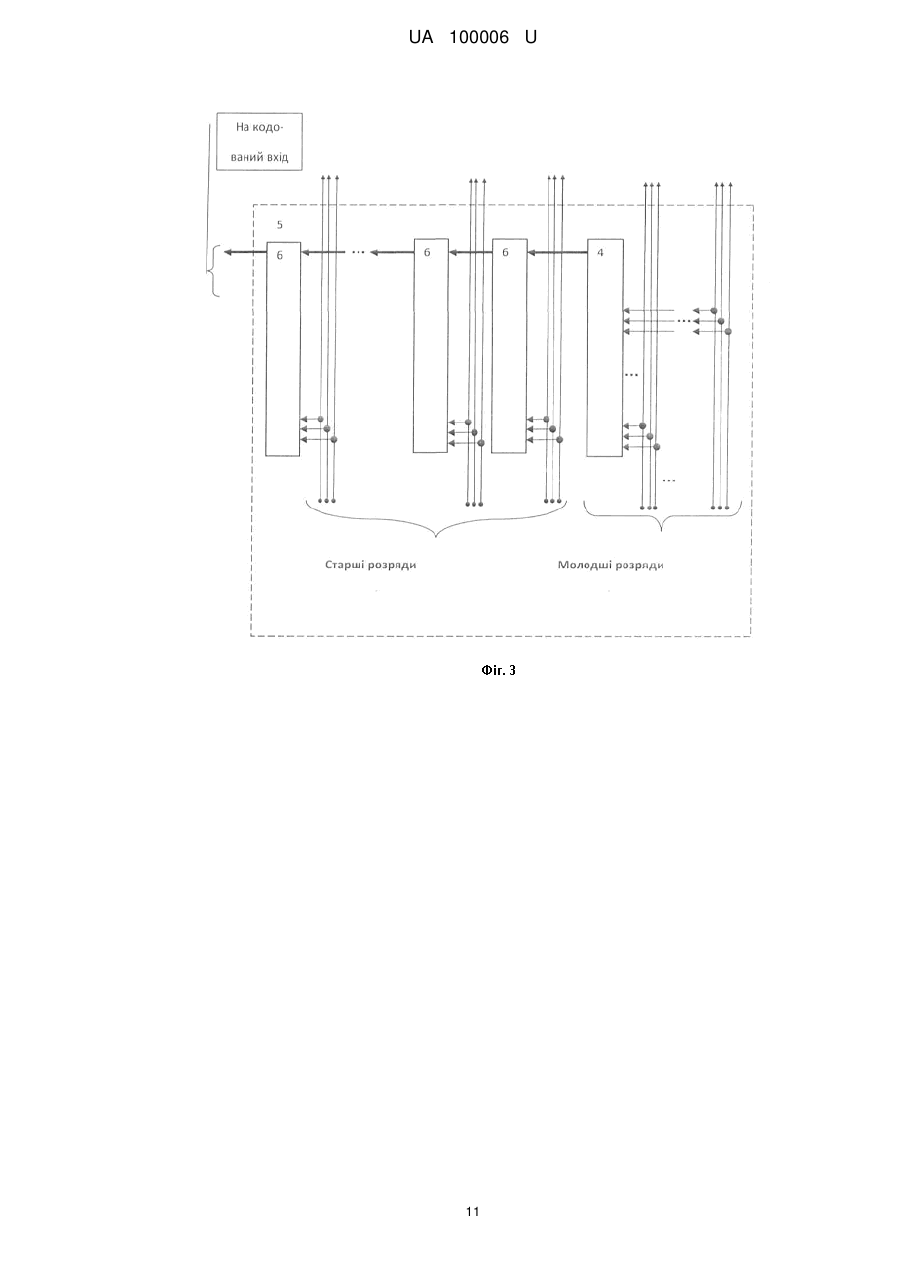

2. Багаторозрядний суматор за змінним модулем із груповим переносом за п. 1, який відрізняється тим, що для підвищення швидкості схема суматора містить з'єднані додаткові об'єднані блоки (2) молодших розрядів, та блоки (3) формування сигналу прискореного переносу в старші розряди, містить багаторозрядні блоки (5) групового переносу, які містять порозрядні блоки (6) групового переносу та малорозрядний блок (4) групового переносу, на входи якого підключено первинні входи молодших розрядів операндів групи, на входи з першого по третій порозрядних блоків (6) групового переносу підключено відповідні входи наступних розрядів операндів групи, вихід кодованого сигналу малорозрядного блока (4) групового переносу підключено на четвертий вхід кодованого сигналу першого порозрядного блока (6) групового переносу, виходи кодованого сигналу порозрядних блоків (6) групового переносу підключено на четвертий вхід кодованого сигналу порозрядного блока (6) наступного розряду групи, вихід кодованого сигналу останнього порозрядного блока (6) підключено на вхід кодованого сигналу блока (3) формування сигналу прискореного переносу в старші розряди.

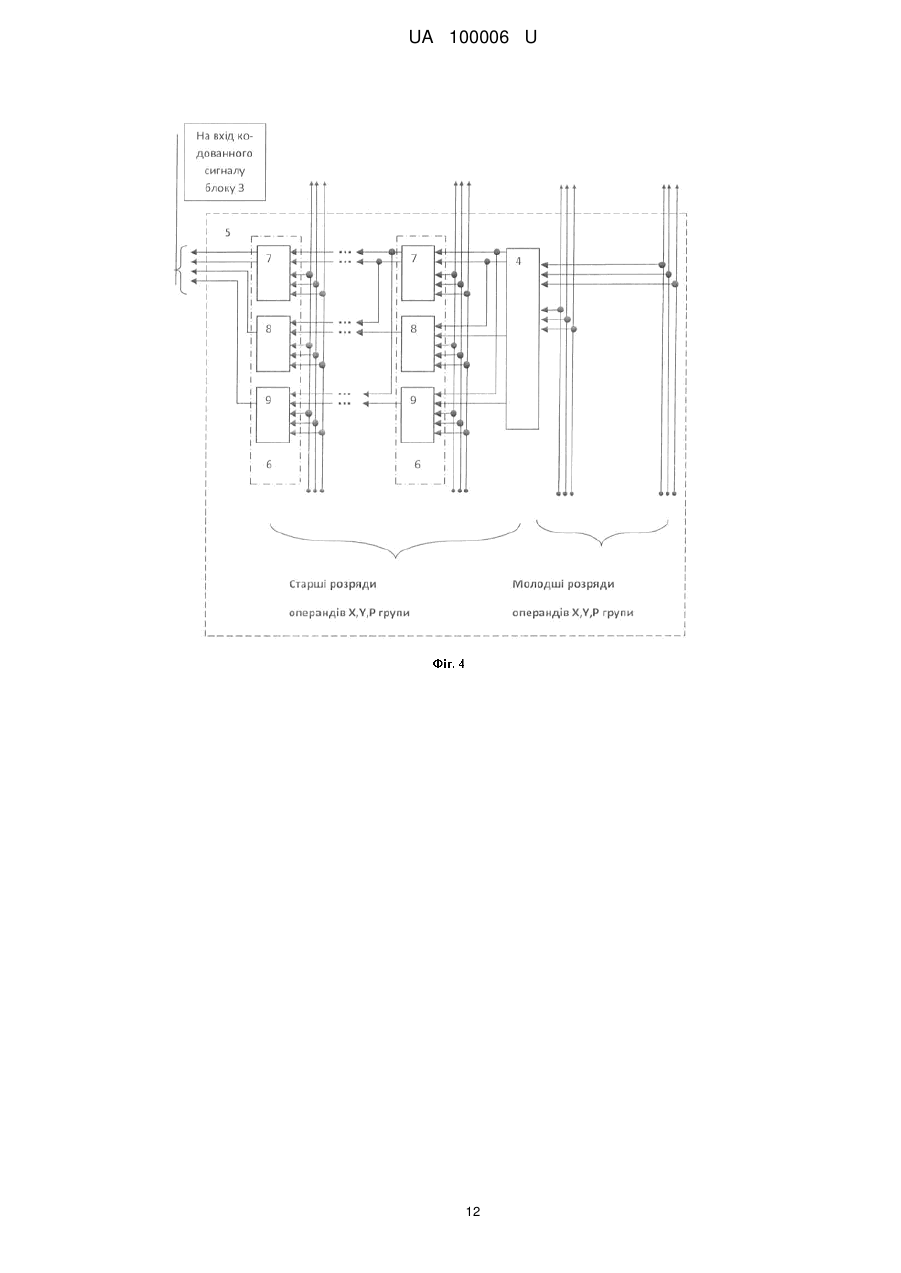

3. Багаторозрядний суматор за змінним модулем із груповим переносом за п. 2, який відрізняється тим, що порозрядні блоки (6) групового переносу містять першу (7), другу (8) та третю (9) логічні схеми поточних від третього до останнього розрядів операндів групи, виходи першої (7), другої (8) та третьої (9) логічних схем останнього порозрядного блока (6) підключені до третього кодованого сигналу блока (3) групового переносу групи, на перший та другий входи першої логічної схеми (7) поточного поразрядного блока (6) підключено відповідно перший та другий виходи першої логічної схеми (7) попереднього поразрядного блока (6), на перший вхід другої логічної схеми (8) поточного порозрядного блока (6) підключено другий вихід першої логічної схеми (7) попереднього поразрядного блока (6), на другий вхід другої логічної схеми (8) поточного порозрядного блока (6) підключено вихід другої логічної схеми (8) попереднього порозрядного блока (6), на перший вхід третьої логічної схеми (9) поточного порозрядного блока (6) підключено перший вихід першої логічної схеми (7) попереднього порозрядного блока (6), на другий вхід третьої логічної схеми (9) поточного порозрядного блока (6) підключено вихід третьої логічної схеми (9) попереднього порозрядного блока (6), перший вихід малорозрядного блока (4) групового переносу підключено до першого входу першої логічної схеми (7) та до першого входу третьої логічної схеми (9) порозрядного блока (6) третього розряду групи, другий вихід малорозрядного блока (4) групового переносу підключено до другого входу першої логічної схеми (7) та до першого входу другої логічної схеми (8) порозрядного блока (6) третього розряду групи, третій вихід малорозрядного блока (4) групового переносу підключено до другого входу другої логічної схеми (8) порозрядного блока (6) третього розряду групи, четвертий вихід малорозрядного блока (4) групового переносу підключено до другого входу третьої логічної схеми (9) порозрядного блока (6) третього розряду групи, на входи з третього по п'ятий першої (7), другої (8) та третьої (9) логічних схем порозрядних блоків (6) підключено первинні входи відповідного розряду операндів групи, на перші три входи малорозрядного блока (4) групового переносу підключено первинні входи першого розряду операндів групи, на входи з четвертого по шостий підключено первинні входи другого розряду операндів групи.

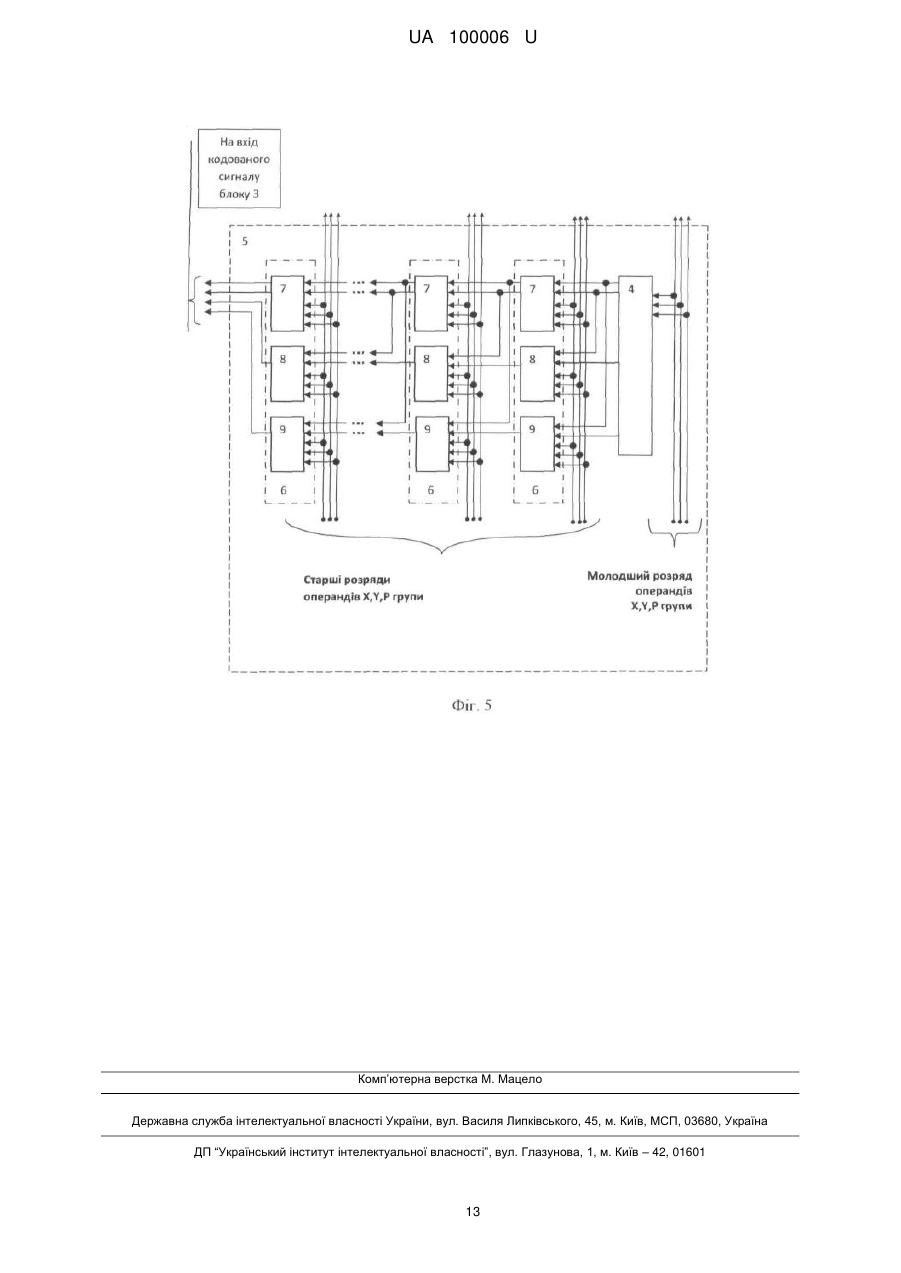

4. Багаторозрядний суматор за змінним модулем із груповим переносом за п. 2, який відрізняється тим, що багаторозрядні блоки (5) групового переносу, містять з'єднані з третього до останнього порозрядні блоки (6) групового переносу, порозрядний блок (6) групового переносу другого розряду групи, який містить першу (7), другу (8) та третю (9) логічні схеми, на перший та другий входи першої логічної схеми (7) порозрядного блока (6) третього розряду групи підключено відповідно перший та другий виходи першої логічної схеми (7) порозрядного блока (6) другого розряду групи, на перший вхід другої логічної схеми (8) порозрядного блока (6) третього розряду групи підключено другий вихід першої логічної схеми (7) порозрядного блока (6) другого розряду групи, на другий вхід другої логічної схеми (8) порозрядного блока (6) третього розряду групи підключено вихід другої логічної схеми (8) порозрядного блока (6) другого розряду групи, на перший вхід третьої логічної схеми (9) порозрядного блока (6) третього розряду групи підключено перший вихід першої логічної схеми (7) порозрядного блока (6) другого розряду групи, на другий вхід третьої логічної схеми (9) порозрядного блока (6) третього розряду групи підключено вихід третьої логічної схеми (9) порозрядного блока (6) другого розряду групи, перший вихід малорозрядного блока (4) групового переносу підключено до першого входу першої логічної схеми (7) та до першого входу третьої логічної схеми (9) порозрядного блока (6) другого розряду групи, другий вихід малорозрядного блока (4) групового переносу підключено до другого входу першої логічної схеми (7) та до першого входу другої логічної схеми (8) порозрядного блока (6) другого розряду групи, третій вихід малорозрядного блока (4) групового переносу підключено до другого входу другої логічної схеми (8) порозрядного блока (6) другого розряду групи, четвертий вихід малорозрядного блокау (4) групового переносу підключено до другого входу третьої логічної схеми (9) порозрядного блока (6) другого розряду групи, на входи з третього по п'ятий першої (7), другої (8) та третьої (9) логічних схем поразрядного блока (6) другого розряду групи підключено первинні входи другого розряду операндів групи, на входи малорозрядного блока (4) групового переносу підключено первинні входи першого розряду операндів групи.

Текст

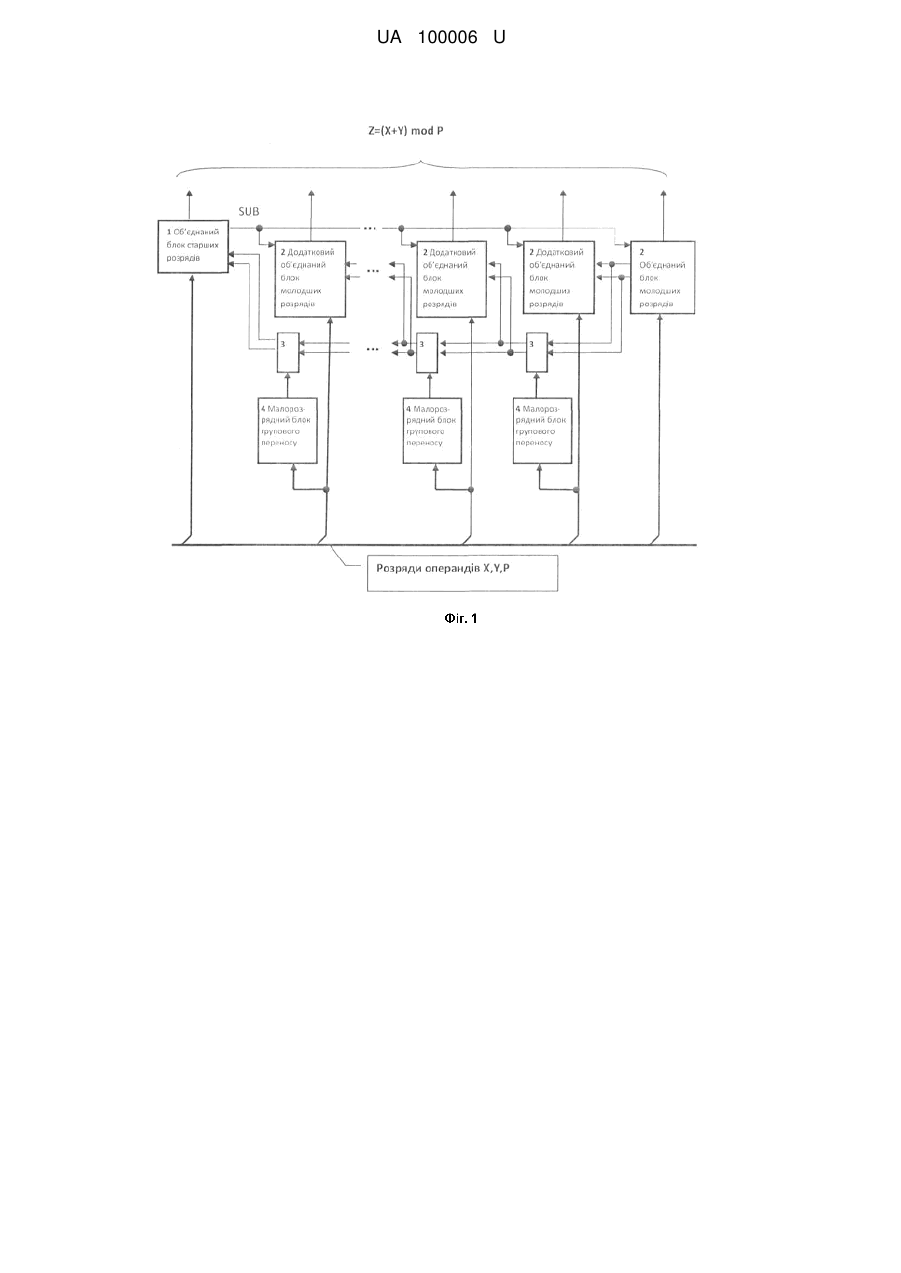

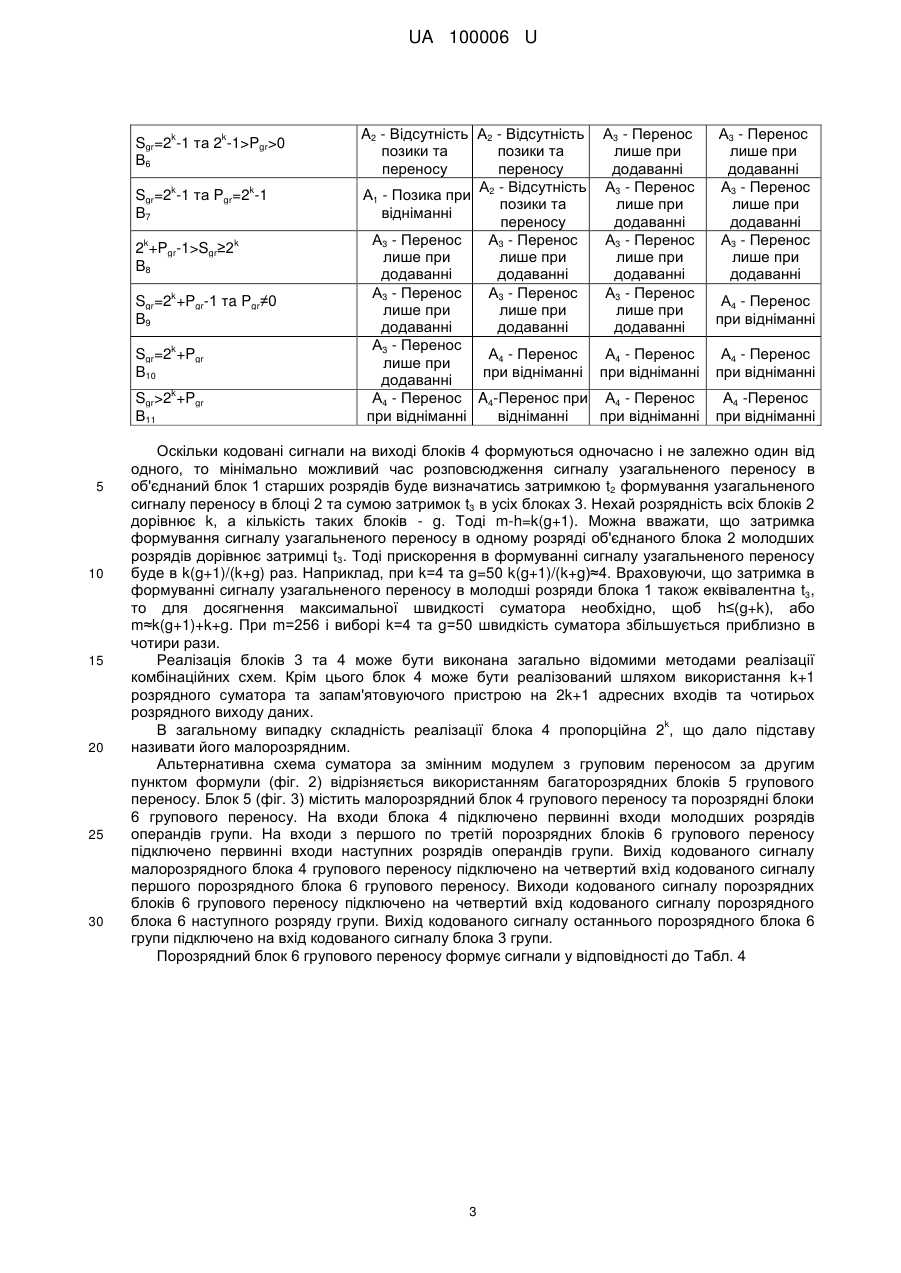

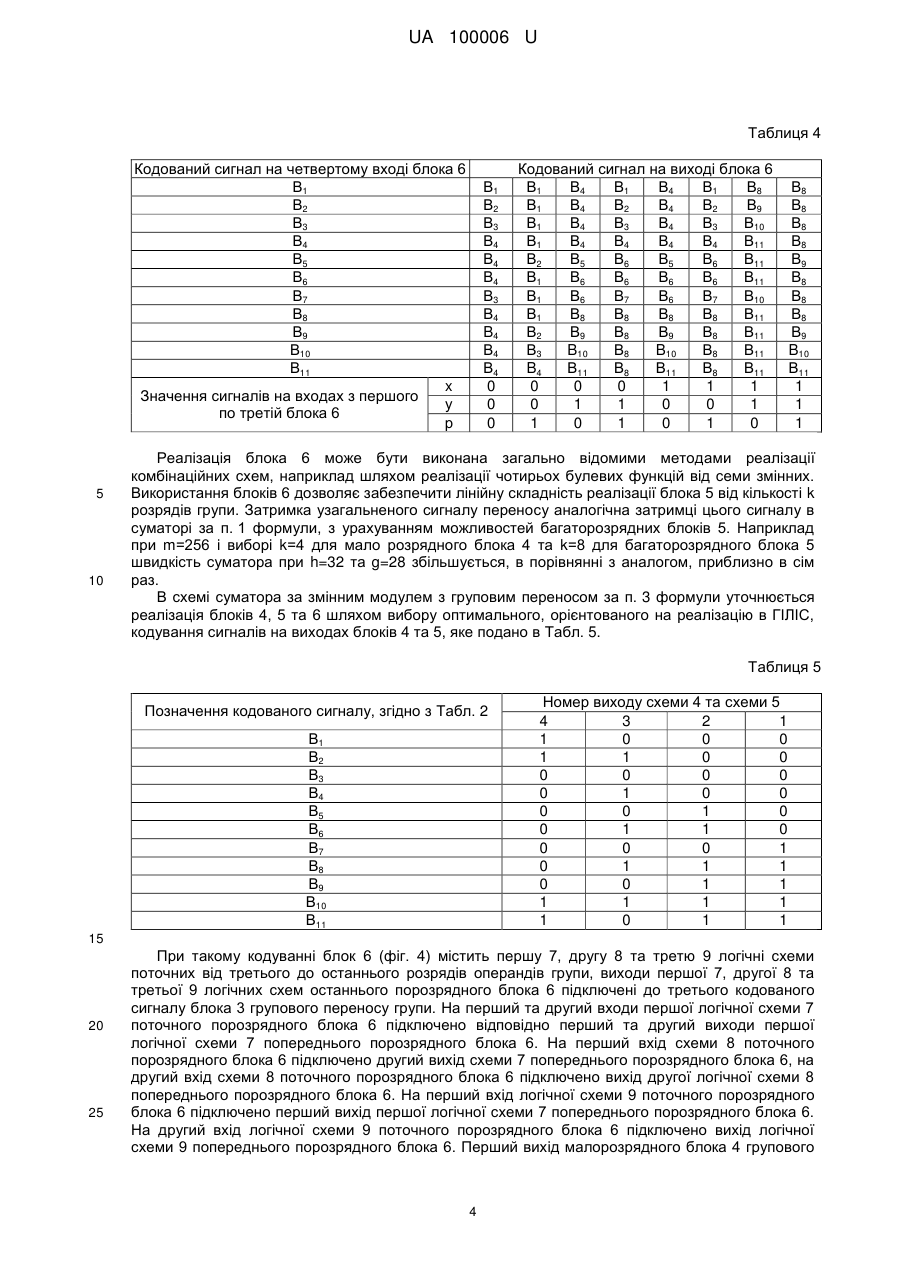

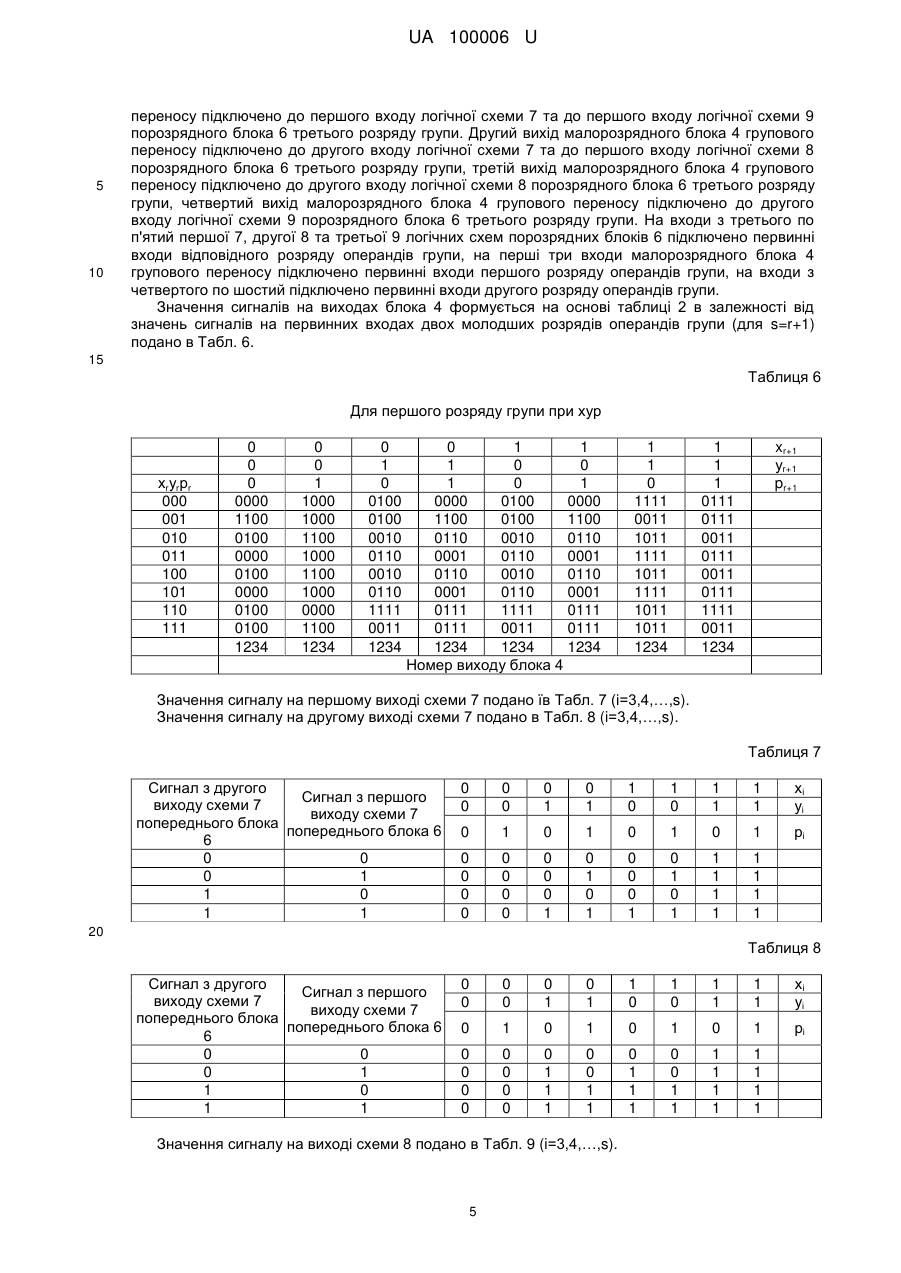

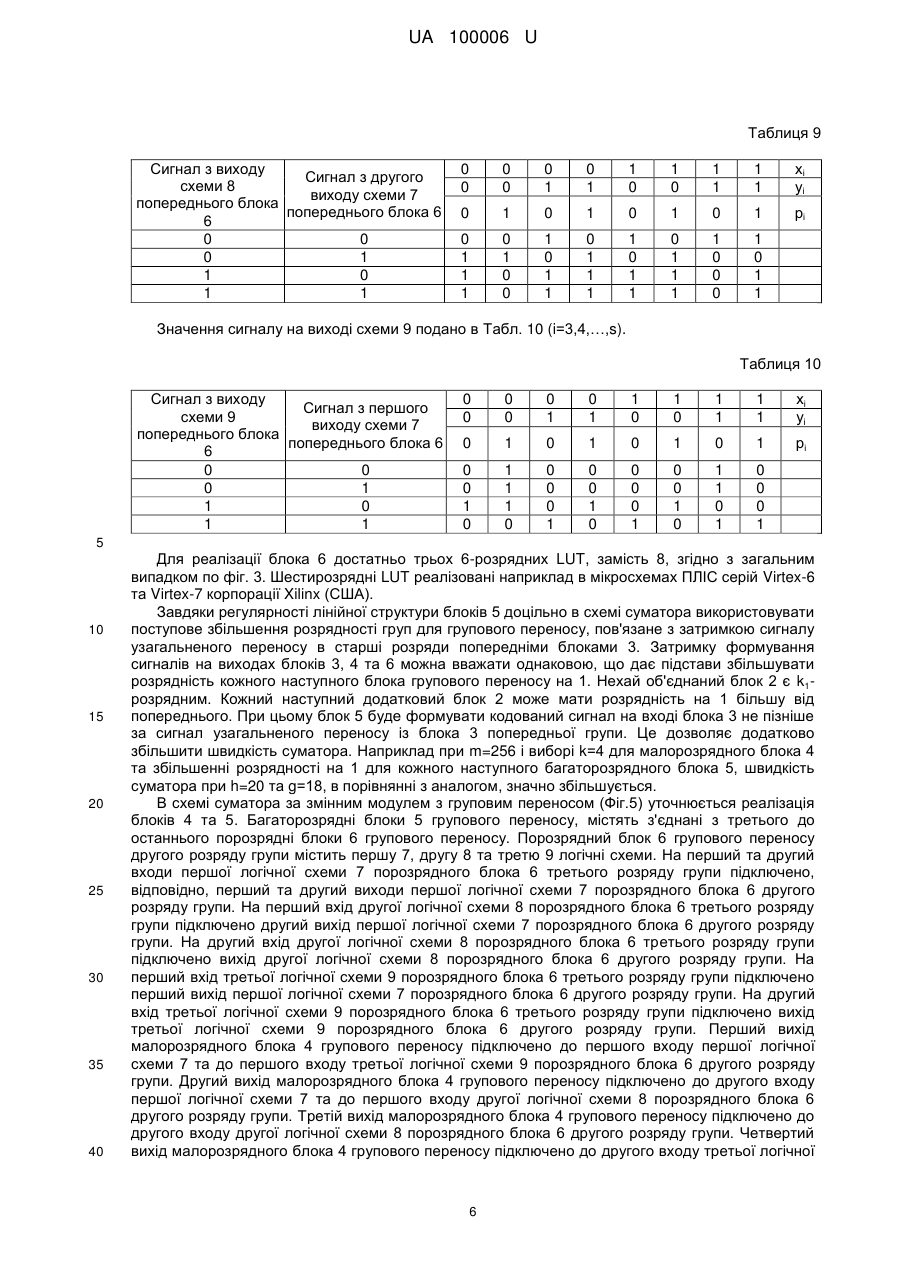

Реферат: Багаторозрядний суматор за змінним модулем із груповим переносом містить від першого до третього первинні входи операндів, первинний вихід результату, об'єднаний блок старших розрядів, що містить порозрядні комірки одного типу, об'єднаний блок молодших розрядів, що містить порозрядні комірки другого типу, вихід сигналу SUB з об'єднаного блока підключено до входів сигналу SUB комірок другого типу об'єднаного блока молодших розрядів. Містить додаткові об'єднані блоки молодших розрядів, блоки формування сигналу прискореного переносу в старші розряди, малорозрядні блоки групового переносу. UA 100006 U (12) UA 100006 U UA 100006 U 5 10 15 20 25 30 35 40 45 50 Корисна модель належить до обчислювальної техніки і може бути використана у спеціалізованих обчислювальних пристроях на базі ПЛІС для побудови швидкодіючих помножувачів за змінним модулем, системах асиметричних криптографічних перетворень, системах цифрового підпису. Відомий суматор за змінним модулем [1], який складається з об'єднаного блока 1 старших розрядів та об'єднаного блока 2 молодших розрядів. Блок 1 складається із h≥1 комірок, які містять схему обчислення основної функції, схему формування сигналу віднімання (SUB) для схеми обчислення основної функції попереднього молодшого розряду, схеми формування сигналу узагальненого переносу в старші розряди та схему формування сигналу узагальненого переносу в молодші розряди. Об'єднаний блок 2 молодших розрядів складається із m-h комірок, які містять схему обчислення основної функції з використанням сигналу SUB та схеми формування узагальненого переносу в старші розряди, де m - розрядність суматора. Недоліком аналога [1] є те, що при виконанні операції над операндами великої розрядності із-за збільшення кількості комірок пропорційно збільшується і затримка сигналу узагальненого переносу у старші розряди, що приводить до збільшення часу для обчислення кінцевого результату. Найближчим аналогом до корисної моделі є комірка двійкового суматора за змінним модулем [2], що містить від першого до третього первинні входи операндів, первинний вихід результату, логічну схему формування сигналу SUB, первинні входи та первинні виходи перенесення в старші розряди, первинні входи та первинні виходи перенесення в молодші розряди. Недоліком комірки найближчого аналога[2] є відсутність можливості виконання групового переносу, що приводить до збільшення часу для обчислення кінцевого результату, в окремих групах комірок. Задачею даної корисної моделі є удосконалення схеми переносу у багаторозрядному суматорі за змінним модулем, шляхом внесення змін до його структури. Поставлена задача корисної моделі вирішується тим, що внесено зміни у вигляді введення додаткових об'єднаних блоків 2 молодших розрядів, блоків 3 формування прискореного сигналу переносу в старші розряди та малорозрядних блоків (4) групового переносу (фіг. 1) для прискорення процесу розповсюдження сигналу узагальненого переносу у старші розряди та обчислення цільової функції. Первинні входи операндів розбиваються на групи з послідовною зміною розрядів у групі. Первинні входи групи самих молодших розрядів підключені, на входи об'єднаного блока 2 молодших розрядів. Первинні входи операндів першої та наступних груп підключено, відповідно, на входи додаткових об'єднаних блоків 2 та на входи малорозрядних блоків 4 групового переносу. Первинні входи операндів групи самих старших розрядів підключено на входи об'єднаного блока 1 старших розрядів. Виходи кодованого сигналу малорозрядного блока 4 групи підключені на третій вхід кодованого сигналу блока 3 цієї ж групи, а на перший та другий входи блока 3 поточної групи підключено відповідно перший та другий виходи блока 3 попередньої групи, які підключено також на входи сигналу узагальненого переносу додаткового об'єднаного блока 2 поточної групи. Перший та другий виходи узагальненого сигналу переносу об'єднаного блока 2 молодших розрядів підключені відповідно на перший та другий входи узагальненого переносу додаткового об'єднаного блока 2 першої групи та на перший та другий входи формування сигналу прискореного переносу блока 3 першої групи. Перший та другий виходи блока 3 останньої групи підключено відповідно до першого та другого входу сигналу узагальненого переносу в старші розряди об'єднаного блока 1 старших розрядів. Вихід сигналу SUB блока 1 підключено до входу сигналу SUB всіх блоків 2. Суматор реалізує операцію Z=X+Y-P при (X+Y)≥Р, та Z=X+Y, при (X+Y)0 k k Sgr=2 -1 та Pgr=2 -1 k k 2 +Pgr-1>Sgr≥2 k Sgr=2 +Pgr-1 тa Pgr0 k Sgr=2 +Pgr k Sgr>2+Pgr 10 Кодований сигнал на виході блока 4 В1 В2 В3 B4 B5 B6 B7 B8 B9 B10 В11 На основі узагальненого сигналу переносу із попередньої групи та сформованого блоком 4 кодованого сигналу, блок 3, згідно з Табл. 3, формує сигнал узагальненого переносу в старші розряди суматора. Таблиця 3 Значення узагальненого сигналу переносу на виході схеми 3 Узагальнений сигнал переносу на вході схеми 3 А - Відсутність А3 - Перенос Значення кодованого сигналу А1 - Позика при 2 А4 - Перенос позики та лише при на третьому вході схеми 3 відніманні при відніманні переносу додаванні SgrSgr>Pgr позики та позики та позики та позики та В4 переносу переносу переносу переносу А2 - Відсутність А2 - Відсутність А3 - Перенос k Sgr=2 -1 та Pgr=0 А4 - Перенос позики та позики та лише при B5 при відніманні переносу переносу додаванні 2 UA 100006 U k k Sgr=2 -1 та 2 -1>Pgr>0 В6 k k Sgr=2 -1 та Pgr=2 -1 B7 k 2 +Pgr-1>Sgr≥2 B8 k k Sgr=2 +Pgr-1 тa Pgr≠0 B9 k Sgr=2 +Pgr B10 k Sgr>2 +Pgr В11 5 10 15 20 25 30 A2 - Відсутність А2 - Відсутність А3 - Перенос позики та позики та лише при переносу переносу додаванні А - Відсутність А3 - Перенос А1 - Позика при 2 позики та лише при відніманні переносу додаванні А3 - Перенос А3 - Перенос А3 - Перенос лише при лише при лише при додаванні додаванні додаванні А3 - Перенос А3 - Перенос А3 - Перенос лише при лише при лише при додаванні додаванні додаванні А3 - Перенос А4 - Перенос А4 - Перенос лише при при відніманні при відніманні додаванні А4 - Перенос A4-Перенос при А4 - Перенос при відніманні відніманні при відніманні А3 - Перенос лише при додаванні А3 - Перенос лише при додаванні А3 - Перенос лише при додаванні А4 - Перенос при відніманні А4 - Перенос при відніманні А4 -Перенос при відніманні Оскільки кодовані сигнали на виході блоків 4 формуються одночасно і не залежно один від одного, то мінімально можливий час розповсюдження сигналу узагальненого переносу в об'єднаний блок 1 старших розрядів буде визначатись затримкою t2 формування узагальненого сигналу переносу в блоці 2 та сумою затримок t3 в усіх блоках 3. Нехай розрядність всіх блоків 2 дорівнює k, а кількість таких блоків - g. Тоді m-h=k(g+1). Можна вважати, що затримка формування сигналу узагальненого переносу в одному розряді об'єднаного блока 2 молодших розрядів дорівнює затримці t3. Тоді прискорення в формуванні сигналу узагальненого переносу буде в k(g+1)/(k+g) раз. Наприклад, при k=4 та g=50 k(g+1)/(k+g)≈4. Враховуючи, що затримка в формуванні сигналу узагальненого переносу в молодші розряди блока 1 також еквівалентна t3, то для досягнення максимальної швидкості суматора необхідно, щоб h≤(g+k), або m≈k(g+1)+k+g. При m=256 і виборі k=4 та g=50 швидкість суматора збільшується приблизно в чотири рази. Реалізація блоків 3 та 4 може бути виконана загально відомими методами реалізації комбінаційних схем. Крім цього блок 4 може бути реалізований шляхом використання k+1 розрядного суматора та запам'ятовуючого пристрою на 2k+1 адресних входів та чотирьох розрядного виходу даних. k В загальному випадку складність реалізації блока 4 пропорційна 2 , що дало підставу називати його малорозрядним. Альтернативна схема суматора за змінним модулем з груповим переносом за другим пунктом формули (фіг. 2) відрізняється використанням багаторозрядних блоків 5 групового переносу. Блок 5 (фіг. 3) містить малорозрядний блок 4 групового переносу та порозрядні блоки 6 групового переносу. На входи блока 4 підключено первинні входи молодших розрядів операндів групи. На входи з першого по третій порозрядних блоків 6 групового переносу підключено первинні входи наступних розрядів операндів групи. Вихід кодованого сигналу малорозрядного блока 4 групового переносу підключено на четвертий вхід кодованого сигналу першого порозрядного блока 6 групового переносу. Виходи кодованого сигналу порозрядних блоків 6 групового переносу підключено на четвертий вхід кодованого сигналу порозрядного блока 6 наступного розряду групи. Вихід кодованого сигналу останнього порозрядного блока 6 групи підключено на вхід кодованого сигналу блока 3 групи. Порозрядний блок 6 групового переносу формує сигнали у відповідності до Табл. 4 3 UA 100006 U Таблиця 4 Кодований сигнал на четвертому вході блока 6 В1 В2 В3 В4 В5 В6 В7 В8 В9 В10 В11 x Значення сигналів на входах з першого у по третій блока 6 р 5 10 В1 В2 В3 В4 В4 В4 В3 В4 B4 В4 В4 0 0 0 Кодований сигнал на виході блока 6 В1 В4 В1 В4 В1 В8 В1 В4 В2 В4 В2 В9 В1 В4 В3 В4 В3 В10 В1 В4 В4 В4 В4 В11 В2 В5 В6 В5 В6 В11 В1 В6 В6 В6 В6 В11 В1 В6 В7 В6 В7 В10 В1 В8 В8 В8 В8 В11 В2 В9 В8 В9 В8 В11 В3 B10 В8 B10 В8 В11 B4 В11 В8 В11 В8 В11 0 0 0 1 1 1 0 1 1 0 0 1 1 0 1 0 1 0 В8 В8 В8 В8 В9 В8 В8 В8 В9 B10 В11 1 1 1 Реалізація блока 6 може бути виконана загально відомими методами реалізації комбінаційних схем, наприклад шляхом реалізації чотирьох булевих функцій від семи змінних. Використання блоків 6 дозволяє забезпечити лінійну складність реалізації блока 5 від кількості k розрядів групи. Затримка узагальненого сигналу переносу аналогічна затримці цього сигналу в суматорі за п. 1 формули, з урахуванням можливостей багаторозрядних блоків 5. Наприклад при m=256 і виборі k=4 для мало розрядного блока 4 та k=8 для багаторозрядного блока 5 швидкість суматора при h=32 та g=28 збільшується, в порівнянні з аналогом, приблизно в сім раз. В схемі суматора за змінним модулем з груповим переносом за п. 3 формули уточнюється реалізація блоків 4, 5 та 6 шляхом вибору оптимального, орієнтованого на реалізацію в ГІЛІС, кодування сигналів на виходах блоків 4 та 5, яке подано в Табл. 5. Таблиця 5 Позначення кодованого сигналу, згідно з Табл. 2 В1 В2 В3 В4 В5 В6 В7 В8 В9 В10 В11 Номер виходу схеми 4 та схеми 5 4 3 2 1 1 0 0 0 1 1 0 0 0 0 0 0 0 1 0 0 0 0 1 0 0 1 1 0 0 0 0 1 0 1 1 1 0 0 1 1 1 1 1 1 1 0 1 1 15 20 25 При такому кодуванні блок 6 (фіг. 4) містить першу 7, другу 8 та третю 9 логічні схеми поточних від третього до останнього розрядів операндів групи, виходи першої 7, другої 8 та третьої 9 логічних схем останнього порозрядного блока 6 підключені до третього кодованого сигналу блока 3 групового переносу групи. На перший та другий входи першої логічної схеми 7 поточного порозрядного блока 6 підключено відповідно перший та другий виходи першої логічної схеми 7 попереднього порозрядного блока 6. На перший вхід схеми 8 поточного порозрядного блока 6 підключено другий вихід схеми 7 попереднього порозрядного блока 6, на другий вхід схеми 8 поточного порозрядного блока 6 підключено вихід другої логічної схеми 8 попереднього порозрядного блока 6. На перший вхід логічної схеми 9 поточного порозрядного блока 6 підключено перший вихід першої логічної схеми 7 попереднього порозрядного блока 6. На другий вхід логічної схеми 9 поточного порозрядного блока 6 підключено вихід логічної схеми 9 попереднього порозрядного блока 6. Перший вихід малорозрядного блока 4 групового 4 UA 100006 U 5 10 переносу підключено до першого входу логічної схеми 7 та до першого входу логічної схеми 9 порозрядного блока 6 третього розряду групи. Другий вихід малорозрядного блока 4 групового переносу підключено до другого входу логічної схеми 7 та до першого входу логічної схеми 8 порозрядного блока 6 третього розряду групи, третій вихід малорозрядного блока 4 групового переносу підключено до другого входу логічної схеми 8 порозрядного блока 6 третього розряду групи, четвертий вихід малорозрядного блока 4 групового переносу підключено до другого входу логічної схеми 9 порозрядного блока 6 третього розряду групи. На входи з третього по п'ятий першої 7, другої 8 та третьої 9 логічних схем порозрядних блоків 6 підключено первинні входи відповідного розряду операндів групи, на перші три входи малорозрядного блока 4 групового переносу підключено первинні входи першого розряду операндів групи, на входи з четвертого по шостий підключено первинні входи другого розряду операндів групи. Значення сигналів на виходах блока 4 формується на основі таблиці 2 в залежності від значень сигналів на первинних входах двох молодших розрядів операндів групи (для s=r+1) подано в Табл. 6. 15 Таблиця 6 Для першого розряду групи при хур хrуrрr 000 001 010 011 100 101 110 111 0 0 0 0000 1100 0100 0000 0100 0000 0100 0100 1234 0 0 1 1000 1000 1100 1000 1100 1000 0000 1100 1234 0 1 0 0100 0100 0010 0110 0010 0110 1111 0011 1234 0 1 1 1 0 0 1 0 1 0000 0100 0000 1100 0100 1100 0110 0010 0110 0001 0110 0001 0110 0010 0110 0001 0110 0001 0111 1111 0111 0111 0011 0111 1234 1234 1234 Номер виходу блока 4 1 1 0 1111 0011 1011 1111 1011 1111 1011 1011 1234 1 1 1 0111 0111 0011 0111 0011 0111 1111 0011 1234 xr+1 уr+1 pr+1 Значення сигналу на першому виході схеми 7 подано їв Табл. 7 (і=3,4,…,s). Значення сигналу на другому виході схеми 7 подано в Табл. 8 (i=3,4,…,s). Таблиця 7 Сигнал з другого Сигнал з першого виходу схеми 7 виходу схеми 7 попереднього блока попереднього блока 6 6 0 0 0 1 1 0 1 1 0 0 0 0 0 1 0 1 1 0 1 0 1 1 1 1 хі уі 0 1 0 1 0 1 0 1 рі 0 0 0 0 0 0 0 0 0 0 0 1 0 1 0 1 0 0 0 1 0 1 0 1 1 1 1 1 1 1 1 1 20 Таблиця 8 Сигнал з другого Сигнал з першого виходу схеми 7 виходу схеми 7 попереднього блока попереднього блока 6 6 0 0 0 1 1 0 1 1 0 0 0 0 0 1 0 1 1 0 1 0 1 1 1 1 хі уі 0 1 0 1 0 1 0 1 рі 0 0 0 0 0 0 0 0 0 1 1 1 0 0 1 1 0 1 1 1 0 0 1 1 1 1 1 1 1 1 1 1 Значення сигналу на виході схеми 8 подано в Табл. 9 (i=3,4,…,s). 5 UA 100006 U Таблиця 9 Сигнал з виходу Сигнал з другого схеми 8 виходу схеми 7 попереднього блока попереднього блока 6 6 0 0 0 1 1 0 1 1 0 0 0 0 0 1 0 1 1 0 1 0 1 1 1 1 хі уі 0 1 0 1 0 1 0 1 рі 0 1 1 1 0 1 0 0 1 0 1 1 0 1 1 1 1 0 1 1 0 1 1 1 1 0 0 0 1 0 1 1 Значення сигналу на виході схеми 9 подано в Табл. 10 (i=3,4,…,s). Таблиця 10 Сигнал з виходу Сигнал з першого схеми 9 виходу схеми 7 попереднього блока попереднього блока 6 6 0 0 0 1 1 0 1 1 0 0 0 0 0 1 0 1 1 01 0 1 1 1 1 хі уі 0 1 0 1 0 1 0 1 рі 0 0 1 0 1 1 1 0 0 0 0 1 0 0 1 0 0 0 0 1 0 0 1 0 1 1 0 1 0 0 0 1 5 10 15 20 25 30 35 40 Для реалізації блока 6 достатньо трьох 6-розрядних LUT, замість 8, згідно з загальним випадком по фіг. 3. Шестирозрядні LUT реалізовані наприклад в мікросхемах ПЛІС серій Virtex-6 та Virtex-7 корпорації Xilinx (США). Завдяки регулярності лінійної структури блоків 5 доцільно в схемі суматора використовувати поступове збільшення розрядності груп для групового переносу, пов'язане з затримкою сигналу узагальненого переносу в старші розряди попередніми блоками 3. Затримку формування сигналів на виходах блоків 3, 4 та 6 можна вважати однаковою, що дає підстави збільшувати розрядність кожного наступного блока групового переносу на 1. Нехай об'єднаний блок 2 є k1розрядним. Кожний наступний додатковий блок 2 може мати розрядність на 1 більшу від попереднього. При цьому блок 5 буде формувати кодований сигнал на вході блока 3 не пізніше за сигнал узагальненого переносу із блока 3 попередньої групи. Це дозволяє додатково збільшити швидкість суматора. Наприклад при m=256 і виборі k=4 для малорозрядного блока 4 та збільшенні розрядності на 1 для кожного наступного багаторозрядного блока 5, швидкість суматора при h=20 та g=18, в порівнянні з аналогом, значно збільшується. В схемі суматора за змінним модулем з груповим переносом (Фіг.5) уточнюється реалізація блоків 4 та 5. Багаторозрядні блоки 5 групового переносу, містять з'єднані з третього до останнього порозрядні блоки 6 групового переносу. Порозрядний блок 6 групового переносу другого розряду групи містить першу 7, другу 8 та третю 9 логічні схеми. На перший та другий входи першої логічної схеми 7 порозрядного блока 6 третього розряду групи підключено, відповідно, перший та другий виходи першої логічної схеми 7 порозрядного блока 6 другого розряду групи. На перший вхід другої логічної схеми 8 порозрядного блока 6 третього розряду групи підключено другий вихід першої логічної схеми 7 порозрядного блока 6 другого розряду групи. На другий вхід другої логічної схеми 8 порозрядного блока 6 третього розряду групи підключено вихід другої логічної схеми 8 порозрядного блока 6 другого розряду групи. На перший вхід третьої логічної схеми 9 порозрядного блока 6 третього розряду групи підключено перший вихід першої логічної схеми 7 порозрядного блока 6 другого розряду групи. На другий вхід третьої логічної схеми 9 порозрядного блока 6 третього розряду групи підключено вихід третьої логічної схеми 9 порозрядного блока 6 другого розряду групи. Перший вихід малорозрядного блока 4 групового переносу підключено до першого входу першої логічної схеми 7 та до першого входу третьої логічної схеми 9 порозрядного блока 6 другого розряду групи. Другий вихід малорозрядного блока 4 групового переносу підключено до другого входу першої логічної схеми 7 та до першого входу другої логічної схеми 8 порозрядного блока 6 другого розряду групи. Третій вихід малорозрядного блока 4 групового переносу підключено до другого входу другої логічної схеми 8 порозрядного блока 6 другого розряду групи. Четвертий вихід малорозрядного блока 4 групового переносу підключено до другого входу третьої логічної 6 UA 100006 U 5 схеми 9 порозрядного блока 6 другого розряду групи. На входи з третього по п'ятий першої 7, другої 8 та третьої 9 логічних схем порозрядного блока 6 другого розряду групи підключено первинні входи другого розряду операндів групи. На входи малорозрядного блока 4 групового переносу підключено первинні входи першого розряду операндів групи. Значення сигналів на виходах блока 4 формується на основі таблиці 2 в залежності від значень сигналів на первинних входах молодшого розряду операндів групи (для s=r) та подано в Табл. 11. Таблиця 11 0 0 0 0000 1234 10 0 0 1 1100 1234 0 1 0 0010 1234 0 1 1 1 0 0 1 0 1 0001 0010 0001 1234 1234 1234 Номер виходу блока 4 1 1 0 1111 1234 1 1 1 0011 1234 хr уr рr Затримка узагальненого сигналу переносу аналогічна затримці цього сигналу в суматорі за п. 3 формули, але для реалізації блока 4 достатньо чотирьох 4-розрядних LUT, замість 16, згідно з випадком по фіг. 4. Для реалізації схем 7, 8 та 9 необхідно 8 чотирьох розрядних LUT. Таким чином варіант реалізації за п. 4 формули корисної моделі орієнтовано на використання 4х розрядних LUT, які реалізовані в більшості мікросхем ПЛІС FPGA попередніх серій. 15 20 Джерела інформації: 1. Пат. № 68397 G06F 7/50 (2006.01). Багаторозрядний суматор по змінному модулю / Тарасенко В.П., Тесленко O.K., Роговенко А.І., Волік А.С.; НТУУ КПІ; заявл. 23.08.2011; опубл. 26.03.12. Бюл. № 6 2. Пат. № 61647 G06F 7/00 (2011.01). Комірка суматора за змінним модулем / Тарасенко В.П., Тесленко O.K., Роговенко А.І.; НТУУ KПІ; заявл. 29.12.2010; опубл. 25.07.2011. Бюл. № 14 ФОРМУЛА КОРИСНОЇ МОДЕЛІ 25 30 35 40 45 50 1. Багаторозрядний суматор за змінним модулем із груповим переносом, що містить від першого до третього первинні входи операндів, первинний вихід результату, об'єднаний блок (1) старших розрядів, що містить порозрядні комірки одного типу, об'єднаний блок (2) молодших розрядів, що містить порозрядні комірки другого типу, вихід сигналу SUB з об'єднаного блока (1) підключено до входів сигналу SUB комірок другого типу об'єднаного блока (2) молодших розрядів, який відрізняється тим, що для підвищення швидкості схема суматора містить додаткові об'єднані блоки (2) молодших розрядів, блоки (3) формування сигналу прискореного переносу в старші розряди, малорозрядні блоки (4) групового переносу, вихід кодованого сигналу малорозрядного блока (4) групового переносу поточної групи підключено до третього входу кодованого сигналу блока (3) поточної групи, до першого та другого входів якого підключено відповідно перший та другий виходи блока (3) формування сигналу прискореного переносу попередньої групи, які підключені також до першого та другого входів узагальненого переносу додаткового об'єднаного блока (2) поточної групи, до першого та другого входів блока (3) формування прискореного переносу першої групи підключено відповідно перший та другий виходи узагальненого сигналу переносу з об'єднаного блока (2) молодших розрядів, які підключено відповідно на перший та другий входи узагальненого сигналу переносу першого додаткового блока (2), а виходи останнього блока (3) формування узагальненого сигналу переносу в старші розряди підключено відповідно до першого та другого входів узагальненого переносу об'єднаного блока (1) старших розрядів, вихід сигналу SUB якого підключено до входу сигналу SUB додаткових об'єднаних блоків (2) молодших розрядів, на входи додаткових об'єднаних блоків (2) молодших розрядів поточної групи підключено первинні входи розрядів операндів поточної групи, які підключено також на входи малорозрядного блока (4) групового переносу поточної групи. 2. Багаторозрядний суматор за змінним модулем із груповим переносом за п. 1, який відрізняється тим, що для підвищення швидкості схема суматора містить з'єднані додаткові об'єднані блоки (2) молодших розрядів, та блоки (3) формування сигналу прискореного переносу в старші розряди, містить багаторозрядні блоки (5) групового переносу, які містять порозрядні блоки (6) групового переносу та малорозрядний блок (4) групового переносу, на 7 UA 100006 U 5 10 15 20 25 30 35 40 45 50 55 60 входи якого підключено первинні входи молодших розрядів операндів групи, на входи з першого по третій порозрядних блоків (6) групового переносу підключено відповідні входи наступних розрядів операндів групи, вихід кодованого сигналу малорозрядного блока (4) групового переносу підключено на четвертий вхід кодованого сигналу першого порозрядного блока (6) групового переносу, виходи кодованого сигналу порозрядних блоків (6) групового переносу підключено на четвертий вхід кодованого сигналу порозрядного блока (6) наступного розряду групи, вихід кодованого сигналу останнього порозрядного блока (6) підключено на вхід кодованого сигналу блока (3) формування сигналу прискореного переносу в старші розряди. 3. Багаторозрядний суматор за змінним модулем із груповим переносом за п. 2, який відрізняється тим, що порозрядні блоки (6) групового переносу містять першу (7), другу (8) та третю (9) логічні схеми поточних від третього до останнього розрядів операндів групи, виходи першої (7), другої (8) та третьої (9) логічних схем останнього порозрядного блока (6) підключені до третього кодованого сигналу блока (3) групового переносу групи, на перший та другий входи першої логічної схеми (7) поточного поразрядного блока (6) підключено відповідно перший та другий виходи першої логічної схеми (7) попереднього поразрядного блока (6), на перший вхід другої логічної схеми (8) поточного порозрядного блока (6) підключено другий вихід першої логічної схеми (7) попереднього поразрядного блока (6), на другий вхід другої логічної схеми (8) поточного порозрядного блока (6) підключено вихід другої логічної схеми (8) попереднього порозрядного блока (6), на перший вхід третьої логічної схеми (9) поточного порозрядного блока (6) підключено перший вихід першої логічної схеми (7) попереднього порозрядного блока (6), на другий вхід третьої логічної схеми (9) поточного порозрядного блока (6) підключено вихід третьої логічної схеми (9) попереднього порозрядного блока (6), перший вихід малорозрядного блока (4) групового переносу підключено до першого входу першої логічної схеми (7) та до першого входу третьої логічної схеми (9) порозрядного блока (6) третього розряду групи, другий вихід малорозрядного блока (4) групового переносу підключено до другого входу першої логічної схеми (7) та до першого входу другої логічної схеми (8) порозрядного блока (6) третього розряду групи, третій вихід малорозрядного блока (4) групового переносу підключено до другого входу другої логічної схеми (8) порозрядного блока (6) третього розряду групи, четвертий вихід малорозрядного блока (4) групового переносу підключено до другого входу третьої логічної схеми (9) порозрядного блока (6) третього розряду групи, на входи з третього по п'ятий першої (7), другої (8) та третьої (9) логічних схем порозрядних блоків (6) підключено первинні входи відповідного розряду операндів групи, на перші три входи малорозрядного блока (4) групового переносу підключено первинні входи першого розряду операндів групи, на входи з четвертого по шостий підключено первинні входи другого розряду операндів групи. 4. Багаторозрядний суматор за змінним модулем із груповим переносом за п. 2, який відрізняється тим, що багаторозрядні блоки (5) групового переносу, містять з'єднані з третього до останнього порозрядні блоки (6) групового переносу, порозрядний блок (6) групового переносу другого розряду групи, який містить першу (7), другу (8) та третю (9) логічні схеми, на перший та другий входи першої логічної схеми (7) порозрядного блока (6) третього розряду групи підключено відповідно перший та другий виходи першої логічної схеми (7) порозрядного блока (6) другого розряду групи, на перший вхід другої логічної схеми (8) порозрядного блока (6) третього розряду групи підключено другий вихід першої логічної схеми (7) порозрядного блока (6) другого розряду групи, на другий вхід другої логічної схеми (8) порозрядного блока (6) третього розряду групи підключено вихід другої логічної схеми (8) порозрядного блока (6) другого розряду групи, на перший вхід третьої логічної схеми (9) порозрядного блока (6) третього розряду групи підключено перший вихід першої логічної схеми (7) порозрядного блока (6) другого розряду групи, на другий вхід третьої логічної схеми (9) порозрядного блока (6) третього розряду групи підключено вихід третьої логічної схеми (9) порозрядного блока (6) другого розряду групи, перший вихід малорозрядного блока (4) групового переносу підключено до першого входу першої логічної схеми (7) та до першого входу третьої логічної схеми (9) порозрядного блока (6) другого розряду групи, другий вихід малорозрядного блока (4) групового переносу підключено до другого входу першої логічної схеми (7) та до першого входу другої логічної схеми (8) порозрядного блока (6) другого розряду групи, третій вихід малорозрядного блока (4) групового переносу підключено до другого входу другої логічної схеми (8) порозрядного блока (6) другого розряду групи, четвертий вихід малорозрядного блокау (4) групового переносу підключено до другого входу третьої логічної схеми (9) порозрядного блока (6) другого розряду групи, на входи з третього по п'ятий першої (7), другої (8) та третьої (9) логічних схем поразрядного блока (6) другого розряду групи підключено первинні входи другого розряду операндів групи, на входи малорозрядного блока (4) групового переносу підключено первинні входи першого розряду операндів групи. 8 UA 100006 U 9 UA 100006 U 10 UA 100006 U 11 UA 100006 U 12 UA 100006 U Комп’ютерна верстка М. Мацело Державна служба інтелектуальної власності України, вул. Василя Липківського, 45, м. Київ, МСП, 03680, Україна ДП “Український інститут інтелектуальної власності”, вул. Глазунова, 1, м. Київ – 42, 01601 13

ДивитисяДодаткова інформація

Автори англійськоюRohovenko Andrii Ivanovych, Tarasenko Volodymyr Petrovych, Teslenko Oleksandr Kyrylovych

Автори російськоюРоговенко Андрей Иванович, Тарасенко Владимир Петрович, Тесленко Александр Кирилович

МПК / Мітки

Мітки: груповим, суматор, багаторозрядний, змінним, модулем, переносом

Код посилання

<a href="https://ua.patents.su/15-100006-bagatorozryadnijj-sumator-za-zminnim-modulem-z-grupovim-perenosom.html" target="_blank" rel="follow" title="База патентів України">Багаторозрядний суматор за змінним модулем з груповим переносом</a>

Попередній патент: Магнітоелектрична форсунка

Наступний патент: Спосіб усунення бурчання в животі у пацієнтів з алкогольною пивною залежністю в стадії ремісії

Випадковий патент: Навісна жатка "maans-contour f"