Пристрій для обміну інформацією між еом і зовнішньою пам’яттю

Номер патенту: 322

Опубліковано: 30.04.1993

Автори: Драгунов Володимир Костянтинович, Зуйко Володимир Михайлович, Вировец Тетяна Іванівна, Роза Тамар Йосипівна

Формула / Реферат

Формула изобретения

Устройство для обмена информацией между ЭВМ и внешней памятью, содержащее блок микропрограммного управления, арифметико-логический блок, блок сопряжения с ЭВМ и блок сопряжения с памятью, группа информационно-управляющих входов и выходов блока сопряжения с ЭВМ является группой входов-выходов устройства для подключения к ЭВМ, группа информационно-управляющих входов и выходов блока сопряжения с памятью - группой входов-выходов для подключения к внешней памяти, первая группа выходов блока микропрограммного управления соединена с группой стробирующих входов блока сопряжения с ЭВМ; управляющий выход которого соединен с управляющим входом арифметико-логического блока, управляющий выход которого соединен с входом логического условия блока микропрограммного управления, отличающееся тем, что, с целью повышения скорости обмена информацией, в устройство введены дешифратор управления шинами, внутренняя оперативная память, мультиплексор, демультиплексор и буферная память данных, вторая-шестая группы выходов блока микропрограммного управления соединены соответственно с группами входов адреса, инструкций, режима арифметико-логического блока, группой входов дешифратора управления шинами и первым информационным входом мультиплексора, выход которого соединен с группой информационных входов арифметико-логического блока, первый выход блока микропрограммного управления соединен с синхровходом внутренней оперативной памяти группа режимных входов которой соединена с первой группой выходов дешифратора управления шинами, вторая и третья группы выходов которого соединены с группами управляющих входов соответственно мультиплексора и демультиплексора, группа выходов арифметико-логического блока соединена с группой информационных входов демультиплексора, четвертая группа выходов дешифратора управления шинами - с первой группой управляющих входов буферной памяти данных, первая группа информационных входов, первая группа информационных выходов и группа выходов состояния которой соединены соответственно с первой группой выходов демультиплексора, второй и третьей группами информационных входов мультиплексора, вторые группы информационных входов и выходов, вторая группа управляющих входов и управляющий выход буферной памяти данных соединены соответственно с первыми информационными группами входов и выходов, группой управляющих выходов и управляющим входом блока сопряжения с памятью, группа управляющих входов и вторая группа информационных выходов которого соединены соответственно с второй группой выходов демультиплексора и четвертой группой информационных входов мультиплексора, пятая и шестая группы информационных входов которого соединены соответственно с группами информационных выходов блока сопряжения с ЭВМ и внутренней оперативной памяти, группы информационных входов которых соединены соответственно с 20 третьей и четвертой группами выходов демультиплексора, пятая и шестая группы выходов которого соединены соответственно с адресными входами блока микропрограммного управления и внутренней оперативной памяти, управляющий выход блока сопряжения с памятью соединен с управляющим входом блока сопряжения с ЭВМ, второй выход блока микропрограммного управления - с вторым управляющим входом блока сопряжения с памятью.

Текст

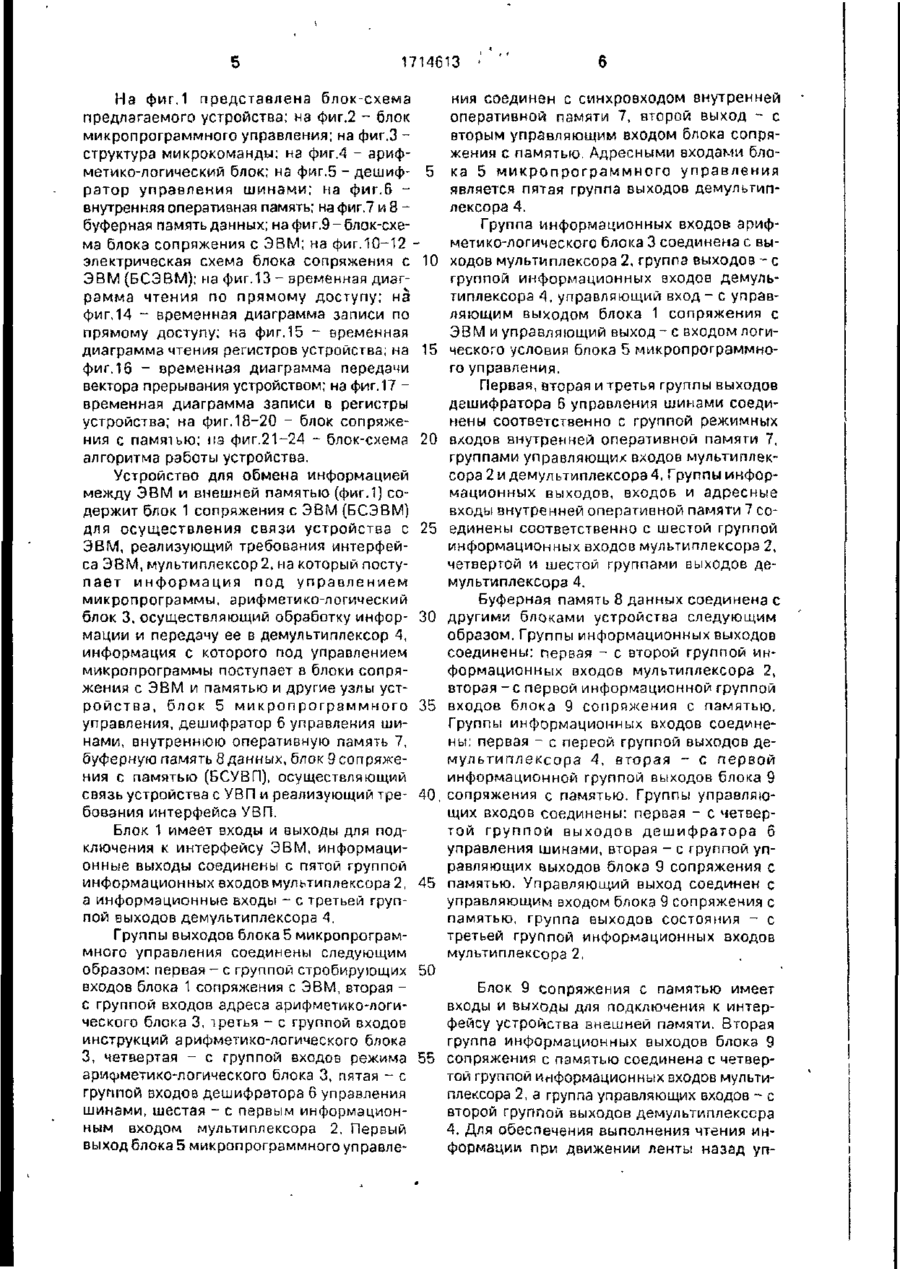

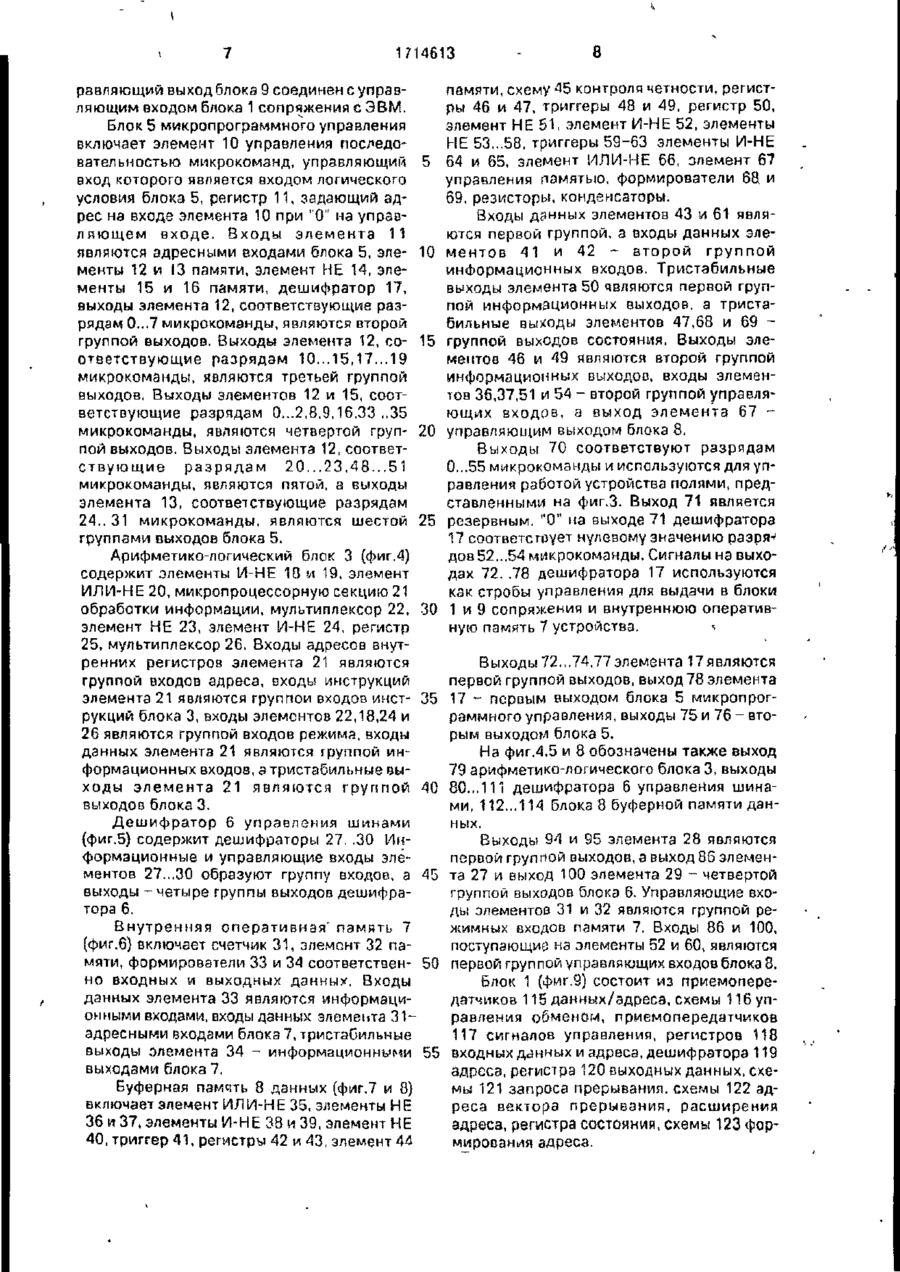

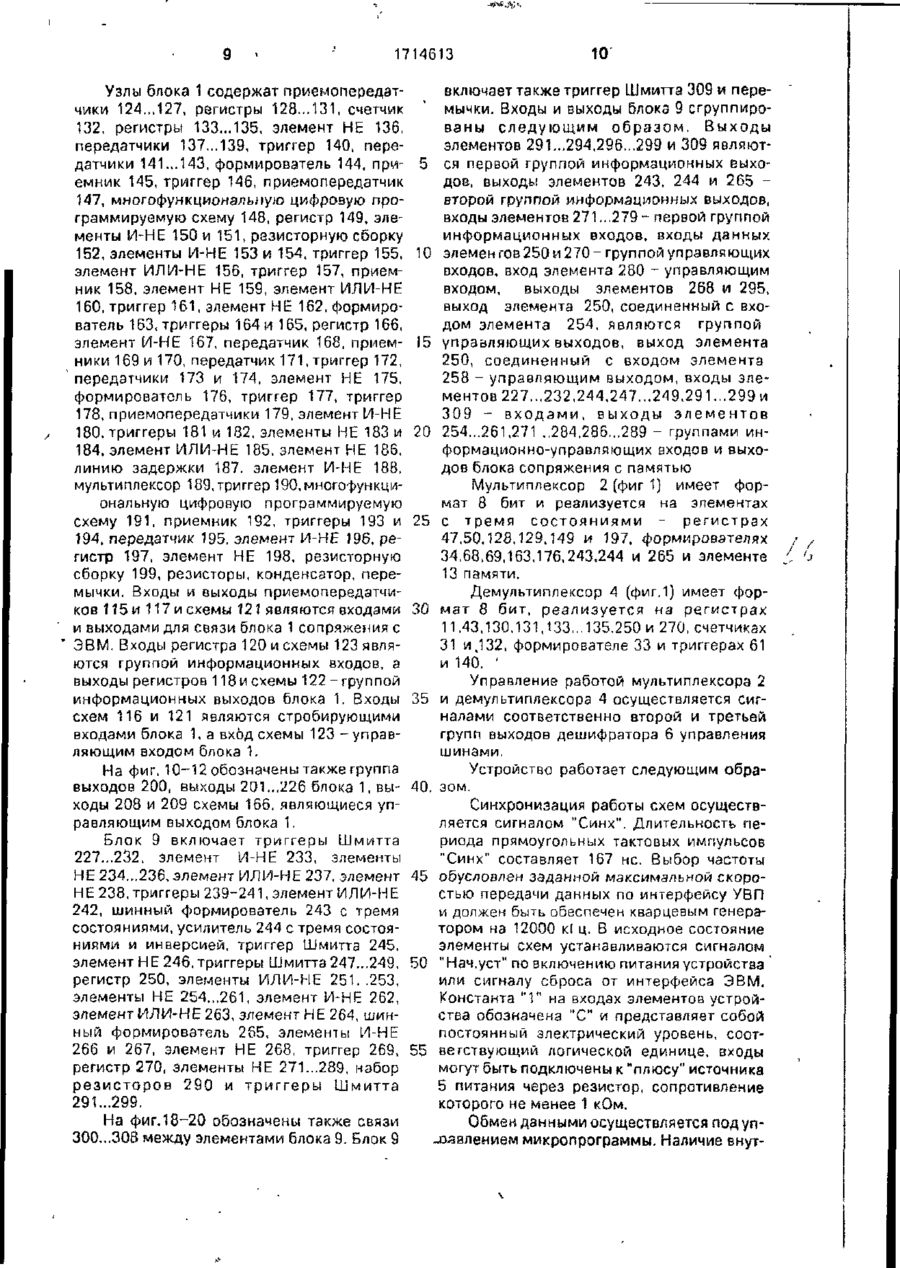

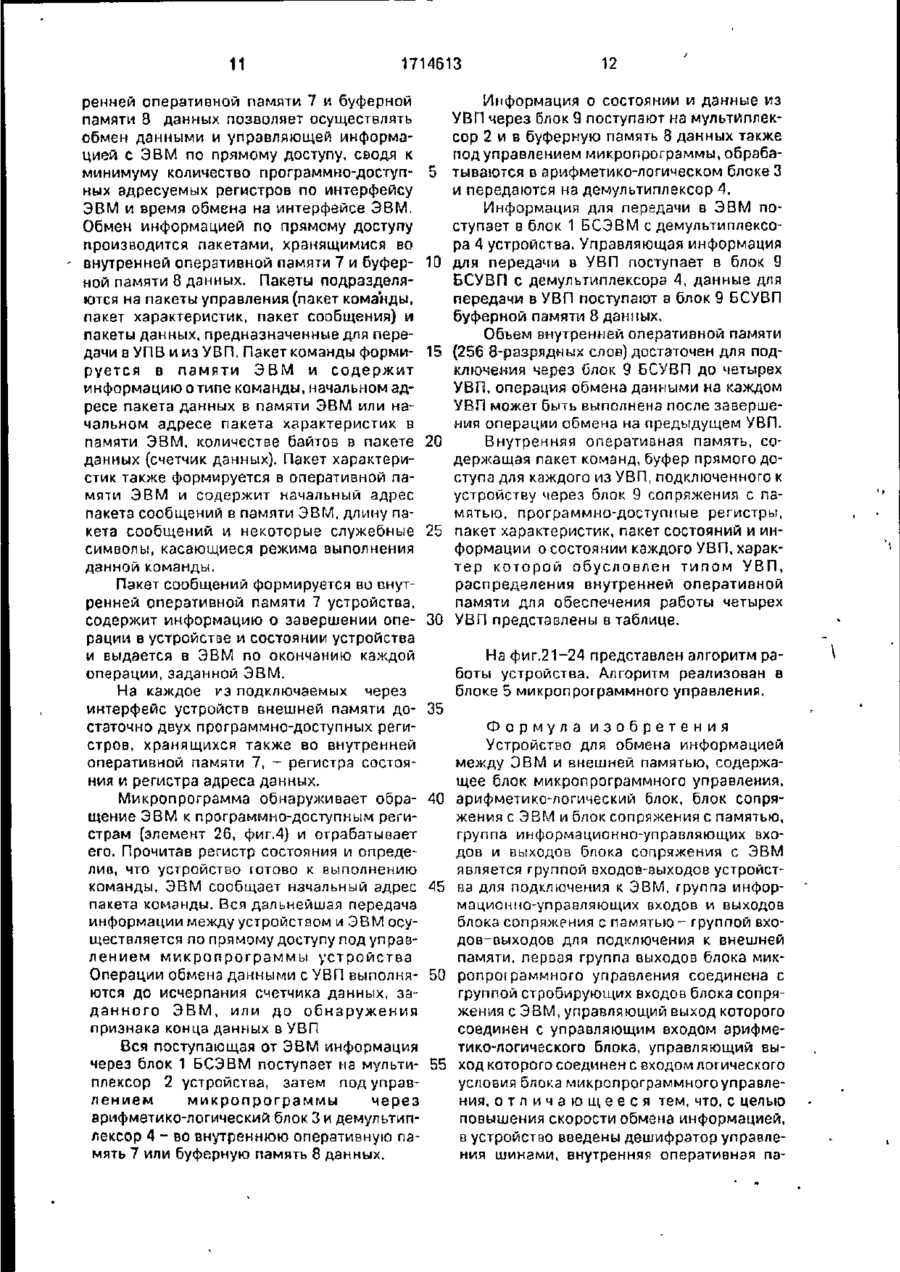

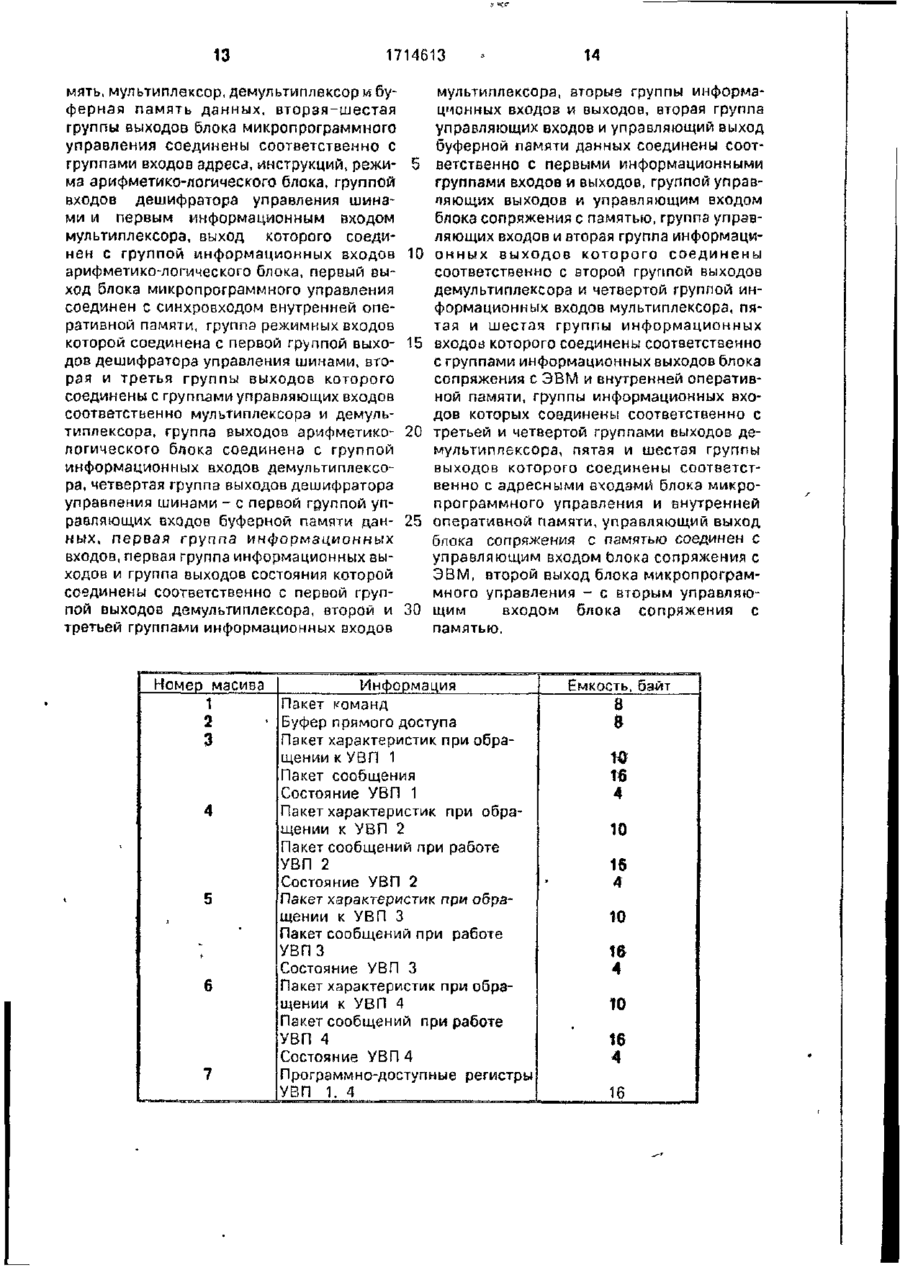

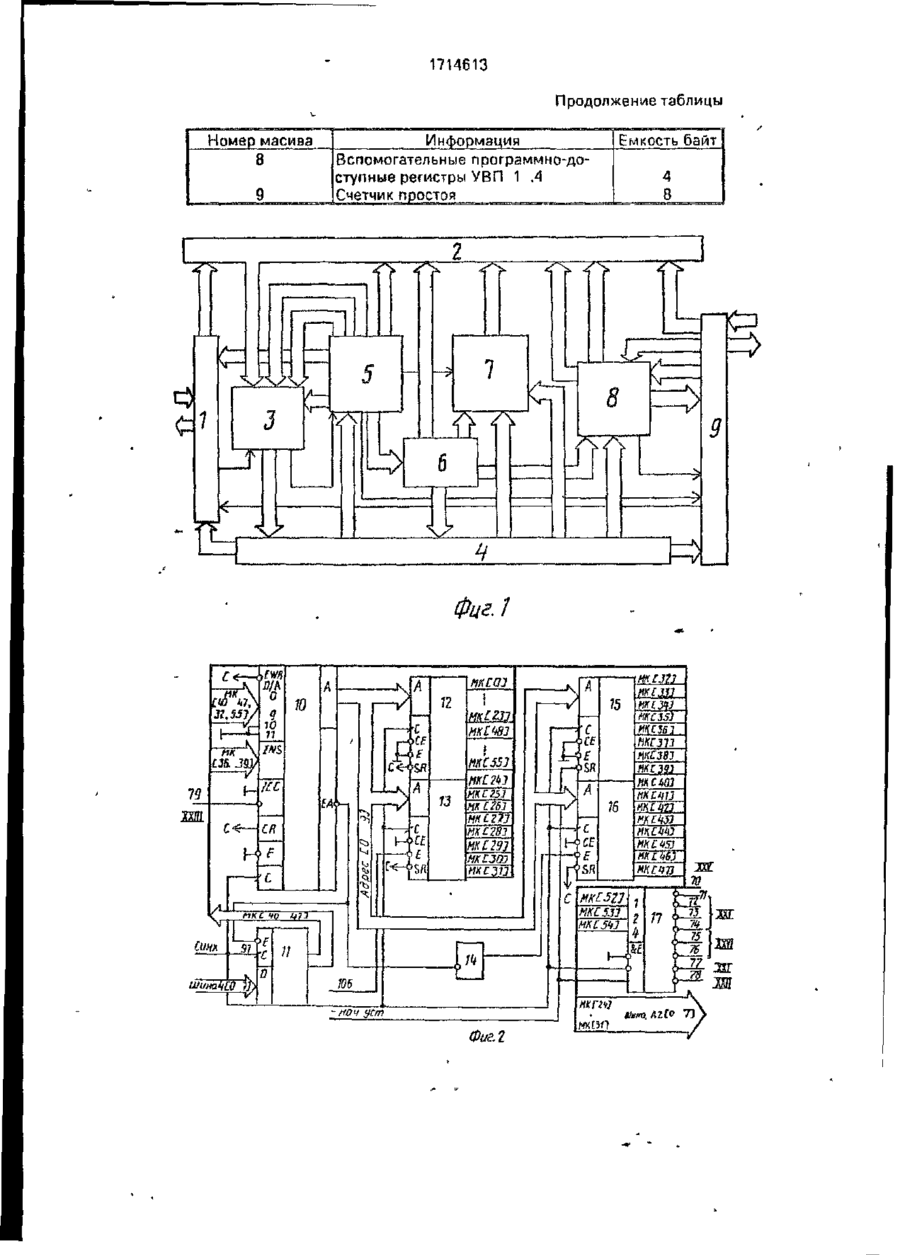

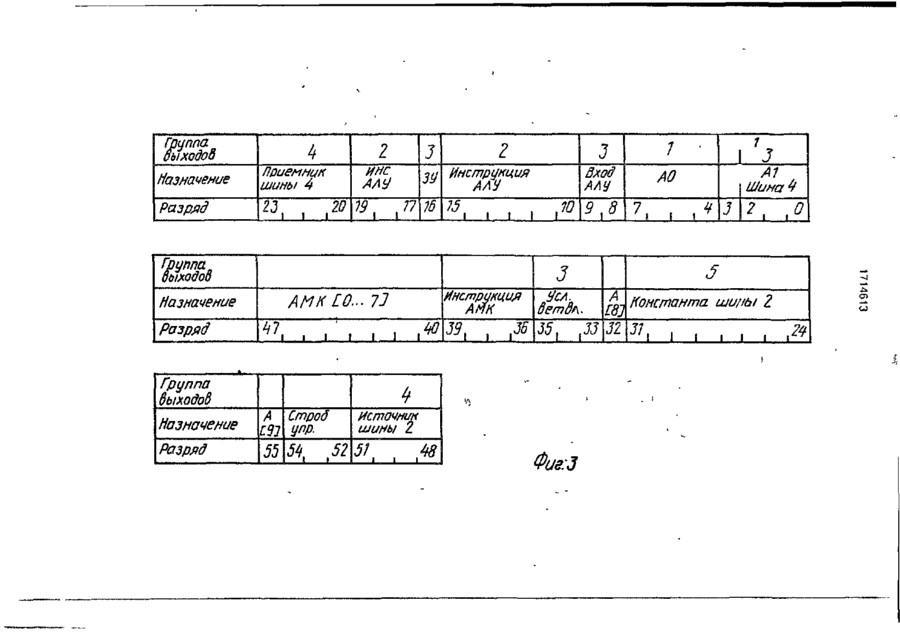

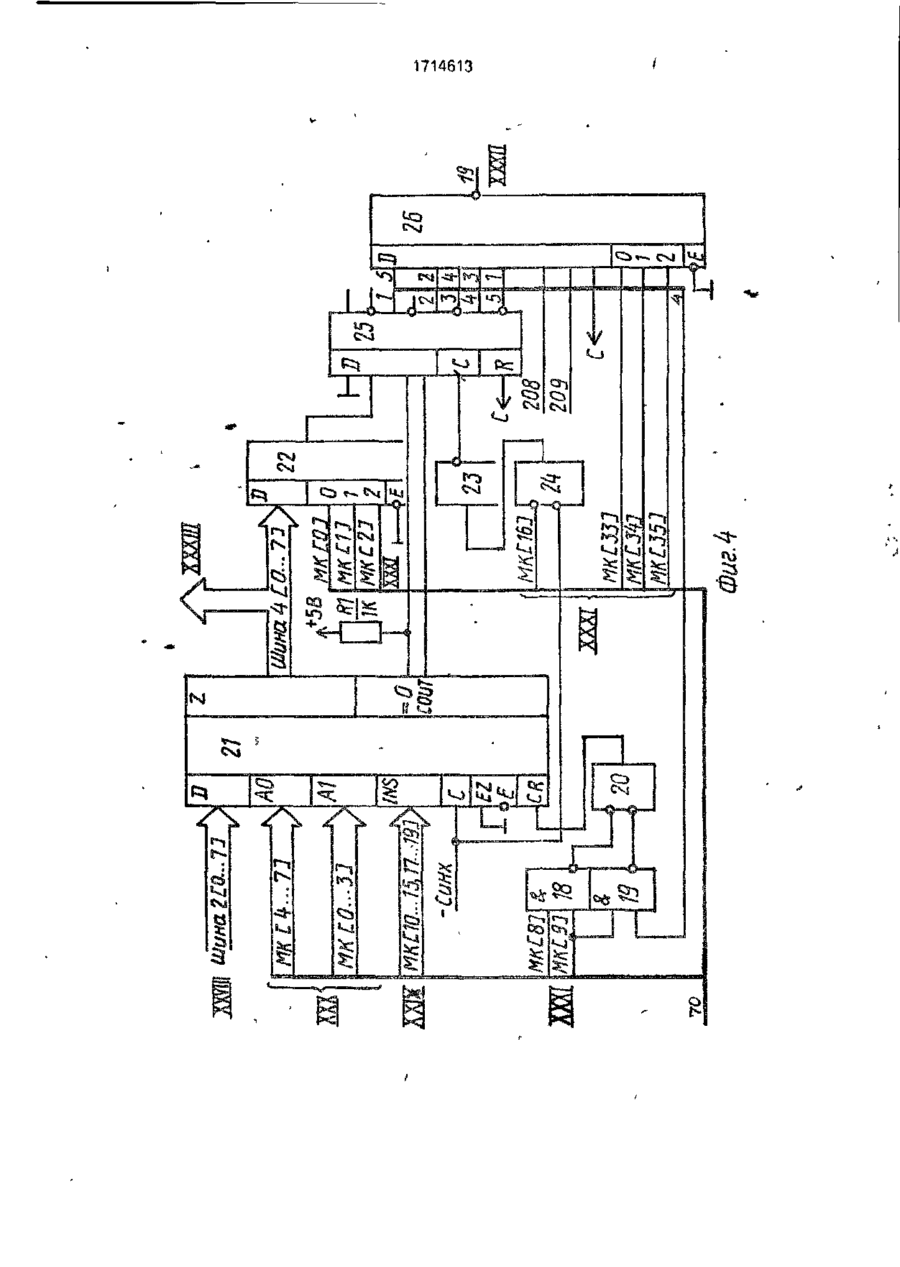

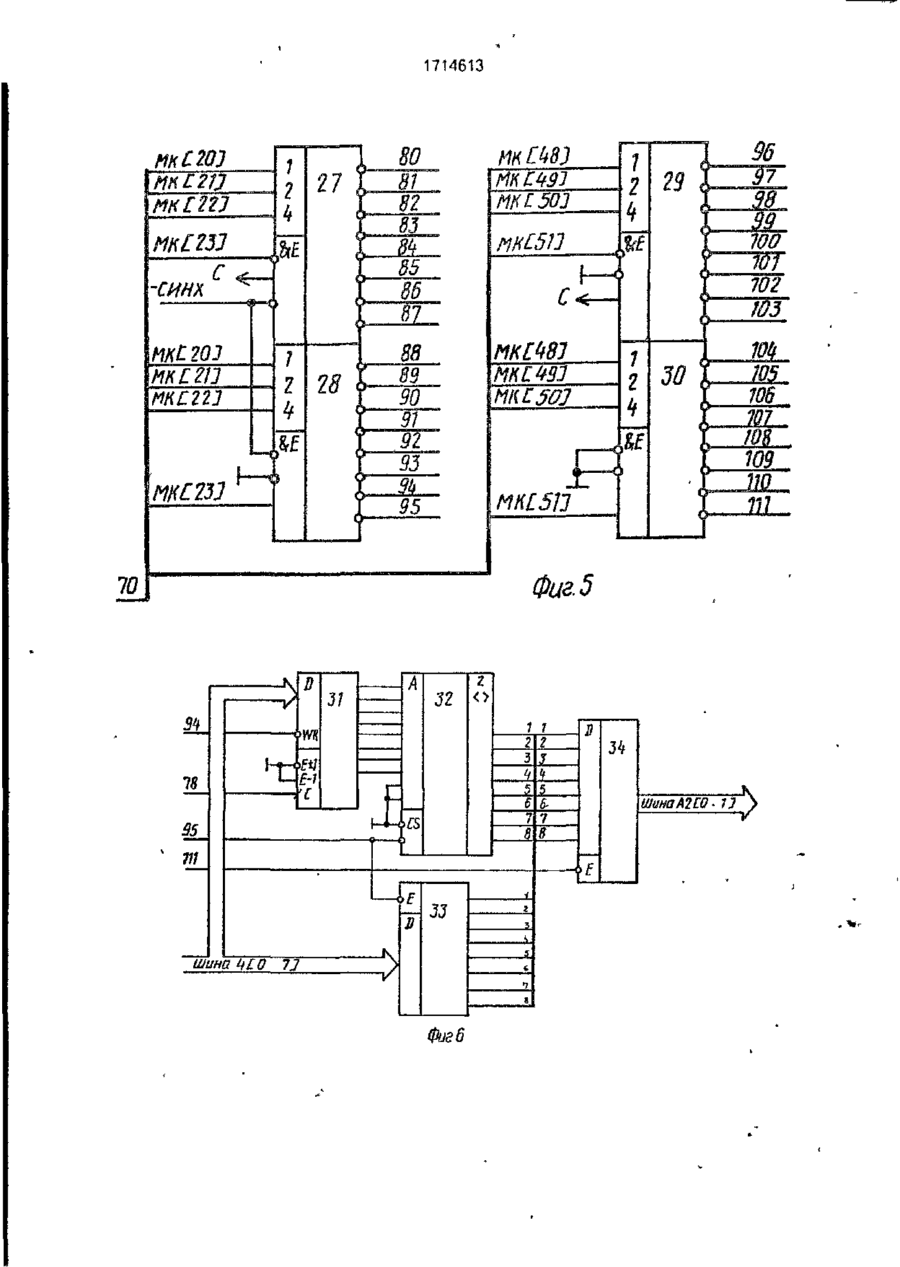

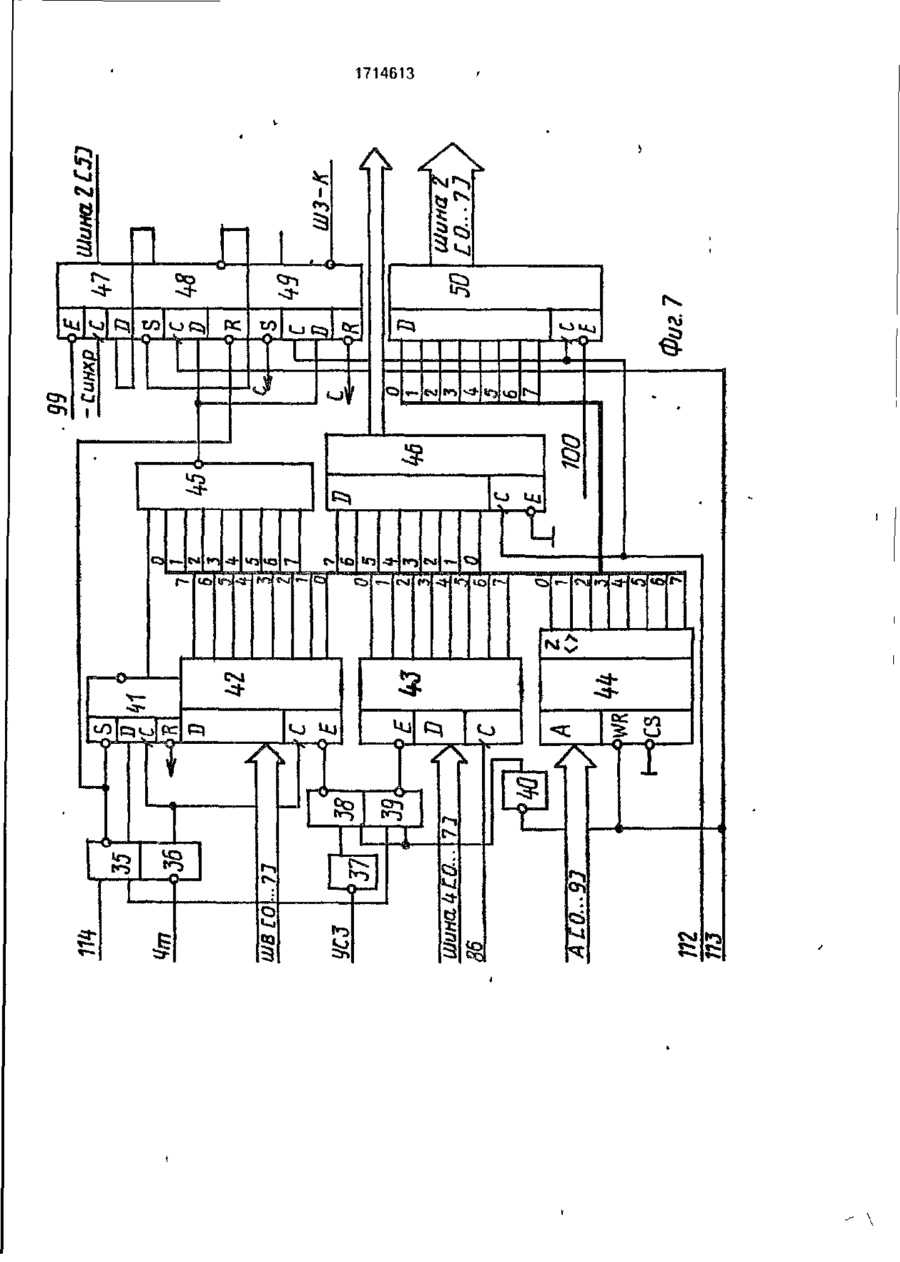

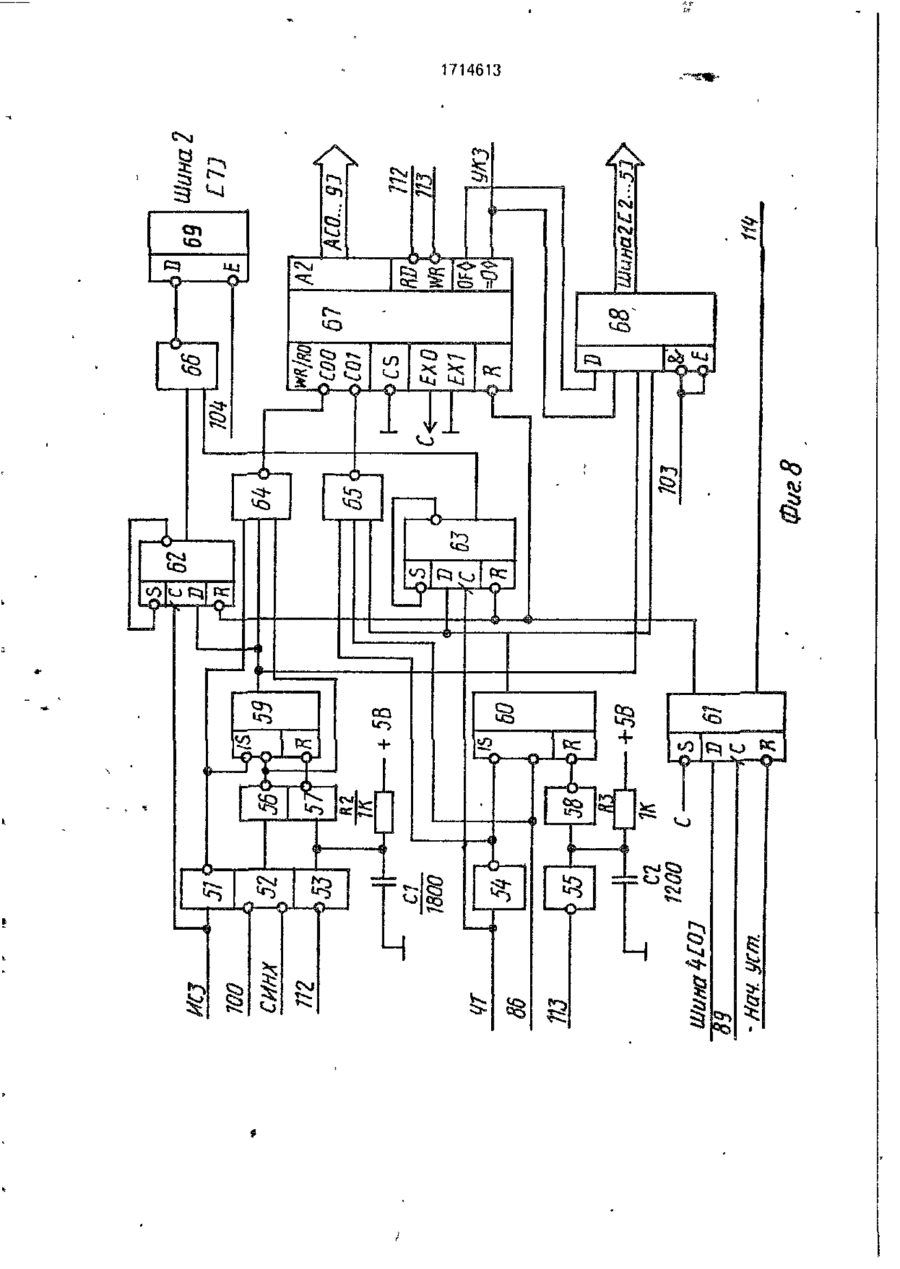

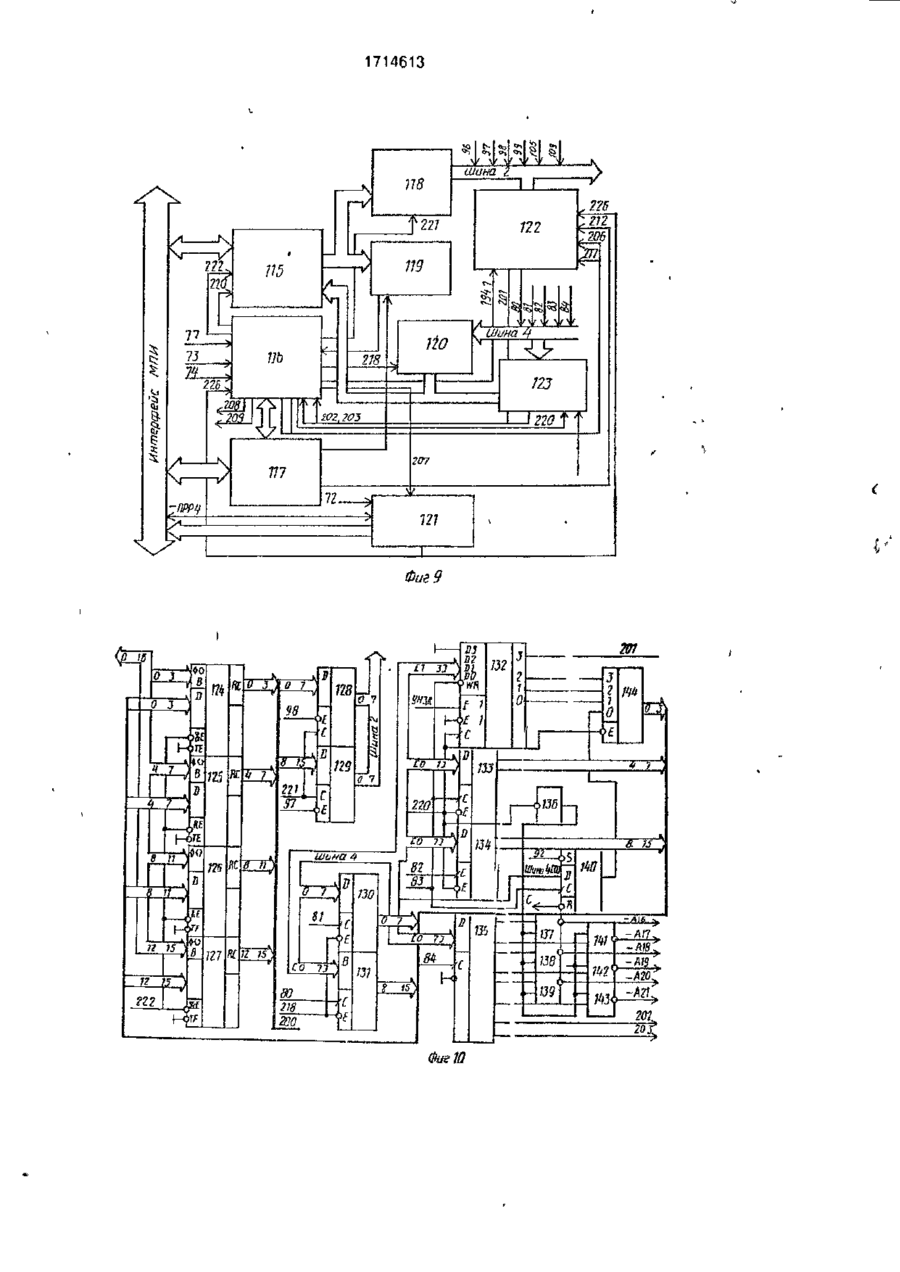

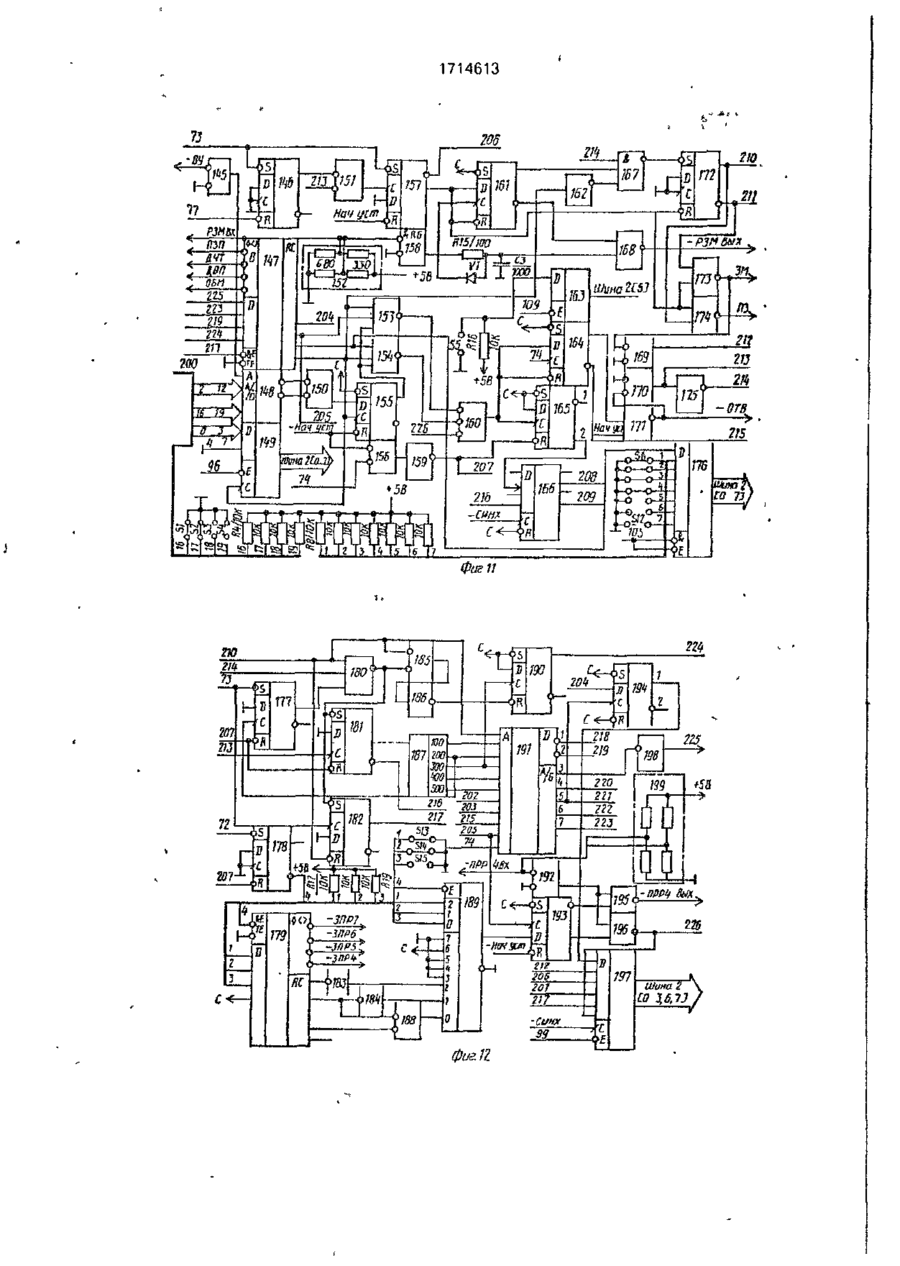

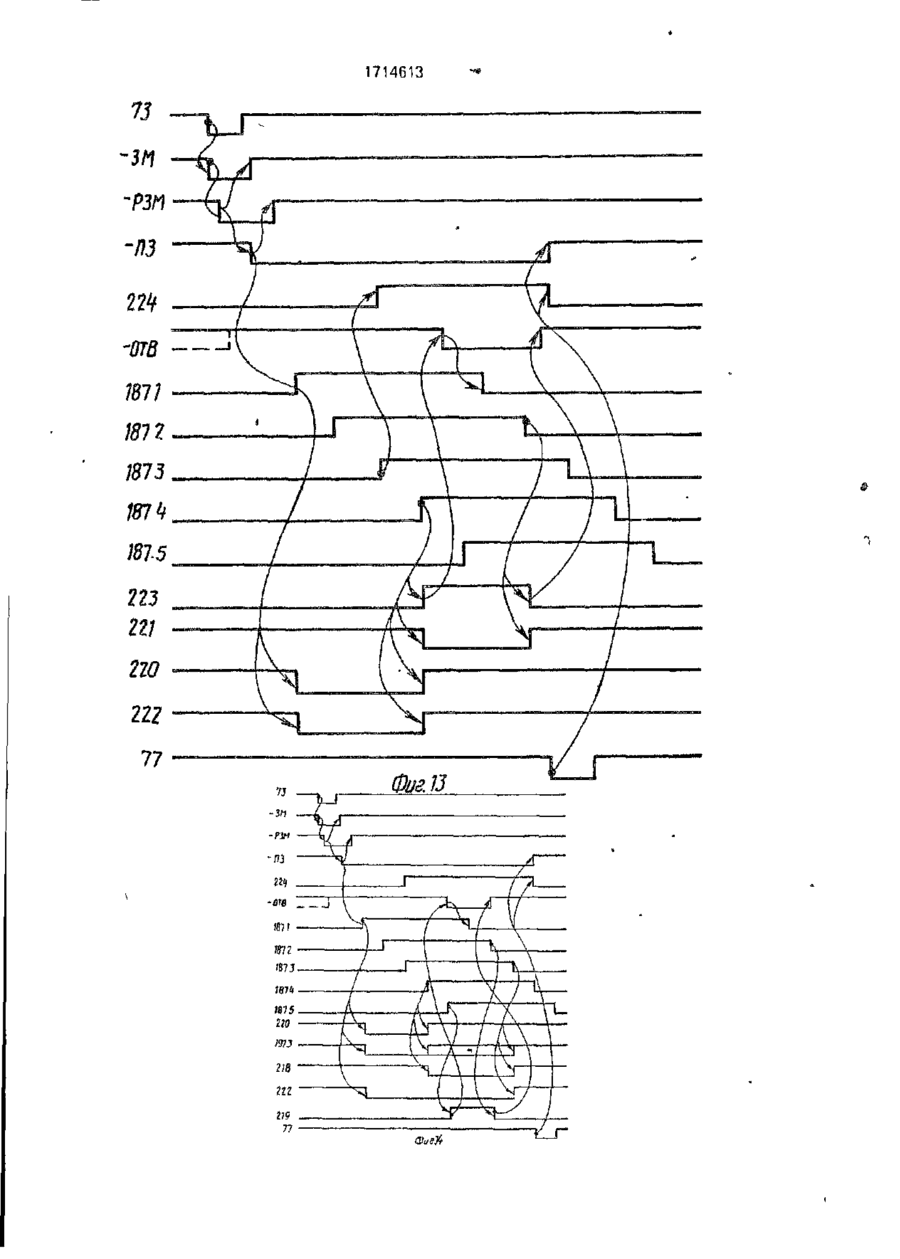

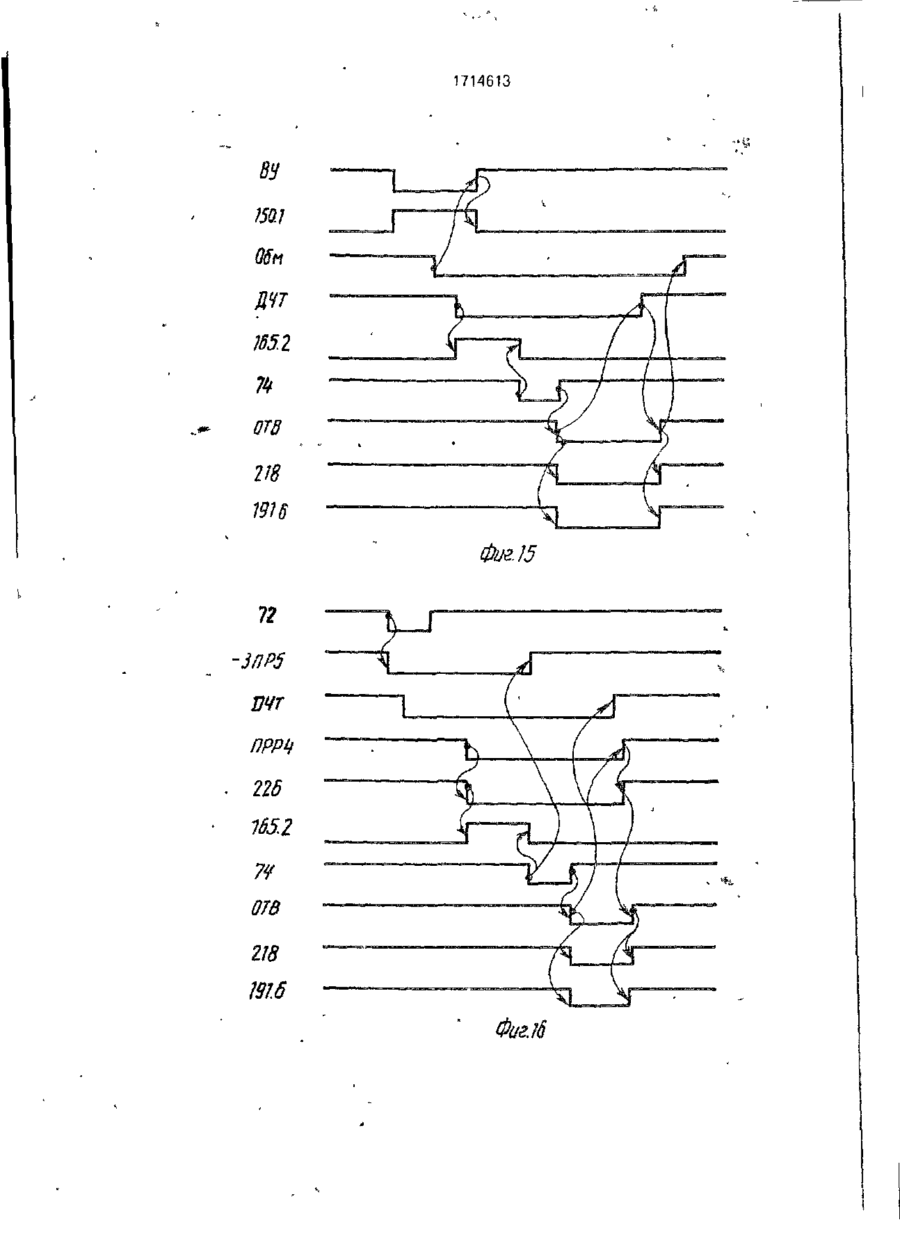

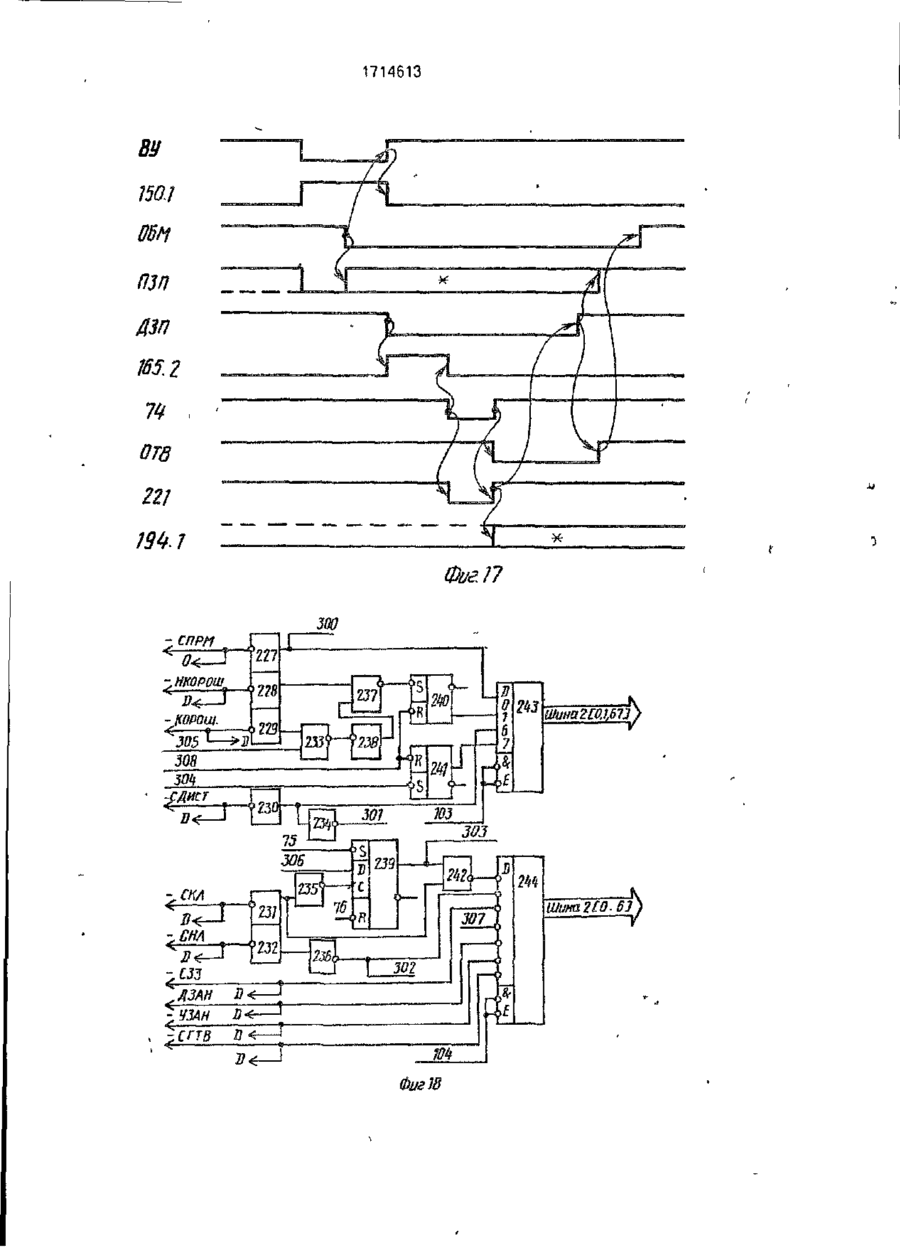

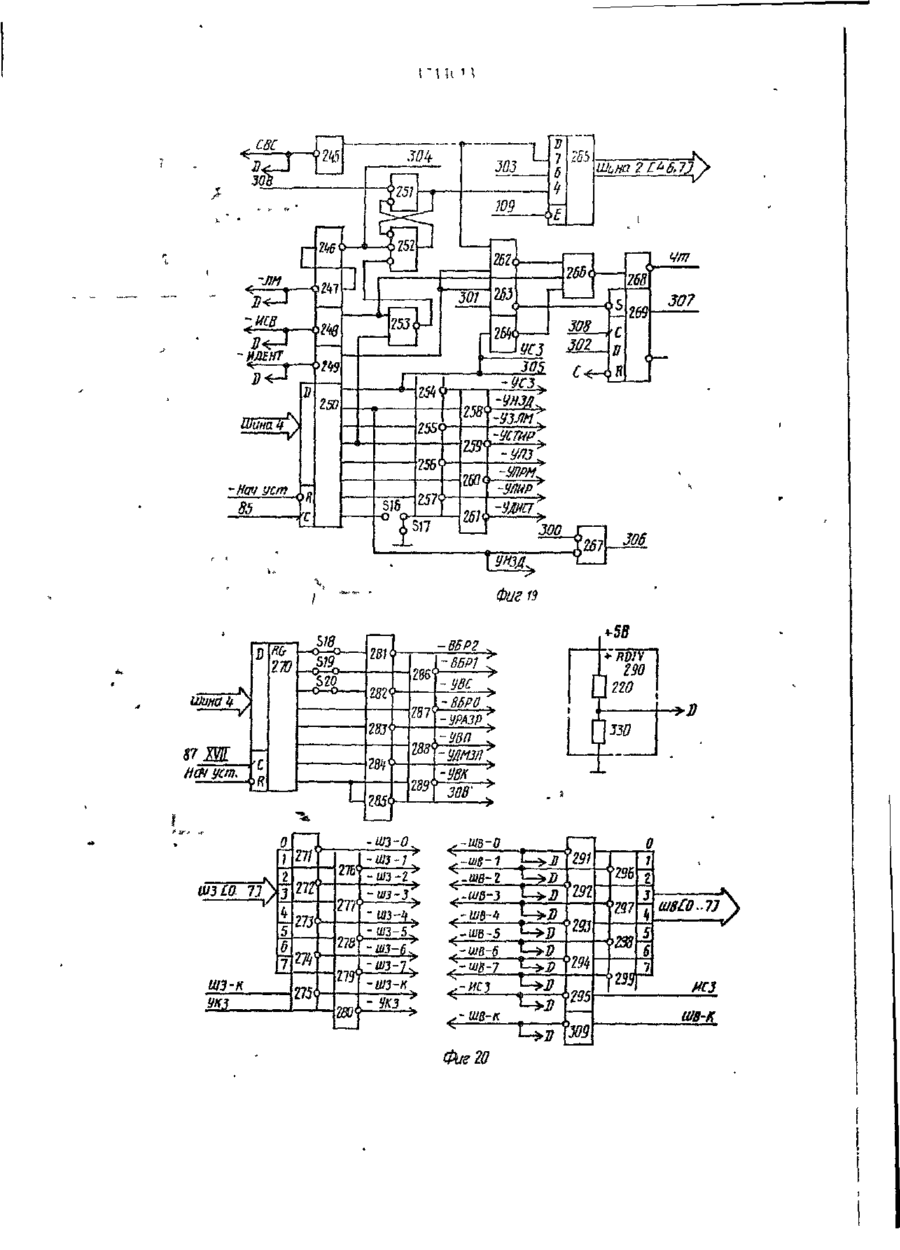

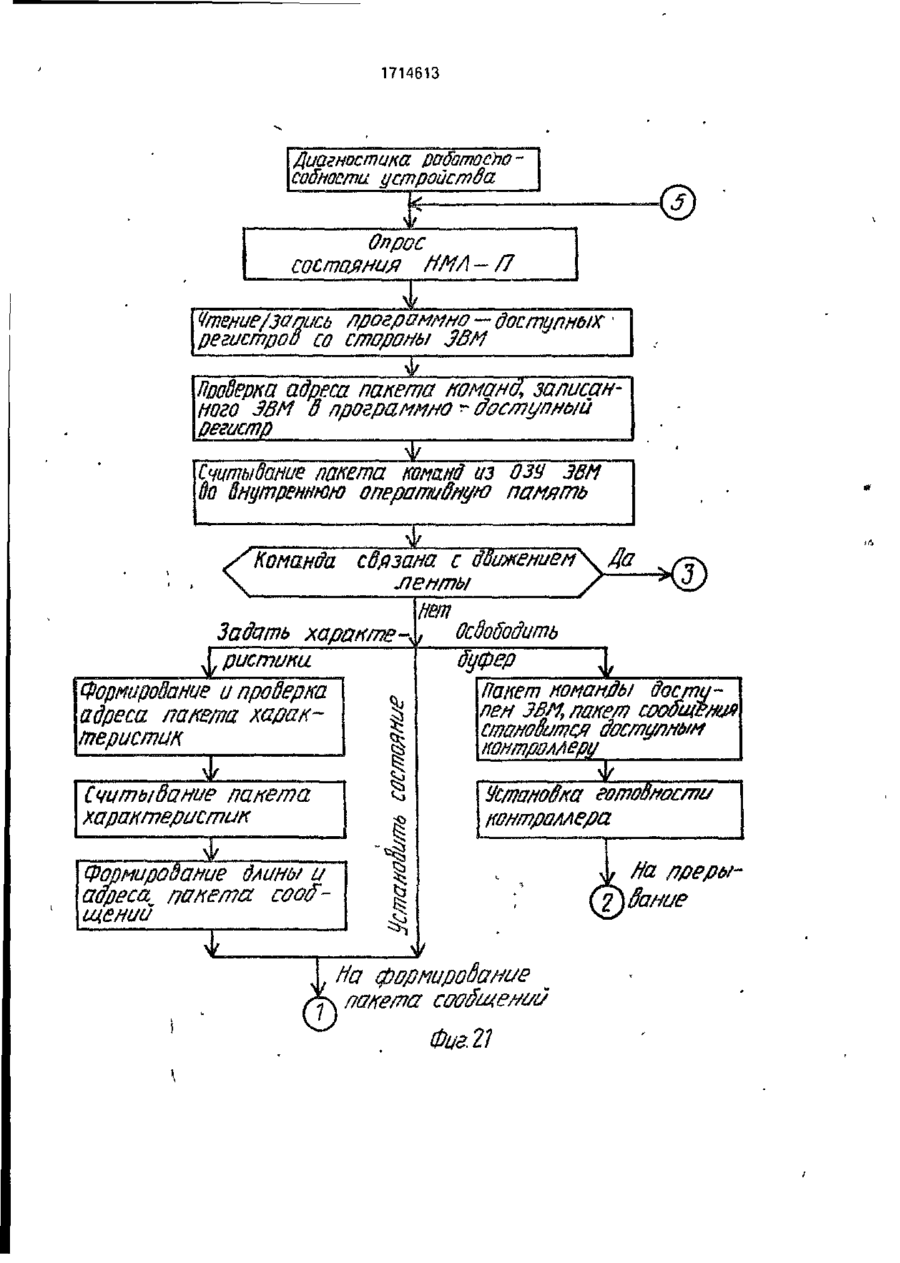

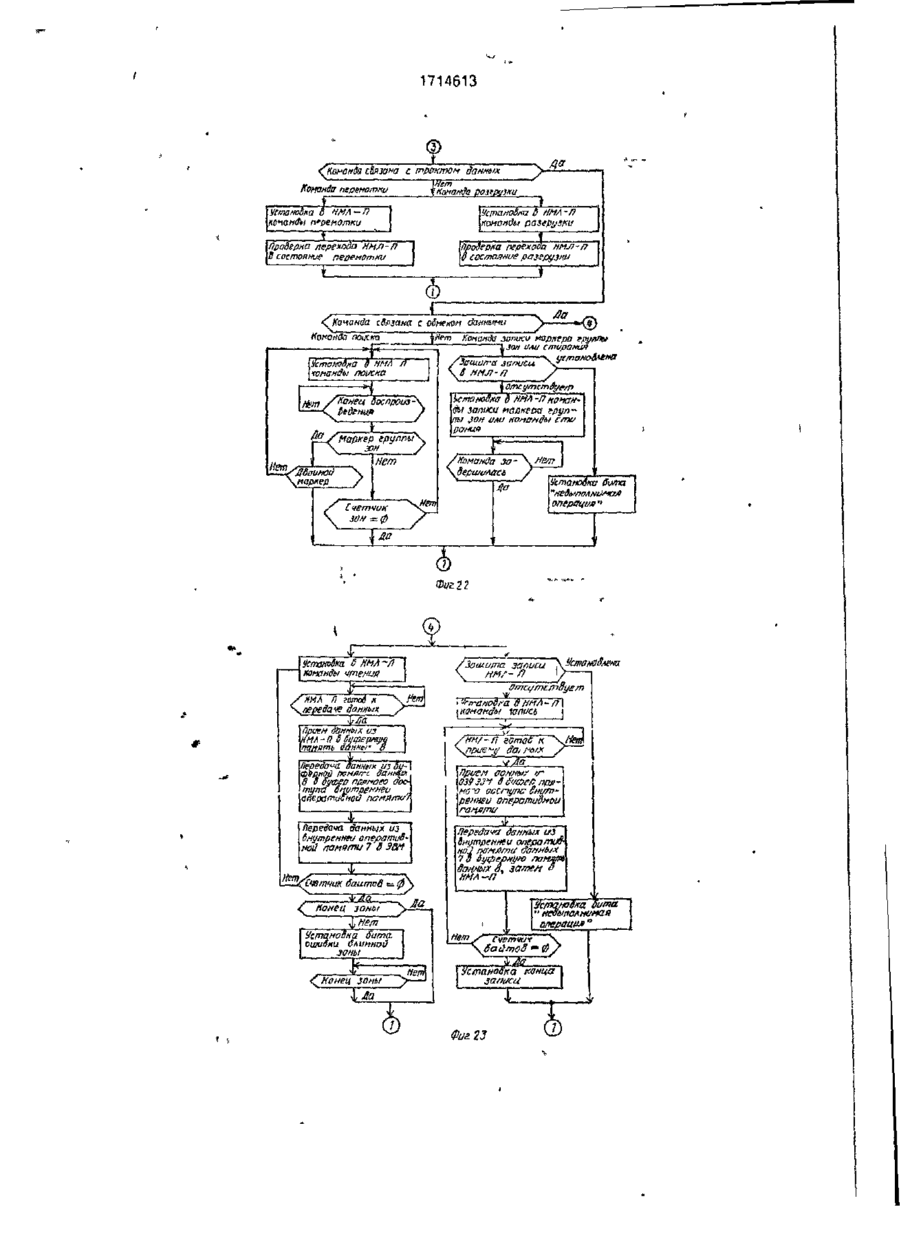

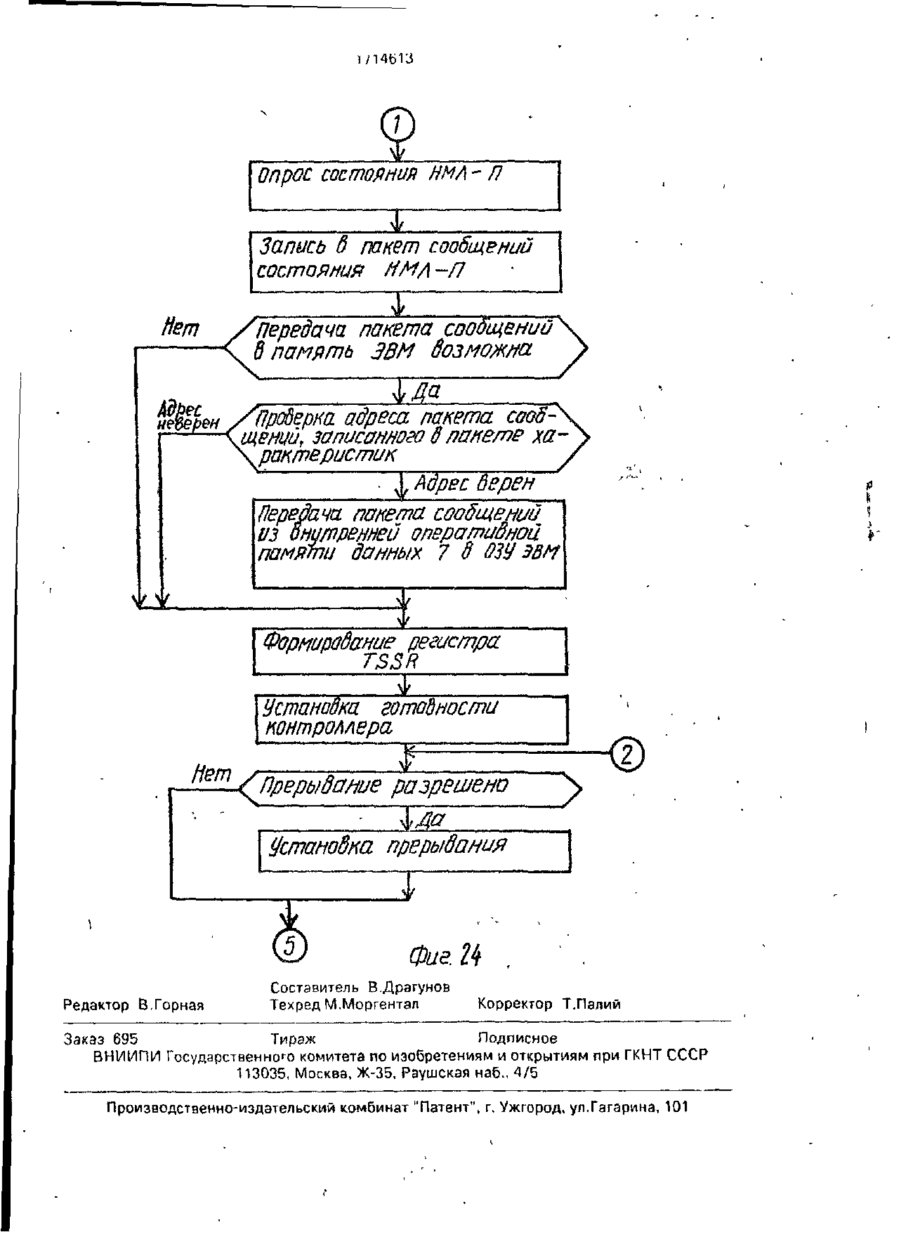

Изобретение относится к вычислительной технике и может быть использовано в ЭВМ, использующих магистральный параллельный интерфейс (МПИ) для реализации обмена информацией между ЭВМ и устройствами внешней памяти (УПВ), использующими другие интерфейсы Оно может быть применено при необходимости обмена информацией между ЭВМ и накопителями на магнитной ленте Изобретение позволяет увеличить скорость обмена информацией между ЭВМ и устройствами внешней памяти до 200 бит/с за счет того, что в устройство, содержащее блок микропрограммного управления, арифметико-логический блок, блоки сопряжения с ЭВМ и памятью, введены дешифратор управления шинами, внутренняя оперативная память, мультиплексор, демультиплексор, буферная память" данных 24 ил., 1 тэбл Изобретение относится к вычислительной технике и может быть использовано в ЭВМ, использующих магистральный параллельный интерфейс (МПИ) для реализации обмена информацией между ЭВМ и устройствами внешней памяти (УВП), использующими другие интерфейсы, в частности может быть применено при необходимости обмена информацией между ЭВМ и устройством внешней памяти Известно устройство для сопряжения внешних устройств с электронной вычислительной машиной, содержащее дешифратор адреса, блок выполнения программных прерываний, блок обмена, мультиплексор адреса, регистр команды, регистр адреса первого внешнего устройства, регистр адреса второго внешнего устройства, узел задания последовательности операций, счетчик фаз, коммутатор запросов, регистры начального и текущего адреса, регистры начальной и текущей длины массива, регистр циклов, узел перезаписи, мультиплексор данных, узел записи и узел чтения, узел выполнения прерываний для внепроцессорного обмена два блока усиления, причем группы входоввыходов блоков усиления являются соответственно первой и второй группами входов-выходов устройства. Наиболее близким техническим решением к предлагаемому является устройство для обмена информацией между ЭВМ и периферийными устройствами, содержащее дешифратор адреса, два блока прерывания, регистр команд и состояний, регистр текущего адреса, регистр данных, блок формирователей сигналов обмена и два блока усиления, блок микропрограммного управ 1714613 ления, блок синхронизации,блок регистров коррекции ошибок, блок регистрации состояния, регистр управляющих сигналов, регистр вывода, блок формирования признаков состояния. 5 Недостатком данного устройства является низкая скорость обмена информацией. Целью изобретения является повышение скорости обмена информацией между ЭВМиУВП. 10 Поставленная цель достигается тем, что в устройство обмена информацией между ЭВМ и внешней памятью, содержащее блок микропрограммного управления, арифметико-логический блок, блок сопряжения с 15 ЭВМ и блок сопряжения с внешней памятью введены внутренняя оперативная память, буферная память данных, две внутренние шины (мультиплексор и демультиплексор), дешифратор управления шина- 20 ми, первая-шестяя группы выходов блока микропрограммного управления соединены соответственно с группой стробирующих входов блока сопряжения с ЭВМ, группой входов адреса, инструкций и режи- 25 ма арифметико-логического блока, группой входов дешифратора управления шинами и первым информационным входом мультиплексора, первый выход блока микропрограммного управления соединен с 30 синхровходом внутренней оперативной памяти, группа режимных входов которого соединена с первой группой выходов дешифратора управления шинами, четвертая группа управляющих выходов которого соединена с первой группой управляющих 35 входов буферной памяти данных а вторая и третья группы выходов соединены с группами управляющих входов мультиплексора и демультиплексора, группа информационных входов и адресные входы внутренней 40 оперативной памяти соединены соответственно с четвертой и шестой группами выходов демультиплексора, пятая группа выходов которого соединена с адресными входами блока микропрограммного управ- 45 ления, группа информационных выходов внутренней оперативной памяти соединена с шестой группой информационных входов мультиплексора. 50 Группа информационных входов и управляющий вход арифметико-логического блока соединены соответственно с выходом мультиплексора и управляющим выходом блока сопряжения с ЭВМ, группа выходов ш 55 управляющий выход арифметико-логического блока соединены соответственно с группой информационных ЕХОДОВ демультиплексора и входом логичесгого условия блока микропрограммного управления. Первая и вторая группы информационных оходов буферной памяти данных соединены соответственно с первой группой выходов демультиплексора и первой информационной группой выходов блока сопряжения с памятью, группа управляющих выходов и управляющий вход которого соединены соответственно с второй группой управляющих входов и управляющим выходом буферной памяти данных, группа выходов состояния которой соединена с третьей группой информационных входов мультиплексора, а первая и вторая группы информационных выходов соединены соотвегственно с второй группой информационных входов мультиплексора и первой информационной группой входов блока сопряжения с памятью, вторая группа информационных оыходоа которого соединена с четвертой группой информационных входов мультиплексора, а группа управляющих входов - с второй группой выходов демультиплексора Группы информационных входов и выходов блока сопряжения с ЭВМ соединены соответственно с третьей группой выходов демультиплексора и пятой группой информационных входов мультиплексора. Второй выход блока микропрограммного управления соединен с вторым упрзвляющим входом блока сопряжения с памятью, управляющий выход которого при использовании в качестве устройства внешней памяти накопителя на магнитной ленте соединен с управляющим входом блока сопряжения с ЭВМ, что позволяет выполнять чтение при движении ленты назад. Группа информационно-управляющих входов и выходов блока сопряжения с ЭВМ является группой входов-выходов устройства для подключения к ЭВМ. Группа информационно-/прзвляющих входов и выходов блока сопряжения с памятью является (руппой входов-выходов для подключения к внешней памяти. Благодаря введению внутренней оперативной памяти буферной памяти данных, двух внутренних шин {мультиплексора и демультиплексора), дешифратора управления шинами и связей между блоками устройства увеличивается скорость обмена информацией между ЭВМ и УВП за счет увеличения скорости передачи данных через интерфейс УВП и обеспечения потокового режима работы УВП, организации обмена информацией между ЭВМ и устройством по прямому доступу, а для накопителей на магнитной ленте еще и за счет обеспечения чтения информации при движении ленты назад 1714613 На фиг.1 представлена блок-схема предлагаемого устройства; на фиг.2 - блок микропрограммного управления; на фиг.З структура микрокоманды; на фиг.4 - арифметико-логический блок; на фиг.5 - дешиф- 5 ратор управления шинами; на фиг.6 внутренняя оперативная память; на фиг.7 и 8 буферная память данных; на фиг.9 - блок-схема блока сопряжения с ЭВМ; на фиг.10-12 электрическая схема блока сопряжения с 10 ЭВМ (БСЭВМ); на фиг.13 - временная диаграмма чтения по прямому доступу; на фиг,14 - временная диаграмма записи по прямому доступу; на фиг. 15 - временная диаграмма чтения регистров устройства; на 15 фиг.16 - временная диаграмма передачи вектора прерывания устройством; на фиг. 17 временная диаграмма записи в регистры устройства; на фиг.18-20 - блок сопряжения с памятью; из фиг.21-24 - блок-схема 20 алгоритма работы устройства. ния соединен с синхровходом внутренней оперативной памяти 7, второй выход - с вторым управляющим входом блока сопряжения с памятью. Адресными входами блока 5 микропрограммного управления является пятая группа выходов демультиплексора 4. Группа информационных входов арифметико-логического блока 3 соединена с выходов мультиплексора 2, группа выходов - с группой информационных входов демультиплексора 4, управляющий вход - с управляющим выходом блока 1 сопряжения с ЭВМ и управляющий выход- с входом логического условия блока 5 микропрограммного управления. Первая, вторая и третья группы выходов дешифратора 6 управления шинами соединены соответственно с группой режимных входов внутренней оперативной памяти 7, группами управляющих входов мультиплексора 2 и демультиплексора 4. Группы инфорУстройство для обмена информацией мационных выходов, входов и адресные между ЭВМ и внешней памятью (фиг.1) совходы внутренней оперативной памяти 7 содержит блок 1 сопряжения с ЭВМ (БСЭВМ) для осуществления связи устройства с 25 единены соответственно с шестой группой информационных входов мультиплексора 2, ЭВМ, реализующий требования интерфейчетвертой и шестой группами выходов деса ЭВМ, мультиплексор 2, на который постумультиплексора 4. пает информация под управлением микропрограммы, арифметико-логический Буферная память 8 данных соединена с блок 3, осуществляющий обработку инфор- 30 другими блоками устройства следующим мации и передачу ее в демультиплексор 4, образом. Группы информационных выходов информация с которого под управлением соединены: первая - с второй группой инмикропрограммы поступает в блоки сопряформационных входов мультиплексора 2, жения с ЭВМ и памятью и другие узлы уствторая - с первой информационной группой ройства, блок 5 микропрограммного 35 входов блока 9 сопряжения с памятью. управления, дешифратор 6 управления шиГруппы информационных входов соединенами, внутреннюю оперативную память 7, ны; первая - с первой группой выходов дебуферную память 8 данных, блок 9 сопряжемультиплексора 4, вторая - с первой ния с памятью (БСУВП), осуществляющий информационной группой выходов блока 9 связь устройства с УВП и реализующий тре- 40, сопряжения с памятью. Группы управляюбования интерфейса УВП. щих входов соединены: первая - с четвертой группой выходов дешифратора 6 Блок 1 имеет входы и выходы для подуправления шинами, вторая - с группой упключения к интерфейсу ЭВМ, информациравляющих выходов блока 9 сопряжения с онные выходы соединены с пятой группой информационных входов мультиплексора 2, 45 памятью. Управляющий выход соединен с управляющим входом блока 9 сопряжения с а информационные входы - с третьей группамятью, группа выходов состояния - с пой выходов демультиплексора А. третьей группой информационных входов Группы выходов блока 5 микропрограммультиплексора 2. много управления соединены следующим образом: первая - с группой стробирующих 50 входов блока 1 сопряжения с ЭВМ, вторая Блок 9 сопряжения с памятью имеет с группой входов адреса арифметико-логивходы и выходы для подключения к интерческого блока 3, третья - с группой входов фейсу устройства внешней памяти. Вторая инструкций арифметико-логического блока группа информационных выходов блока 9 3, четвертая - с группой входов режима 55 сопряжения с памятью соединена с четверарифметико-логического блока 3, пятая - с той группой информационных входов мультигруппой входов дешифратора 6 управления плексора 2, а группа управляющих входов - с шинами, шестая - с первым информационвторой группой выходов демультиплекссра ным входом мультиплексора 2, Первый 4. Для обеспечения выполнения чтения инвыход блока 5 микропрограммного управлеформации при движении ленты назад уп 1714613 8 памяти, схему 45 контроля четности, регистры 46 и 47, триггеры 48 и 49, регистр 50, элемент НЕ 51, элемент И-НЕ 52, элементы НЕ 53...58, триггеры 59-63 элементы И-НЕ 64 и 65, элемент ИЛИ-НЕ 66, элемент 67 управления памятью, формирователи 68, и 69, резисторы, конденсаторы. Входы данных элементов 43 и 61 являются первой группой, а входы данных элементов 41 и 42 - второй группой информационных входов. Тристабильные выходы элемента 50 являются первой группой информационных выходов, а тристабильные выходы элементов 47,68 и 69 группой выходов состояния. Выходы элементов 46 и 49 являются второй группой информационных выходов, входы элементов 36,37,51 и 54 - второй группой управляющих входов, а выход элемента 67 управляющим выходом блока 8. Выходы 70 соответствуют разрядам 0...55 микрокоманды и используются для управления работой устройства полями, представленными на фиг.З. Выход 71 является резервным. "0" на выходе 71 дешифратора 17 соответствует нулевому значению разряд дов 52...54 микрокоманды. Сигналы на выхоАрифметико-логический блок 3 (фиг.4) содержит элементы И-НЕ 10 и 19, элемент дах 72. .78 дешифратора 17 используются ИЛИ-НЕ 20, микропроцессорную секцию 21 как стробы управления для выдачи в блоки обработки информации, мультиплексор 22, 30 1 и 9 сопряжения и внутреннюю оперативэлемент НЕ 23, элемент И-НЕ 24, регистр ную память 7 устройства. • ; 25, мультиплексор 26, Входы адресов внутренних регистров элемента 21 являются Выходы 72...74,77 элемента 17 являются группой входов адреса, входы инструкций первой группой выходов, выход 78 элемента элемента 21 являются группой входов и нет- 35 17 - первым выходом блока 5 микропрогрукций блока 3, входы элементов 22,18,24 и раммного управления, выходы 75 и 76 - вто26 являются группой входов режима, входы рым выходом блока 5. данных элемента 21 являются группой инНа фиг.4,5 и 8 обозначены также выход формационных входов, а тристабильные вы79 арифметико-логического блока 3, выходы ходы элемента 21 являются группой 40 80...111 дешифратора 6 управления шинавыходов блока 3. ми, 112..,114 блокз 8 буферной памяти данных. Дешифратор 6 управления шинами (фиг.5) содержит дешифраторы 27. .30 ИнВыходы 94 и 95 элемента 28 являются формационные и управляющие входы элепервой группой выходов, а выход 86 элеменментов 27...30 образуют группу входов, а 45 та 27 и выход 100 элемента 29 - четвертой выходы -четыре группы выходов дешифрагруппой выходов блокз 6. Управляющие вхотора 6. ды элементов 31 и 32 являются группой режимных входов памяти 7. Входы 86 и 100, Внутренняя оперативная' память 7 поступающие на элементы 52 и 60, являются (фиг.6) включает счетчик 31, элемент 32 памяти, формирователи 33 и 34 соответствен- 50 первой группой управляющих входов блока 8. но входных и выходных данных. Входы Блок 1 (фиг.9) состоит из приемопереданных элемента 33 являются информацидатчиков 115 данных/адреса, схемы 116 упонными входами, входы данных элемента 3 1 равления обменом, приемопередатчиков адресными входами блокз 7, тристабильные 117 сигналов управления, регистров 118 выходы элемента 34 - информационными 55 входных данных и адреса, дешифратора 119 выходами блока 7. адреса, регистра 120 выходных данных, схемы 121 запроса прерывания, схемы 122 адБуферная памчть 8 данных (фиг.7 и 8) реса вектора прерывания, расширения включает элемент ИЛИ-НЕ 35, элементы НЕ адреса, регистра состояния, схемы 123 фор36 и 37» элементы И-НЕ 38 и 39, элемент НЕ мирования адреса. 40, триггер 41, регистру 42 и 43, элемент 44 равляющий выход блока 9 соединен с управляющим входом блока 1 сопряжения с ЭВМ. Блок 5 микропрограммного управления включает элемент 10 управления последовательностью микрокоманд, управляющий 5 вход которого является входом логического условия блока 5, регистр 11, задающий адрес на входе элемента 10 при "0" на управляющем входе. Входы элемента 11 являются адресными входами блока 5, эле- 10 менты 12 и ІЗ памяти, элемент НЕ 14, элементы 15 и 16 памяти, дешифратор 17, выходы элемента 12, соответствующие разрядам 0...7 микрокоманды, являются второй группой выходов. Выходы элемента 12, со- 15 ответствующие разрядам 10...15,17...19 микрокоманды, являются третьей группой выходов. Выходы элементов 12 и 15, соответствующие разрядам 0...2,8,9,16.33 ..35 микрокоманды, являются четвертой груп- 20 пой выходов. Выходы элемента 12, соответствующие разрядам 20...23,48...51 микрокоманды, являются пятой, а выходы элемента 13, соответствующие разрядам 24.. 31 микрокоманды, являются шестой 25 группами выходов блока 5. 1714613 включает также триггер Шмиттз 309 и перемычки. Входы и выходы блока 9 сгруппированы следующим образом. Выходы элементов 291...294,296...299 и 309 являются первой группой информационных выходов, выходы элементов 243. 244 и 265 второй группой информационных выходов, входы элементов 271...279- первой группой информационных входов, входы данных элементов250и270-группойуправляющих входов, вход элемента 280 - управляющим входом, выходы элементов 268 и 295, выход элемента 250, соединенный с входом элемента 254, являются группой управляющих выходов, выход элемента 250, соединенный с входам элемента 258 - управляющим выходом, входы элементов 227...232,244,247...249,291...299 и 309 - входами, выходы элементов 254...261,271 .,284.286...289 - группами информационно-управляющих входов и выходов блока сопряжения с памятью Мультиплексор 2 (фиг 1) имеет формат 8 бит и реализуется на элементах с тремя состояниями - регистрах 47,50.128,129,149 и 197, формирователях 34,68,69,163,176,243,244 и 265 и элементе 13 памяти. Демультнплексор 4 (фиг.1) имеет формат 8 бит, реализуется на регистрах 11,43,130,131,133...135,250 и 270, счетчиках 31 и/132, формирователе 33 и триггерах 61 и 140. ' Управление работой мультиплексора 2 и демультиплексора 4 осуществляется сигналами соответственно второй и третьей групп выходов дешифратора 6 управления шинами, Устройство работает следующим обра40. зом. Синхронизация работы схем осуществляется сигналом "Синх". Длительность периода прямоугольных тактовых импульсов "Синх" составляет 167 не. Выбор частоты 45 обусловлен заданной максимальной скоростью передачи данных по интерфейсу УВП и должен быть обеспечен кварцевым генератором на 12000 к! ц. В исходное состояние элементы схем устанавливаются сигналом 50 "Нач.уст" по включению питания устройства или сигналу сброса от интерфейса ЭВМ, Константа "1" на входах элементов устройства обозначена "С" и представляет собой постоянный электрический уровень, соот55 вегствующий логической единице, входы могут быть подключены к "плюсу" источника 5 питания через резистор, сопротивление которого не менее 1 кОм. Обмен данными осуществляется подуп_оявлением микропрограммы. Наличие внут Узлы блока 1 содержат приемопередатчики 124...127, регистры 128...131, счетчик 132, регистры 133...135, элемент НЕ 136, передатчики 137,..139, триггер 140, передатчики 141...143, формирователь 144, при- 5 емник 145, триггер 146, приемопередатчик 147, многофункциональную цифровую программируемую схему 148, регистр 149, элементы И-НЕ 150 и 151, рззисторную сборку 152, элементы И-НЕ 153 и 154, триггер 155, 10 элемент ИЛИ-НЕ 156, триггер 157, приемник 158, элемент НЕ 159, элемент ИЛИ-НЕ 160, триггер 161, элемент НЕ 162, формирователь 163, триггеры 164 и 165, регистр 166, элемент И-НЕ 167, передатчик 168, прием- [5 ники 169 и 170, передатчик 171, триггер 172, передатчики 173 и 174, элемент НЕ 175, формирователь 176, триггер 177, триггер 178, приемопередатчики 179, элемент И-НЕ 180, триггеры 181 и 182, элементы НЕ 183 и 184, элемент ИЛИ-НЕ 185, элемент НЕ 186. 20 линию задержки 187. элемент И-НЕ 188, мультиплексор 189,триггер 190, многофункциональную цифровую программируемую схему 191, приемник 192, триггеры 193 и 194, передатчик 195, элемент И-НЕ 196, ре- 25 гистр 197, элемент НЕ 198, резисторную сборку 199, резисторы, конденсатор, перемычки. Входы и выходы приемопередатчиков 115 и 117 и схемы 121 являются входами и выходами для связи блока 1 сопряжения с 30 ЭВМ. Входы регистра 120 и схемы 123 являются группой информационных входов, а выходы регистров 118и схемы 122-группой информационных выходов блока 1. Входы схем 116 и 121 являются стробирующими 35 входами блока 1, а вход схемы 123 - управляющим входом блока 1. На фиг. 10-12 обозначены также группа выходов 200, выходы 201...226 блока 1, выходы 208 и 209 схемы 166, являющиеся управляющим выходом блока 1. Блок 9 включает триггеры Шмитта 227...232, элемент И-НЕ 233, элементы НЕ 234...236, элемент ИЛИ-НЕ 237, элемент НЕ 238, триггеры 239-241, элемент ИЛИ-НЕ 242, шинный формирователь 243 с тремя состояниями, усилитель 244 с тремя состояниями и инверсией, триггер Шмитта 245, элемент НЕ 246, триггеры Шмиттз 247...249, регистр 250, элементы ИЛИ-НЕ 251. .253, элементы НЕ 254...261, элемент И-НЕ 262, элемент ИЛИ-НЕ 263, элемент НЕ 264, шинный формирователь 265, элементы И-НЕ 266 и 267, элемент НЕ 268, триггер 269, регистр 270, элементы НЕ 271...289, набор резисторов 290 и триггеры Шмитта 291...299. На фиг,18-20 обозначены также связи 300...308 между элементами блока 9. Блок 9 10 11 1714613 12 Информация о состоянии и данные из УВП через блок 9 поступают на мультиплексор 2 и в буферную память 8 данных также под управлением микропрограммы, обрабатываются в арифметико-логическом блоке 3 и передаются на демультиплексор 4. Информация для передачи в ЭВМ поступает в блок 1 БСЭВМ с демультиплексора 4 устройства. Управляющая информация для передачи в УВП поступает в блок 9 БСУВП с демультиплексора 4, данные для передачи в УВП поступают в блок 9 БСУВП буферной памяти 8 данных. Объем внутренней оперативной памяти (256 8-разрядных слов) достаточен для подключения через блок 9 БСУВП до четырех УВП, операция обмена данными на каждом УВП может быть выполнена после завершения операции обмена на предыдущем УВП. Внутренняя оперативная память, содержащая пакет команд, буфер прямого доступа для каждого из УВП, подключенного к устройству через блок 9 сопряжения с памятью, программно-доступные регистры, пакет характеристик, пакет состояний и информации о состоянии каждого УВП, характер которой обусловлен типом УВП, распределения внутренней оперативной Пакет сообщений формируется во пнутпамяти для обеспечения работы четырех ренней оперативной памяти 7 устройства, содержит информацию о завершении опе- 30 УВП представлены в таблице. рации в устройстве и состоянии устройства и выдается в ЭВМ по окончанию каждой На фиг.21-24 представлен алгоритм раоперации, заданной ЭВМ. боты устройства. Алгоритм реализован в блоке 5 микропрограммного управления. На каждое из подключаемых через интерфейс устройств внешней памяти до- 35 статочно двух программно-доступных региФормула изобретения стров, хранящихся также во внутренней Устройство для обмена информацией оперативной памяти 7, - регистра состоямежду ЭВМ и внешней памятью, содержания и регистра адреса данных. щее блок микропрограммного управления, 40 арифметико-логический блок, блок сопряМикропрограмма обнаруживает ображения с ЭВМ и блок сопряжения с памятью, щение ЭВМ к программно-доступным регигруппа информационно-управляющих вхострам (элемент 26, фиг.4) и отрабатывает дов и выходов блока сопряжения с ЭВМ его. Прочитав регистр состояния и опредеявляется группой входов-выходов устройстлив, что устройство готово к выполнению команды, ЭВМ сообщает начальный адрес 45 ва для подключения к ЭВМ, группа инфорпакета команды. Вся дальнейшая передача мационно-управляющих входов и выходов информации между устройством и ЭВМ осублока сопряжения с памятью - группой вхоществляется по прямому доступу под управдов-выходов для подключения к внешней лением микропрограммы устройства памяти, первая группа выходов блока микОперации обмена данными с УВП выполня- 50 ропроіраммного управления соединена с ются до исчерпания счетчика данных, загруппой стробирующих входов блока сопряданного ЭВМ, или до обнаружения жения с ЭВМ, управляющий выход которого признака конца данных в УВП соединен с управляющим входом арифметико-логического блока, управляющий выВся поступающая от ЭВМ информация через блок 1 БСЭВМ поступает на мульти- 55 ход которого соединен с входом логического плексор 2 устройства, затем под управусловия блока микропрограммного управлелением микропрограммы через ния, о т л и ч а ю щ е е с я тем, что, с целью арифметико-логический блок 3 и демультипповышения скорости обмена информацией, лексор 4 - so внутреннюю оперативную пав устройство введены дешифратор управлемять 7 или буферную память 8 данных. ния шинами, внутренняя оперативная пэ ренней оперативной памяти 7 и буферной памяти 8 данных позволяет осуществлять обмен данными и управляющей информацией с ЭВМ по прямому доступу, сводя к минимуму количество программно-доступ- 5 ных адресуемых регистров по интерфейсу ЭВМ и время обмена на интерфейсе ЭВМ. Обмен информацией по прямому доступу производится пакетами, хранящимися во внутренней оперативной памяти 7 и буфер- 10 ной памяти 8 данных. Пакеты подразделяются на пакеты управления (пакет команды, пакет характеристик, пакет сообщения) и пакеты данных, предназначенные для передачи вУПВ и из УВП. Пакет команды форми- 15 руется в памяти ЭВМ и содержит информацию о типе команды, начальном адресе пакета данных в памяти ЭВМ или начальном адресе пакета характеристик в памяти ЭВМ, количестве байтов в пакете 20 данных (счетчик данных). Пакет характеристик также формируется в оперативной памяти ЭВМ и содержит начальный адрес пакета сообщений в памяти ЭВМ, длину пакета сообщений и некоторые служебные символы, касающиеся режима выполнения 25 данной команды. 13 1714613 мять, мультиплексор, демультиплексор и буферная память данных, вторзя-шестая группы выходов блока микропрограммного управления соединены соответственно с группами входов адреса, инструкций, режи- 5 ма арифметико-логического блока, группой входов дешифратора управления шинами и первым информационным входом мультиплексора, выход которого соединен с группой информационных входов 10 арифметико-логического блока, первый выход блока микропрограммного управления соединен с синхровходом внутренней оперативной памяти, группа режимных входов которой соединена с первой группой выхо- 15 дов дешифратора управления шинами, вторая и третья группы выходов которого соединены с группами управляющих входов соответственно мультиплексора и демультиплексора, группа выходов арифметико- 20 логического блока соединена с группой информационных входов демультиплексора, четвертая группа выходов дешифратора управпения шинами - с первой группой управляющих входов буферной памяти дан- 25 ных, первая группа информационных входов, первая группа информационных выходов и группа выходов состояния которой соединены соответственно с первой группой выходов демультиплексора, второй и 30 третьей группами информационных входов Номер масива 1 2 3 4 5 * 6 7 14 мультиплексора, вторые группы информационных входов и выходов, вторая группа управляющих входов и управляющий выход буферной памяти данных соединены соответственно с первыми информационными группами входов и выходов, группой управляющих выходов и управляющим входом блока сопряжения с памятью, группа управляющих входов и вторая группа информационных выходов которого соединены соответственно с второй группой выходов демультиплексора и четвертой группой информационных входов мультиплексора, пятая и шестая группы информационных входов которого соединены соответственно с группами информационных выходов блока сопряжения с ЭВМ и внутренней оперативной памяти, группы информационных входов которых соединены соответственно с третьей и четвертой группами выходов демультиплексора, пятая и шестая группы выходов которого соединены соответственно с адресными входами блока микропрограммного управления и внутренней оперативной памяти, управляющий выход блока сопряжения с памятью соединен с управляющим входом олока сопряжения с ЭВМ, второй выход блока микропрограммного управления - с вторым управляющим входом блока сопряжения с памятью. Информация Пакет команд Буфер прямого доступа Пакет характеристик при обращении к УВП 1 Пакет сообщения Состояние УВП 1 Пакет характеристик при обращении к УВП 2 Пакет сообщений при работе УВП 2 Состояние УВП 2 Пакет характеристик при обращении к УВП 3 Пакет сообщений при работе УВПЗ Состояние УВП 3 Пакет характеристик при обращении к УВП 4 Пакет сообщений при работе УВП 4 Состояние УВП 4 Программно-доступные регистры УВП 1. 4 Емкость, байт 8 8 ta is 4 10 16 4 to 16 4 10 16 4 16 1714613 Продолжение таблицы Номер масива 8 9 Информация Вспомогательные программно-доступные регистры УВП 1 А Счетчик простоя ФигЛ Емкость байт 4 8 Группа оыходоб г 4 Назначение Разряд 231 ИНС Приемник шины 4 , х у 3 16 **. Г7 . . Группа выходов / Вход ААУ ЗУ Инструкция ААУ ААУ 20 19 г J . А1 Шина 4 АО 7 >10 1 ! I Инструнция УСА. АМК 8етд* АМК LQ... 77 Разряд і і і Группа выходов 1 1 II Назначение А Строб C9J упр. Источник шины 1 Разряд 55 51\ х 4S t 39Х к% Фиг:3 J 2 А Константа ши/лі сю зг "і хзз ,ХЗВ Ч , ,° J 3 Назначение 1 ^ • і і її 2 1 х& 1714613 to „л 04 C>*-- Счї 4j 1714613 Фиг 6 1714613 1714613 1714613 Фиг 9 ФигЮ 1714613 гю Фиг 11 210 фиг 11 1714613 1714613 m 150.1 № W5.2 ОТВ 218 1915 Фиг. 15 72 •ЗПР5 тт ПРРі) 226 165.2 7¥ ore Z!8 law 1714613 89 пзп дзп т. ФигП -НКОРОШ ' -£ ФигШ Г Hi Ч свс 87 Ш Г 271 шзса гш шз~к -W3-0 275 277 •29В •-ШВ-1 -ШЗ-3. Ш8С0..\ шь-ц -ШЗ-5 113 275' -W5~0 .-Ш8-1 > шъ-Т ,-шв-$ .'ШВ-6 •4--шв-7 ,-исз . - шв-к Фиг 20 V+S 294

ДивитисяДодаткова інформація

МПК / Мітки

МПК: G06F 13/16

Мітки: інформацією, еом, пам'яттю, пристрій, зовнішньою, обміну

Код посилання

<a href="https://ua.patents.su/22-322-pristrijj-dlya-obminu-informaciehyu-mizh-eom-i-zovnishnoyu-pamyattyu.html" target="_blank" rel="follow" title="База патентів України">Пристрій для обміну інформацією між еом і зовнішньою пам’яттю</a>

Попередній патент: Система автоматичного регулювання двигуна внутрішнього згоряння

Наступний патент: Пристрій для узгодження системних магістралей

Випадковий патент: Лічильник обліку витрати рідини