Пристрій для контролю імпульсів перешкоди електричного сигналу

Номер патенту: 18442

Опубліковано: 25.12.1997

Автори: Дороніна Ольга Михайлівна, Ванько Володимир Михайлович, Лавров Геннадій Миколайович

Формула / Реферат

Устройство для контроля импульсов помехи электрического сигнала, содержащее аналого-цифровой преобразователь, первый и второй регистры, вычитатель, первый и второй элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, первый и второй D-триггеры и элемент И, причем шина входного сигнала подключена к информационному входу аналого-цифрового преобразователя, выходы которого соединены с информационнымивходами второго регистра, выходы последнего подключены ко вторым входам вычитателя, выход знака которого соединен с первым входом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, прямой выход первого D-триггера подключен к C-входу второго D-триггера, а выходы первого регистра являются первыми выходами устройства, отличающееся тем, что в него введены переключатель кодов, третий и четвертый регистры, блок памяти, генератор опорной частоты, дешифратор, счетчик и элемент ИЛИ-НЕ, причем выходы аналого-цифрового преобразователя подключены к первым входам переключателя кодов, вторые входы которого соединены с выходами третьего регистра, а выходы - с первыми входами вычитателя, выходы второго регистра подключены к информационным входам первого регистра и выходам блока памяти, адресный вход которого соединен с прямым выходом второго D-триггера и вторым входом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, вход управления записью первого регистра подключен к выходу элемента И, первый вход которого соединен с выходом генератора опорной частоты, C-входом первого D-триггера и первым входом элемента ИЛИ-НЕ, а второй вход-с прямым выходом первого D-триггера, входом счетчика, входами управления записью второго и третьего регистров, тактовым входом аналого-цифрового преобразователя и входом разрешения выбора блока памяти, инверсный выход первого D-триггера подключен к его D-входу, входу разрешения выбора второго регистра, входу управления переключателем кодов и первому входу второго элемента. ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен с первым выходом дешифратора и входом установки в "ноль" счетчика, а выход - со вторым входом элемента ИЛИ-НЕ, выходы вычитателя подключены к информационным входам третьего регистра, а выход знака - также к D-входу второго D-триггера, вход управления записью четвертого регистра соединен с выходом элемента ИЛИ-НЕ, первый информационный вход - с выходом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй информационный вход - с первым выходом четвертого регистра и первым входом дешифратора, вход установки в "единицу" - с шиной ПУСК, а второй выход - со вторым входом дешифратора, выходы счетчика являются вторыми выходами устройства, а выходы дешифратора - его третьими выходами.

Текст

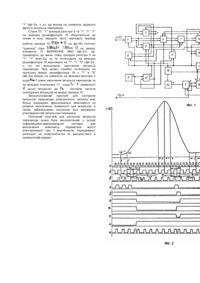

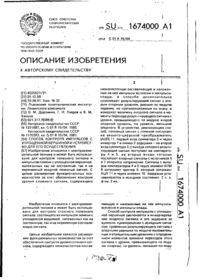

Винахід відноситься до галузі електровимірювальної техніки і може бути використаний у інформаційно-вимірювальних системах для аналізу імпульсної перешкоди в електричних сигналах. Найбільш близьким за технічною суттю до запропонованого винаходу є пристрій для визначення імпульсів перешкоди електричного сигналу, який містить аналого-цифровий перетворювач, регістри, елементи ВИКЛЮЧНЕ АБО, віднімач, елементи І, D-тригери, формувачі імпульсів, елемент АБО [2]. Відомий пристрій працює за принципом знаходження екстремумів електричного сигналу та вимірювання їх рівнів. У даному випадку не виконується виділення імпульсів перешкоди із загального числа екстремумів вхідного сигналу та не визначаються тривалості цих імпульсів. Таким чином, недоліком відомого пристрою є обмежені функціональні можливості при роботі з електричними сигналами, у складі яких містяться імпульсні перешкоди. В основу винаходу поставлене завдання розширення функціональних можливостей запропонованого пристрою за рахунок забезпечення вимірювання тривалості імпульса перешкоди. Це завдання розв'язується завдяки тому, що в пристрої для контролю імпульсів перешкоди електричного сигналу, який містить аналогоцифровий перетворювач, перший та другий регістри, віднімач, перший і другий елементи ВИКЛЮЧНЕ АБО, перший і другий D-тригери та елемент І, причому шина вхідного сигналу підключена до інформаційного входу аналогоцифрового перетворювача, виходи якого з'єднані з інформаційними входами другого регістра, виходи останнього підключено до других входів віднімача, вихід знаку якого з'єднаний з першим входом першого елемента ВИКЛЮЧНЕ АБО, прямий вихід першого D-тригера підключено до C-входу др угого D-тригера, а виходи першого регістра є першими виходами пристрою, згідно з винаходом перемикач кодів, третій і четвертий регістри, блок пам'яті, генератор опорної частоти, деши фратор, лічильник та елемент АБО-НІ, причому виходи аналого-цифрового перетворювача підключені до перших входів перемикача кодів, другі входи якого з'єднано з виходами третього регістра, а виходи - з першими входами віднімача, виходи другого регістра підключені до інформаційних входів першого регістра та виходів блока пам'яті, адресний вхід якого з'єднано з прямим виходом другого D-тригера і другим входом першого елемента ВИКЛЮЧНЕ АБО, вхід керування записом першого регістра підключено до виходу елемента І, перший вхід якого з'єднано з виходом генератора опорної частоти, C-входом першого Dтригера і першим входом елемента АБО-НІ, а другий вхід - з прямим виходом першого Dтригера, входом лічильника, входами керування записом другого і третього регістрів, тактовим входом аналого-цифрового перетворювача і входом дозволу виборки блока сталої пам'яті, інверсний вихід першого D-триггера підключений до його D-входу, входу дозволу виборки другого регістра, входу керування перемикачем кодів і першого входу др угого елемента ВИКЛЮЧНЕ АБО, другий вхід якого з'єднаний з першим виходом дешифратора і входом встановлення в "нуль" лічильника, а вихід - з другим входом елемента АБО-НІ, виходи віднімача підключені до інформаційних входів третього регістра, а вихід знака - також до D-входу др угого D-тригера, вхід керування записом четвертого регістра з'єднано з виходом елемента АБО-НІ, перший інформаційний вхід - з ви ходом першого елемента ВИКЛЮЧНЕ АБО, другий інформаційний вхід - з першим виходом четвертого регістра і першим входом дешифратора, вхід встановлення в "одиницю" - з шиною ПУСК, а другий вихід - з другим входом дешифратора, виходи лічильника є другими виходами пристрою, а виходи дешифратора - його третіми виходами. Відомі пристрої для контролю та регістрації перешкод працюють по принципу виявлення імпульсів перешкод за перевищенням ними апріорі визначеного рівня, котрий з метою уникнення збоїв у роботі повинен бути ви ще максимально можливого рівня корисного сигналу (напр., максимально можливої амплітуди синусоподібного сигналу) промислової електромережі. Таким чином, відомими пристроями не фіксується інформація про наявність імпульсів перешкоди нижче контрольного рівня, наприклад не надаються дані про імпульсні спади до нуля або імпульси, накладені на низькі рівні корисного сигналу. Отже, має місце звуження діапазону досліджуваних імпульсних перешкод в електричному сигналі. Запропонований винахід дозволяє розширити функціональні можливості контролю та регістрації імпульсних перешкод за рахунок вимірювання їх тривалості та забезпечення автоматичного відслідкування всього діапазону таких перешкод. Елемент АБО-НЕ реалізований на 1533ЛЕІ (6К0.347.364 - 04 ТУ). На фіг.1 зображена схема запропонованого пристрою для контролю імпульсів перешкоди електричного сигналу; на фіг.2 - часові діаграми, які пояснюють його роботу. Пристрій (фіг.1) містить аналого-цифровий перетворювач 1, регістри 2 - 5, перемикач 6 кодів, віднімай 7, блок 8 пам'яті, генератор 9 опорної частоти, D-тригери 10, 11, елементи 12, 13 ВИКЛЮЧНЕ АБО, елемент 14 АБО-НІ, елемент 15 І, дешифратор 16 і лічильник 17. Шина вхідного сигналу підключена до інформаційного входу аналого-цифрового перетворювача 1, виходи якого з'єднані з інформаційними входами регістра 3 та першими входами перемикача 6 кодів. Другі входи перемикача 6 кодів підключені до виходів регістра 4, а виходи - до перших входів віднімача 7. Виходи регістра 3 з'єднано з інформаційними входами регістра 2, виходами блока 8 сталої пам'яті і другими входами віднімача 7, виходи якого підключені до інформаційних входів регістра 4, а вихід знака - також до D-входу D-тригера 11 і другого входу елемента 13 ВИКЛЮЧНЕ АБО. Адресний вхід блока 8 пам'яті з'єднано з прямим виходом D-тригера 11 і першим входом елемента 13 ВИКЛЮЧНЕ АБО. Вхід керування записом регістра 2 підключено до виходу елемента 15 І, перший вхід якого з'єднано з виходом генератора 9 опорної частоти, C-входом D-тригера 10 і першим входом елемента 14 АБО-НІ, а другий вхід - з прямим виходом D-тригера 10, входом лічильника 17, входами керування записом регістрів 3 і 4, тактовим входом аналого-цифрового перетворювача 1, входом дозволу виборки блока 8 пам'яті і С-входом D-тригера 11. Інверсний вихід Dтригера 10 підключений до D-входу цього тригера, входу дозволу виборки регістра 3, входу керування перемикача 6 кодів і першого входу елемента 12 ВИКЛЮЧНЕ АБО, др угий вхід якого з'єднано з першим виходом дешифратора 16 і входом встановлення в "нуль" лічильника 17, а вихід - з другим входом елемента 14 АБО-НІ. Вхід керування записом регістра 5 підключений до виходу елемента 14 АБО-НІ, перший інформаційний вхід - до виходу елемента 13 ВИКЛЮЧНЕ АБО, др угий інфоромаційний вхід - до першого виходу регістра 5 і першого входу дешифратора 16, вхід встановлення в "одиницю" до шини ПУСК, а другий вихід - до др угого входу дешифратора 16. Виходи регістра 2, лічильника 17 і дешифратора 16 є, відповідно, першими, другими і третіми виходами пристрою. Пристрій для контролю імпульсів перешкоди електричного сигналу працює наступним чином. Вхідний сигнал (фіг.2) надходить на вхід аналого-цифрового перетворювача 1 (фіг.1), який керується імпульсною послідовністю з прямого виходу D-тригера 10, котрий ділить на два частоту повторення імпульсів з виходу генератора 9 (фіг.2а,б). Черговий період роботи D-тригера 10 можна розділити на два такти і (фіг.2б). На протязі перетворювач 1 здійснює виборку і перетворення в цифровий код значення вхідного сигналу в миттєвого точці його дискретизації. На протязі результат перетворення встановлюється на виході перетворювача 1 та підключається перемикачем 6 на перші входи віднімача 7. В останньому відбувається віднімання від значення коду миттєвого вхідного сигналу в попередній точці його дискретизації. Результат віднімання в кінці від'ємним фронтом сигналу з прямого виходу тригера 10 (фіг.2б) заноситься в регістр 4, а його знак, в додатку до цього, запам'ятовується тригером 11. Крім того, на протязі від'ємним фронтом сигналу з виходу елемента 15 І (фіг.2в) код який зберігається в регістрі 3, заноситься в регістр 2, а в кінці від'ємним фронтом сигналу з прямого виходу тригера 10 (фіг.2б) код цифрового перетворювача регістр 3. На протязі першого такту періоду з виходу аналого1 переноситься в наступного (фіг.2б) роботи тригера 10 віднімач 7 здійснює віднімання від опорного коду або з виходів блока 8 пам'яті, відповідно, у випадку додатнього або від'ємного знаку який визначає адресу читання інформації з блока 8. При цьому, коли знаки та результату віднімання рівні то на виході елемента 13 ВИКЛЮЧНЕ АБО з'являється нульовий потенціал, а коли знаки нерівні - рівень логічної "одиниці" (фіг.2г). Тригери дворозрядного регістра 5 сигналом "Пуск" встановлюються в стан "1", "1" (фіг.2д,е). Внаслідок цього, на першому, другому та третьому виходах деши фратора 16 з'являються потенціали, відповідно, "1", "1", "0" (фіг.2ж, з, й), що вказує на відсутність імпульсів перешкоди. "Одиничний" потенціал на першому ви ходу дешифратора 16 сприяє формуванню на виході елемента 14 АБО-НЕ імпульсів керування записом в регістр 5 в кінці першого такту кожного поточного періоду роботи тригера 10 (фіг.2к). Таким чином, при "одиничному" потенціалі в кінці на виході елемента 13 ВИКЛЮЧНЕ АБО тригери регістра 5 залишаються в початковому стані "1", "1", а у випадку нульового потенціалу - з від'ємним фронтом чергового імпульса з виходу елемента 14 АБО-НЕ (фіг.2к) переходять в стан "0", "0" (фіг.2д,е). Це змінює потенціали на виходах дешифратора 16 відповідно на "0", "1", "1" (фіг.2ж, з, й), що вказує на виникнення імпульса перешкоди в контрольованому вхідному сигналі. Дійсно, швидкість зміни рівня по фронту в імпульса перешкоди завжди більша від швидкості зміни рівня корисного сигналу. Тому код різниці між рівнем корисного сигналу в точці дискретизації яка знаходиться перед імпульсом перешкоди, та рівнем власне цього імпульса в першій точці його дискретизації буде за абсолютним значенням більше деякого значення яке є за абсолютним значенням більшим, ніж максимальна різниця між рівнями корисного сигналу в двох сусідніх точках його дискретизації. Умові відповідає "нуль" на виході елемента 13 в кінці Зміна потенціалу з "1" в "0" на першому виході дешифратора 16 (мал.2ж) у випадку виникнення імпульса перешкоди приводить до скидання в "нуль" лічильника 17, після чого останній починає формувати код тривалості імпульса перешкоди та вказує на наявність на виходах регістра 2 кода рівня корисного сигналу, на якому виникає імпульс перешкоди. Нульовий потенціал на першому виході дешифратора 16 (фіг.2ж) сприяє формуванню на виході елемента 14 АБО-НІ імпульсів керування записом в регістр 5 в кінці другого такту кожного поточного періода роботи тригера 10 (фіг.2к). В другому такті чергового періода роботи тригера 10, напр. ТК (фіг.2б), елемент 13 ВИКЛЮЧНЕ АБО виконує порівняння коду знака різниці рівнів вхідного сигналу в і точках дискретизації, який формується на виході знака віднімача 7 в кінці з кодом знака різниці рівнів вхідного сигналу в і точках дискретизації, який зберігався в тригері 11. У випадку рівності кодів цих знаків на виході елемента 13 ВИКЛЮЧНЕ АБО, з'являється нульовий потенціал і стан тригерів регістра 5 залишається незмінним. При нерівності цих кодів, що свідчить про перехід виявленого імпульса через вершину, на виході елемента 13 з'являється логічна "одиниця", яка викликає зміну стану тригерів регістра 5 по задньому фронту чергового імпульса з виходу елемента 14 на "1", "0" (фіг.2д, е) і, відповідно зміну потенціалів на виходах дешифратора 16 на "1", "0", "1". Стрибок з "1" в "0" на другому виході дешифратора 16 вказує на наявність на виходах регістра 2 коду вершини імпульса перешкоди. Стан "1", "0" тригерів регістра 5 та стан "1", "0", "1" на виходах де шифратора 16 зберігається до появи в кінці першого такту чергового періода тригера 10 на мал.2б) нульового потенціала при на виході елемента 13 ВИКЛЮЧНЕ АБО (фіг.2г), що призводить до зміни стану тригерів регістра 5 на "0", "1" (фіг.2д, е) та потенціалів на виходах деши фратора 16 на "1", "1", "1" (фіг.2ж, з, и), що вказує на наявність заднього фронту імпульса перешкоди. Стани "0", "1" тригерів регістра 5 та "1", "1", "1" на виходах де шифратора 16 зберігаються до появи в кінці першого такту чергового періода роботи тригера 10 на фіг.2б) логічної "одиниці" (при на виході елемента 13 ВИКЛЮЧНЕ АБО (фіг.2г), що призводить до зміни стану тригерів регістра 5 на "1", "1" (мал.2д, е) та потенціалів на виходах дешифратора 16 відповідно на "1", "1", "0" (фіг.2ж, з, и), які визначають закінчення імпульса перешкоди. При цьому стрибок потенціалу на третьому виході дешифратора 16 з "1" в "0" (фіг.2и) вказує на наявність на виходах регістра 2 кода рівня закінчення імпульса перешкоди та на виходах лічильника 17 - кода тривалості цього імпульса, де - постійна частота повторення імпульсів на виході тригера 10. Запропонований пристрій для контролю імпульсів перешкоди електричного сигналу має більш розширені функціональні можливості за рахунок визначення тривалості цих імпульсів, а також забезпечення контролю всіх ймовірних різновидностей імпульсних перешкод. Описаний пристрій для контролю імпульсів перешкоди може бути використаний у складі інформаційно-вимірювальної системи для визначення комплексу параметрів якості електроенергії при її виробництві, передаванні, розподілі на енергооб'єктах та використанні в промисловій мережі.

ДивитисяДодаткова інформація

Назва патенту англійськоюAppliance for control of pulses of barrier for electric signal

Автори англійськоюDoronina Olha Mykhailivna, Lavrov Hennadii Mykolaiovych, Vanko Volodymyr Mykhailovych

Назва патенту російськоюУстройство для контроля импульсов преграды электрического сигнала

Автори російськоюДоронина Ольга Михайловна, Лавров Геннадий Николаевич, Ванько Владимир Михайлович

МПК / Мітки

МПК: G01R 19/04

Мітки: пристрій, перешкоди, імпульсів, сигналу, контролю, електричного

Код посилання

<a href="https://ua.patents.su/3-18442-pristrijj-dlya-kontrolyu-impulsiv-pereshkodi-elektrichnogo-signalu.html" target="_blank" rel="follow" title="База патентів України">Пристрій для контролю імпульсів перешкоди електричного сигналу</a>

Попередній патент: Фофоліпідні похідні та композиція, яка має антиоксидантну та інгібуючу активність щодо пероксидів ліпідів

Випадковий патент: Лампа підкапотна