Гібридний обчислювальний пристрій

Номер патенту: 33624

Опубліковано: 10.07.2008

Автори: Лукашенко Дмитро Андрійович, Караван Микола Анатолійович, Лукашенко Валентина Максимівна, Лукашенко Володимир Андрійович, Корпань Ярослав Васильович, Лукашенко Андрій Германович, Рудаков Костянтин Сергійович

Формула / Реферат

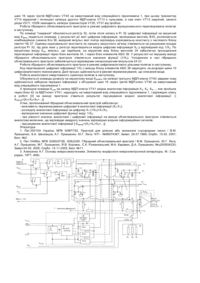

Гібридний обчислювальний пристрій цифро-аналогового помножувача, що містить операційний підсилювач, резисторну матрицю типу R-2R, резистор зворотного зв'язку, шини живлення, шину загального потенціалу, керуючу шину "скидання" пристрою, першу вхідну шину аналогової інформації Х1, другу вхідну шину цифрової інформації Х2, n-розрядні елементи, причому кожний n-розрядний елемент містить вхідну n-розрядну шину, перший і другий захисні діоди, перший і другий МДП-ключі, транзистор скидання, керуючий транзистор, при цьому вихід першого захисного діода підключений до шини загального потенціалу, кожний з виходів резисторної матриці через відповідний перший МДП-ключ підключений до об'єднаної шини відповідних виходів n-розрядних елементів, інвертуючий вхід операційного підсилювача з'єднано з виходом резистора зворотного зв'язку, вхід якого підключений до виходу операційного підсилювача, вихід якого є виходом пристрою, затвор першого МДП-ключа з'єднаний з відповідним стоком керуючого транзистора, а витік першого МДП-ключа з'єднаний з витоком другого МДП-ключа і з відповідним виходом резисторної матриці, стік другого МДП-ключа підключений до неінвертуючого входу операційного підсилювача і шини загального потенціалу, а його затвор з'єднаний зі стоком транзистора скидання, перша вхідна шина аналогової інформації Х1 з'єднана з входом резисторної матриці, загальна шина резисторної матриці з'єднана із шиною загального потенціалу, n-розрядні входи цифро-аналогового помножувача, крім того, є генератор тактових імпульсів, фазовий селектор, чотири перетворювачі рівнів напруги, шина синхронізації, у кожному n-розрядному елементі є роздільний транзистор, другий захисний діод, транзистор попередньої установки, два МДП-варактори, другий транзистор керування, другий транзистор скидання, причому витік роздільного транзистора підключений до n-розрядних входів цифро-аналогового помножувача, а затвор роздільного транзистора з'єднаний із входом першого захисного діода і підключений до виходу відповідного перетворювача рівня, стік роздільного транзистора підключений до затворів першого МДП-варактора, першого керуючого транзистора і стоку другого транзистора скидання, витоки останніх, а також стік і витік першого МДП-варактора підключені до виходу відповідного перетворювача рівня напруги, затвор другого транзистора скидання з'єднаний із витоком першого транзистора скидання, із входом другого захисного діода і підключені до виходу відповідного перетворювача рівня напруги, стік і витік другого МДП-варактора підключені до затвора другого МДП-ключа і стоку другого керуючого транзистора, витік останнього з'єднаний з витоком і затвором транзистора попередньої установки і підключений до виходу відповідного перетворювача рівня напруги, затвори другого МДП-варактора, другого керуючого транзистора підключені до стоку транзистора попередньої установки, вихід генератора тактових імпульсів підключений до шини синхронізації і до входу фазового селектора, виходи якого з'єднані з відповідними входами перетворювачів рівня напруги, шина загального потенціалу пристрою з'єднана з виходами других захисних діодів і підключена до відповідного шинам генератора тактових імпульсів, фазового селектора, чотирьох перетворювачів рівнів напруги, шини живлення пристрою підключені до відповідного шинам живлення генератора тактових імпульсів, фазового селектора, чотирьох перетворювачів рівня напруги, функціональний перетворювач, що містить функціональний регістр на тригерах з кодовими і рахунковими входами, вхідний блок вентилів, вихідний блок вентилів, адресний блок вентилів, комбінаційну схему адреси, числовий блок пам'яті, вихідний блок елементів АБО, причому кодові виходи функціонального регістра через адресний блок вентилів підключені до входів комбінаційної схеми адреси, виходи якого підключені до входів числового блока пам'яті, виходи якого підключені до рахункових входів функціонального регістра, а його виходи підключені до інформаційних входів вихідного блока вентилів, виходи якого підключені до перших входів вихідного блока елементів АБО, кодові входи функціонального регістра є другими входами пристрою і входами цифрової інформації Х2, які підключені до інформаційних входів вхідного блока вентилів, виходи якого підключені до других входів вихідного блока елементів АБО, виходи якого підключені відповідно до входів n-розрядної шини цифро-аналогового помножувача і до першого виходу пристрою "вихід 1: 1/Х2", крім того, керуючі входи функціонального регістра, вхідного блока вентилів, вихідного блока вентилів, адресногоблока вентилів підключені до керуючих входів пристрою Кфунк, Кмнож, Кділ відповідно, а вхід "скидання" підключено до керуючої шини "скидання" пристрою і до відповідних входів керування функціонального регістра, пристрій, який відрізняється тим, що додатково введені третій і четвертий МДП-ключі, причому третій МДП-ключ входом підключено до об'єднаної шини відповідних виходів n-розрядних елементів, його затвор підключено до шини керування пристрою Кдозвол, а виходом підключено до інвертуючого входу операційного підсилювача і до виходу резистора зворотного зв'язку та виходу четвертого МДП-ключа, затвор якого підключено до шини керування пристрою Ксум, а вхід з'єднано з виходами блока вхідних резисторів, а їх відповідні входи є входами суматора аналогових сигналів Х3, Х4.Х5...й є третім входом пристрою.

Текст

Корисна модель відноситься до обчислювальної техніки і може бути використаний в системах керування при обробці інформації з функціонального перетворення цифрової кодової послідовності і виконанню арифметичних операцій над цифровими й аналоговими сигналами. Побудова систем керування, які використовують гібридні арифметичні розширювачі з малою споживчою потужністю і високою швидкодією є актуальною проблемою. Відомий прецизійний цифровий арифметичний розширювач [1], який містить таблично-алгоритмічний помножувач, цифровий функціональний перетворювач, який має мале споживання потужності, завдяки використанню напівадитивного таблично-логічного методу апаратурної реалізації з таблицями малого обсягу. Але при обробці аналогової і цифрової інформації одночасно необхідно вводити АЦП, що викликає додаткові апаратурні й енергетичні витрати. Найбільш близьким по технічній суті є гібридний обчислювальний пристрій [2], що вміщує операційний підсилювач, резисторну матрицю типу R-2R, резистор зворотного зв'язку, шини живлення, шину загального потенціалу, керуючу шину "скидання" пристрою, першу вхідну шину аналогової інформації Х1 другу вхідну шину цифрової інформації Х2, n-розрядні елементи, причому кожний n-розрядний елемент містить вхідну n-розрядну шину, перший і другий захисні діоди, перший і другий МДП-ключі, транзистор скидання, керуючий транзистор, при цьому вихід першого захисного діода підключений до шини загального потенціалу, кожний з виходів резисторної матриці через відповідний перший МДП-ключ підключені до об'єднаної шини відповідних виходів n-розрядних елементів, інвертуючий вхід операційного підсилювача з'єднано з виходом резистора зворотного зв'язку, вхід якого підключений до виходу операційного підсилювача, вихід якого є виходом пристрою, затвор першого МДПключа з'єднаний з відповідним стоком керуючого транзистора, а витік першого МДП-ключа з'єднаний з витоком другого МДП-ключа і з відповідним виходом резисторної матриці, стік другого МДП-ключа підключений до неінвертуючого входу операційного підсилювача і шині загального потенціалу, а його затвор з'єднаний зі стоком транзистора скидання, перша вхідна шина аналогової інформації Х 1 з'єднана з входом резисторної матриці, загальна шина резисторної матриці з'єднана із шиною загального потенціалу, n-розрядні входи цифроаналогового помножувача, крім того, є генератор тактових імпульсів, фазовий селектор, чотири перетворювачі рівнів напруги, шина синхронізації, у кожному n-розрядному елементі є роздільний транзистор, другий захисний діод, транзистор попередньої установки, два МДП-варактора, другий транзистор керування, другий транзистор скидання, причому витік роздільного транзистора підключений до n-розрядних входів цифроаналогового помножувача, а затвор роздільного транзистора з'єднаний із входом першого захисного діода і підключений до виходу відповідного перетворювача рівня, стік роздільного транзистора підключений до затворів першого МДП-варактора, першого керуючого транзистора і стоку другого транзистора скидання, витоки останніх, а також стік і витік першого МДП-варактора підключені до виходу відповідного перетворювача рівня напруги, затвор другого транзистора скидання з'єднаний із витоком першого транзистора скидання, із входом другого захисного діода і підключені до виходу відповідного перетворювача рівня напруги, стік і витік другого МДПварактора підключені до затвора другого МДП-ключа і стоку другого керуючого транзистора, витік останнього з'єднаний з витоком і затвором транзистора попередньої установки і підключені до виходу відповідного перетворювача рівня напруги, затвори другого МДП-варактора, другого керуючого транзистора підключені до стоку транзистора попередньої установки, вихід генератора тактових імпульсів підключений до шини синхронізації і до входу фазового селектора, виходи якого з'єднані з відповідними входами перетворювачів рівня напруги, шина загального потенціалу пристрою з'єднана з виходами других захисних діодів і підключена до відповідного шинам генератора тактових імпульсів, фазового селектора, чотирьох перетворювачів рівнів напруги, шини живлення пристрою підключені до відповідної шини живлення генератора тактових імпульсів, фазового селектора, чотирьох перетворювачів рівня напруги, функціональний перетворювач, що містить функціональний регістр на тригерах з кодовими і рахунковими входами, вхідний блок вентилів, вихідний блок вентилів, адресний блок вентилів, комбінаційну схему адреси, числовий блок пам'яті, вихідний блок елементів АБО, причому кодові виходи функціонального регістра через адресний блок вентилів підключені до входів комбінаційної схеми адреси, виходи якого підключені до входів числового блоку пам'яті, виходи якого підключені до рахункових входів функціонального регістра, а його виходи підключені до інформаційних входів вихідного блоку вентилів, виходи якого підключені до перших входів вихідного блоку елементів АБО, кодові входи функціонального регістра є другими входами пристрою і входами цифрової інформації Х 2, які підключені до інформаційних входів вхідного блоку вентилів, виходи якого підключені до других входів вихідного блоку елементів АБО, виходи якого підключені відповідно до входів n-розрядної шини цифроаналогового помножувача і до першого виходу пристрою "вихід 1: 1/Х2", крім того, керуючі входи функціонального регістра, вхідного блоку вентилів, вихідного блоку вентилів, адресного блоку вентилів підключені до керуючих входів пристрою Кфунк, Кмнож, Кділ відповідно, а вхід "скидання" підключено до керуючої шини "скидання" пристрою і до відповідних входів керування функціонального регістра і цифроаналогового помножувача. Недоліком даного гібридного арифметичного пристрою є обмежені функціональні можливості. В основу корисної моделі поставлено задачу вдосконалення: розширення функціональних можливостей, гібридного обчислювального пристрою, представленого на Фіг. Це досягається наступним шляхом - у гібридний обчислювальний пристрій: цифроаналогового помножувача, що вміщує операційний підсилювач 1, резисторну матрицю 2 типу R-2R, резистор зворотного зв'язку 3, шини живлення 4, 5, шину загального потенціалу 6, керуючу шину "скидання" пристрою, першу вхідну шину 7 аналогової інформації Х1, другу вхідну шину 8 цифрової інформації Х2, n-розрядні елементи 9, причому кожний n-розрядний елемент містить вхідну n-розрядну шину 10, перший захисний діод VD11, перший VT12 і другий VT13 МДП-ключі, транзистор скидання VT14, керуючий транзистор VT15, при цьому вихід першого захисного діода VT11 підключений до шини загального потенціалу 6, кожний з виходів резисторної матриці 2 через відповідний перший МДП-ключ VT12 підключені до об'єднаної шини 16 відповідних виходів n-розрядних елементів 10, інвертуючий вхід операційного підсилювача 1 з'єднано з виходом резистора зворотного зв'язку 3, вхід якого підключений до виходу операційного підсилювача 1, вихід якого є виходом пристрою, затвор першого МДП-ключа VT12 з'єднаний з відповідним стоком керуючого транзистора VT15, а витік першого МДП-ключа VT12 з'єднаний з витоком другого МДП-ключа VT13 і з відповідним виходом резисторної матриці 2, стік другого МДП-ключа VT13 підключений до неінвертуючого входу операційного підсилювача 1 і шині загального потенціалу 6, а його затвор з'єднаний зі стоком транзистора скидання VT14, перша вхідна шина 7 аналогової інформації Х1 з'єднана з входом резисторної матриці 2, загальна шина резисторної матриці 2 з'єднана із шиною загального потенціалу 6, n-розрядні входи 10 цифроаналогового помножувача, крім того, є генератор тактових імпульсів 18, фазовий селектор 19, чотири перетворювачі рівнів напруги 20, 21, 22, 23, шина синхронізації 24, у кожному n-розрядному елементі 9 є роздільний транзистор VT25, другий захисний діод VD26, транзистор попередньої установки VT27, два МДП-варактора VT28, VT29, другий транзистор керування VT30, другий транзистор скидання VT31, причому витік роздільного транзистора VT25 підключений до n-розрядних входів 10, а затвор роздільного транзистора VT25 з'єднаний із входом першого захисного діода VD11 і підключений до виходу відповідного перетворювача рівня 22, стік роздільного транзистора VT25 підключений до затворів першого МДП-варактора VT28, першого керуючого транзистора VT15 і стоку другого транзистора скидання VT31, витоки останніх, а також стік і витік першого МДП-варактора VT28 підключені до виходу відповідного перетворювача рівня напруги 20, затвор другого транзистора скидання VT31 з'єднаний із витоком першого транзистора скидання VT14, із входом другого захисного діода VD26 і підключені до виходу відповідного перетворювача рівня напруги 21, стік і витік другого МДП-варактора VT29 підключені до затвора другого МДП-ключа VT13 і стоку другого керуючого транзистора VT30, витік останнього з'єднаний з витоком і затвором транзистора попередньої установки VT27 і підключені до виходу відповідного перетворювача рівня напруги 23, затвори другого МДП-варактора VT29, другого керуючого транзистора VT30 підключені до стоку транзистора попередньої установки VT27, вихід генератора тактових імпульсів 18 підключений до шини синхронізації 24 і до входу фазового селектора 19, виходи якого з'єднані з відповідними входами перетворювачів рівня напруги 20, 21, 22, 23, шина загального потенціалу 6 пристрою з'єднана з виходами других захисних діодів VD26 і підключена до відповідного шинам генератора тактових імпульсів 18, фазового селектора 19, чотирьох перетворювачів рівнів напруги 20, 21, 22, 23, шини живлення 4, 5 пристрою підключені до відповідного шинам живлення генератора тактових імпульсів 18, фазового селектора 19, чотирьох перетворювачів рівня напруги 20, 21, 22, 23, функціональний перетворювач, що містить функціональний регістр 32 на тригерах з кодовими і рахунковими входами, вхідний блок вентилів 33, вихідний блок вентилів 34, адресний блок вентилів 35, комбінаційну схему адреси 36, числовий блок пам'яті 37, вихідний блок елементів АБО 38, причому кодові виходи функціонального регістра 32 через адресний блок вентилів 35 підключені до входів комбінаційної схеми адреси 36, виходи якого підключені до входів числового блоку пам'яті 37, виходи якого підключені до рахункових входів функціонального регістра 32, а його виходи підключені до інформаційних входів вихідного блоку вентилів 34, виходи якого підключені до перших входів вихідного блоку елементів АБО 38, кодові входи функціонального регістра 32 є другими входами пристрою і входами 8 цифрової інформації Х2, які підключені до інформаційних входів вхідного блоку вентилів 33, виходи якого підключені до других входів вихідного блоку елементів АБО 38, виходи якого підключені відповідно до входів n-розрядної шини 10 цифроаналогового помножувача і до першого виходу пристрою "вихід 1: 1/Х2", крім того, керуючі входи функціонального регістра 32 вхідного блоку вентилів 33, вихідного блоку вентилів 34, адресного блоку вентилів 35 підключені до керуючих входів пристрою Кфунк, Кмнож, Кділ відповідно, а вхід "скидання" 39 підключено до керуючої шини "скидання" пристрою і до відповідних входів керування функціонального регістра 32, додатково введені третій VT40 і четвертий VT41 МДП-ключі, причому третій МДП-ключ VT40 входом підключено до об'єднаної шині відповідних виходів n-розрядних елементів 16, його затвор підключено до шини керування пристрою Кдозвол, а виходом підключено до інвертируючого входу операційного підсилювача 1 і до виходу резистора 3 зворотного зв'язку та виходу четвертого МДП-ключа VT41, затвор якого підключено до шини керування пристрою Ксум, а вхід з'єднано з виходами блоку вхідних резисторів 42, а їх відповідні вході є входами суматору аналогових сигналів Х3, Х4, Х5... й є третім входом пристрою. При цьому забезпечується надпідсумковий позитивний ефект, зумовлений сукупністю ознак цифроаналогового помножувача, ознак цифрового функціонального перетворювача, ознак цифроаналогового дільника та ознак аналогового інвертируючого суматору, який визначається в тому, що при збереженні ознак цифроаналогового помножувача, цифрового функціонального перетворювача, цифроаналогового дільника розширення функціональних можливостей пристрою забезпечується за рахунок схемотехнічного вирішення підсумовування, завдяки введеним ознакам третього VT40 та четвертого VT41 МДП-ключів, блоку вхідних резисторів 42, їх відповідні вході є входами суматору аналогових сигналів Х3, Х4; Х5... й є третім входом пристрою, шини керування пристрою Кдозвол та шини керування пристрою Ксум з відповідними зв'язками. Отже, пропонований гібридний обчислювальний пристрій дозволяє виконувати з цифровими операндами Х 2 і аналоговими Х1, Х3, Х4, X5,..., наступні функції: (1/Х2); [(1/Х2)·X1]; (Х2-Х1); [-(Х3+Х4+Х5+...)] і задовольняє критерію "суттєві відмінності". Працює пристрій у такий спосіб. Робота гібридного обчислювального пристрою включає наступні режими: цифроаналогового помножувача, цифрового функціонального перетворювача, цифроаналогового дільника, аналогового суматора. Робота гібридного обчислювального пристрою в режимі цифроаналогового помножувача аналогічна [2] і здійснюється з приходом команди множення на керуючий вхід Кмнож та на шину керування Кдозвол одночасно. По команді Кмнож цифрова інформація Х2, яка пройшла через блок вентилів В33 і блок елементів АБО 38 з'являється на входах 10. При цьому перед початком обчислення роблять обнуління ємнісних вузлів S в елементі 9 і ємності вузла зв'язку витоків МДП-ключів VT12, VT13, для цього по шинах 39 подаються імпульси скиду, вироблені ГТІ 18 і виділені фазовим селектором 19, високий рівень яких забезпечується перетворювачем рівня 21,23. Обнуління j ємності вузла S здійснюється через відкритий транзистор VT31 на нульовий потенціал вихідної шини 20 ( 1 ), транзистор VT27 і другий МДП-варактор сприяють подачі напруги високого рівня через відкритий транзистор VT30 на затвор другого МДП-ключа VT13, відкриваючи його підключає відповідні опори 2R до шини загального потенціалу 6, транзистор VT14 закритий. Потім із приходом фази розділення високого рівня з виходу перетворювача рівня 22, відкривається транзистор VT25 і логічний сигнал із входу 10 підзаряджає відповідну ємність вузла S елементу 9. Одночасна поява логічної одиниці на вході 10 і роздільної фази на затворі транзистора VT25 забезпечується імпульсами по шині синхронізації UT 24. З приходом фази керування з виходу перетворювача високого рівня 20, завдяки першому МДП-варактору VT28 "форсується" нагромадження заряду у вузлі S, у результаті відкривається транзистор VT15 і імпульс керування високого рівня надходить на затвор першого МДП-ключа VT12, відкриваючи його підключає відповідний опір 2R матриці 2 до шини 16 і завдяки команді Кдозвол здійснюється передача інформації з об'єднаної шині 16 через третій МДП-ключ VT40 на інвертований вхід операційного підсилювача 1, при цьому транзистор VT14 відкритий і потенціал затвора другого МДП-ключа VT13 є нульовим, а сам ключ VT13 закритий, захисні діоди VD11, VD26 захищають затвори транзисторів VT25, VT31 від пробою. Робота гібридного обчислювального пристрою в режимі цифрового функціонального перетворювача полягає в наступному. По команді "скидання" обнулюється регістр 32, потім після запису в Рг 32 цифрової інформації на керуючий вхід К функ подається команда, у результаті дії якої цифрова інформація, пройшовши вентиль В35, розпізнається комбінаційною схемою Ксх 36, вихідний імпульс якої зчитує відповідну коригувальну константу з числового блоку пам'яті ЧБ 37. Одиниці коригувальної константи по ланцюгу зворотного зв'язку з'являються на рахункових входах регістра Рг 32, під дією яких у регістрі перетвориться вхідна цифрова інформація Х2 у відповідний код 1/Х2. По керуючому входу Кділ імпульс, що надійшов, на керуючий вхід блоку вентилів 34 забезпечує проходження перетвореної інформації через блок вентилів 34, і через блок елементів АБО 38. У результаті на першому виході гібридного обчислювального пристрою з'являється значення функції (1/Х2). Узгодження в часі гібридного обчислювального пристрою забезпечується відповідним синхронізуючим імпульсом 24 Uт. Робота гібридного обчислювального пристрою в режимі цифроаналогового дільника полягає в наступному. Код перетвореної цифрової інформації 1/Х2 з виходу блоку елементів АБО 38 надходить на розрядні шини 10 цифроаналогового помножувача. Далі процес здійснюється в режимі перемножування, що описаний вище. Робота аналогового інвертованого суматора полягає в наступному. Обнулюється команда дозволу на керуючому вході Кдозвол на затворі третього МДП-ключа VT40 завдяки чому здійснюється заборона передачі інформації з об'єднаної шині 16 через третій МДП-ключ VT40 на інвертований вхід операційного підсилювача 1. З приходом команди Ксум на затвор МДП-ключа VT41 вхідна аналогова інформація Х 3, Х4, Х5,..., яка пройшла через блок 42 та МДП-ключ VT41, надходить на інвертований вхід операційного підсилювача 1, і відповідно опису в роботі [3] на виході пристрою з'явиться результат підсумування вхідної аналогової інформації: [Хвиход=(Х3+Х4+Х5+...)]. Отже, пропонований гібридний обчислювальний пристрій забезпечує: - можливість перемножування цифрової й аналогової інформації (Х2·X1); - розподілу аналогової інформації на цифрову X1·(1/X2)=X1/X2; - відтворення значення цифрової функції виду: 1/Х2; - при рівності значень аналогової і цифрової інформації на виході обчислювального пристрою з'являється аналогова величина, що відповідає квадрату значень відповідних вхідних інформаційних сигналів; - підсумування аналогової інформації [-Хвиход=(Х3+Х4+Х5+...)]. Література: 1. Пат.35015А Україна, МПК G06F7/52. Пристрій для ділення або множення n-розрядних чисел / В.М. Лукашенко, Б.А. Шеховцов, А.Г. Лукашенко, Ю.Г. Лега; ЧІТІ - №99074387; Заявл. 29.07.1999; Опубл. 15.03. 2001; Бюл. №2. 2. Пат.10485и, МПК G06G07/26, G06J3/00. Гібридний обчислювальний пристрій / В.М. Лукашенко, Ю.Г. Лега, А.Г. Лукашенко, М.Г. Лукашенко, Я.В. Корпань, С.К. Романовський, М.А. Караван, Д.А. Лукашенко; №u200504233; Заявл.04.05. 2005; Опубл. 15.11.2005; Бюл. №11. 3. Алексенко А.Г. Основы микросхемотехники. Элементы морфологи микроэлектронной аппаратуры. М.: Сов. радио, 1977, 408с.

ДивитисяДодаткова інформація

Назва патенту англійськоюHybrid computer device

Автори англійськоюLukashenko Valentyna Maksymivna, Lukashenko Andrii Hermanovych, Korpan Yaroslav Vasyliovych, Karavan Mykola Anatoliiovych, Lukashenko Dmytro Andriiovych, Rudakov Kostiantyn Serhiiovych, Lukashenko Volodymyr Andriiovych

Назва патенту російськоюГибридное вычислительное устройство

Автори російськоюЛукашенко Валентина Максимовна, Лукашенко Андрей Германович, Корпань Ярослав Васильевич, Караван Николай Анатольевич, Лукашенко Дмитрий Андреевич, Рудаков Константин Сергеевич, Лукашенко Владимир Андреевич

МПК / Мітки

Мітки: обчислювальній, гібридний, пристрій

Код посилання

<a href="https://ua.patents.su/3-33624-gibridnijj-obchislyuvalnijj-pristrijj.html" target="_blank" rel="follow" title="База патентів України">Гібридний обчислювальний пристрій</a>

Попередній патент: Електронагрівач

Наступний патент: Гідромеханічна установка-перетворювач

Випадковий патент: П'єзоелектричний перетворювач механічних величин