Адаптивний діагностичний процесор

Номер патенту: 74995

Опубліковано: 15.02.2006

Автори: Кривцов Володимир Станіславович, Кулік Анатолій Степанович

Формула / Реферат

Адаптивний діагностичний процесор, що містить групу Інформаційних входів, три блоки пам'яті, двійковий лічильник, три схеми порівняння, елемент І, генератор, керуючий вхід, вихідну шину, елемент АБО, демультиплексор, блок тригерів, мультиплексор, причому керуючий вхід з'єднаний з першим входом елемента І, вихід генератора з'єднаний з другим входом елемента І, вихід якого з'єднаний з лічильним входом двійкового лічильника, виходи двійкового лічильника з'єднані з першою групою адресних входів першого блока пам'яті та першою групою входів першої схеми порівняння, група інформаційних входів з'єднана з відповідними інформаційними входами мультиплексора, виходи першого блока пам’яті з’єднані з адресними входами мультиплексора, з адресними входами другого блока пам'яті та з адресними входами демультиплексора, виходи мультиплексора з'єднані з першою групою входів другої схеми порівняння та з першою групою входів третьої схеми порівняння, перша група виходів другого блока пам'яті з'єднана з другою групою входів другої схеми порівняння, друга група виходів другого блока пам'яті з'єднана з другою групою входів третьої схеми порівняння, вихід другої схеми порівняння з'єднаний з першим входом елемента АБО, вихід третьої схеми порівняння з'єднаний з другим входом елемента АБО, вихід якого з'єднаний з інформаційним входом демультиплексора, виходи демультиплексора з'єднані з відповідними входами першого блока тригерів, виходи третього блока пам'яті з'єднані з другою групою входів першої схеми порівняння, який відрізняється тим, що має елемент затримки, другий блок тригерів, виходи якого з'єднані з вихідною шиною, другою групою адресних входів першого блока пам'яті та з адресними входами третього блока пам'яті, вихід першої схеми порівняння з'єднаний з входом "Запис" другого блока тригерів та через елемент затримки з'єднаний з входом "Скид" двійкового лічильника та першого блока тригерів, виходи першого блока тригерів з'єднані з відповідними входами другого блока тригерів.

Текст

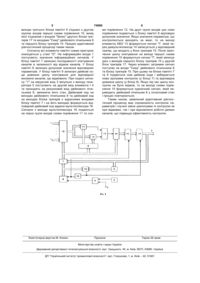

Адаптивний діагностичний процесор, що містить групу Інформаційних входів, три блоки пам'яті, двійковий лічильник, три схеми порівняння, елемент І, генератор, керуючий вхід, вихідну шину, елемент АБО, демультиплексор, блок тригерів, мультиплексор, причому керуючий вхід з'єднаний з першим входом елемента І, вихід генератора з'єднаний з другим входом елемента І, вихід якого з'єднаний з лічильним входом двійкового лічильника, виходи двійкового лічильника з'єднані з першою групою адресних входів першого блока пам'яті та першою групою входів першої схеми порівняння, група інформаційних входів з'єднана з відповідними інформаційними входами мультиплексора, виходи першого блока пам’яті з’єднані з адресними входами мультиплексора, з адресними C2 2 (19) 1 3 74995 4 вого лічильника, виходи двійкового лічильника входом демультиплексора, виходи демультиплекз'єднані з першою групою адресних входів першосора з'єднані з відповідними входами першого го блока пам'яті та першою групою входів першої блока тригерів, виходи третього блока пам'яті схеми порівняння, група інформаційних входів з'єднані з другою групою входів першої схеми поз'єднана з відповідними інформаційними входами рівняння, згідно з винаходом має елемент затриммультиплексора, виходи першого блока пам'яті ки, другий блок тригерів, виходи якого з'єднані з з'єднані з адресними входами мультиплексора, з вихідною шиною, другою групою адресних входів адресними входами другого блока пам'яті та з адпершого блока пам'яті та з адресними входами ресними входами демультиплексора, виходи мутретього блока пам'яті, вихід першої схеми порівльтиплексора з'єднані з першою групою входів няння з'єднаний з входом "Запис" другого блоку другої схеми порівняння та з першою групою вхотригерів та через елемент затримки з'єднаний з дів третьої схеми порівняння, перша група виходів входам "Скид" двійкового лічильника та першого другого блока пам'яті з'єднана з другою групою блоку тригерів, виходи першого блоку тригерів входів другої схеми порівняння, друга група вихоз'єднані з відповідними входами другого блоку дів другого блока пам'яті з'єднана з другою групою тригерів. входів третьої схеми порівняння, вихід другої схеЗаявлений пристрій має новий склад елеменми порівняння з'єднаний з першим входом елеметів, та нову організацію взаємозв'язків між ними, нта АБО, вихід третьої схеми порівняння з'єднаний тобто містить нову сукупність ознак, які забезпез другим входом елемента АБО, вихід якого з'єдчують нові технічні властивості винаходу. Технічнаний з інформаційним входом демультиплексора, ний результат, як наслідок цих властивостей - підвиходи демультиплексора з'єднані з відповідними вищення ефективності контролю, а саме входами першого блока тригерів, виходи третього спроможність контролю параметрів і гнучкої зміни блока пам'яті з'єднані з другою групою входів перциклограми їх контролю при відмовах та відновшої схеми порівняння. ленні працездатності деяких каналів. Недоліком відомого пристрою є обмежені фунНа фіг.1 представлена функціональна схема кціональні можливості, бо він не враховує можлиадаптивного діагностичного процесора. Адаптиввість відновлення працездатності каналів. ний діагностичний процесор містить групу інфорВ основу винаходу поставлено задачу вдоскомаційних входів 1i (і = 1...n), вихідну шину 2, керуналення адаптивного діагностичного процесора ючий вхід 3, елемент І 4, генератор 5, двійковий шляхом введення нового складу елементів, та лічильник 6, перший блок пам'яті 7, другий блок нової організації взаємозв'язків між ними, забезпепам'яті 8, третій блок пам'яті 9, першу схему порівчити ширші функціональні можливості при викориняння 10, другу схему порівняння 11, третю схему станні винаходу, а саме - спроможність гнучкої порівняння 12, елемент АБО 13, демультиплексор зміни циклограми контролю не тільки при відмовах 14, блок тригерів 15, мультиплексор 16, другий деяких каналів, а також при відновленні працездаблок тригерів 17, елемент затримки 18, причому тності каналів, що підвищує ефективність контрокеруючий вхід 3 з'єднаний з першим входом елелю. мента І 4, вихід генератора 5 з'єднаний з другим Поставлене завдання вирішується тим, що входом елемента І 4, вихід якого з'єднаний з рахуадаптивний діагностичний процесор містить групу нковим входом двійкового лічильника 6, виходи інформаційних входів, три блоки пам'яті, двійковий двійкового лічильника 6 з'єднані з першою групою лічильник, три схеми порівняння, елемент І, генеадресних входів блока пам'яті7, та першою груратор, керуючий вхід, вихідну шину, елемент АБО, пою входів першої схеми порівняння 10, група індемультиплексор, блок тригерів, мультиплексор, формаційних входів 1i(і = 1...n) з'єднана з відповідпричому керуючий вхід з'єднаний з першим вхоними інформаційними входами мультиплексора дом елемента І, вихід генератора з'єднаний з дру16, виходи першого блока пам'яті 7 з'єднані з адгим входом елемента І, вихід якого з'єднаний з ресними входами мультиплексора 16, з адресними рахунковим входом двійкового лічильника, виходи входами другого блока пам'яті 8, та з адресними двійкового лічильника з'єднані з першою групою входами демультиплексора 14, виходи мультиплеадресних входів першого блока пам'яті та першою ксора 16 з'єднані з першою групою входів другої групою входів першої схеми порівняння, група інсхеми порівняння 11 та з першою групою входів формаційних входів з'єднана з відповідними інфотретьої схеми порівняння 12, перша група виходів рмаційними входами мультиплексора, виходи другого блока пам'яті 8 з'єднана з другою групою першого блока пам'яті з'єднані з адресними вховходів другої схеми порівняння 11, друга група дами мультиплексора, з адресними входами друвиходів блока пам'яті 8 з'єднана з другою групою гого блока пам'яті та з адресними входами девходів третьої схеми порівняння 12, вихід другої мультиплексора, виходи мультиплексора з'єднані схеми порівняння 11 з'єднаний з першим входом з першою групою входів другої схеми порівняння елемента АБО 13, вихід третьої схеми порівняння та з першою групою входів третьої схеми порів12 з'єднаний з другим входом елемента АБО 13, няння, перша група виходів другого блока пам'яті вихід якого з'єднаний з інформаційним входом з'єднана з другою групою входів другої схеми порідемультиплексора 14, виходи якого з'єднані з відвняння, друга група виходів другого блока пам'яті повідними входами першого блока тригерів 15, з'єднана з другою групою входів третьої схеми виходи першого блока тригерів 15 з'єднані з відпопорівняння, вихід другої схеми порівняння з'єднавідними входами другого блока тригерів 17, вихоний з першим входом елемента АБО, вихід третьої ди якого з'єднані з вихідною шиною 2, з другою схеми порівняння з'єднаний з другим входом елегрупою адресних входів першого блока пам'яті 7 та мента АБО, вихід якого з'єднаний з інформаційним з адресними входами третього блока пам'яті 9, 5 74995 6 виходи третього блока пам'яті 9 з'єднані з другою ми порівняння 12. На другі групи входів цих схем групою входів першої схеми порівняння 10, вихід порівняння подаються з блоку пам'яті 8 відповідні якої з'єднаний з входом "Запис" другого блока тридопускові значення. Якщо значення параметра, що герів 17 та входами "Скид" двійкового лічильника 6 контролюється виходять за межі, то на виході та першого блоку тригерів 15. Працює адаптивний елемента АБО 13 формується сигнал "І", який чедіагностичний процесор таким чином. рез демультиплексор 14 записується у відповідний Спочатку всі елементи пам'яті схеми пристрою тригер, що входить у блок тригерів 15. Після закінзнаходяться у стані "О". На інформаційні входи 1 чення циклу опитування на виході першої схеми поступають значення інформаційних сигналів. У порівняння 10 формується сигнал "І", який записує блоці пам'яті 7 записані послідовності опитування дані з виходів першого блоку тригерів 15 у другий каналів в залежності від відмов каналів. У блоці блок тригерів 17. Через елемент затримки сигнал пам'яті 8 записані допускові значення відповідних поступає на входи "Скид" двійкового лічильника 6 параметрів. У блоці пам'яті 9 записані двійкові кота блоку тригерів 15. При цьому на блоки пам'яті 7 ди довжини циклу опитування для відповідної та 9 подаються нові двійкові коди і вибирається множини каналів, що відмовили. При подачі сигнанова програма контролю (у блоці 7) та відповідна лу "1" на керуючий вхід 3 імпульси з виходу генедовжина циклу (у блоці 9). Якщо під час циклу конратора 5 поступають на другий вхід елемента І 4 тролю не було відмов, то на виході схеми порівта проходять на рахунковий вхід двійкового лічиняння 10 формується одиничний сигнал, який пельника 6, змінюючи його стан. Двійковий код на реводить двійковий лічильник 6 у початковий стан виходах двійкового лічильника 6 та двійковий код і процес повторюється. на виходах блока тригерів є адресними входами Таким чином, заявлений адаптивний діагносблоку пам'яті 7 і на його виходах формується відтичний процесор має спроможність контролю паповідний двійковий код адреси мультиплексора 16. раметрів і гнучкої зміни циклограми їх контролю як Сигнали з вихода мультиплексора 16 подаються при відмовах, так і при відновленні роботи деяких на перші групи входів схеми порівняння 11 та схеканалів, що підвищує ефективність контролю. Комп’ютерна верстка M. Клюкін Підписне Тираж 26 прим. Міністерство освіти і науки України Державний департамент інтелектуальної власності, вул. Урицького, 45, м. Київ, МСП, 03680, Україна ДП “Український інститут промислової власності”, вул. Глазунова, 1, м. Київ – 42, 01601

ДивитисяДодаткова інформація

Назва патенту англійськоюAdaptive diagnostic processor

Автори англійськоюKryvtsov Volodymyr Stanislavovych, Kulik Anatolii Stepanovych

Назва патенту російськоюАдаптивный диагностический процессор

Автори російськоюКривцов Владимир Станиславович, Кулик Анатолий Степанович

МПК / Мітки

МПК: G06F 9/00, H04B 17/00, G06F 15/00

Мітки: діагностичний, адаптивний, процесор

Код посилання

<a href="https://ua.patents.su/3-74995-adaptivnijj-diagnostichnijj-procesor.html" target="_blank" rel="follow" title="База патентів України">Адаптивний діагностичний процесор</a>

Попередній патент: Спосіб одержання 3-трифторметилфеніл-4-ціанобензилкетону

Наступний патент: Пристрій для визначення парності числа, представленого у системі залишкових класів

Випадковий патент: Пристрій для безконтактного вимірювання температури ротора гідрогенератора