Буферний каскад

Номер патенту: 38424

Опубліковано: 12.01.2009

Автори: Притула Максим Олександрович, Крупельницький Леонід Віталійович, Головатюк Олександр Володимирович, Азаров Олексій Дмитрович

Формула / Реферат

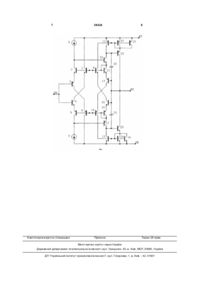

Буферний каскад, який містить вісімнадцять транзисторів, два джерела струму, шини додатного та від'ємного живлення, вхідну та вихідну шини, причому вхідну шину з'єднано з базами другого та третього транзисторів, емітери яких з'єднано з емітерами першого та четвертого транзисторів, колектор другого транзистора з'єднано з емітером шостого транзистора, колектор третього транзистора з'єднано з емітером п'ятого транзистора, колектор п'ятого транзистора з'єднано з шиною додатного живлення, колектор шостого транзистора з'єднано з шиною від'ємного живлення, який відрізняється тим, що у нього введено дев'ятнадцятий, двадцятий, двадцять перший, двадцять другий транзистори, причому колектор першого транзистора з'єднаний з базою десятого транзистора та шиною додатного живлення через перше джерело струму, колектор четвертого транзистора з'єднаний з базою п'ятнадцятого транзистора та шиною від'ємного живлення через друге джерело струму, базу та колектор чотирнадцятого транзистора об'єднано та з'єднано з емітером п'ятнадцятого транзистора та базами четвертого, шостого та восьмого транзисторів, базу та колектор одинадцятого транзистора об'єднано та з'єднано з емітером десятого транзистора та базами першого, п'ятого та сьомого транзисторів, емітер одинадцятого транзистора з'єднано з емітером дванадцятого транзистора, емітер тринадцятого транзистора з'єднано з емітером чотирнадцятого транзистора, колектори та бази сімнадцятого та двадцять першого транзисторів об'єднані та з'єднані з базою дев'ятого, емітером вісімнадцятого та колектором сьомого транзисторів, емітери дев'ятого, сімнадцятого та двадцять першого транзисторів об'єднані та з'єднані з шиною додатного живлення, колектори та бази двадцятого та двадцять другого транзисторів об'єднані та з'єднані з базою шістнадцятого, емітером дев'ятнадцятого та колектором восьмого транзисторів, емітери шістнадцятого, двадцятого та двадцять другого транзисторів об'єднані та з'єднані з шиною від'ємного живлення, колектор дев'ятого транзистора з'єднано з першим виводом першого конденсатора, колектором десятого та базою вісімнадцятого транзисторів, колектор п'ятнадцятого транзистора з'єднано з другим виводом другого конденсатора, колектором шістнадцятого та базою дев'ятнадцятого транзисторів, вихідна шина з'єднана з другим виводом першого конденсатора, базами дванадцятого та тринадцятого транзисторів, колекторами вісімнадцятого та дев'ятнадцятого транзисторів.

Текст

Буферний каскад, який містить вісімнадцять транзисторів, два джерела струму, шини додатного та від'ємного живлення, вхідну та ви хідну шини, причому вхідну шину з'єднано з базами другого та третього транзисторів, емітери яких з'єднано з емітерами першого та четвертого транзисторів, колектор другого транзистора з'єднано з емітером шостого транзистора, колектор третього транзистора з'єднано з емітером п'ятого транзистора, колектор п'ятого транзистора з'єднано з шиною додатного живлення, колектор шостого транзистора з'єднано з шиною від'ємного живлення, який відрізняється тим, що у нього введено дев'ятнадцятий, двадцятий, двадцять перший, двадцять другий транзистори, причому колектор першого транзистора з'єднаний з базою десятого транзистора та шиною додатного живлення через перше джерело струму, колектор четвертого транзистора з'єднаний з базою п'ятнадцятого транзистора та шиною від'ємного живлення через друге джерело струму, базу та колектор чотирнадцятого транзис U 2 (19) 1 3 38424 гого та сьомого транзисторів з’єднано з шинами додатного та від’ємного живлення відповідно. Емітери третього та шостого транзисторів з’єднано з вихідною шиною. Основним недоліком аналогу є низька точність, яка обумовлена наявністю вихідної напруги зміщення нуля через неідентичність параметрів пар n-р-n та р-n-р транзисторів у верхньому та нижньому каналах. За прототип обрано буферний пристрій (Патент України №24882, М.КЛ H03F3/26,2006), який містить дванадцять транзисторів, два джерела струму, шини додатного та від’ємного живлення, вхідн у та вихідн у шини, причому вхідну шину з’єднано з базами четвертого та п’ятого транзисторів, емітери четвертого і п’ятого транзисторів з’єднано з емітерами дев’ятого і десятого транзисторів відповідно, бази дев’ятого і десятого транзисторів з’єднано з базами третього і шостого транзисторів відповідно, колектор дев’ятого транзистора з’єднано з емітером першого транзистора, базу першого транзистора з’єднано з базою другого транзистора, колектор першого транзистора з’єднано з першим виводом першого джерела струму, др угі виводи першого і другого джерела струмів, а також колектори другого і сьомого транзисторів з’єднано з шинами додатного і від’ємного живлення відповідно, емітери другого і сьомого транзисторів з’єднано з колекторами третього і шостого транзисторів відповідно, емітери третього і шостого транзисторів з’єднано з емітерами одинадцятого і дванадцятого транзисторів відповідно, бази та колектори одинадцятого і дванадцятого транзисторів з’єднано з вихідною шиною, введено тринадцятий, чотирнадцятий, п’ятнадцятий, шістнадцятий, сімнадцятий, вісімнадцятий транзистори, причому колектори тринадцятого п’ятнадцятого, сімнадцятого та чотирнадцятого, шістнадцятого, вісімнадцятого транзисторів з’єднано з шинами додатного і від’ємного живлення відповідно, бази тринадцятого і чотирнадцятого транзисторів з’єднано з колекторами першого і восьмого транзисторів відповідно, а також з першими виводами першого і другого джерел струмів відповідно, емітери тринадцятого і чотирнадцятого транзисторів з’єднано з базами першого, другого та сьомого, восьмого транзисторів відповідно, бази п’ятнадцятого і шістнадцятого транзисторів з’єднано з емітерами першого і восьмого транзисторів відповідно, а також з колекторами дев’ятого і десятого транзисторів відповідно, емітери п’ятнадцятого і шістнадцятого транзисторів з’єднано з базами третього, дев’ятого та шостого, десятого транзисторів відповідно, бази сімнадцятого і вісімнадцятого транзисторів з’єднано з колекторами третього і шостого транзисторів відповідно, а також з емітерами другого і сьомого транзисторів відповідно емітери сімнадцятого і вісімнадцятого транзисторів з’єднано з колекторами п’ятого і четвертого транзисторів відповідно. Недоліками прототипу є низька точність, що викликано значною вихідною напругою зміщення нуля через неідентичність параметрів пар n-p-n та р-n-р транзисторів у верхньому та нижньому каналах. 4 В основу корисної моделі поставлено задачу створення буферного каскаду, в якому за рахунок введення нових елементів та зв’язків між ними зменшується вихідна напруга зміщення нуля, завдяки чому підвищується точність пристрою. Поставлена задача досягається тим, що в буферний пристрій, який містить вісімнадцять транзисторів, два джерела струму, шини додатного та від’ємного живлення, вхідну та ви хідн у шини, причому вхідн у шин у з’єднано з базами другого та третього транзисторів, емітери яких з’єднано з емітерами першого та четвертого транзисторів, колектор другого транзистора з’єднано з емітером шостого транзистора, колектор третього транзистора з’єднано з емітером п’ятого транзистора, колектор п’ятого транзистора з’єднано з шиною додатного живлення, колектор шостого транзистора з’єднано з шиною від’ємного живлення, введено дев’ятнадцятий, двадцятий, двадцять перший, двадцять другий транзистори, причому колектор першого транзистора з’єднаний з базою десятого транзистора та шиною додатного живлення через перше джерело струму, колектор четвертого транзистора з’єднаний з базою п’ятнадцятого транзистора та шиною від’ємного живлення через друге джерело струму, база та колектор чотирнадцятого транзистора об’єднано та з’єднано з емітером п’ятнадцятого транзистора та базами четвертого, шостого та восьмого транзисторів, база та колектор одинадцятого транзистора об’єднано та з’єднано з емітером десятого транзистора та базами першого, п’ятого та сьомого транзисторів, емітер одинадцятого транзистора з’єднано з емітером дванадцятого транзистора, емітер тринадцятого транзистора з’єднано з емітером чотирнадцятого транзистора, колектори та бази сімнадцятого та двадцять першого транзисторів об’єднані та з’єднані з базою дев’ятого, емітером вісімнадцятого та колектором сьомого транзисторів, емітери дев’ятого, сімнадцятого та двадцять першого транзисторів об’єднані та з’єднані з шиною додатного живлення, колектори та бази двадцятого та двадцять другого транзисторів об’єднані та з’єднані з базою шістнадцятого, емітером дев’ятнадцятого та колектором восьмого транзисторів, емітери шістнадцятого, двадцятого та двадцять другого транзисторів об’єднані та з’єднані з шиною від’ємного живлення, колектор дев’ятого транзистора з’єднано з першим виводом першого конденсатора, колектором десятого та базою вісімнадцятого транзисторів, колектор п’ятнадцятого транзистора з’єднано з другим виводом другого конденсатора, колектором шістнадцятого та базою дев’ятнадцятого транзисторів, вихідна шина з’єднана з другим виводом першого конденсатора, базами дванадцятого та тринадцятого транзисторів, колекторами вісімнадцятого та дев’ятнадцятого транзисторів. На кресленні представлено принципову схему буферного каскаду. Пристрій містить вхідну шину 29, яку з’єднано з базами другого 3 та третього 4 транзисторів, емітери яких з’єднано з емітерами першого 2 та четвертого 5 транзисторів, колектор другого 3 транзистора з’єднано з емітером шостого 8 транзис 5 38424 тора, колектор третього 4 транзистора з’єднано з емітером п’ятого 7 транзистора, колектор п’ятого 7 транзистора з’єднано з шиною додатного живлення 27, колектор шостого транзистора 8 з’єднано з шиною від’ємного живлення 28, колектор першого транзистора 2 з’єднаний з базою десятого транзистора 12 та шиною додатного живлення 27 через перше джерело струму 1, колектор четвертого транзистора 5 з’єднаний з базою п’ятнадцятого транзистора 17 та шиною від’ємного живлення 28 через друге джерело струму 6, база та колектор чотирнадцятого транзистора 16 об’єднано та з’єднано з емітером п’ятнадцятого транзистора 17 та базами четвертого 5, шостого 8 та восьмого 10 транзисторів, база та колектор одинадцятого транзистора 13 об’єднано та з’єднано з емітером десятого транзистора 12 та базами першого 2, п’ятого 7 та сьомого 9 транзисторів, емітер одинадцятого транзистора 13 з’єднано з емітером дванадцятого транзистора 14, емітер тринадцятого транзистора 15 з’єднано з емітером чотирнадцятого транзистора 16, колектори та бази сімнадцятого 21 та двадцять першого 25 транзисторів об’єднані та з’єднані з базою дев’ятого 11, емітером вісімнадцятого 22 та колектором сьомого 9 транзисторів, емітери дев’ятого 11, сімнадцятого 21 та двадцять першого 25 транзисторів об’єднані та з’єднані з шиною додатного живлення 27, колектори та бази двадцятого 24 та двадцять другого 26 транзисторів об’єднані та з’єднані з базою шістнадцятого 18, емітером дев’ятнадцятого 23 та колектором восьмого 10 транзисторів, емітери шістнадцятого 18, двадцятого 24 та двадцять другого 26 транзисторів об’єднані та з’єднані з шиною від’ємного живлення 28, колектор дев’ятого транзистора 11 з’єднано з першим виводом першого конденсатора 19, колектором десятого 12 та базою вісімнадцятого 22 транзисторів, колектор п’ятнадцятого транзистора 17 з’єднано з другим виводом другого конденсатора 20, колектором шістнадцятого 18 та базою дев’ятнадцятого 23 транзисторів, вихідна шина 30 з’єднана з другим виводом першого конденсатора 19, базами дванадцятого 14 та тринадцятого 15 транзисторів, колекторами вісімнадцятого 22 та дев’ятнадцятого 23 транзисторів. Буферний каскад працює таким чином: якщо напруга на вхідній шині 29 збільшується, то третій транзистор 4 привідкривається, а другий транзистор 3 призакривається. Потенціал емітера другого транзистора 3 та третього транзистора 4 збільшується. Завдяки зворотному зв’язку, що діє в схемі за допомогою десятого 12 та п’ятнадцятого 17 транзисторів, потенціали емітерів десятого 12 та п’ятнадцятого 17 транзисторів зростають. При цьому дванадцятий транзистор 14 привідкрива 6 ється, а тринадцятий 15 призакривається. За таких умов колекторний струм десятого транзистора 12 збільшується, а колекторний струм п’ятнадцятого 17 транзистора зменшується. При цьому вісімнадцятий транзистор 22 привідкривається, а дев’ятнадцятий транзистор 23 призакривається. За таких умов струм колектора вісімнадцятого транзистора 22 зростає, а струм колектора дев’ятнадцятого транзистора 23 зменшується. Таким чином потенціал на вихідній шині 30 зростає аж поки вихідна напруга не досягне рівня вхідної напруги. Якщо напруга на вхідній шині 29 зменшується, то третій транзистор 4 призакривається, а другий транзистор 3 привідкривається. Потенціал емітера другого транзистора 3 та третього транзистора 4 зменшується. Завдяки зворотному зв’язку, що діє в схемі за допомогою десятого 12 та п’ятнадцятого 17 транзисторів, потенціали емітерів десятого 12 та п’ятнадцятого 17 транзисторів зменшуються. При цьому дванадцятий транзистор 14 призакривається, а тринадцятий 15 привідкривається. За таких умов колекторний струм десятого транзистора 12 зменшується, а колекторний струм п’ятнадцятого 17 транзистора збільшується. При цьому вісімнадцятий транзистор 22 призакривається, а дев’ятнадцятий транзистор 23 привідкривається. За таких умов струм колектора вісімнадцятого транзистора 22 зменшується, а струм колектора дев’ятнадцятого транзистора 23 зростає. Таким чином потенціал на вихідній шині 30 зменшується аж поки вихідна напруга не досягне рівня вхідної напруги. Для запобігання впливу змінення напруги на переходах колектор-емітер другого 3, третього 4, дванадцятого 14 та тринадцятого 15 транзисторів, у схему введено каскодні каскади відповідно на п’ятому 7 та шостому 8 транзисторах, а також на одинадцятому 13 та чотирнадцятому 16 транзисторах. Для прискорення заряду коригуючи х ємностей 19 та 20 в схему введено вісімнадцятий 22 та дев’ятнадцятий 23 транзистори, які працюють в активному режимі і забезпечують збільшення струму заряду, розряду за умови розбалансу між входом та ви ходом схеми. Це сприяє значному підвищенню швидкодії схеми завдяки підвищенню швидкості наростання вихідного сигналу. Шини додатного 27 та від’ємного 28 живлення забезпечують живлення схеми. Дев’ятий 11, сімнадцятий 21, двадцять перший 25, сьомий 9, восьмий 10, шістнадцятий 18, двадцятий 24 та двадцять другий 26 забезпечують необхідний режим роботи активних елементів схеми. Джерела струму 1 та 6 забезпечують завдання робочої точки транзисторів. 7 Комп’ютерна в ерстка І.Скворцов а 38424 8 Підписне Тираж 28 прим. Міністерство осв іт и і науки України Держав ний департамент інтелектуальної в ласності, вул. Урицького, 45, м. Київ , МСП, 03680, Україна ДП “Український інститут промислов ої в ласності”, вул. Глазунова, 1, м. Київ – 42, 01601

ДивитисяДодаткова інформація

Назва патенту англійськоюBuffer stage

Автори англійськоюAzarov Oleksii Dmytrovych, Prytula Maksym Oleksandrovych, Holovatiuk Oleksandr Volodymyrovych, Krupelnytskyi Leonid Vitaliiovych

Назва патенту російськоюБуферний каскад

Автори російськоюАзаров Алексей Дмитриевич, Притула Максим Александрович, Головатюк Александр Владимирович, Крупельницкий Леонид Витальевич

МПК / Мітки

Код посилання

<a href="https://ua.patents.su/4-38424-bufernijj-kaskad.html" target="_blank" rel="follow" title="База патентів України">Буферний каскад</a>

Попередній патент: Буферний каскад

Наступний патент: Буферний каскад

Випадковий патент: Цифровий спосіб виміру радіальних швидкостей цілей