Буферний каскад

Номер патенту: 23906

Опубліковано: 11.06.2007

Автори: Крупельницький Леонід Віталійович, Ратнюк Вадим Вадимович, Кадук Олександр Володимирович, Азаров Олексій Дмитрович

Формула / Реферат

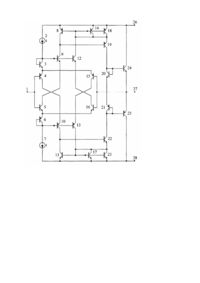

Буферний каскад, що містить шість транзисторів, два джерела струму, вхідну та вихідну шини і шини додатного та від'ємного живлення, причому вхідну шину з'єднано з базами другого та третього транзисторів, колектори яких з'єднано з емітерами шостого та п'ятого транзисторів, відповідно, база та колектор першого транзистора об'єднані між собою та з'єднані з базою п'ятого транзистора, а також з шиною додатного живлення через перше джерело струму, база та колектор четвертого транзистора об'єднані між собою, який відрізняється тим, що в нього введено шістнадцять транзисторів, причому як четвертий транзистор використано транзистор р-n-р типу, а емітери першого і другого транзисторів об'єднано між собою і з'єднано з емітером дванадцятого транзистора, емітери третього і четвертого транзисторів об'єднано між собою і з'єднано з емітером тринадцятого транзистора, база п'ятого транзистора з'єднана з базою дев'ятого транзистора, колектор і база четвертого транзистора з'єднані з базами шостого, десятого транзисторів, а також через друге джерело струму - з шиною від'ємного живлення, колектори п'ятого і шостого транзисторів з'єднано з колекторами сьомого і восьмого транзисторів, відповідно, а також з базами шістнадцятого і дев'ятнадцятого транзисторів, відповідно, емітери дев'ятого і десятого транзисторів з'єднано з колекторами тринадцятого і дванадцятого транзисторів, відповідно, колектор дев'ятого транзистора з'єднано з базами сьомого, одинадцятого і п'ятнадцятого транзисторів, а також з колекторами одинадцятого та п'ятнадцятого транзисторів і емітером шістнадцятого транзистора, колектор десятого транзистора з'єднано з базами восьмого, чотирнадцятого і двадцятого транзисторів, а також з колекторами чотирнадцятого та двадцятого транзисторів і емітером дев'ятнадцятого транзистора, колектори шістнадцятого і дев'ятнадцятого транзисторів з'єднано з базами і колекторами сімнадцятого і вісімнадцятого транзисторів, відповідно, а також з базами двадцять першого і двадцять другого транзисторів, відповідно, емітери сьомого, одинадцятого, п'ятнадцятого транзисторів, а також колектор двадцять першого транзистора з'єднано з шиною додатного живлення, емітери восьмого, чотирнадцятого, двадцятого, а також колектор двадцять другого транзисторів з'єднано з шиною від'ємного живлення, емітери сімнадцятого і вісімнадцятого транзисторів об'єднано між собою, бази дванадцятого і тринадцятого транзисторів з'єднано з емітерами двадцять першого і двадцять другого транзисторів, а також з вихідною шиною.

Текст

Корисна модель відноситься до імпульсної техніки і може бути використана в аналогово-цифрових перетворювачах і цифрових вимірювальних приладах. Відомий буферний пристрій [Бахтиаров Г.Д., Малинин В.В., Школин В.П. Аналого-цифровые преобразорватели / Под ред. Г.Д.Бахтиарова. - М.: Советское радио, 1980. - 280 с. ил. Рис. 6.28 на сторінці 150.], який містить вісім транзисторів, два джерела струму, шини додатного та від'ємного живлення, вхідну та ви хідну шини. Бази четвертого та п'ятого транзисторів з'єднано з вхідною шиною. Емітери четвертого та п'ятого транзисторів з'єднано з емітерами першого та восьмого транзисторів, відповідно, та з базами третього та шостого транзисторів, відповідно, колектори четвертого та п'ятого транзисторів з'єднано з колекторами шостого та третього транзисторів, відповідно, а також з емітерами сьомого та другого транзисторів, відповідно. Бази та колектори першого та восьмого транзисторів з'єднано з базами другого та сьомого транзисторів, відповідно, а також з'єднано з шинами додатного та від'ємного живлення через перше та друге джерела струму, відповідно. Колектори другого та сьомого транзисторів з'єднано з шинами додатного та від'ємного живлення, відповідно. Емітери третього та шостого транзисторів з'єднано з вихідною шиною. Основним недоліком цього пристрою є низька точність, що викликано значною вихідною напругою зміщення нуля через неідентичність параметрів пар n-р-n та р-n-р транзисторів у верхньому та нижньому каналах. За найближчий аналог обрано буферний каскад [Патент на корисну модель №15896 МПК (2006) НОЗК 5/22, G05b 1/00. 17.07.2006. Бюл.№7], який містить дванадцять транзисторів, два джерела струму, вхідну та ви хідну шини і шини додатного та від'ємного живлення. Вхідна шина з'єднана з базами четвертого та п'ятого транзисторів, емітери яких з'єднано з емітерами дев'ятого та десятого транзисторів, відповідно, а колектори їх з'єднано з колекторами шостого та третього транзисторів, відповідно, а також з емітерами сьомого та другого транзисторів, відповідно, бази та колектори дев'ятого та десятого транзисторів об'єднані, та з'єднані з базами третього та шостого транзисторів, відповідно, крім того база і колектор дев'ятого транзистора з'єднана з емітером першого транзистора, а база і колектор десятого транзистора з'єднана з базою і колектором восьмого транзистора, базу і колектор першого транзистора з'єднано з базою другого транзистора та з шиною додатного живлення через перше джерело струму, емітер восьмого транзистора з'єднано з базою сьомого транзистора та з шиною від'ємного живленням через друге джерело струму, колектори другого та сьомого транзисторів з'єднано з шинами додатного та від'ємного живлення, відповідно, емітери третього та шостого транзисторів з'єднано з емітерами одинадцятого та дванадцятого транзисторів, відповідно, бази та колектори одинадцятого та дванадцятого транзисторів з'єднано з вихідною шиною. Недоліком найближчого аналогу є низька навантажувальна здатність, що призводить до значного збільшення похибки передачі вхідного сигналу на ви хід за умови підключення навантаження до виходу схеми. В основу корисної моделі поставлено задачу створення буферного каскаду, в якому за рахунок введення нових елементів та зв'язків досягається збільшення навантажувальної здатності, завдяки чому підвищується точність пристрою. Поставлена задача досягається тим, що в буферний каскад, який містить шість транзисторів, два джерела струму, вхідну та вихідн у шини і шини додатного та від'ємного живлення, причому вхідну шину з'єднано з базами другого та третього транзисторів, колектори яких з'єднано з емітерами шостого та п'ятого транзисторів, відповідно, база та колектор першого транзистора об'єднані між собою та з'єднані з базою п'ятого транзистора, а також з шиною додатного живлення через перше джерело струму, база та колектор четвертого транзистора об'єднані між собою, введено шістнадцять транзисторів, причому як четвертий транзистор використано транзистор р-n-р типу, а емітери першого і другого транзисторів об'єднано між собою і з'єднано з емітером дванадцятого транзистора, емітери третього і четвертого транзисторів об'єднано між собою і з'єднано з емітером тринадцятого транзистора, база п'ятого транзистора з'єднана з базою дев'ятого транзистора, колектор і база четвертого транзистора з'єднані з базами шостого, десятого транзисторів, а також через друге джерело струму з шиною від'ємного живлення, колектори п'ятого і шостого транзисторів з'єднано з колекторами сьомогоі восьмого транзисторів, відповідно, а також з базами шістнадцятого і дев'ятнадцятого транзисторів, відповідно, емітери дев'ятого і десятого транзисторів з'єднано з колекторами тринадцятого і дванадцятого транзисторів, відповідно, колектор дев'ятого транзистора з'єднано з базами сьомого, одинадцятого і п'ятнадцятого транзисторів, а також з колекторами одинадцятого та п'ятнадцятого транзисторів і емітером шістнадцятого транзистора, колектор десятого транзистора з'єднано з базами восьмого, чотирнадцятого і двадцятого транзисторів, а також з колекторами чотирнадцятого та двадцятого транзисторів і емітером дев'ятнадцятого транзистора, колектори шістнадцятого і дев'ятнадцятого транзисторів з'єднано з базами і колекторами сімнадцятого і вісімнадцятого транзисторів, відповідно, а також з базами двадцять першого і двадцять другого транзисторів, відповідно, емітери сьомого, одинадцятого, п'ятнадцятого транзисторів, а також колектор двадцять першого транзистора з'єднано з шиною додатного живлення, емітери восьмого, чотирнадцятого, двадцятого, а також колектор двадцять другого транзисторів з'єднано з шиною від'ємного живлення, емітери сімнадцятого і вісімнадцятого транзисторів об'єднано між собою, бази дванадцятого і тринадцятого транзисторів з'єднано з емітерами двадцять першого і двадцять другого транзисторів, а також з вихідною шиною. На кресленні представлено принципову схему буферного каскаду. Пристрій містить вхідну шину 1, яку з'єднано з базами другого 4 та третього 5 транзисторів, емітери яких з'єднано з емітерами першого 3 і четвертого 6 транзисторів, відповідно, а також з емітерами дванадцятого 15 і тринадцятого 16 транзисторів, відповідно, колектори другого 4 і третього 5 транзисторів з'єднано з емітерами шостого 10 і п'ятого 9 транзисторів, відповідно, база та колектор першого 3 транзистора об'єднано та з'єднано з базами п'ятого 9 і дев'ятого 12 транзисторів, а також через перше джерело струму 2 з шиною додатного живлення 26, база та колектор четвертого 6 транзистора об'єднано та з'єднано з базами шостого 10 і десятого 13 транзисторів, а також через друге джерело струму 7 з шиною від'ємного живлення 28, колектори п'ятого 9 і шостого 10 транзисторів з'єднано з колекторами сьомого 8 і восьмого 11 транзисторів, відповідно, а також з базами шістнадцятого 19 і дев'ятнадцятого 22 транзисторів, відповідно, емітери дев'ятого 12 і десятого 13 транзисторів з'єднано з колекторами тринадцятого 16 і дванадцятого 15 транзисторів, відповідно, колектор дев'ятого 12 транзистора з'єднано з базами сьомого 8, одинадцятого 14 і п'ятнадцятого 18 транзисторів, а також з колекторами одинадцятого 14 та п'ятнадцятого 18 транзисторів і емітером шістнадцятого 19 транзистора, колектор десятого 13 транзистора з'єднано з базами восьмого 11, чотирнадцятого 17 і двадцятого 23 транзисторів, а також з колекторами чотирнадцятого 17 та двадцятого 23 транзисторів і емітером дев'ятнадцятого 22 транзистора, колектори шістнадцятого 19 і дев'ятнадцятого 22 транзисторів з'єднано з базами і колекторами сімнадцятого 20 і вісімнадцятого 21 транзисторів, відповідно, а також з базами двадцять першого 24 і двадцять другого 25 транзисторів, відповідно, емітери сьомого 8, одинадцятого 14, п'ятнадцятого 18 транзисторів, а також колектор двадцять першого 24 транзистора з'єднано з шиною додатного живлення 26, емітери восьмого 11, чотирнадцятого 17, двадцятого 23, а також колектор двадцять другого 25 транзисторів з'єднано з шиною від'ємного живлення 28, емітери сімнадцятого 20 і вісімнадцятого 21 транзисторів об'єднано між собою, бази дванадцятого 15 і тринадцятого 16 транзисторів з'єднано з емітерами двадцять першого 24 і двадцять другого 25 транзисторів, а також з вихідною шиною 27. Буферний каскад працює таким чином: якщо напруга на вхідній шині 1 збільшується, то третій 5 транзистор диференційного каскаду привідкривається, тринадцятий 16 транзистор диференційного каскаду призакривається. У свою чергу др угий 4 транзистор диференційного каскаду призакривається, дванадцятий 15 транзистор привідкривається. За таких умов колекторні струми третього 5 і дванадцятого 15 транзисторів збільшуються, а колекторні струми другого 4 і тринадцятого транзисторів зменшуються. Колекторний струм третього 5 транзистора проходить через колекторно-емітерний перехід каскода на п'ятому 9 транзисторі і витікає із бази шістнадцятого 19 транзистора. Колекторний струм тринадцятого 16 транзистора протікає через колекторноемітерний перехід каскода на дев'ятому 12 транзисторі і зменшує напругу на переходах база-емітер одинадцятого 14 і вісімнадцятого 18 транзисторів. При цьому колекторний струм відбивача струму на сьомому 8 транзисторі зменшується, шістнадцятий 19 транзистор привідкривається. Колекторний струм другого 4 транзистора протікає через колекторно-емітер перехід каскода на шостому 10 транзисторі і потрапляє в базу дев'ятнадцятого 22 транзистора. Колекторний струм дванадцятого 15 транзистора протікає через колекторноемітерний перехід каскода на десятому 13 транзисторі і потрапляє на бази чотирнадцятого 17 і двадцятого 23 транзисторів в діодному вмиканні і восьмий 11 транзистор привідкривається, а його колекторний струм збільшується. Дев'ятнадцятий 22 транзистор призакривається. За таких умов колекторний струм шістнадцятого 19 транзистора збільшується, а колекторний струм дев'ятнадцятого 22 транзистора зменшується. При цьому двадцять перший 24 транзистор вихідного каскаду привідкривається, а двадцять другий 25 транзистор вихідного каскаду призакривається, емітерний струм двадцять першого 24 транзистора збільшується, а емітер ний струм двадцять другого 25 транзистора зменшується. За таких умов потенціал вихідної шини 27 збільшується. Це змінення сигналу на виході схеми призводить до того, що тринадцятий 16 транзистор починає привідкриватися, а дванадцятий 15 транзистор призакриватися. Подібна операція триває доти, поки напруга на вихідній шині 27 схеми не зрівняється з напругою на вхідній шині 1 схеми. При цьому диференційні каскади відповідно, на третьому 5 і тринадцятому 16 транзисторах, а також на другому 4 і дванадцятому 15 транзисторах балансуються. Якщо напруга на вхідній шині 1 схеми зменшується, то другий 4 транзистор диференційного каскаду привідкривається, дванадцятий 15 транзистор диференційного каскаду призакривається. У свою чергу, третій 5 транзистор диференційного каскаду призакривається, тринадцятий 16 транзистор диференційного каскаду привідкривається. За таких умов колекторний струм др угого 4 і тринадцятого 16 транзисторів збільшується, а колекторний струм третього 5 і дванадцятого 15 транзисторів зменшується. Колекторний струм другого 4 транзистора проходить через колекторно-емітерний перехід каскода на шостому 10 транзисторі і втікає в базу дев'ятнадцятого 22 транзистора. Колекторний струм дванадцятого 15 транзистора протікає через колекторноемітерний перехід каскода на десятому 13 транзисторі і зменшує напругу на переходах база-емітер чотирнадцятого 17, двадцятого 23 транзисторів. При цьому колекторний струм відбивача струму на восьмому 11 транзисторі зменшується, дев'ятнадцятий 22 транзистор привідкривається. Колекторний струм третього 5 транзистора протікає через перехід колетор-емітер каскода на п'ятому 9 транзисторі і потрапляє в базу шістнадцятого 19 транзистора. Колекторний струм тринадцятого 16 транзистора протікає через колеторноемітерний перехід каскода на дев'ятому 12 транзисторі і потрапляє на бази одинадцятого 14, п'ятнадцятого 18 транзисторів в діодному вмиканні і сьомий 8 транзистор привідкривається, а його колекторний струм збільшується, при цьому шістнадцятий 19 транзистор призакривається. За таких умов колекторний струм дев'ятнадцятого 22 транзистора збільшується, а колекторний струм шістнадцятого 19 транзистора зменшується. При цьому двадцять другий 25 транзистор вихідного каскаду привідкривається, а двадцять перший 24 транзистор вихідного каскаду призакривається. Емітерний струм двадцять другого 25 транзистора збільшується, а емітерний струм двадцять першого 24 транзистора зменшується. За таких умов потенціал вихідної шини 27 зменшується. Це змінення сигналу на виході схеми призводить до того, що дванадцятий 15 транзистор починає привідкриватись, а тринадцятий 16 транзистор призакриватись. Побідна операція триває доти, поки напруга на вихідній шині 27 схеми не зрівняється з напругою на вхідній шині 1 схеми. При цьому диференційні каскади відповідно, на другому 4, дванадцятому 15 транзисторах, а також третьому 5, шістнадцятому 16 транзисторах балансуються. Використання схем відбивачів струму відповідно, на сьомому 8, одинадцятому 14, п'ятнадцятому 18, шістнадцятому 19 транзисторах, а також на восьмому 11, чотирнадцятому 17, дев'ятнадцятому 22, двадцятому 23 транзисторах дозволяє досягти коефіцієнта передачі цих відбивачів орієнтовно до 2, а також значно збільшити вихідні опори колекторних переходів шістнадцятого 19, двадцять другого 19 транзисторів. Разом узяте це дозволяє зменшити похибку передачі вхідної напруги на вихід схеми за умови наявності навантаження на вихідній шині 27 схеми.

ДивитисяДодаткова інформація

Назва патенту англійськоюBuffer amplifier

Автори англійськоюAzarov Oleksii Dmytrovych, Kaduk Oleksandr Volodymyrovych, Krupelnytskyi Leonid Vitaliiovych

Назва патенту російськоюВуфферный каскад

Автори російськоюАзаров Алексей Дмитриевич, Кадук Александр Владимирович, Крупельницкий Леонид Витальевич

МПК / Мітки

Код посилання

<a href="https://ua.patents.su/3-23906-bufernijj-kaskad.html" target="_blank" rel="follow" title="База патентів України">Буферний каскад</a>

Попередній патент: Вежа у вигляді просторової ферми

Наступний патент: Спосіб лікування хронічних обструктивних захворювань легень у робітників машинобудівної промисловості

Випадковий патент: Шихта для виплавки сілікомарганцю