Пристрій комутації широкосмугових сигналів

Формула / Реферат

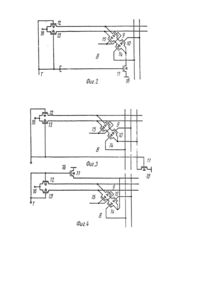

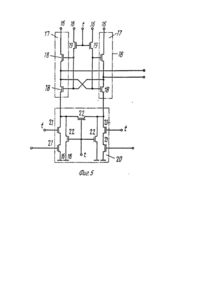

1. Устройство коммутации широкополосных сигналов, содержащее матрицу точек коммутации, узлы коммутации точек коммутации содержат схему управления и элемент коммутации, содержащий переключающий транзистор и дополнительный транзистор, при этом управляющий электрод переключающего транзистора соединен со схемой управления, а управляющий электрод дополнительного транзистора соединен с сигнальным проводом соответствующей входной линии матрицы, первый электрод переключающего транзистора соединен с первым электродом дополнительного транзистора, второй электрод которого соединен через считывающий транзистор с одним полюсом- источника питания, управляющий электрод считывающего транзистора соединен с управляющим электродом транзистора предварительного заряда, первый электрод которого соединен с другим полюсом источника питания, а второй электрод соединен со вторым электродом переключающего транзистора и с сигнальным проводом выходной линии, отличающееся тем, что введены дополнительный переключающий транзистор и второй дополнительный транзистор, первый электрод которого соединен с первым электродом дополнительного переключающего транзистора, второй электрод второго дополнительного транзистора соединен со вторым электродом дополнительного транзистора, второй электрод дополнительного переключающего транзистора соединен с первым электродом дополнительного транзистора предварительного заряда и со вторым сигнальным проводом выходной линии, управляющий электрод второго дополнительного транзистора соединен со вторым сигнальным проводом входной линии, а управляющий и второй электроды дополнительного транзистора предварительного заряда соединены соответственно с управляющим и вторым электродами транзистора предварительного ряда, при этом провода выходной линии соединены с входами выходного дифференциального усилителя, провода входной линии соединены с выходами входного дифференциального усилителя, а управляющий электрод дополнительного переключающего транзистора соединен с управляющим электродом переключающего транзистора.

2. Устройство по п. 1, отличающееся тем, что вторые электроды дополнительных транзисторов объединены вертикалью.

3. Устройство по п. 1, отличающееся тем, что вторые электроды дополнительных транзисторов объединены горизонталью.

4. Устройство по п. 1, отличающаяся тем, что переключающий и дополнительный переключающие транзисторы, дополнительный и второй дополнительный транзисторы, а также считывающий транзистор являются транзисторами "n" типа, а транзистор предварительного заряда и дополнительный транзистор предварительного заряда являются транзисторами "р" типа.

5. Устройство по п. 1, отличающееся тем, что все транзисторы являются транзисторами "р" типа.

6. Устройство по п. 1, отличающаяся тем, что выходной дифференциальный усилитель содержит два перекрестно соединенных инвертора, каждый из которых содержит два последовательно соединенных первых транзистора, управляющие входы которых соединены через соответствующие вторые транзисторы с одним полюсом источника питания и соединенный с инверторами блок управления, содержащий две пары третьих транзисторов, соединенных с другим полюсом источника питания, к которому подключены четвертые транзисторы, управляющие электроды которых подключены к тактовому входу.

Текст

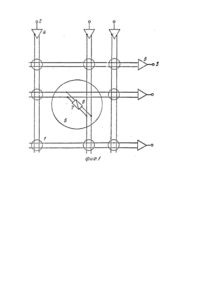

Изобретение относится к технике связи и может быть использовано в узлах коммутации. Цель изобретения - повышение быстродействия. На фиг. 1 представлена структурная электрическая схема устройства коммутации широкополосных сигналов; на фиг. 2-4 - примеры реализации элемента коммутации; на фиг. 5 - структурная электрическая схема выходного дифференциального усилителя с триггерной характеристикой; на Фиг. 6 - временные диаграммы работы устройства. Устройство коммутации широкополосных сигналов содержит матрицу 1 точек коммутации, входные линии 2, выходные линии 3, входные дифференциальные усилители 4, выходные дифференциальные усилители 5, узлы 6 коммутации точек коммутации, каждый из которых содержит схему 7 управления и элемент 8 коммутации, содержащий переключающий транзистор 9, дополнительный транзистор 10, считывающий транзистор 11,транзистор 12 предварительного заряда, дополнительный транзистор 13 предварительного заряда, второй дополнительный транзистор 14 и дополнительный переключающий транзистор 15, источник 16 питания. Выходной дифференциальный усилитель 5 (фиг. 5) содержит инверторы 17, каждый из которых содержит первые транзисторы 18, вторые транзисторы 19, блок 20 управления, содержащий третьи транзисторы 21 и четвертые транзисторы 22. Во время предварительной фазы ph оба сигнальных провода выходных линий 3 матрицы заряжаются через соответствующий транзистор 12 или 13 предварительного заряда до рабочего потенциала (фиг. 6в), для чего выполненные на основе р-канальных транзисторов транзисторы 12,13 предварительного заряда в приведенном примере становятся проводящими в результате "0" сигнала тактового импульса. Одновременно образованные η-канальными транзисторами считывающие транзисторы 11 управляются противоположно с помощью того же "0" сигнала тактового импульса, т.е. запираются так что зарядка обоих сигнальных проводов выходных линий 3 матрицы 1 может осуществляться независимо от управления соответствующими переключающими транзисторами 9, 15 и каждого из дополнительных транзисторов 10, 14 отдельных пар элементов 8 коммутации на входной линии 2. При этом иногда уже может создаваться соответствующий каждому коммутируемому биту потенциал (или удерживаться) как это показано на фиг. 66. Во время последующей основной фазы pv с помощью " 1" сигнала тактового импульса (фиг. 6г) производится запирание предварительно заряженных транзисторов 12,13 и одновременно - деблокирование считывающего транзистора 11. Если теперь начинают проводить переключающие транзисторы 9, 15 на основе прикладываемого к управляющему входу (в данном примере "1") коммутационного сигнала (фиг. 6а, точка связи находится в состоянии проключения), то теперь в соответствующи х проключаемому биту, существующи х на обоих сигнальных проводах, соответствующей входной линии 2 состояниях сигнала производится разрядка сигнальных проводов связанной с этой входной линией 2 через соответствующий элемент коммутации 8 выходной линии 3 или остается на уровне установленного во время предварительной фазы ρ потенциала. Если на сигнальном проводе соответствующей входной линии 2 устанавливается состояние сигнала "0" (фиг. 66) и если в соответствии с этим заперт (n-канальный) дополнительный транзистор 10 или 14 соответствующей пары элементов 8, то соответствующий сигнальный провод выходной линии 3 не разряжается через задействованный элемент 8, а удерживает, если нет никаких други х подводящих к этой выходной линии 3 точек связи, находящихся в состоянии проключения. Если же напротив на только что рассмотренном сигнальном проводе входной линии 2 имеется состояние сигнала "1"(фиг. 66) и, следовательно, дополнительный транзистор 10 или 14 рассмотренной пары элементов 8 становится проводящим так же, как и переключательный транзистор 9 или 14 и соответствующий считывающий транзистор 11, то разряжается соответствующий сигнальный провод выходной линии 3 через этот элемент 8 коммутации и приводится к потенциалу "0". Через деблокированный по своему управляющему входу узел 6 производится проключение соответствующего входного сигнала в инвертированном виде.

ДивитисяДодаткова інформація

Назва патенту англійськоюSwitching device of broad band signals

Назва патенту російськоюУстройство коммутации широкополосных сигналов

МПК / Мітки

МПК: H04M 3/00

Мітки: пристрій, комутації, сигналів, широкосмугових

Код посилання

<a href="https://ua.patents.su/5-19682-pristrijj-komutaci-shirokosmugovikh-signaliv.html" target="_blank" rel="follow" title="База патентів України">Пристрій комутації широкосмугових сигналів</a>

Попередній патент: Електростанція

Наступний патент: Розподільна планка для установки далекого зв’язку

Випадковий патент: Навісне обладнання робочого органа землерийної машини обертальної дії